Microcoded CCU Central Control Unit 252022 Microcoded CCU

- Slides: 47

Microcoded CCU (Central Control Unit) 2/5/2022 Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary. ca 1

What will this talk cover? l Look at what a “microcoded” processor means l Difference between microcoding and assembly code l Development of ever increasing complexity in CCU for different control tasks l Advantages of pipelining -- in context of CCU l Comparision of a microcoded CCU and the branch control logic of 21 k 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 2

4 Basic Phases of an Instruction l Fetch -- Bring the instruction to the instruction register over the instruction data bus l Decode -- Bring in the necessary operands into the processing unit l Execute -- Perform the necessary processing operation l Writeback -- Store the results of the process l Question is -- what controls the action 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 3

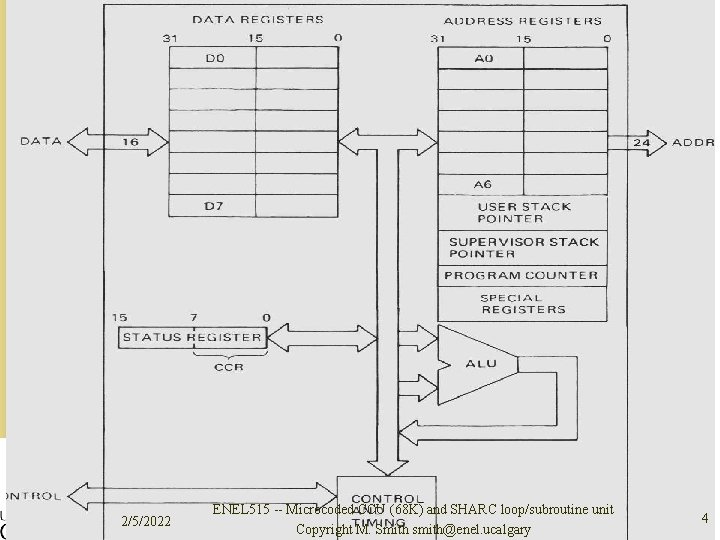

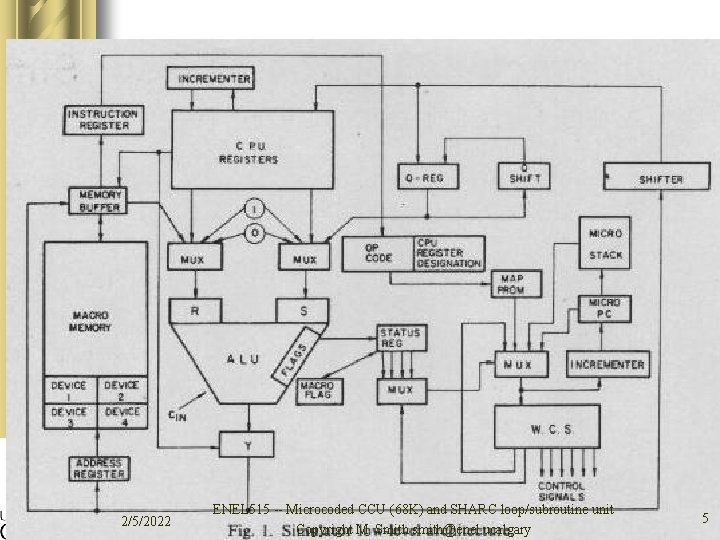

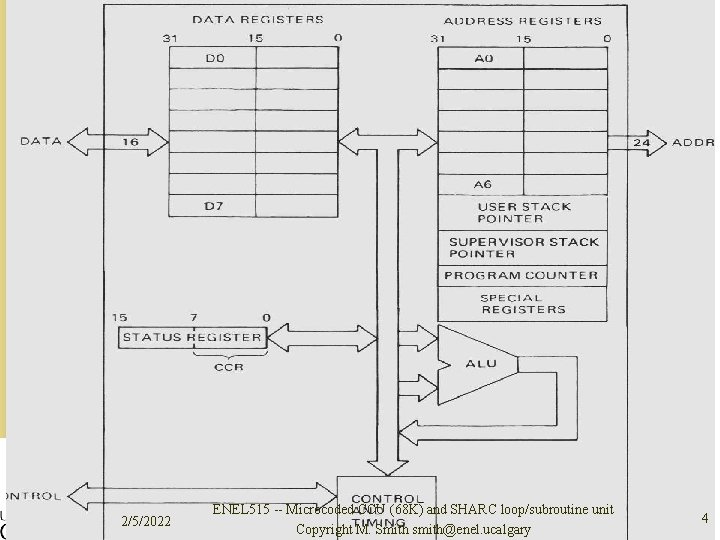

What are signals from CCU controlling? 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 4

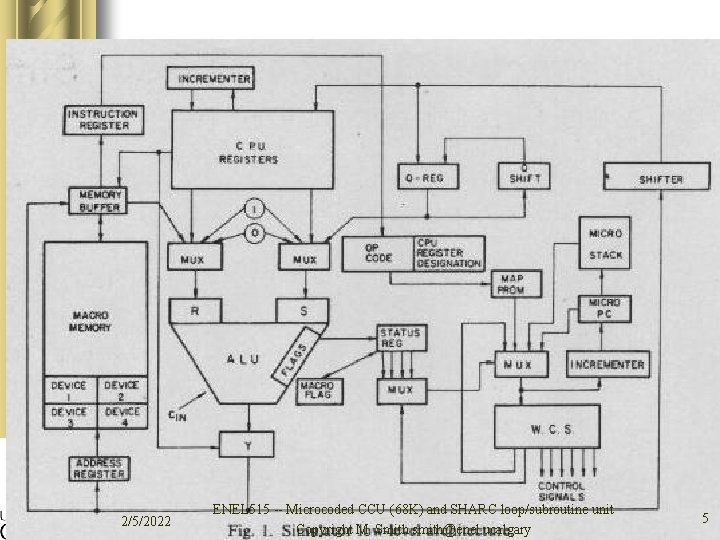

2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 5

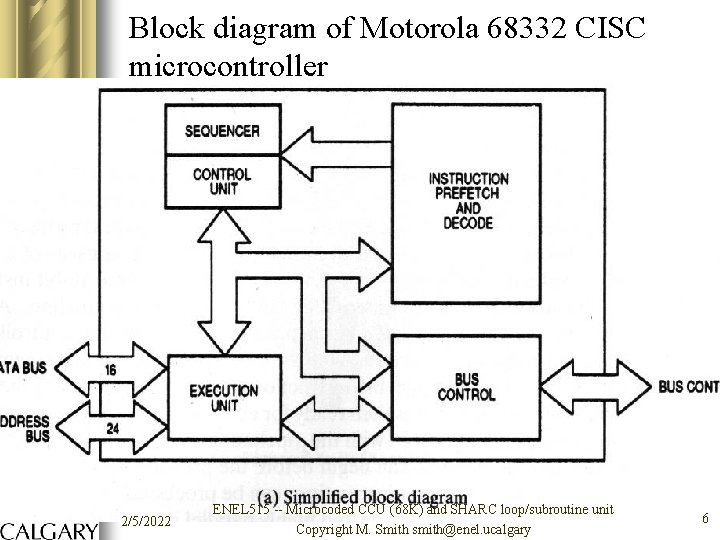

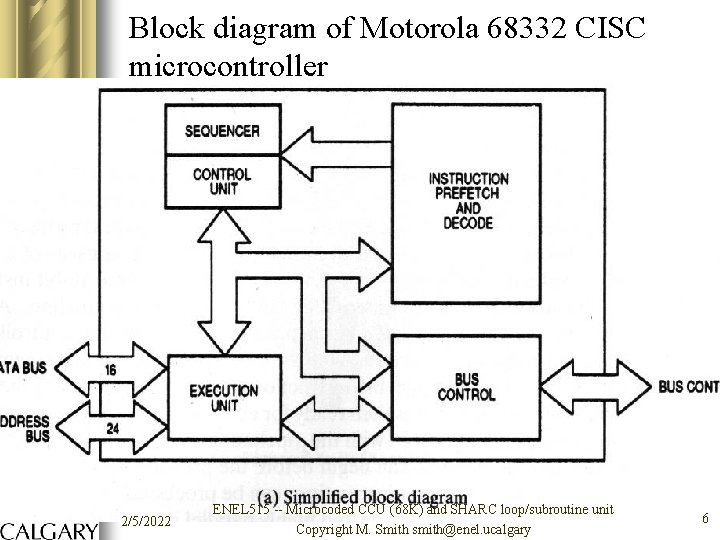

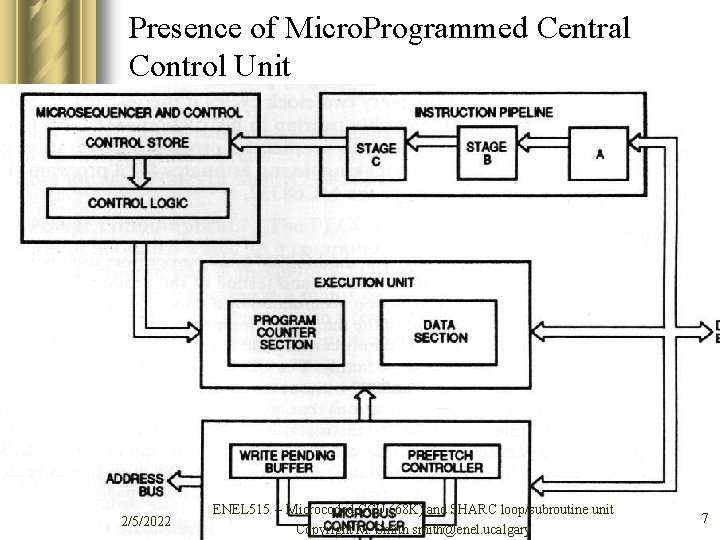

Block diagram of Motorola 68332 CISC microcontroller 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 6

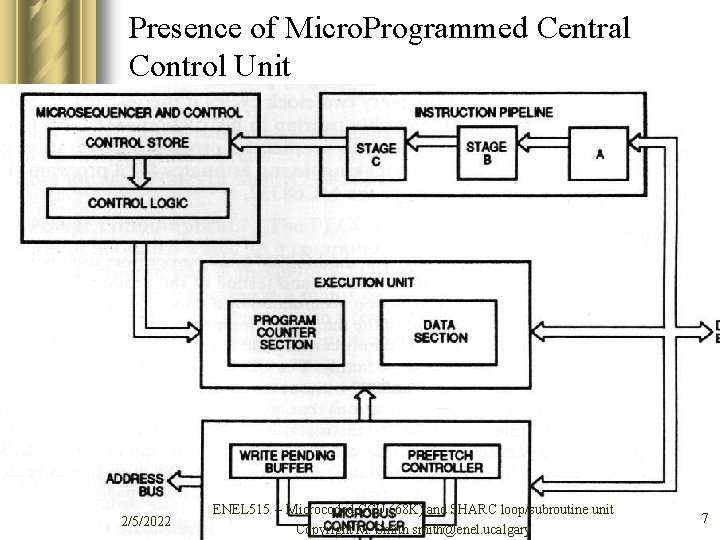

Presence of Micro. Programmed Central Control Unit 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 7

With a microcoded machine l With a microcoded machine, I can change instructions by changing the microcode l Can make it operate as ANY processor l Vax-780 -- Dr. Rao used to run a program in BASIC (interpreter) that used a microcode simulation of a non-780 machine l Build very fancy DSP array processors l Hardware features (and other concepts) can be found inside most DSP processors 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 8

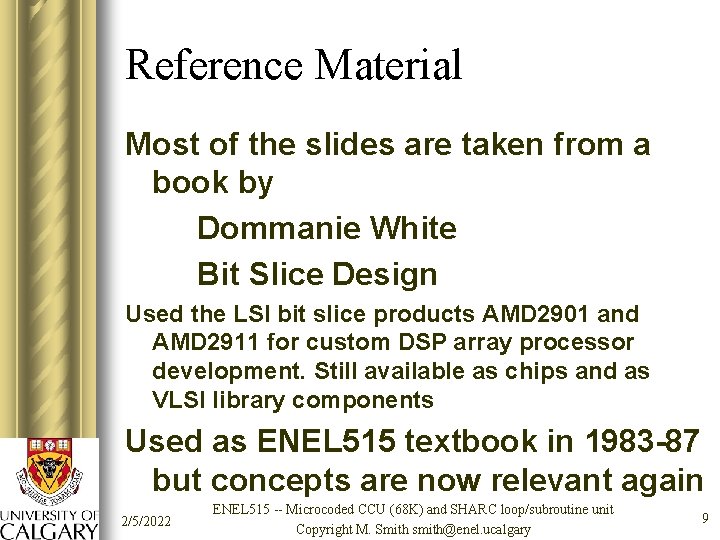

Reference Material Most of the slides are taken from a book by Dommanie White Bit Slice Design Used the LSI bit slice products AMD 2901 and AMD 2911 for custom DSP array processor development. Still available as chips and as VLSI library components Used as ENEL 515 textbook in 1983 -87 but concepts are now relevant again 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 9

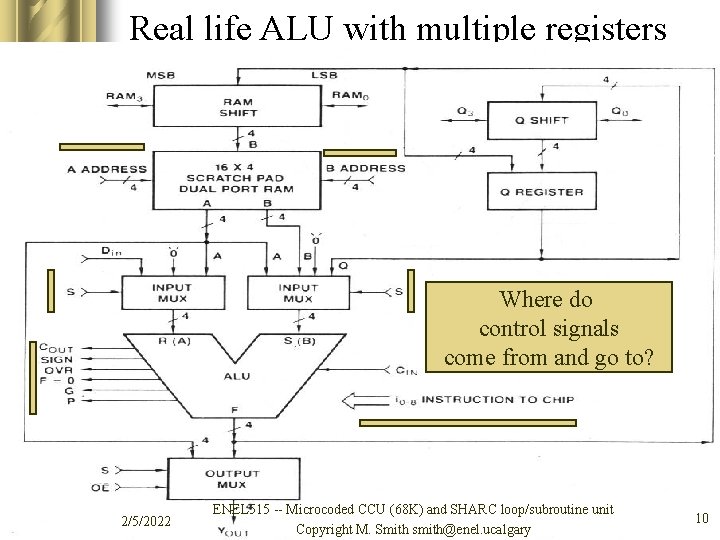

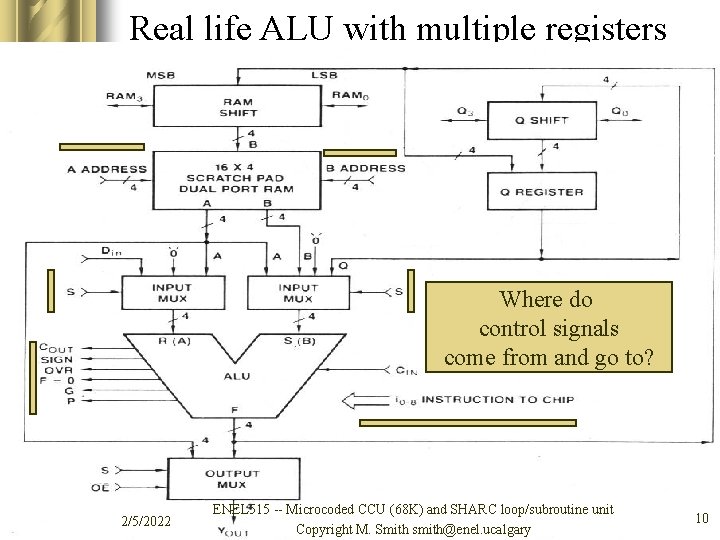

Real life ALU with multiple registers Where do control signals come from and go to? 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 10

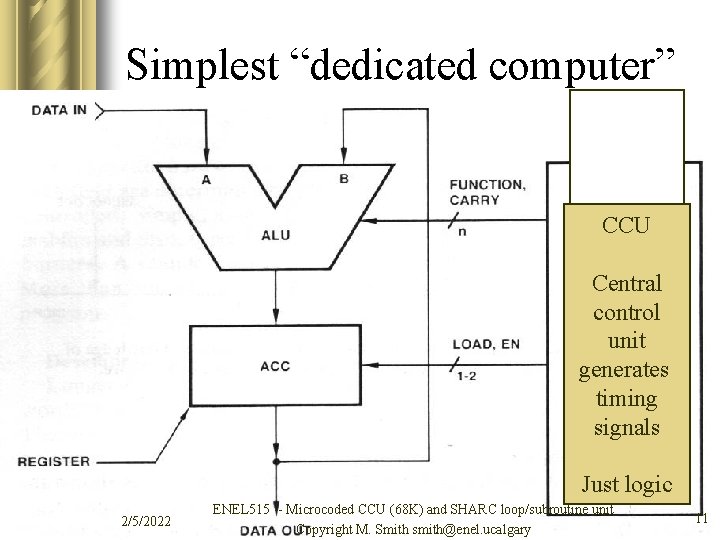

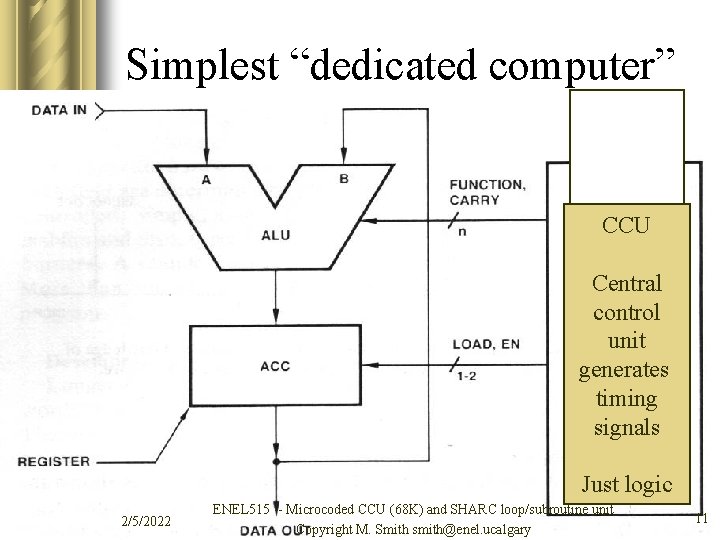

Simplest “dedicated computer” CCU Central control unit generates timing signals Just logic 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 11

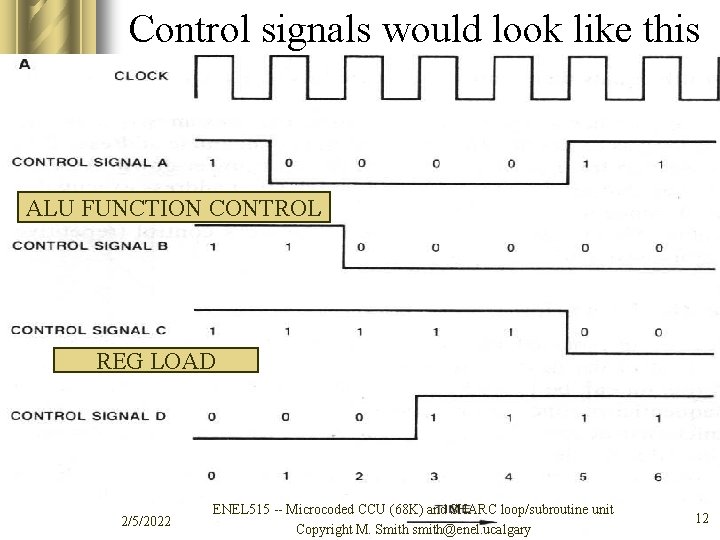

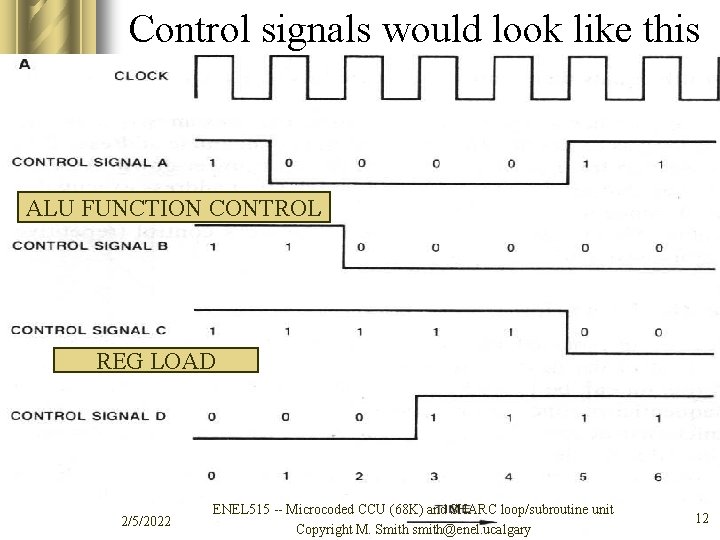

Control signals would look like this ALU FUNCTION CONTROL REG LOAD 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 12

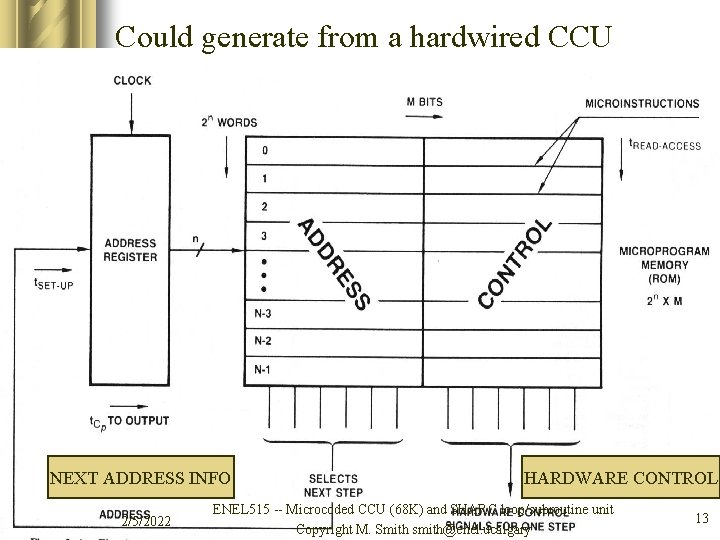

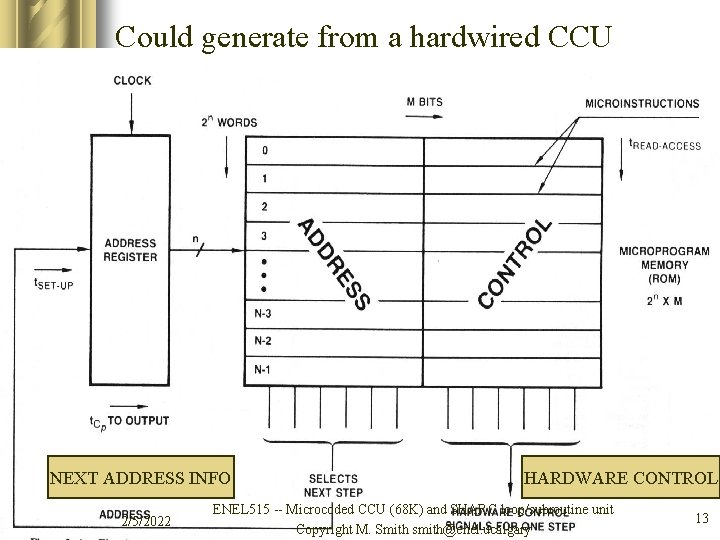

Could generate from a hardwired CCU NEXT ADDRESS INFO 2/5/2022 HARDWARE CONTROL ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 13

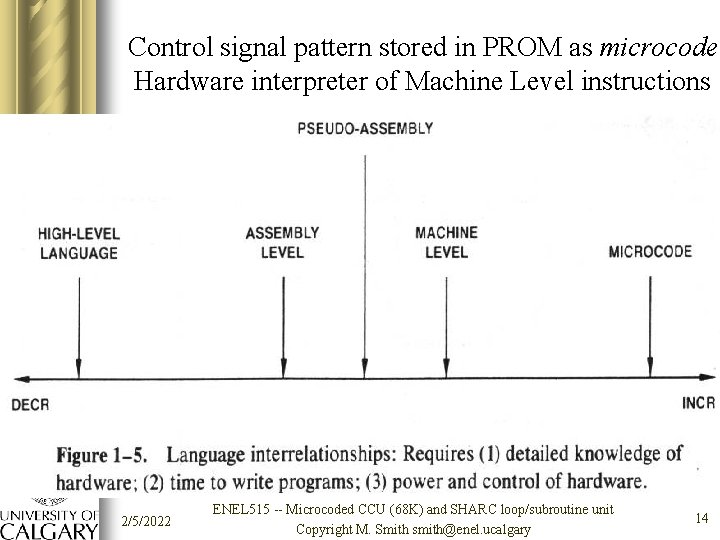

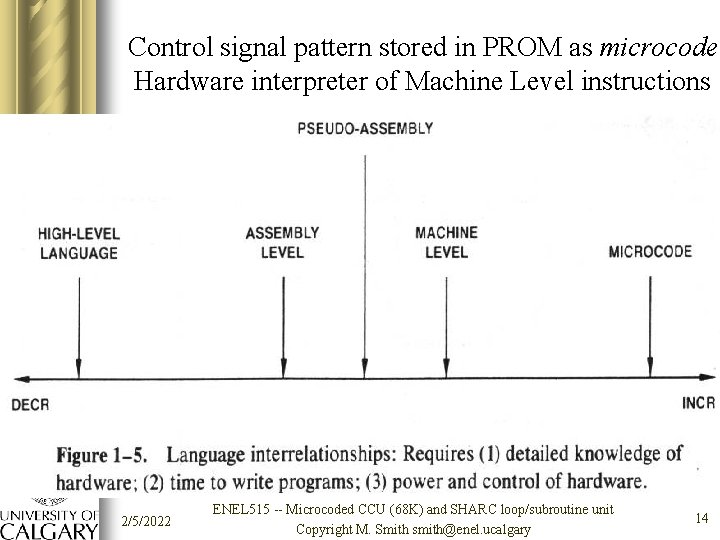

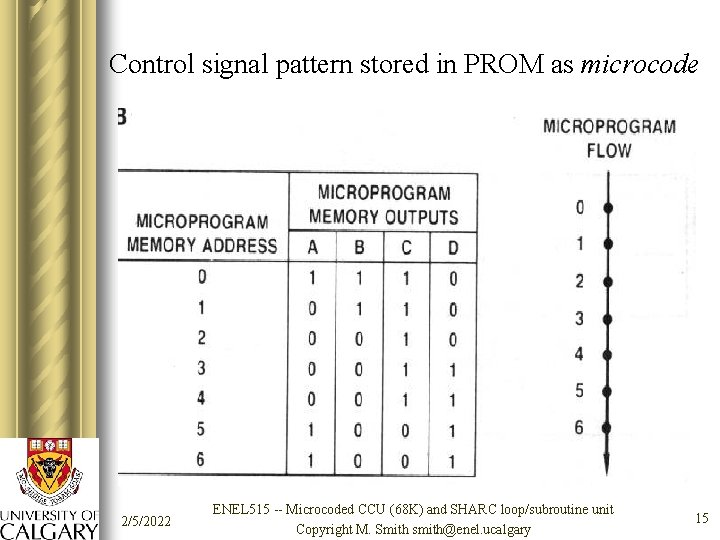

Control signal pattern stored in PROM as microcode Hardware interpreter of Machine Level instructions 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 14

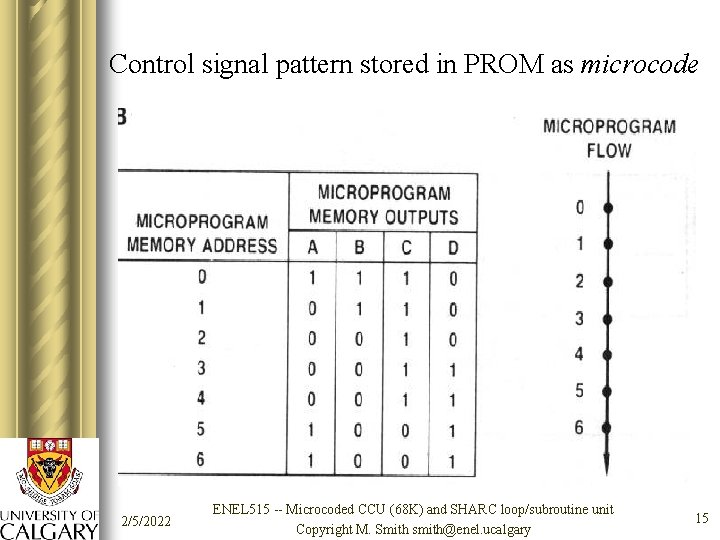

Control signal pattern stored in PROM as microcode 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 15

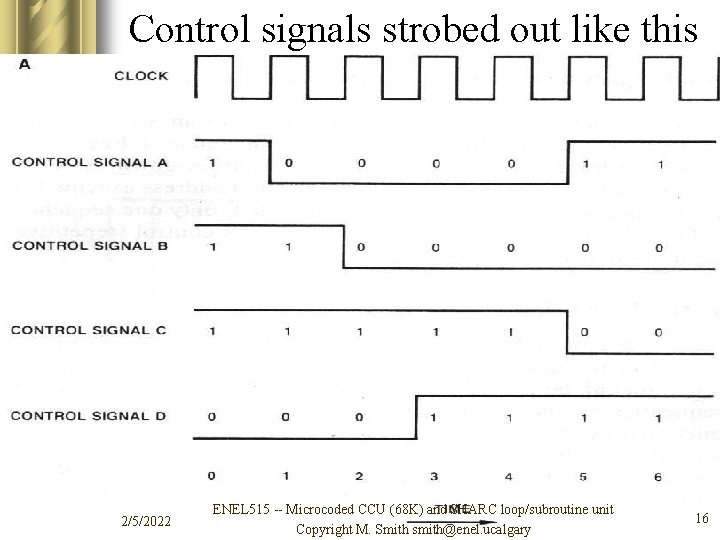

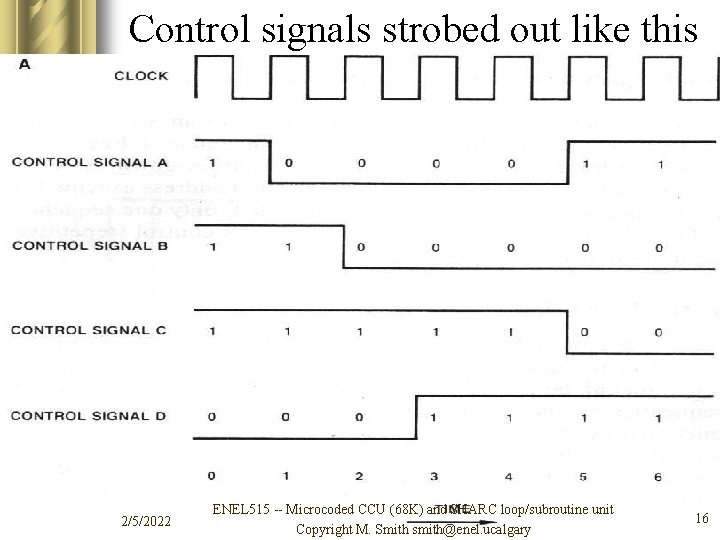

Control signals strobed out like this 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 16

Lots of wasted logic l Discrete Logic bad -- difficult to update l PROM -- can be blasted during design (of chip or board) l If next address of microcode instruction is always specified then can unravel the code into a simple consecutive sequence of addresses 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 17

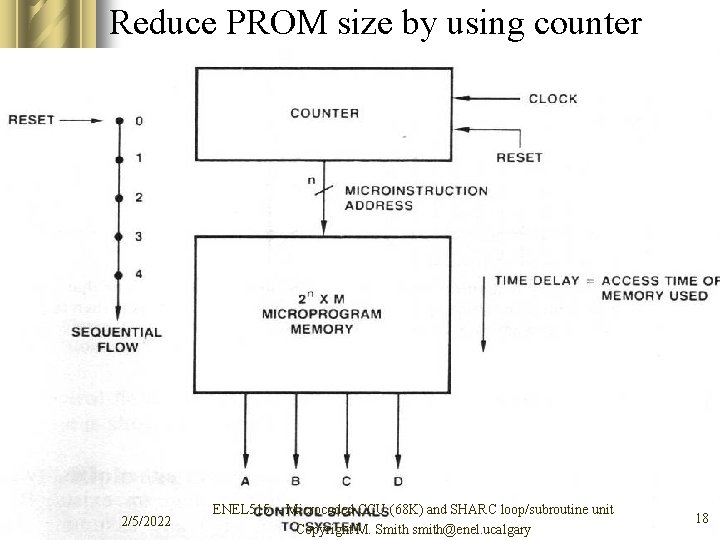

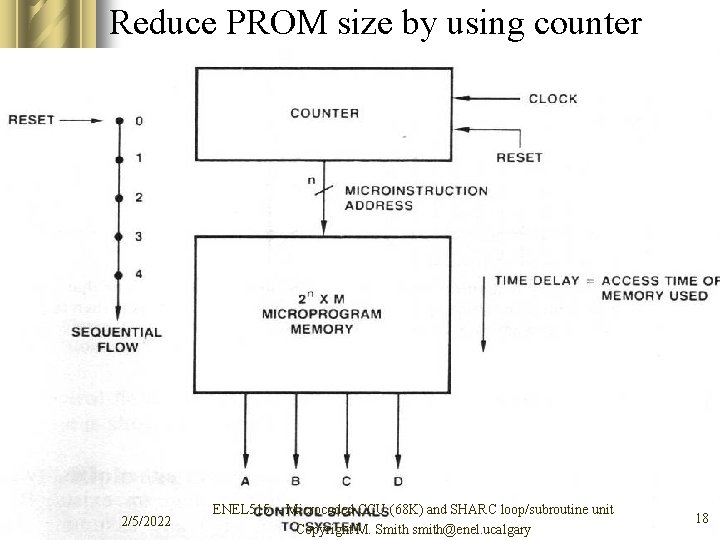

Reduce PROM size by using counter 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 18

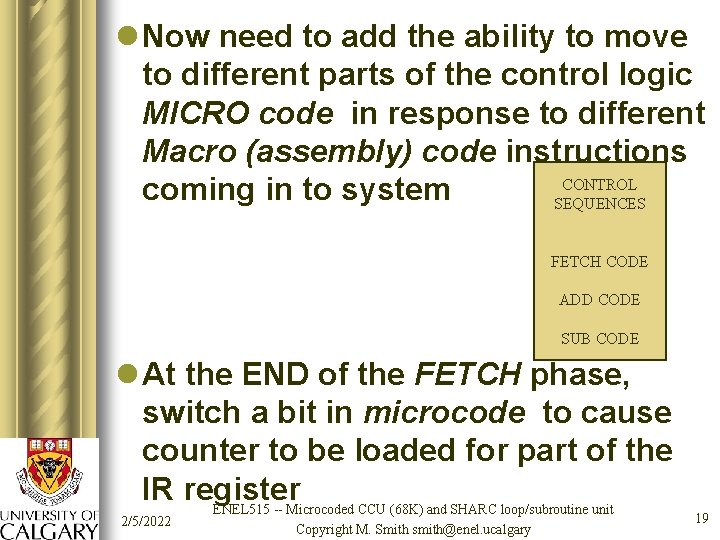

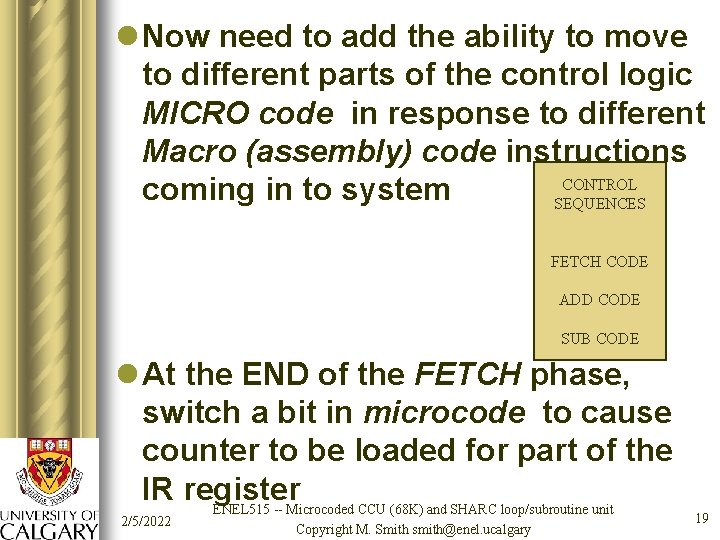

l Now need to add the ability to move to different parts of the control logic MICRO code in response to different Macro (assembly) code instructions CONTROL coming in to system SEQUENCES FETCH CODE ADD CODE SUB CODE l At the END of the FETCH phase, switch a bit in microcode to cause counter to be loaded for part of the IR register ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit 2/5/2022 Copyright M. Smith smith@enel. ucalgary 19

Start microcode from ASSEMBLY CODE INSTRUCTION by loading Loaded counter from external memory during Fetch Loaded last part of Fetch 2/5/2022 INSTRUCTION REGISTER CONTROL SEQUENCES FETCH ADD SUB ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 20

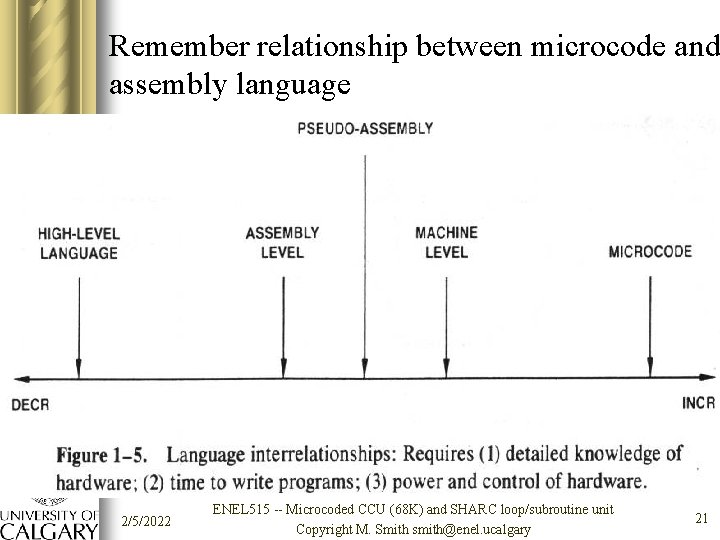

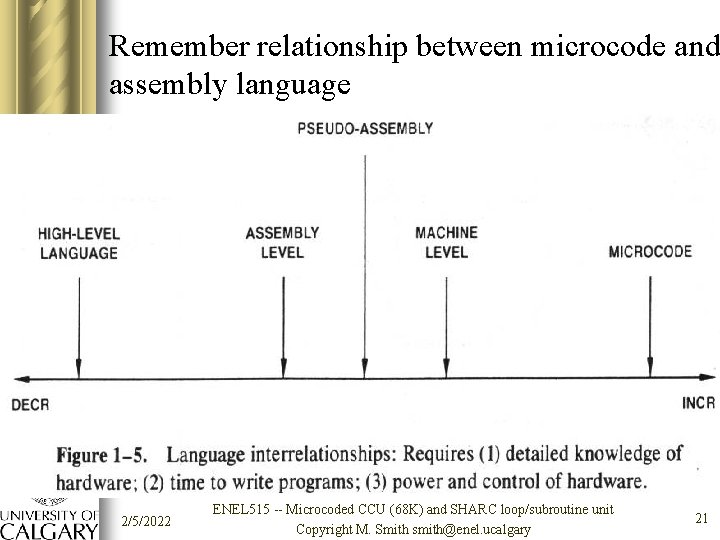

Remember relationship between microcode and assembly language 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 21

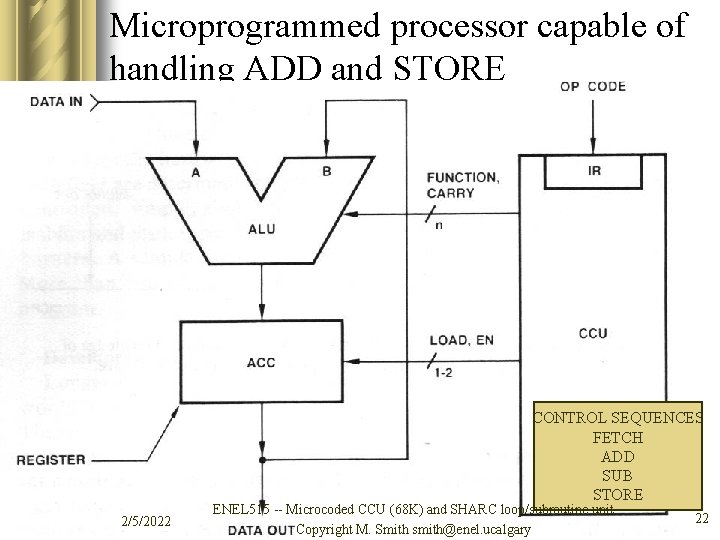

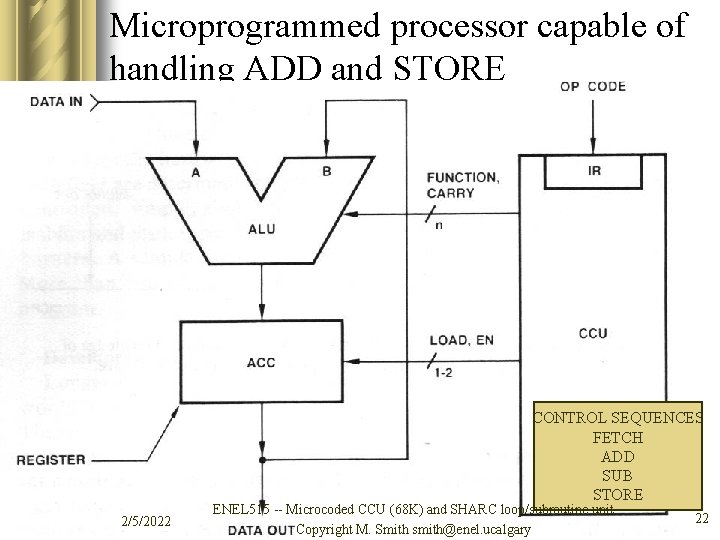

Microprogrammed processor capable of handling ADD and STORE CONTROL SEQUENCES FETCH ADD SUB STORE 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 22

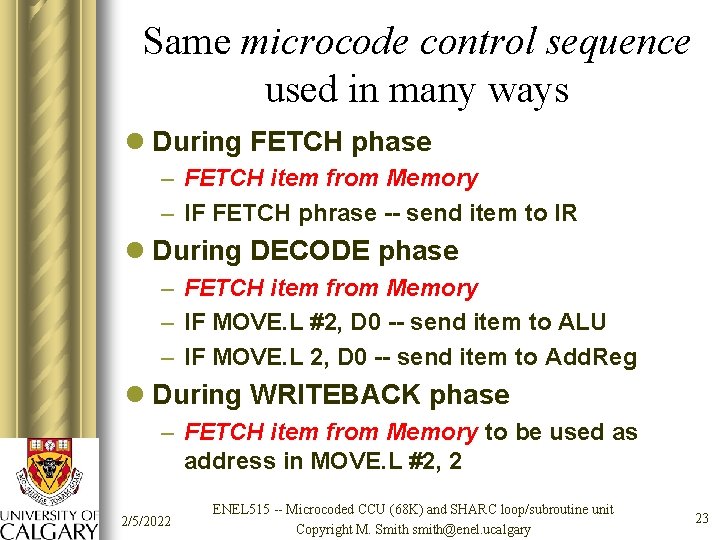

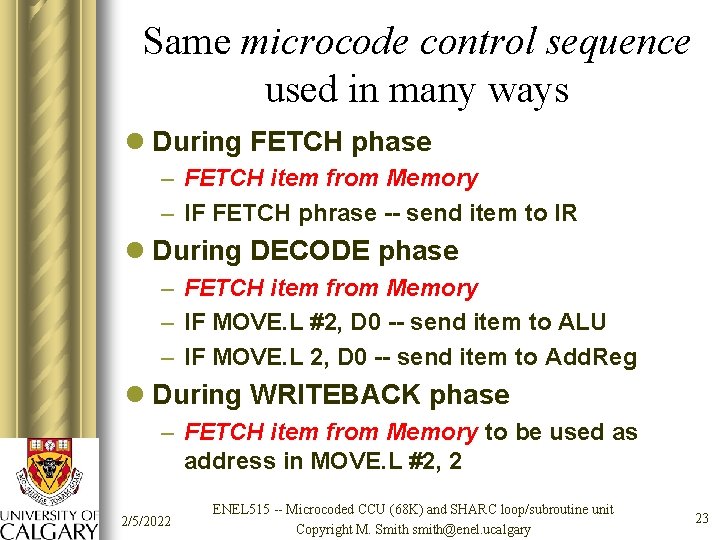

Same microcode control sequence used in many ways l During FETCH phase – FETCH item from Memory – IF FETCH phrase -- send item to IR l During DECODE phase – FETCH item from Memory – IF MOVE. L #2, D 0 -- send item to ALU – IF MOVE. L 2, D 0 -- send item to Add. Reg l During WRITEBACK phase – FETCH item from Memory to be used as address in MOVE. L #2, 2 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 23

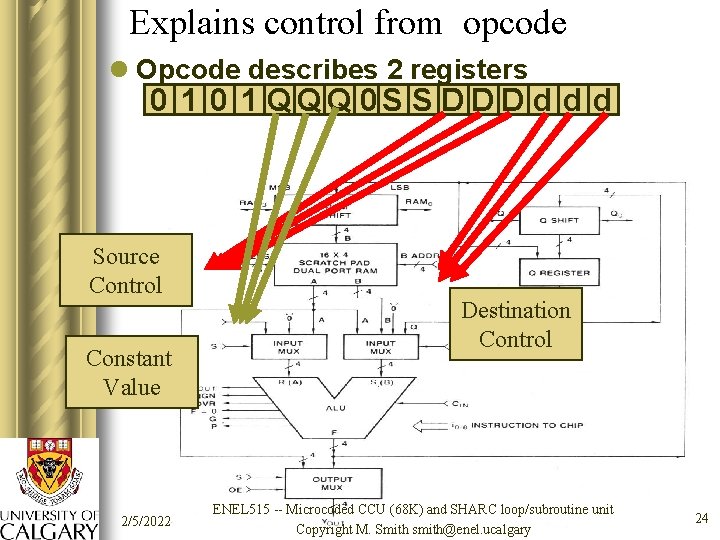

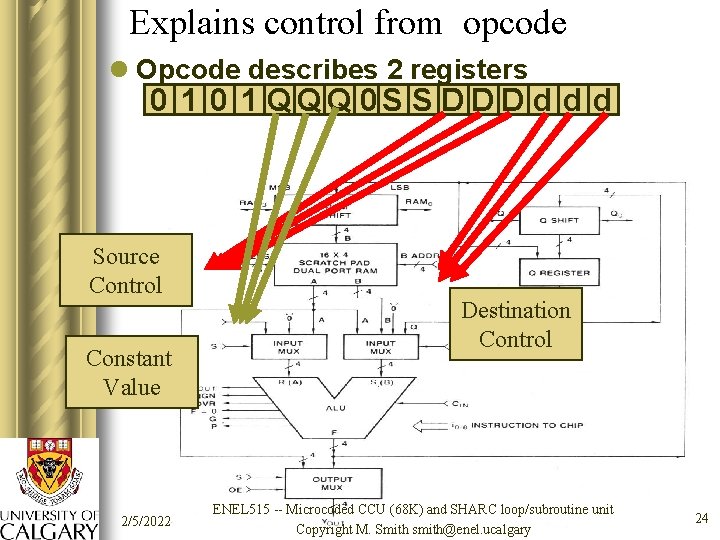

Explains control from opcode l Opcode describes 2 registers 0 1 QQQ 0 S S D D D d d d Source Control Constant Value 2/5/2022 Destination Control ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 24

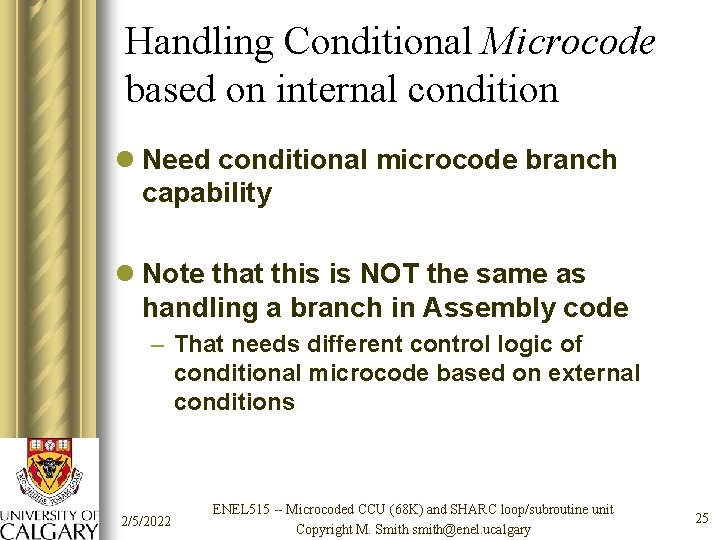

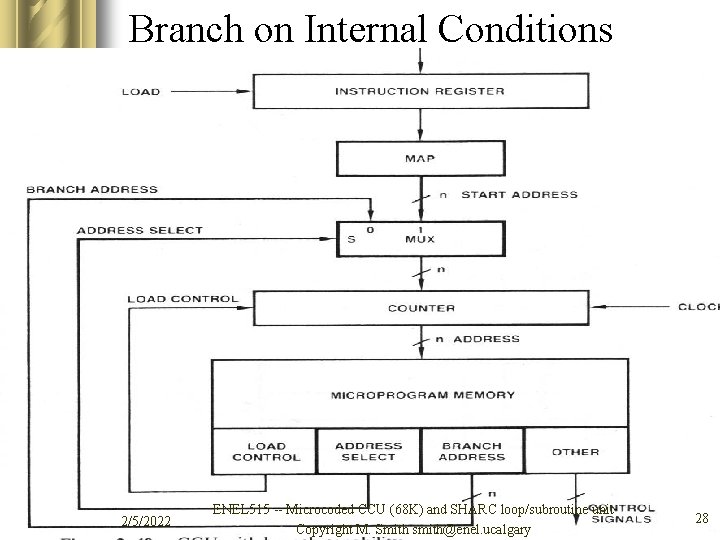

Handling Conditional Microcode based on internal condition l Need conditional microcode branch capability l Note that this is NOT the same as handling a branch in Assembly code – That needs different control logic of conditional microcode based on external conditions 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 25

Examples when might branch based on internal conditions l Handle all the control sequences needed to respond to the different effective addresses when trying to decode a 68 K or 21 K instruction l NOTE 21 K is not microcoded, BUR something equivalent must be happening 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 26

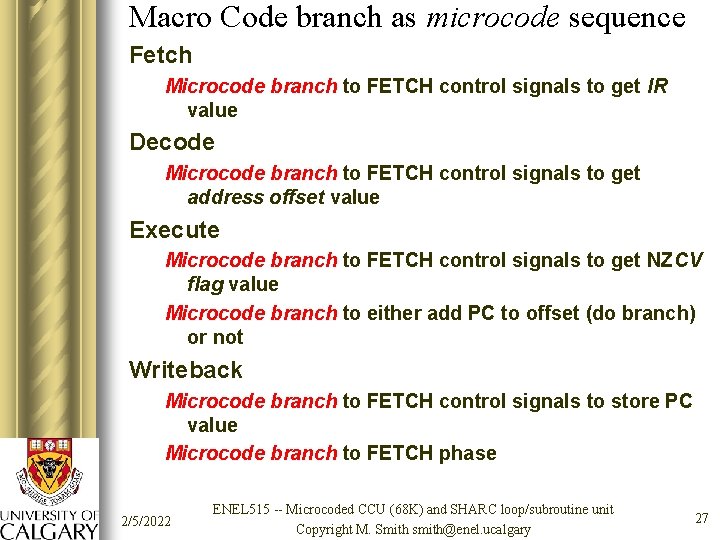

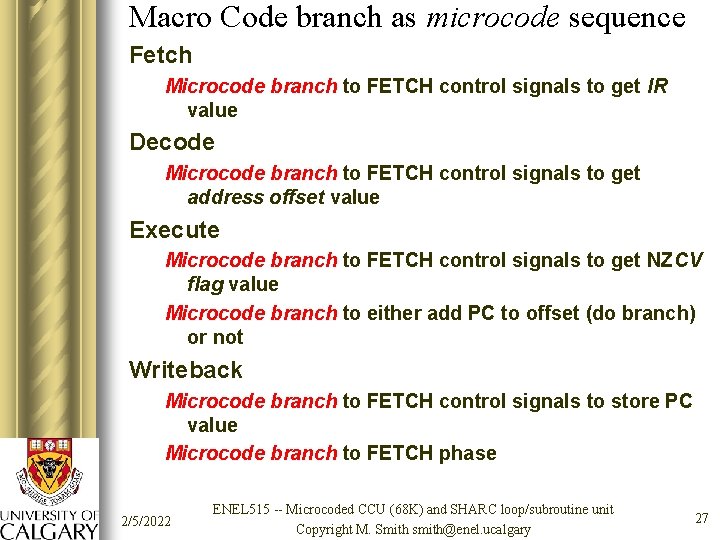

Macro Code branch as microcode sequence Fetch Microcode branch to FETCH control signals to get IR value Decode Microcode branch to FETCH control signals to get address offset value Execute Microcode branch to FETCH control signals to get NZCV flag value Microcode branch to either add PC to offset (do branch) or not Writeback Microcode branch to FETCH control signals to store PC value Microcode branch to FETCH phase 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 27

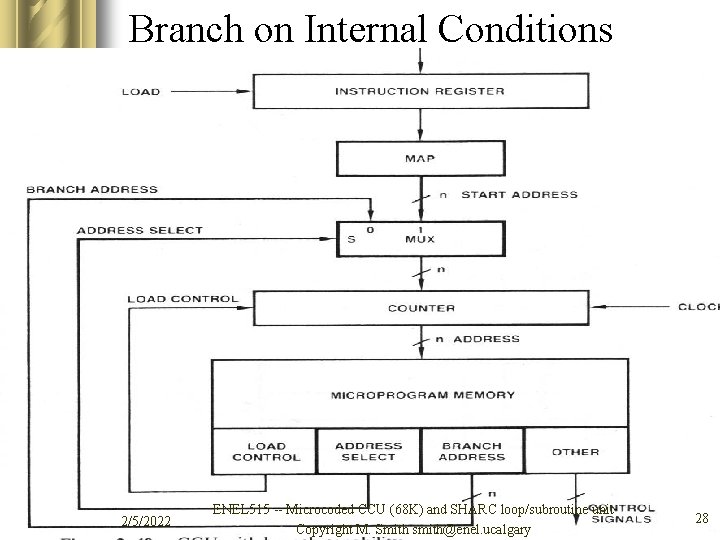

Branch on Internal Conditions 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 28

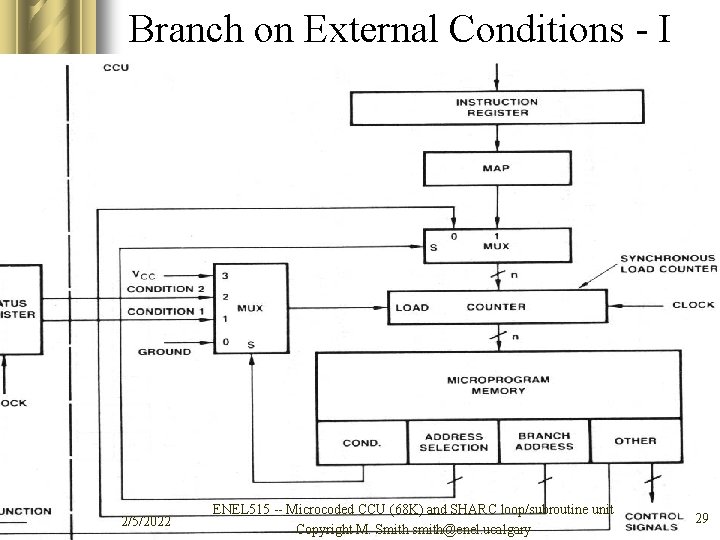

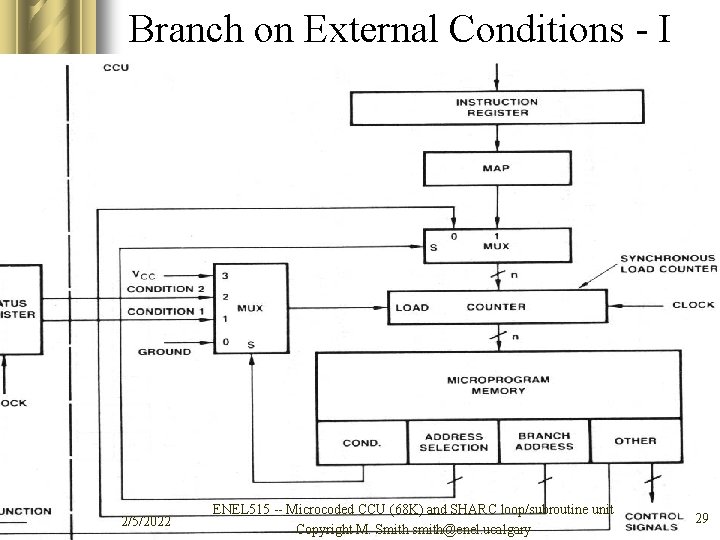

Branch on External Conditions - I 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 29

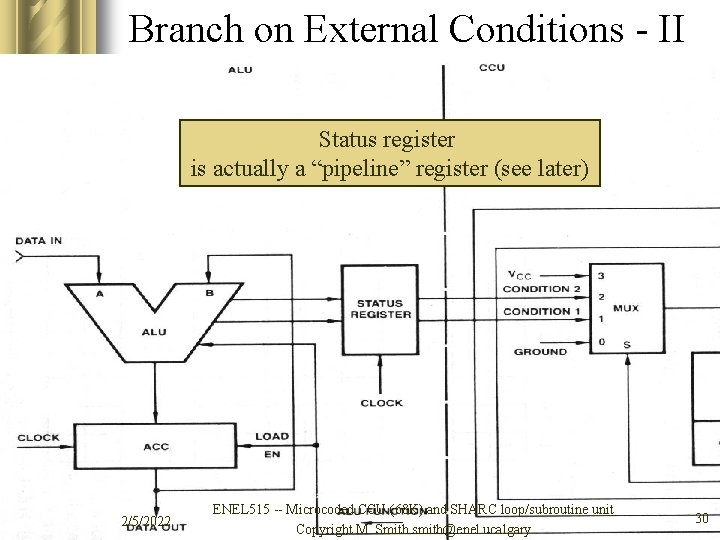

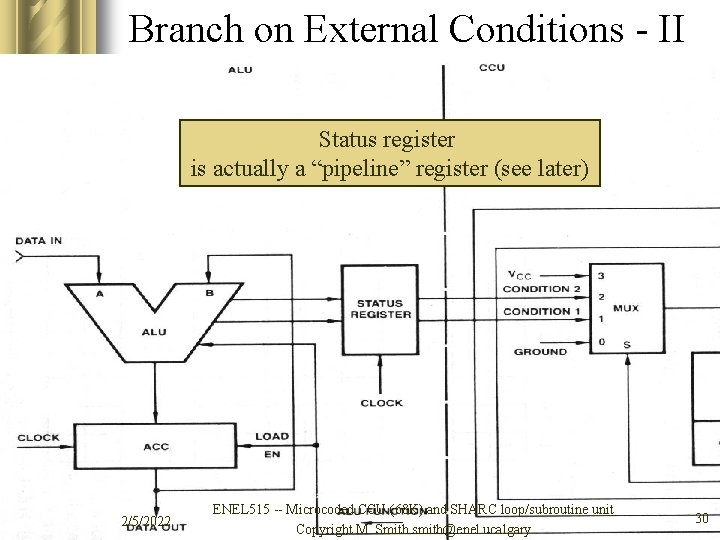

Branch on External Conditions - II Status register is actually a “pipeline” register (see later) 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 30

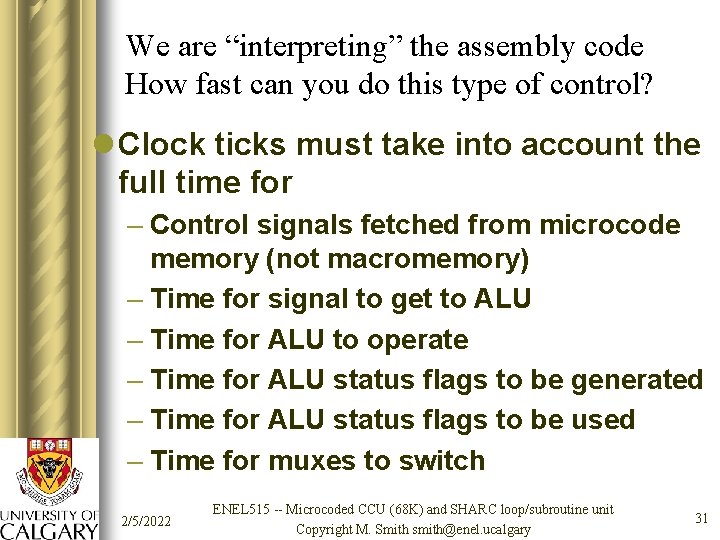

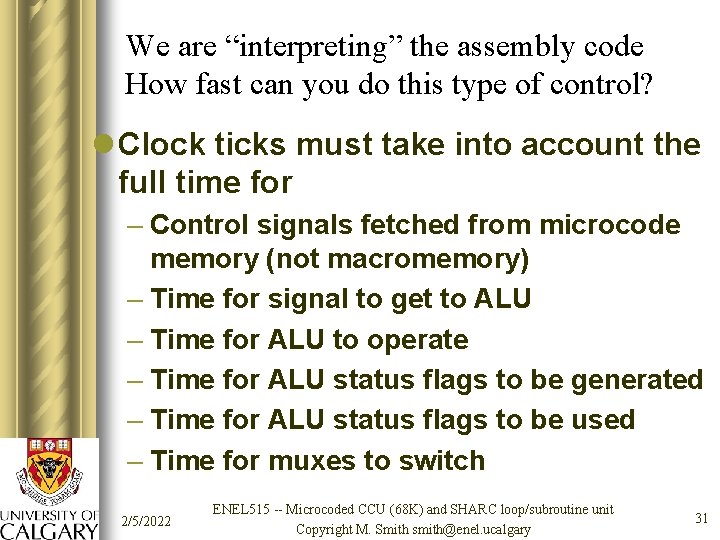

We are “interpreting” the assembly code How fast can you do this type of control? l Clock ticks must take into account the full time for – Control signals fetched from microcode memory (not macromemory) – Time for signal to get to ALU – Time for ALU to operate – Time for ALU status flags to be generated – Time for ALU status flags to be used – Time for muxes to switch 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 31

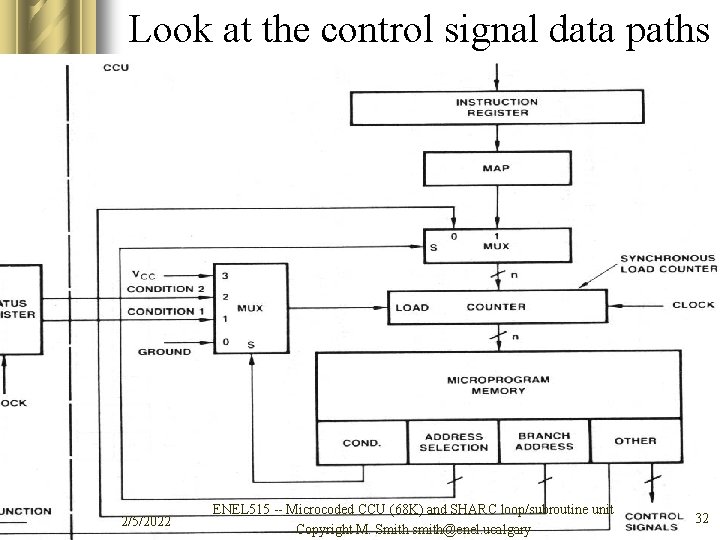

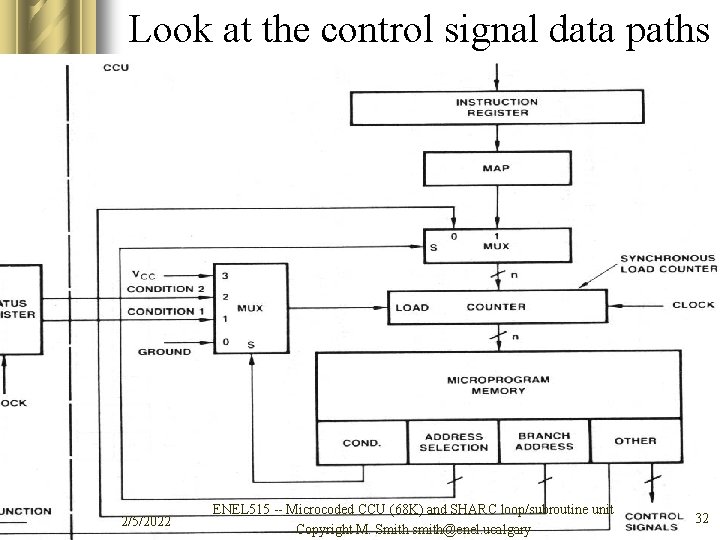

Look at the control signal data paths 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 32

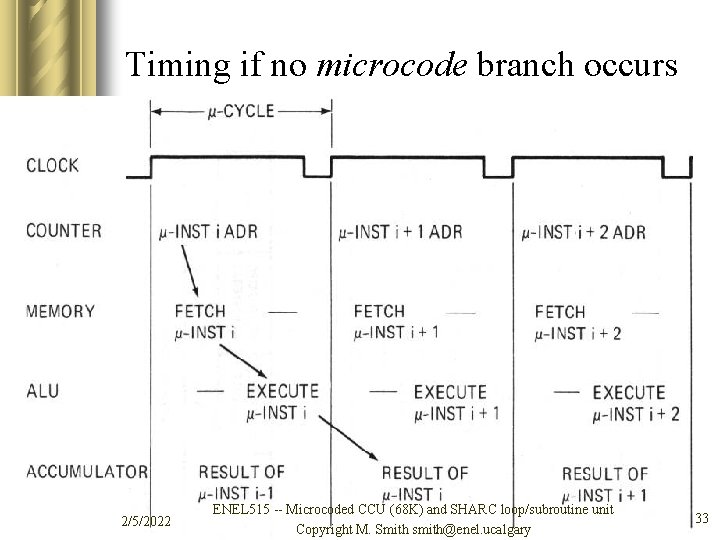

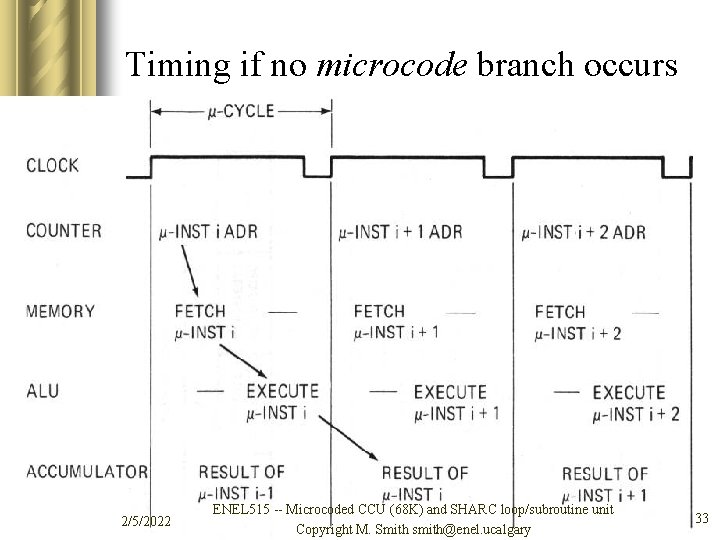

Timing if no microcode branch occurs 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 33

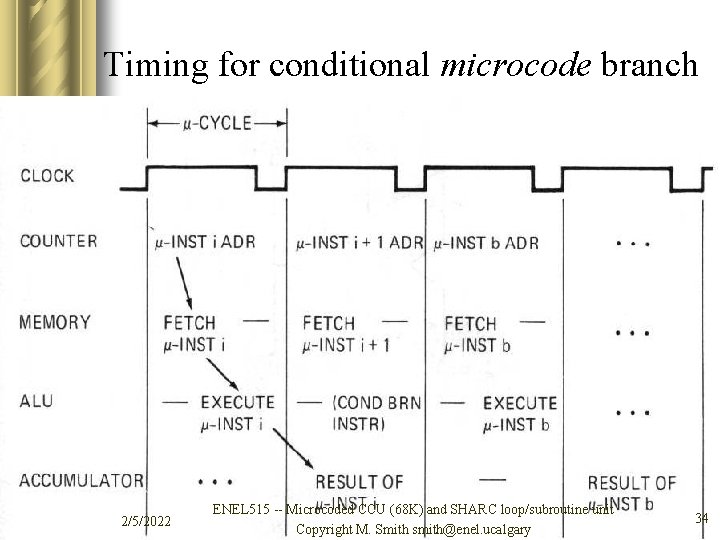

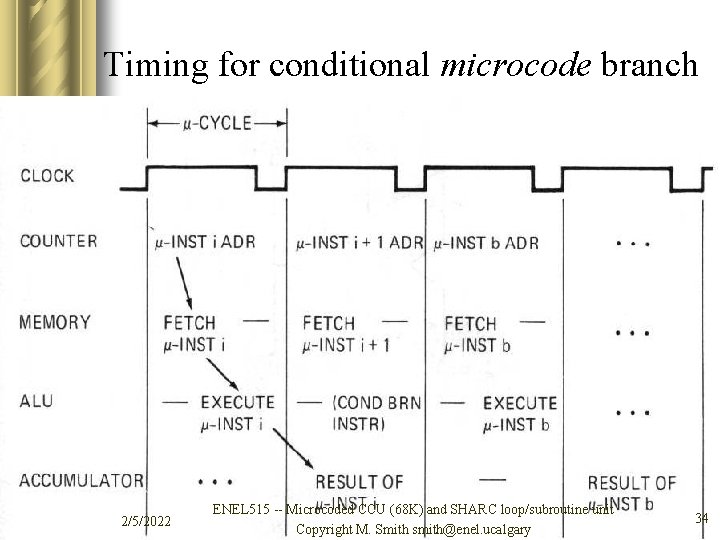

Timing for conditional microcode branch 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 34

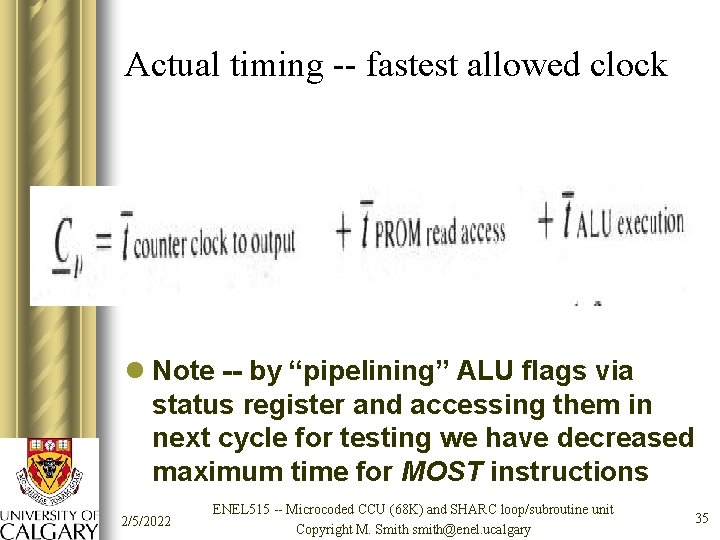

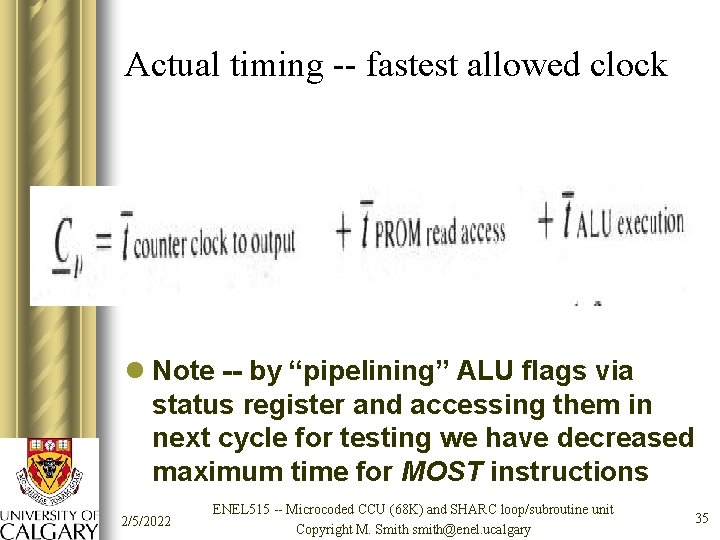

Actual timing -- fastest allowed clock l Note -- by “pipelining” ALU flags via status register and accessing them in next cycle for testing we have decreased maximum time for MOST instructions 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 35

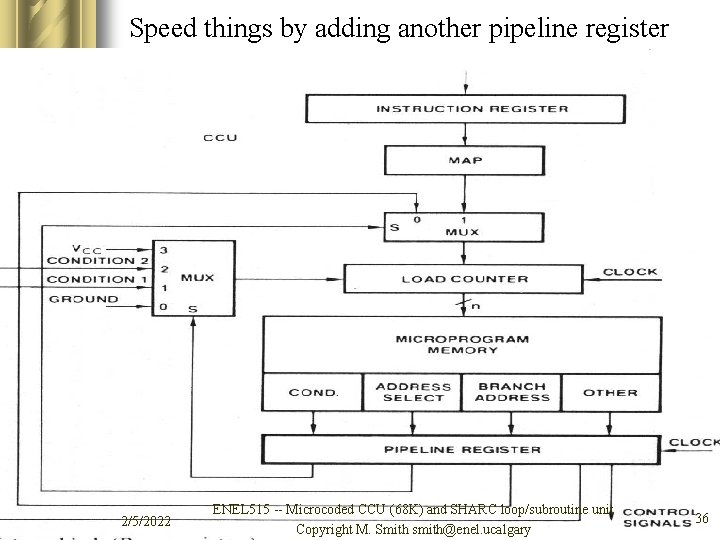

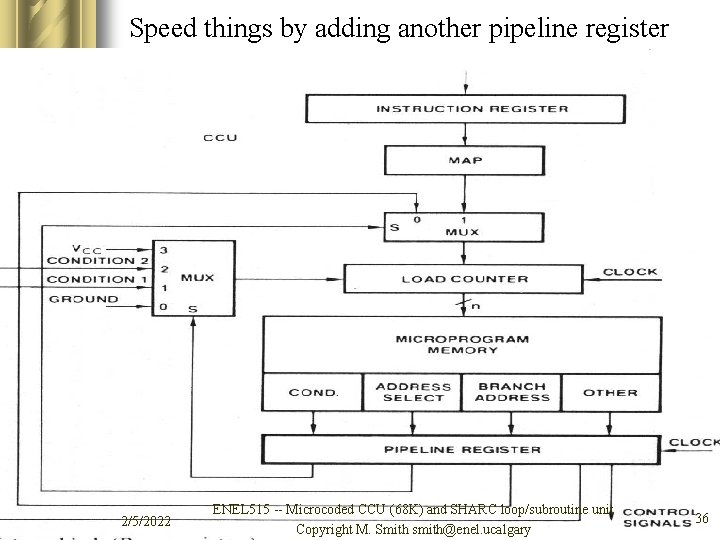

Speed things by adding another pipeline register 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 36

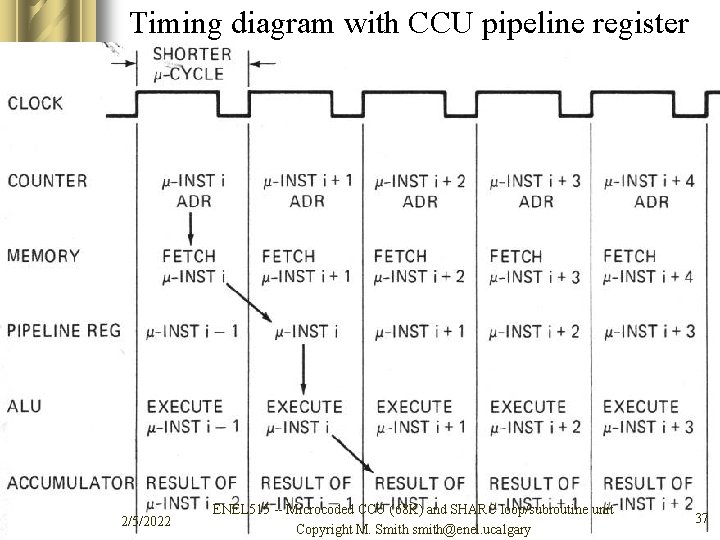

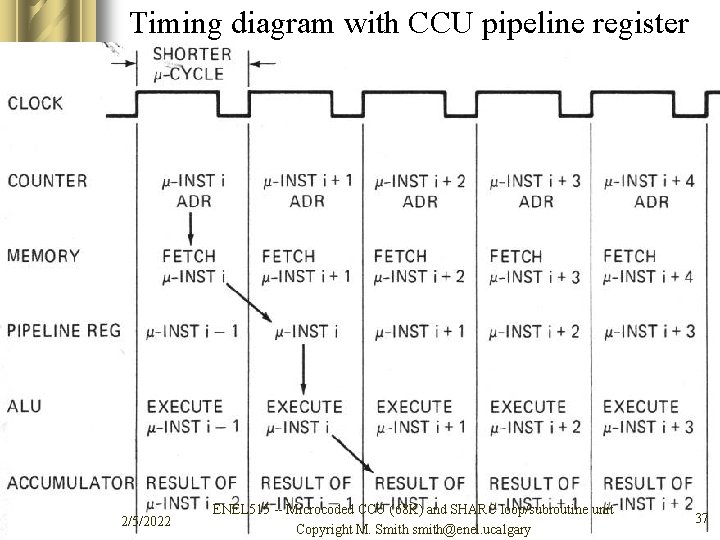

Timing diagram with CCU pipeline register 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 37

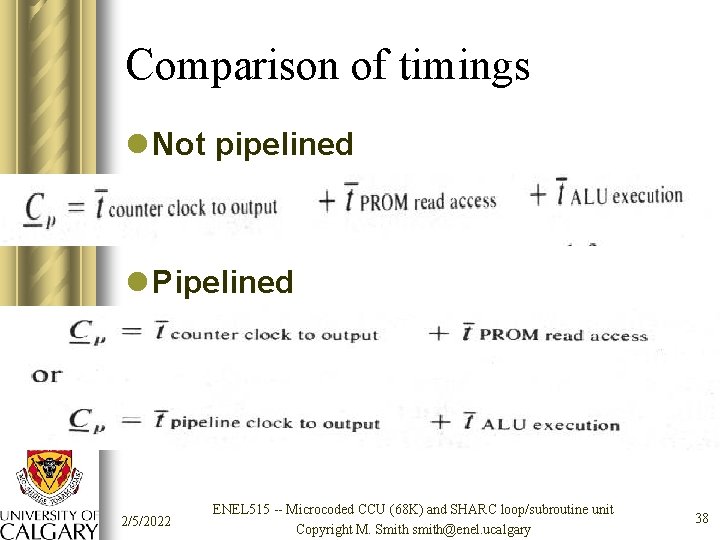

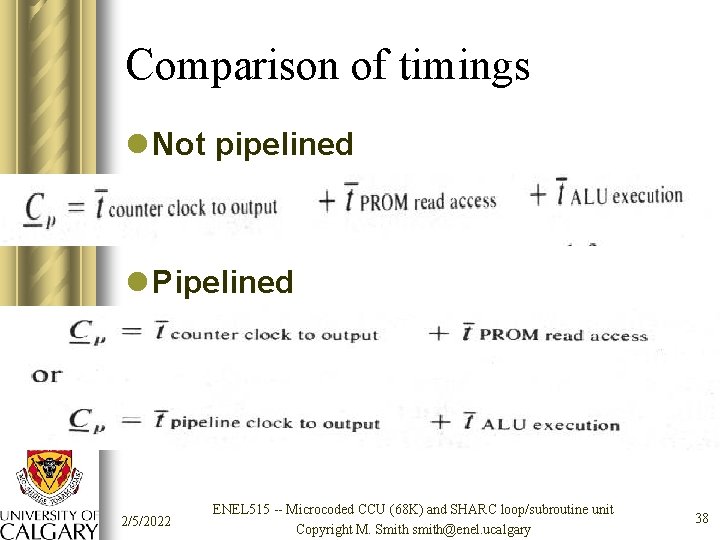

Comparison of timings l Not pipelined l Pipelined 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 38

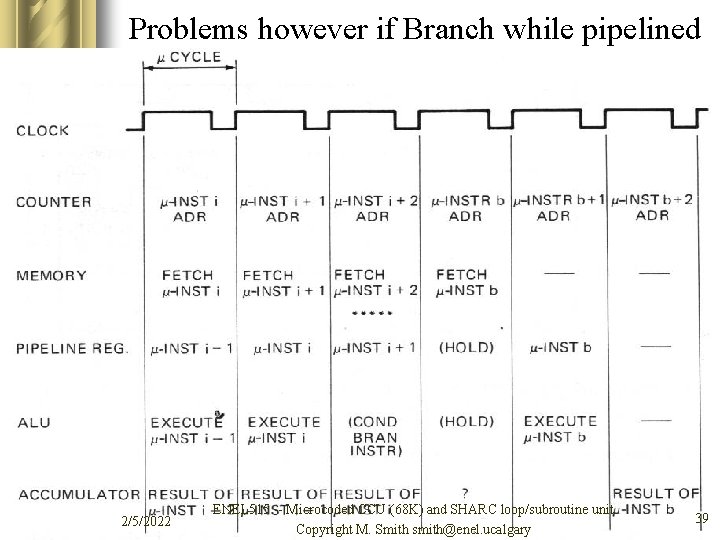

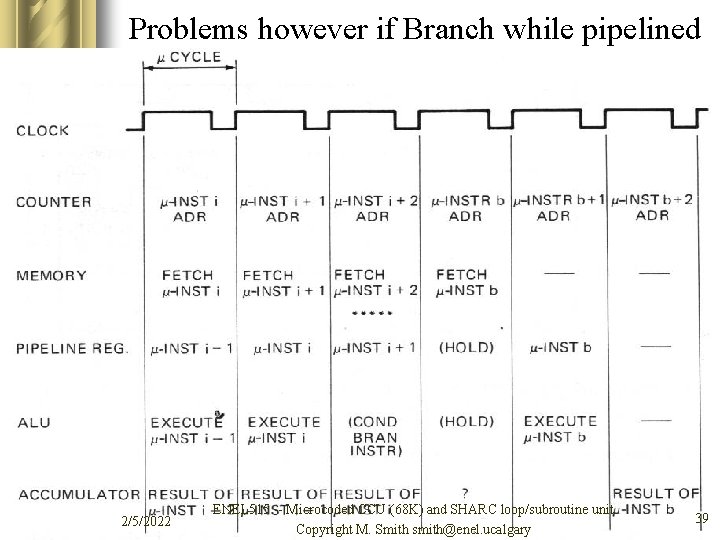

Problems however if Branch while pipelined 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 39

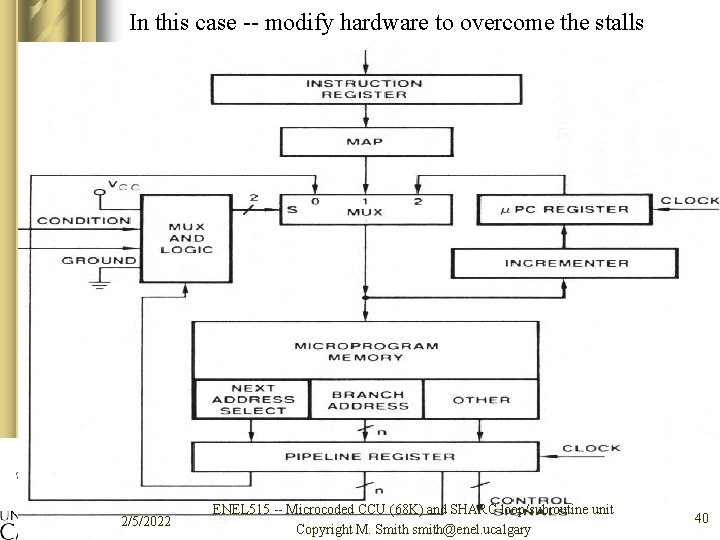

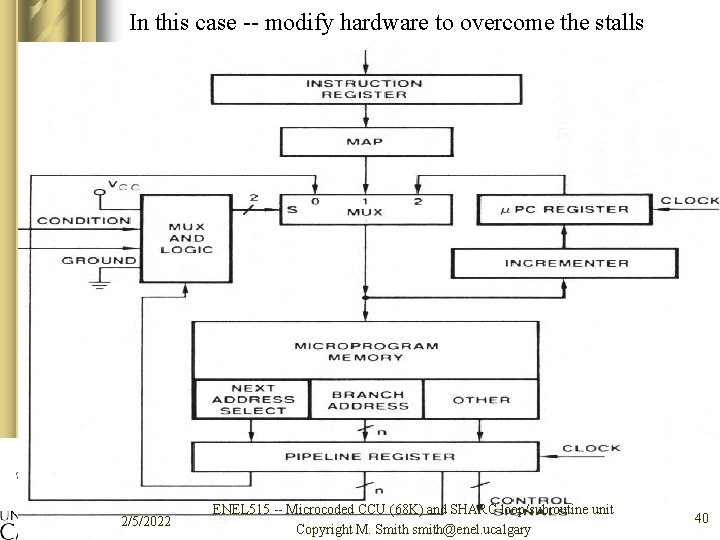

In this case -- modify hardware to overcome the stalls 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 40

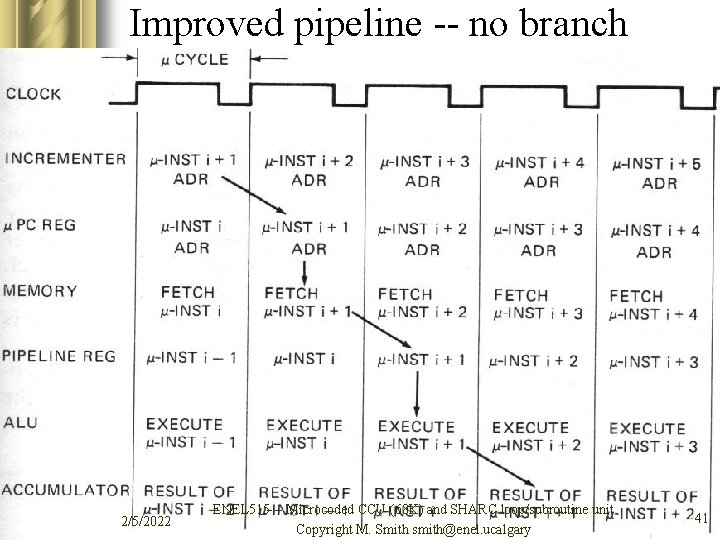

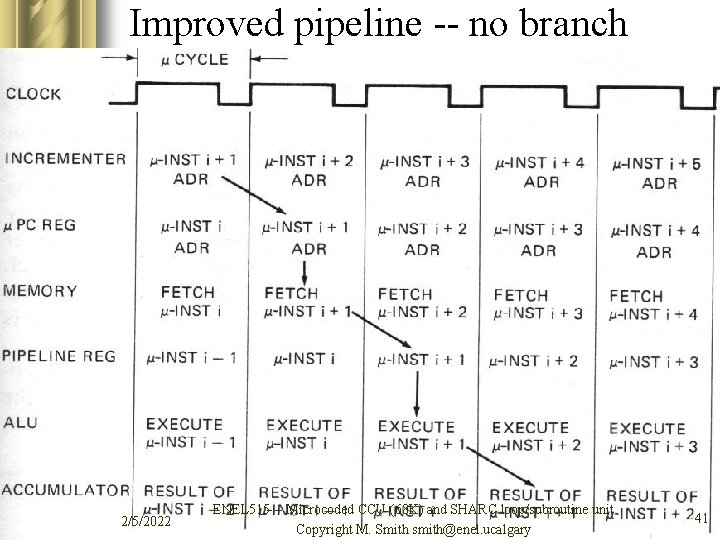

Improved pipeline -- no branch 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 41

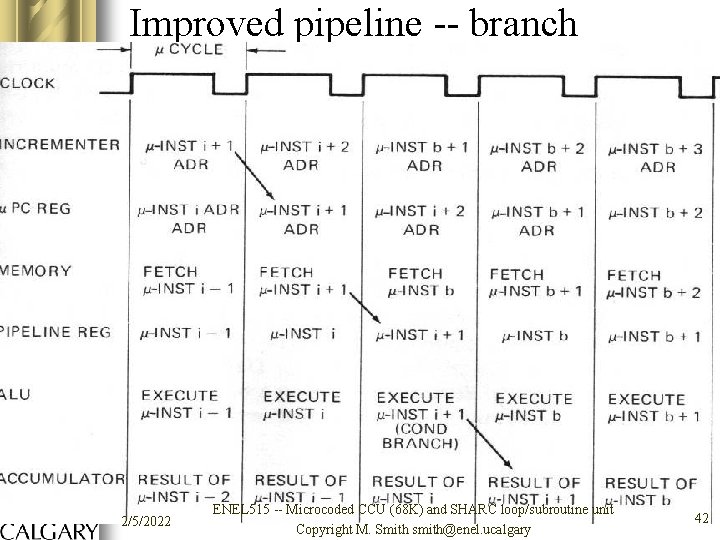

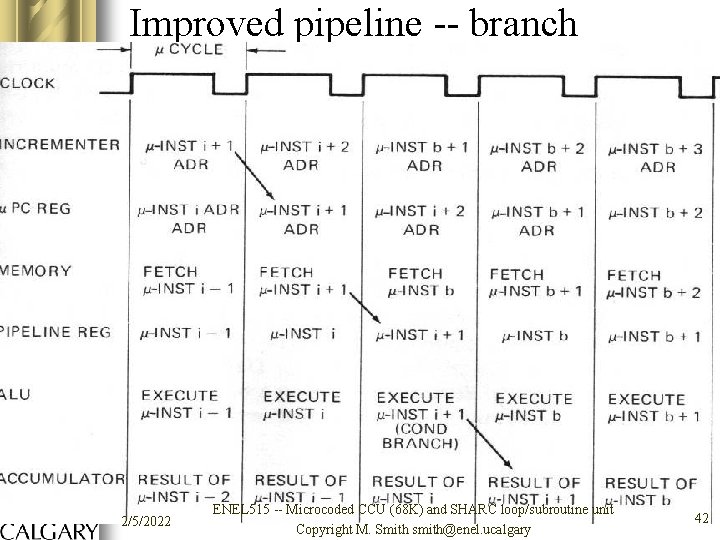

Improved pipeline -- branch 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 42

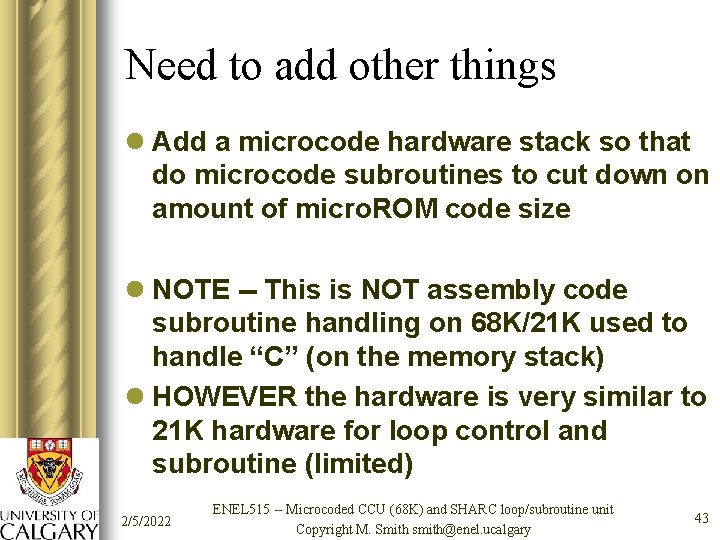

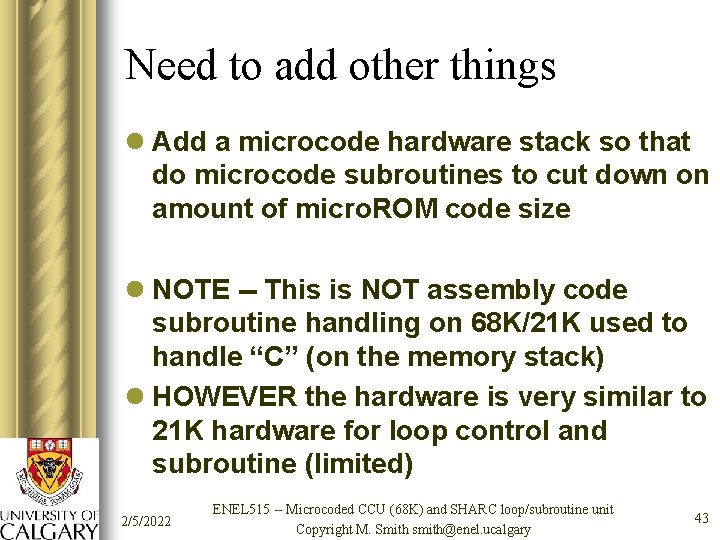

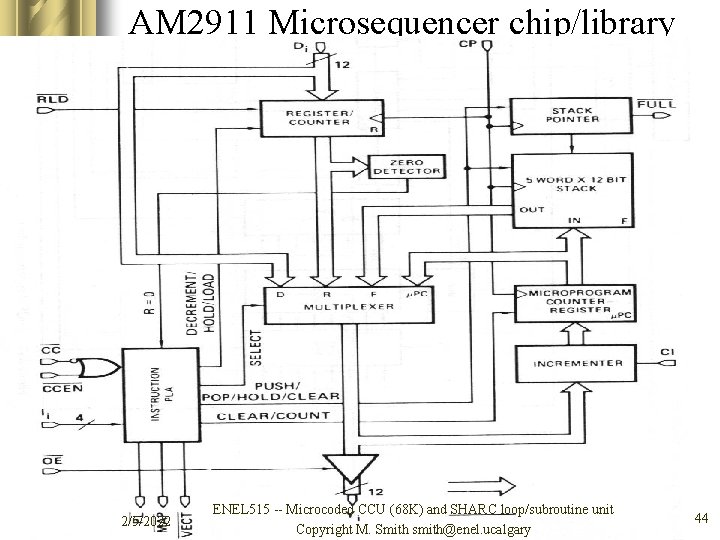

Need to add other things l Add a microcode hardware stack so that do microcode subroutines to cut down on amount of micro. ROM code size l NOTE -- This is NOT assembly code subroutine handling on 68 K/21 K used to handle “C” (on the memory stack) l HOWEVER the hardware is very similar to 21 K hardware for loop control and subroutine (limited) 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 43

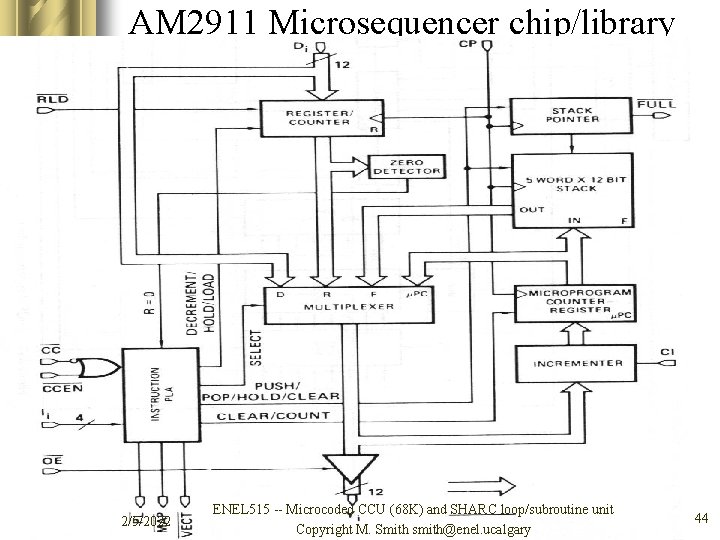

AM 2911 Microsequencer chip/library 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 44

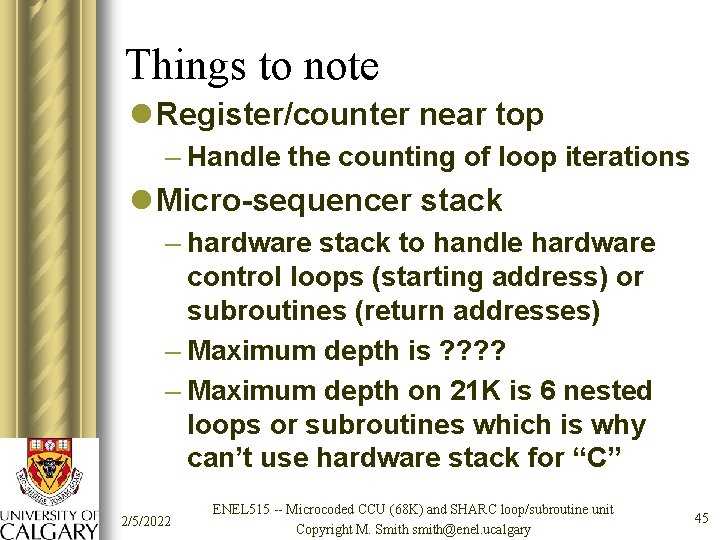

Things to note l Register/counter near top – Handle the counting of loop iterations l Micro-sequencer stack – hardware stack to handle hardware control loops (starting address) or subroutines (return addresses) – Maximum depth is ? ? – Maximum depth on 21 K is 6 nested loops or subroutines which is why can’t use hardware stack for “C” 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 45

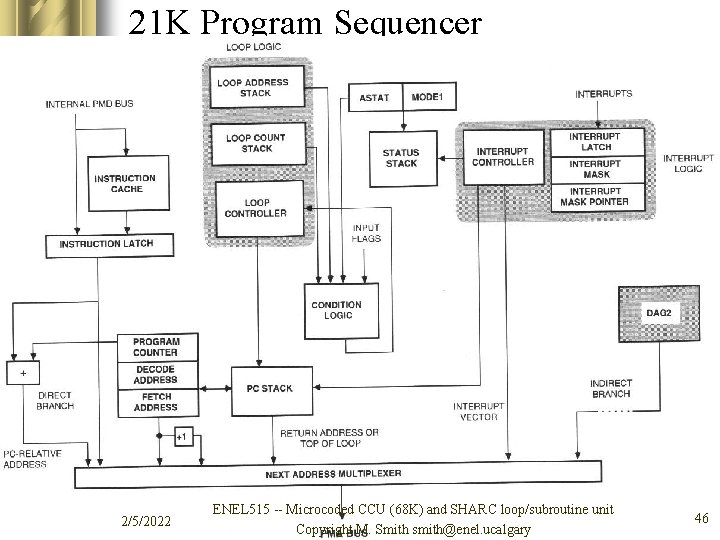

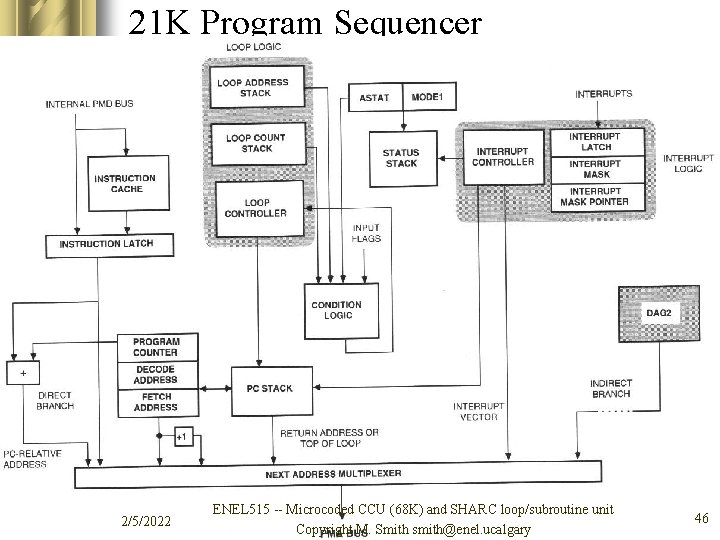

21 K Program Sequencer 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 46

Note other capabilities l Ability to handle interrupts (VECT) – Jump to special microcode l Ability to determine when to handle assembly code instructions (MAP) l Ability to manipulate and break out of microcode loops and microcode subroutines 2/5/2022 ENEL 515 -- Microcoded CCU (68 K) and SHARC loop/subroutine unit Copyright M. Smith smith@enel. ucalgary 47