Micro Programmed Control Chapter 8 Mano Kime Microprogrammed

![Sample Instructions and Program ADI DR, SA, I Op-code 1000010 R[DR] R[SA] +zf I(2: Sample Instructions and Program ADI DR, SA, I Op-code 1000010 R[DR] R[SA] +zf I(2:](https://slidetodoc.com/presentation_image/16d28367b1b48a2abe25b7309559f0f6/image-25.jpg)

- Slides: 44

Micro. Programmed Control Chapter 8 (Mano & Kime)

Microprogrammed Control • A control with its binary control values stored as words in memory is called a microprogrammed control. • Each word is a microinstruction that contains one or more microoperations. • A sequence of microinstructions constitute a microprogram.

Microprogrammed Control • Microprograms are stored in ROMs. • The content of a word at a given address specify the microoperations to be performed for both the data path and the control unit. • The memory in the control unit is called control memory (ROM) or writable control memory (RAM).

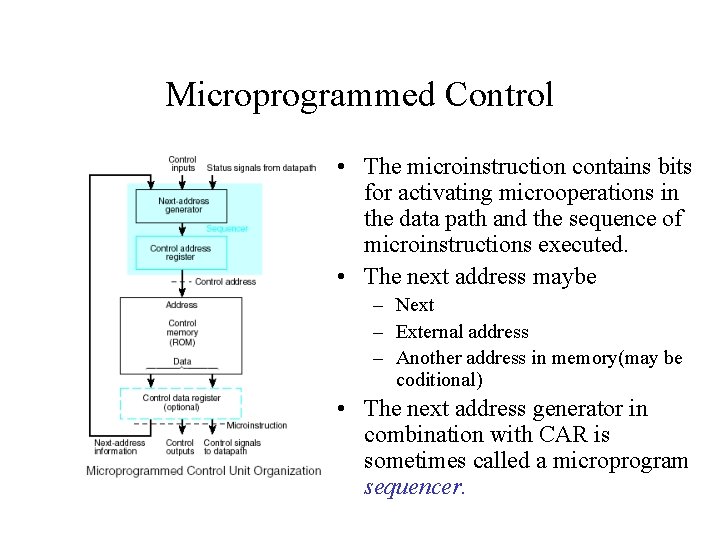

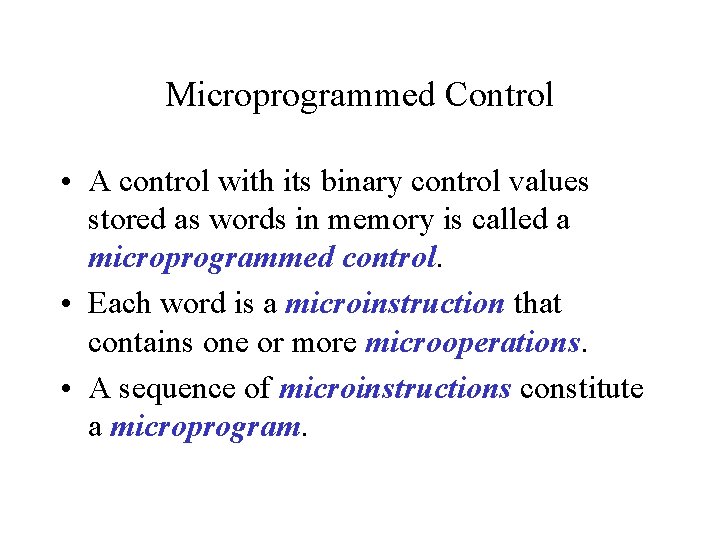

Microprogrammed Control • The microinstruction contains bits for activating microoperations in the data path and the sequence of microinstructions executed. • The next address maybe – Next – External address – Another address in memory(may be coditional) • The next address generator in combination with CAR is sometimes called a microprogram sequencer.

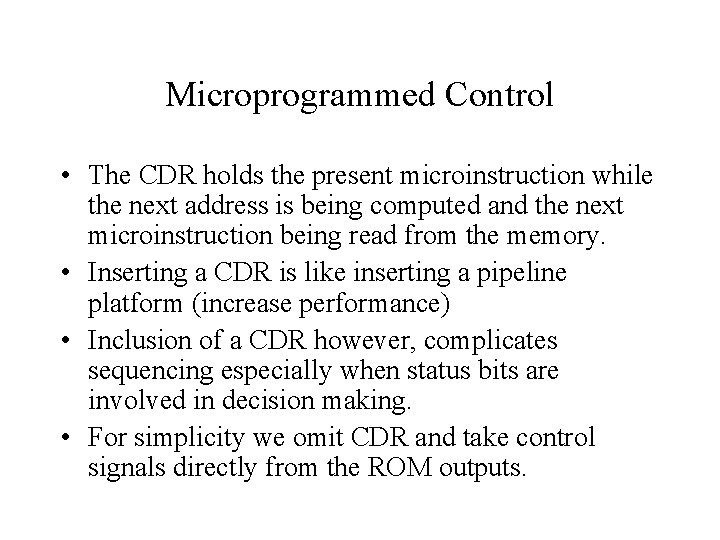

Microprogrammed Control • The CDR holds the present microinstruction while the next address is being computed and the next microinstruction being read from the memory. • Inserting a CDR is like inserting a pipeline platform (increase performance) • Inclusion of a CDR however, complicates sequencing especially when status bits are involved in decision making. • For simplicity we omit CDR and take control signals directly from the ROM outputs.

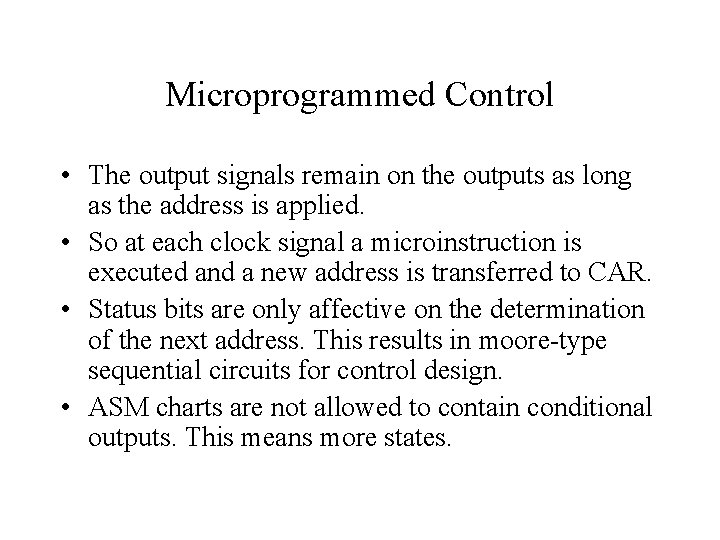

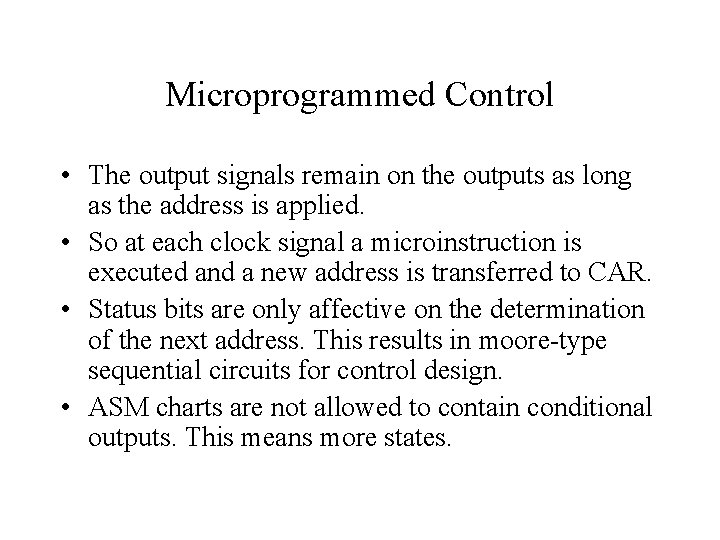

Microprogrammed Control • The output signals remain on the outputs as long as the address is applied. • So at each clock signal a microinstruction is executed and a new address is transferred to CAR. • Status bits are only affective on the determination of the next address. This results in moore-type sequential circuits for control design. • ASM charts are not allowed to contain conditional outputs. This means more states.

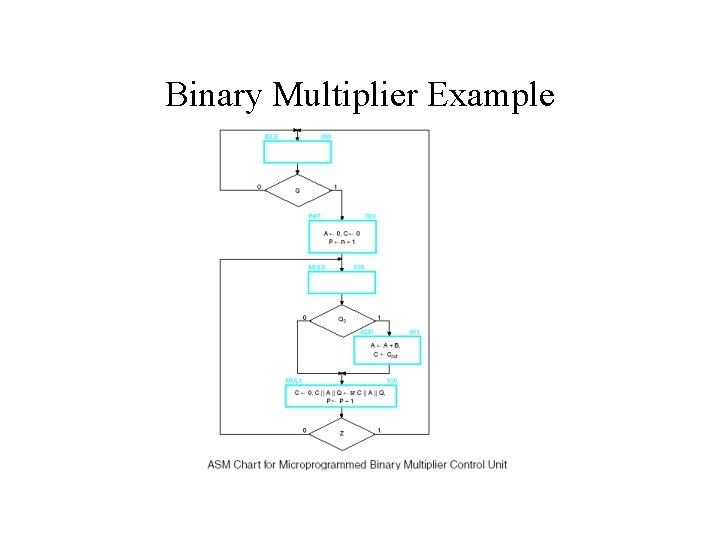

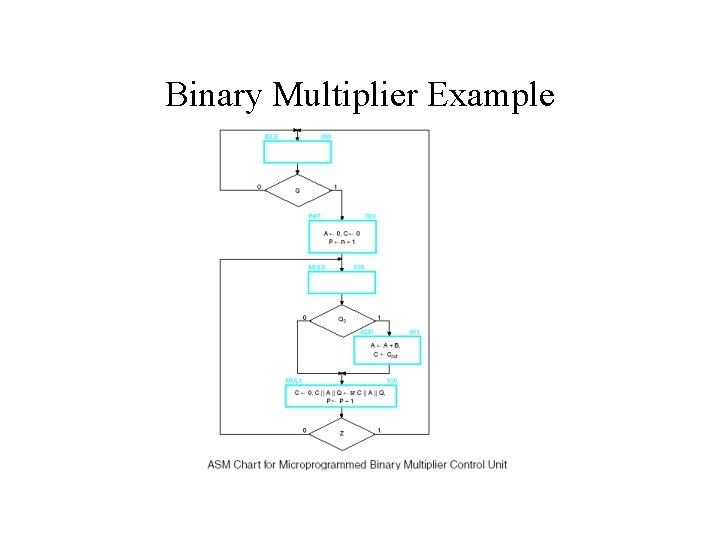

Binary Multiplier Example

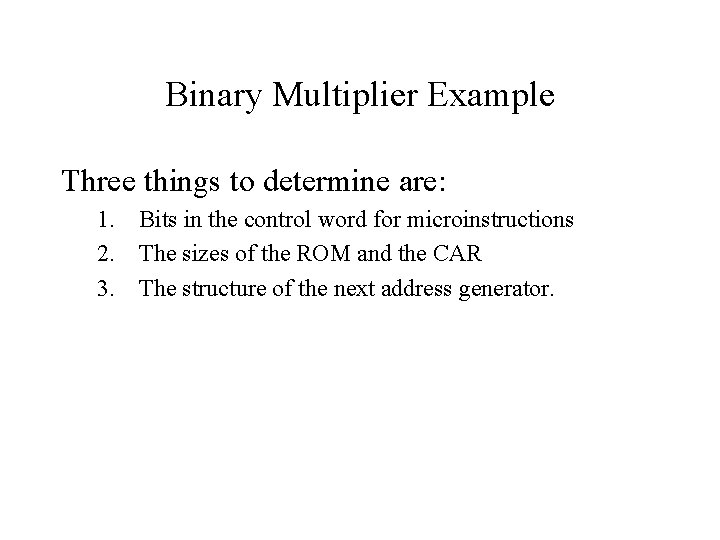

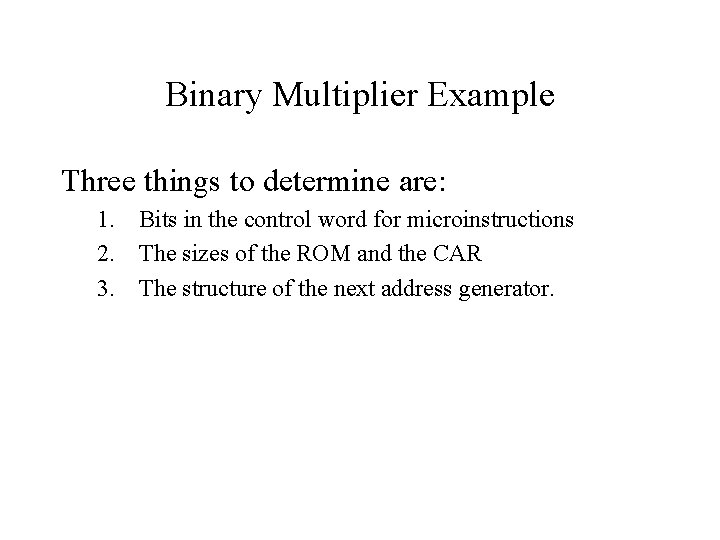

Binary Multiplier Example Three things to determine are: 1. Bits in the control word for microinstructions 2. The sizes of the ROM and the CAR 3. The structure of the next address generator.

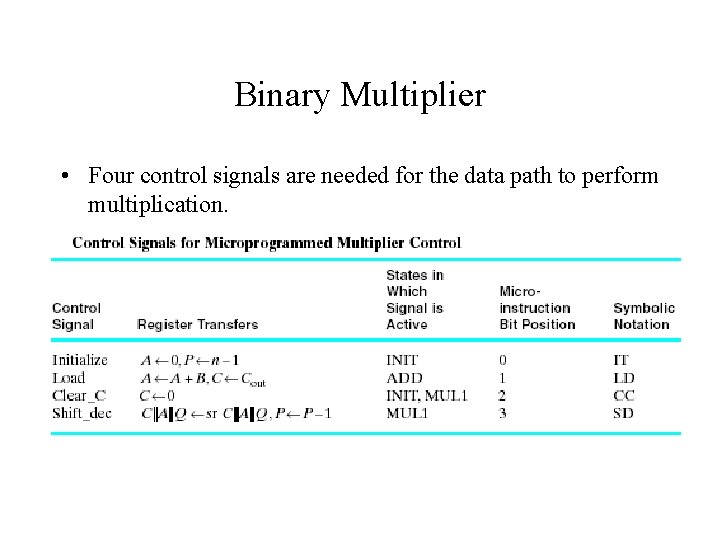

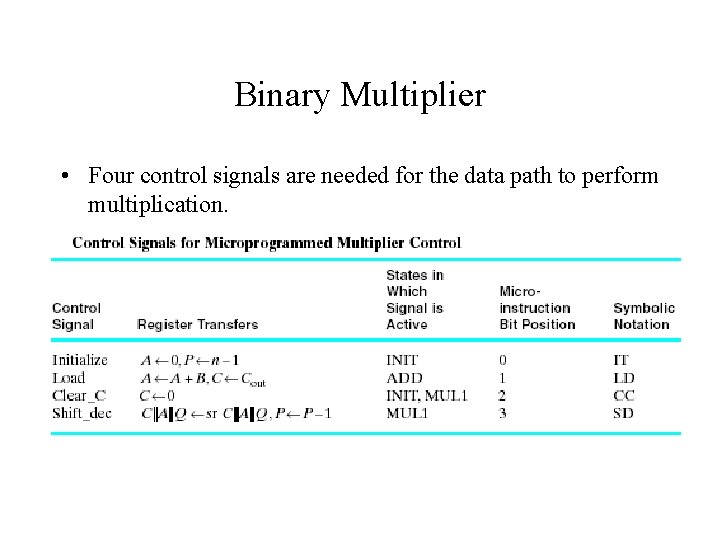

Binary Multiplier • Four control signals are needed for the data path to perform multiplication.

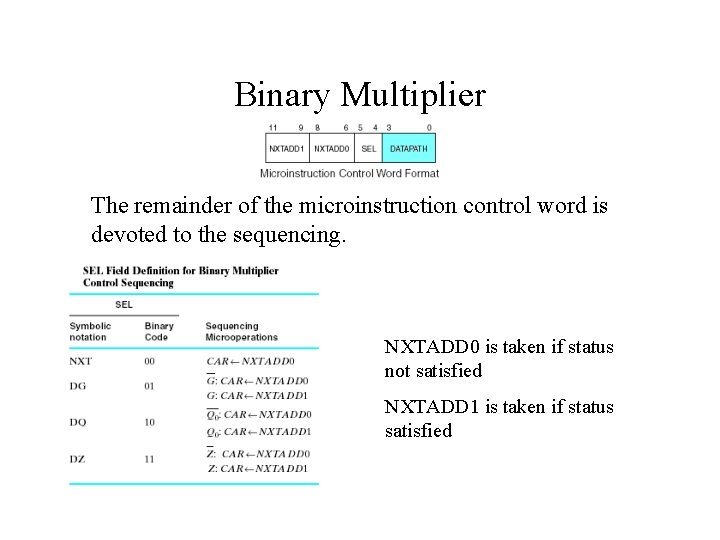

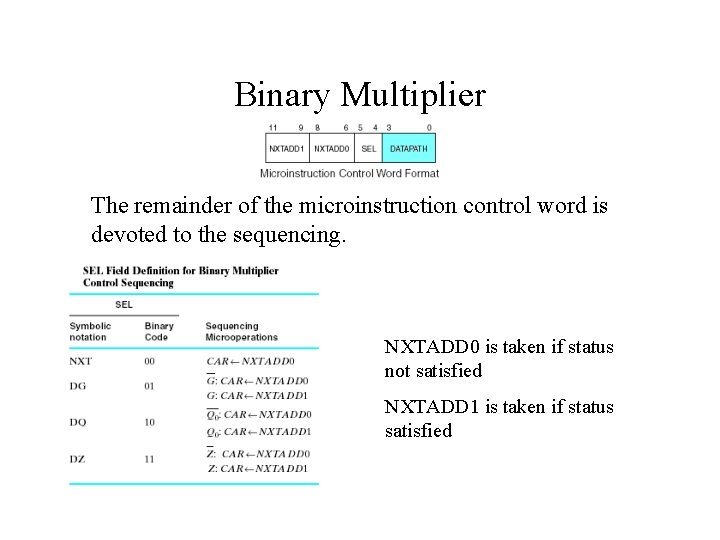

Binary Multiplier The remainder of the microinstruction control word is devoted to the sequencing. NXTADD 0 is taken if status not satisfied NXTADD 1 is taken if status satisfied

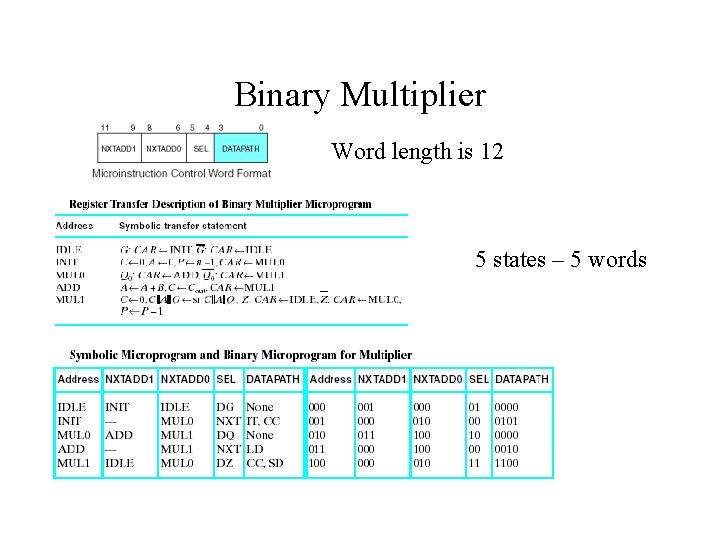

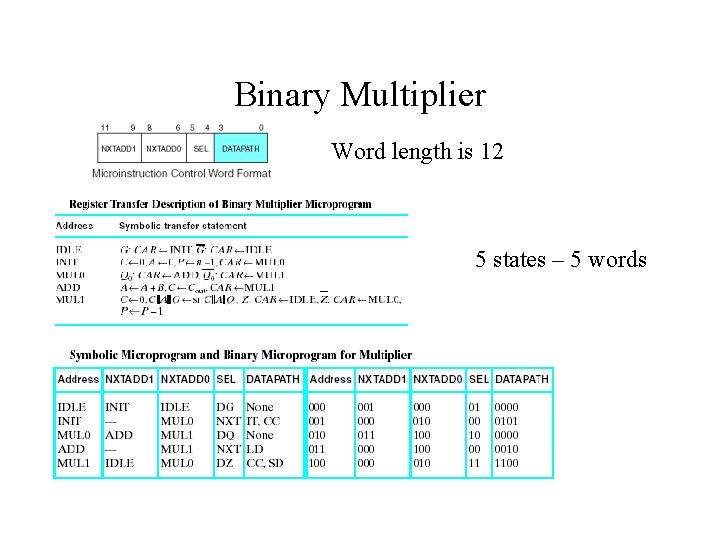

Binary Multiplier Word length is 12 5 states – 5 words

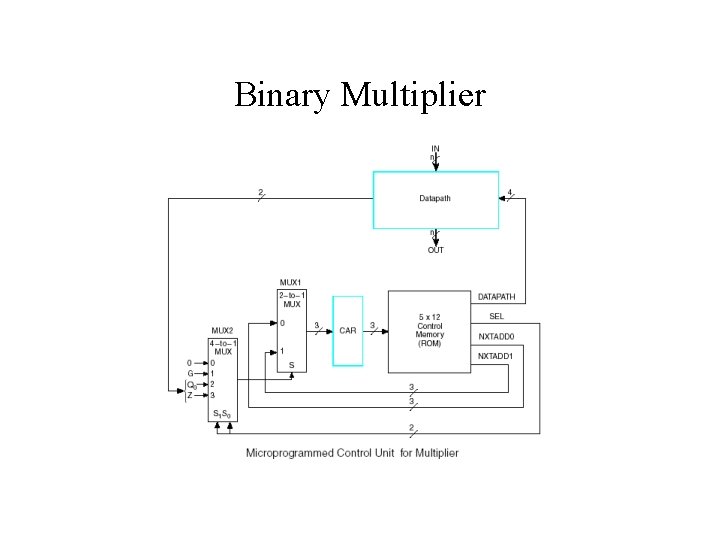

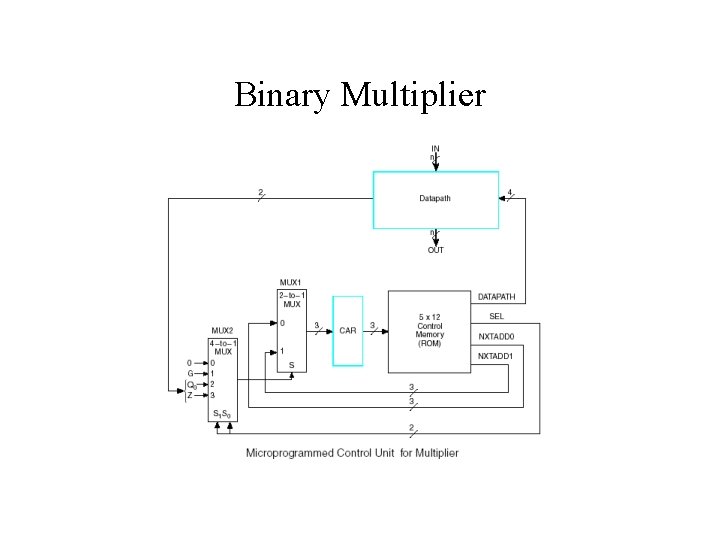

Binary Multiplier

A Simple Computer Architecture • The operations to be performed by the computer are instructed by the user. • A sequence of instructions is called a program. • An instruction is a collection of bits that instructs the computer to perform a specific operation. • The operation code, “opcode”, of an instruction is a group of bits that specifies an operation. • The collection of instructions for a computer is called an instruction set and through description of the instruction set its instruction set architecture.

A Simple Computer Architecture • The control unit fetches an instruction from memory, decodes the opcode and generates necessary control and timing signals. • For 2 m distinct operations opcode must be assigned m bits. • An instruction consits of op-code an address fields for the operands. • Address may be – explicit or – implicit.

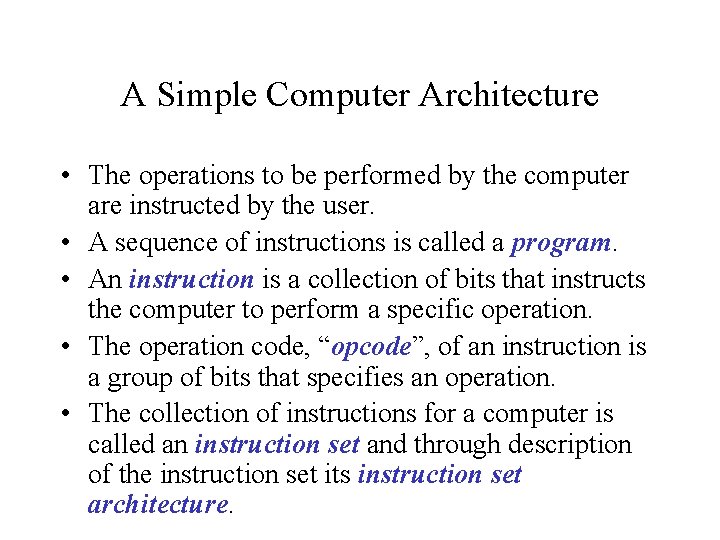

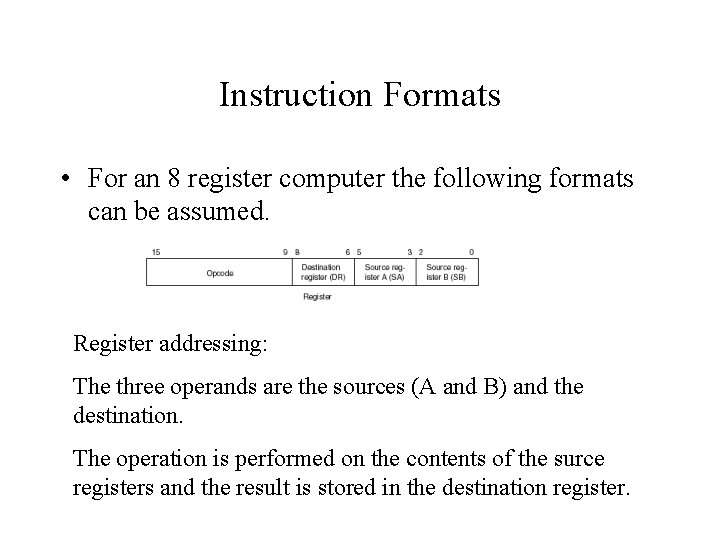

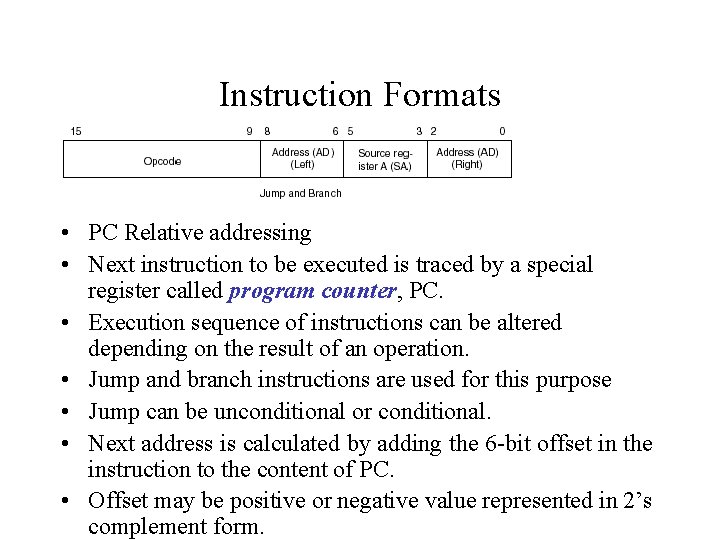

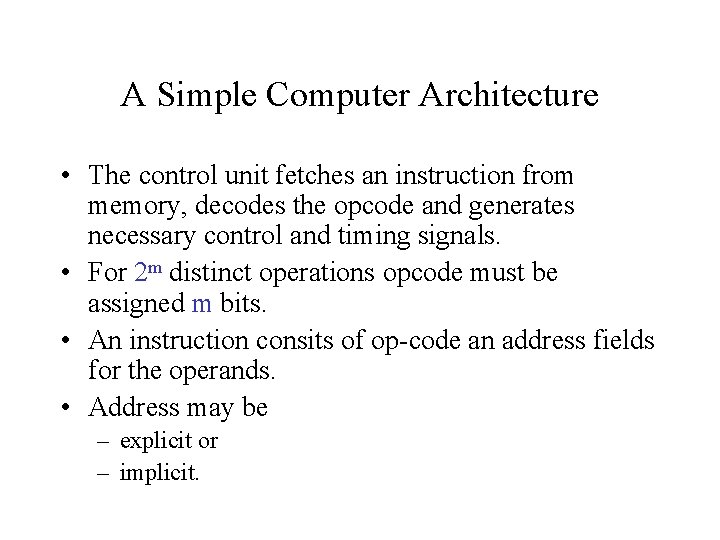

Instruction Formats • For an 8 register computer the following formats can be assumed. Register addressing: The three operands are the sources (A and B) and the destination. The operation is performed on the contents of the surce registers and the result is stored in the destination register.

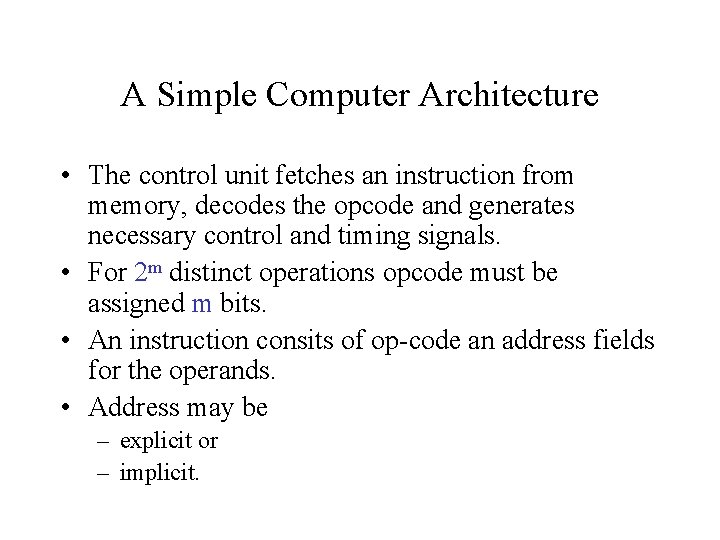

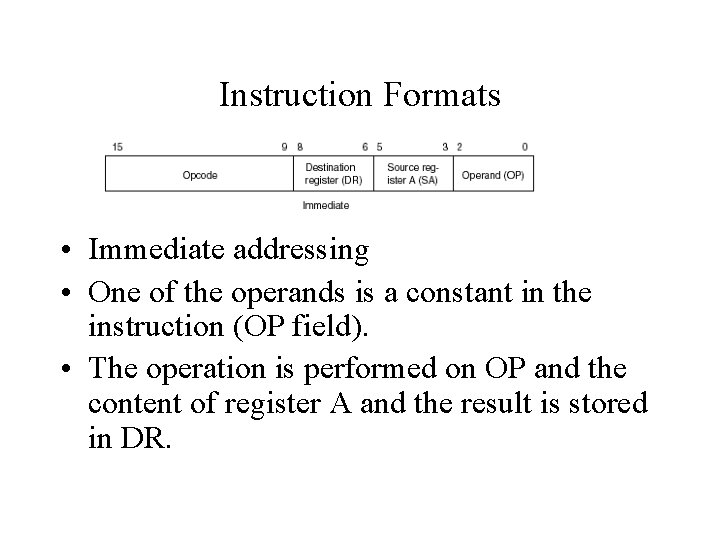

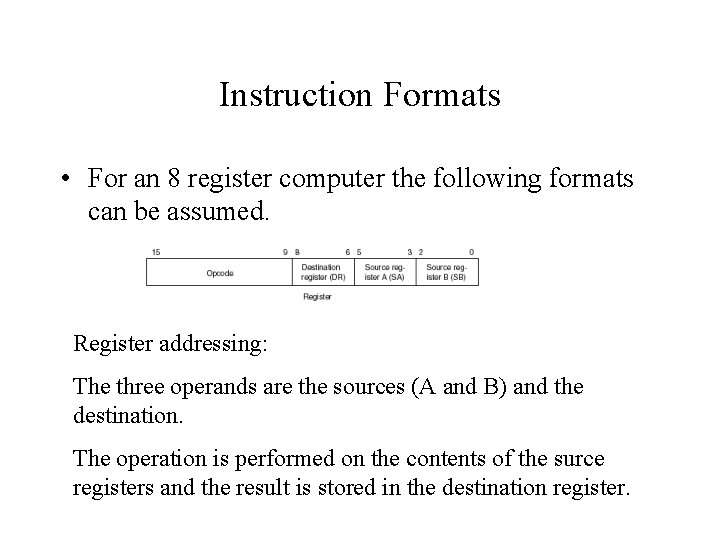

Instruction Formats • Immediate addressing • One of the operands is a constant in the instruction (OP field). • The operation is performed on OP and the content of register A and the result is stored in DR.

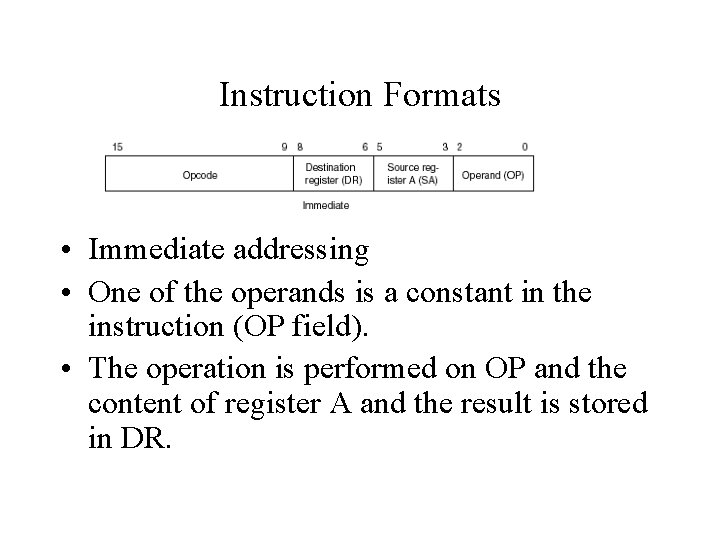

Instruction Formats • PC Relative addressing • Next instruction to be executed is traced by a special register called program counter, PC. • Execution sequence of instructions can be altered depending on the result of an operation. • Jump and branch instructions are used for this purpose • Jump can be unconditional or conditional. • Next address is calculated by adding the 6 -bit offset in the instruction to the content of PC. • Offset may be positive or negative value represented in 2’s complement form.

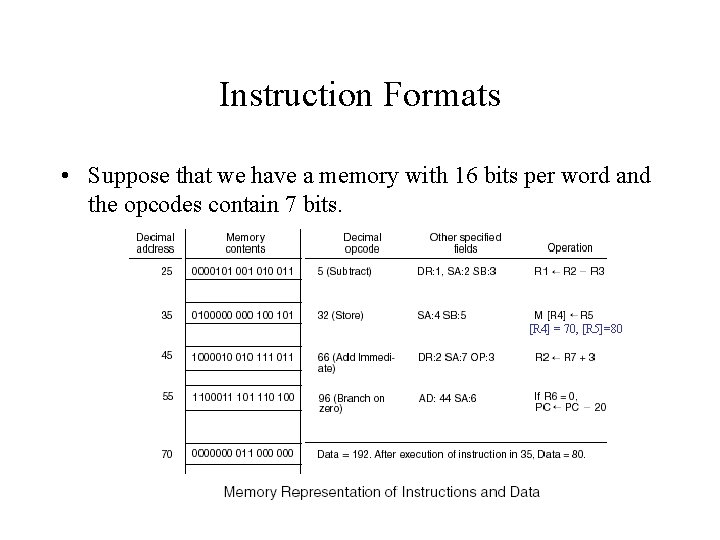

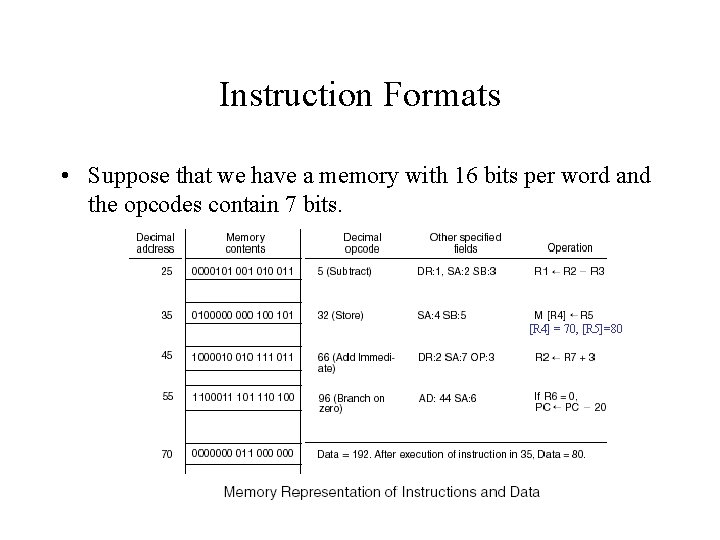

Instruction Formats • Suppose that we have a memory with 16 bits per word and the opcodes contain 7 bits. [R 4] = 70, [R 5]=80

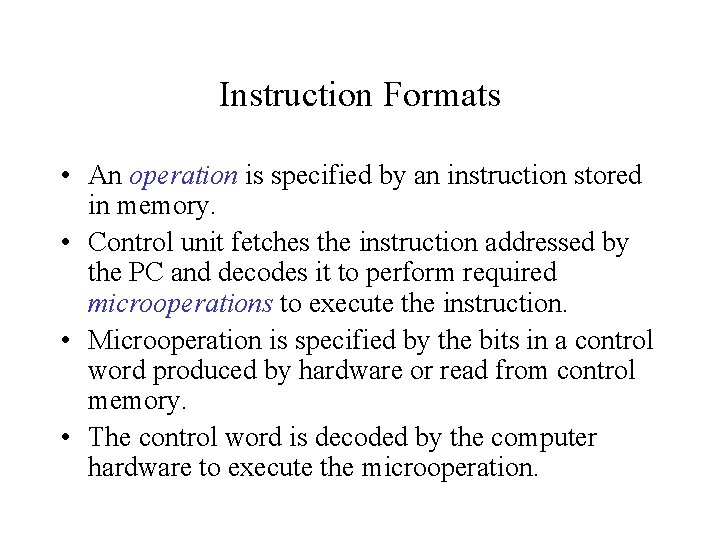

Instruction Formats • An operation is specified by an instruction stored in memory. • Control unit fetches the instruction addressed by the PC and decodes it to perform required microoperations to execute the instruction. • Microoperation is specified by the bits in a control word produced by hardware or read from control memory. • The control word is decoded by the computer hardware to execute the microoperation.

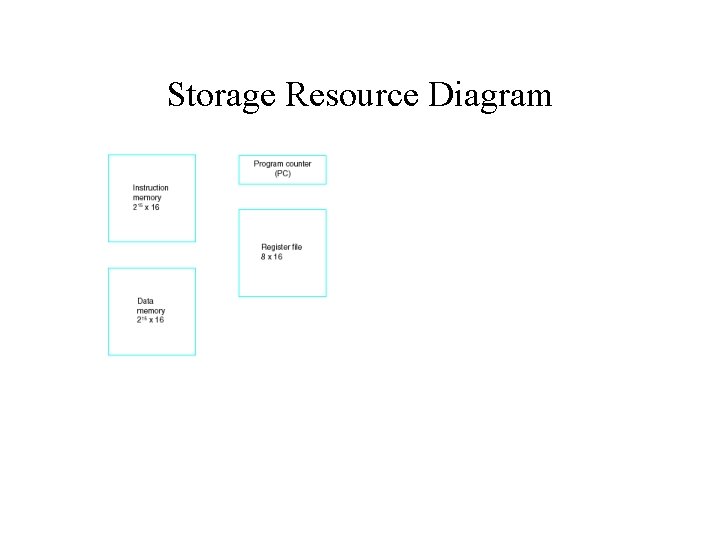

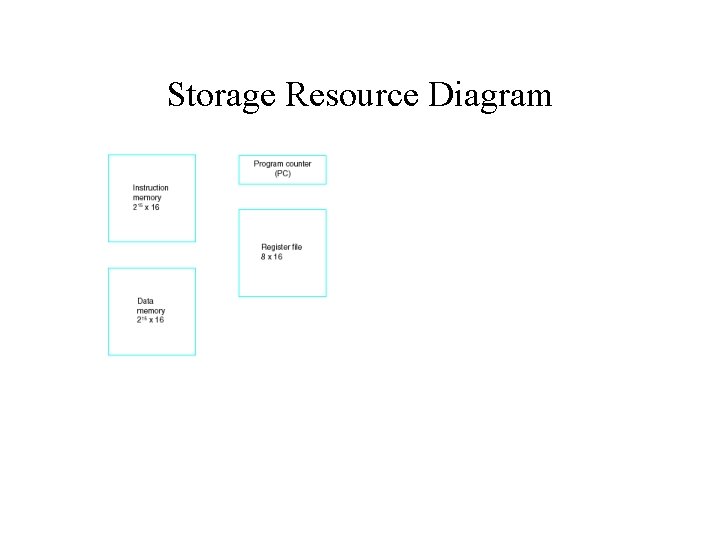

Storage Resource Diagram

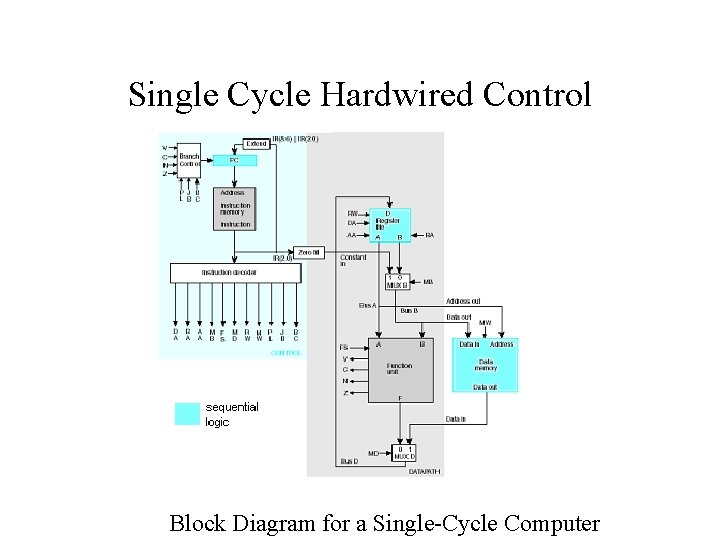

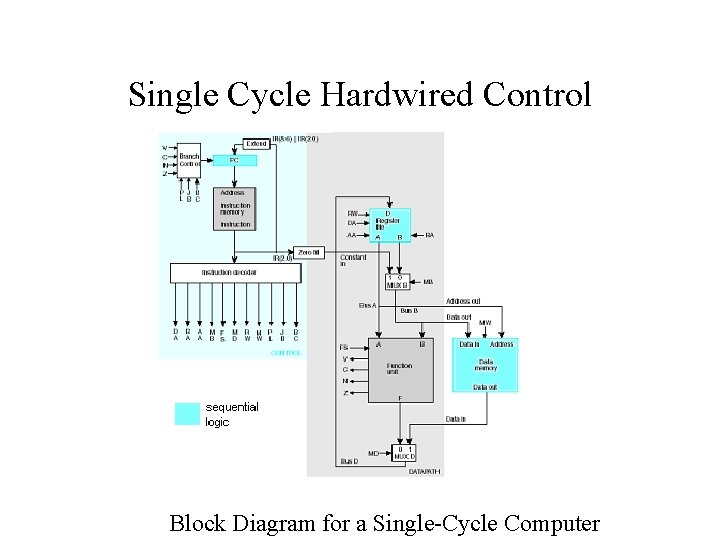

Single Cycle Hardwired Control Block Diagram for a Single-Cycle Computer

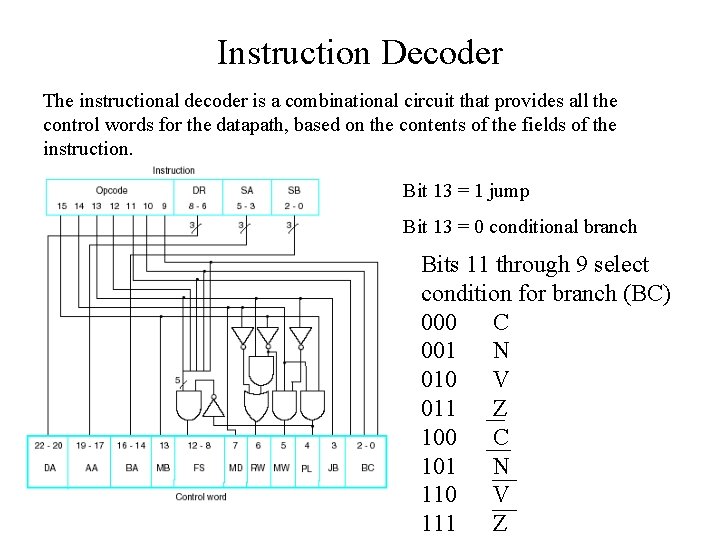

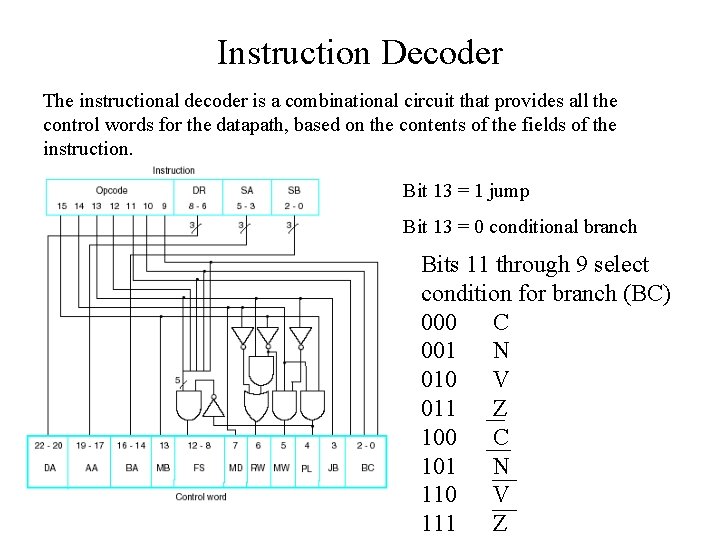

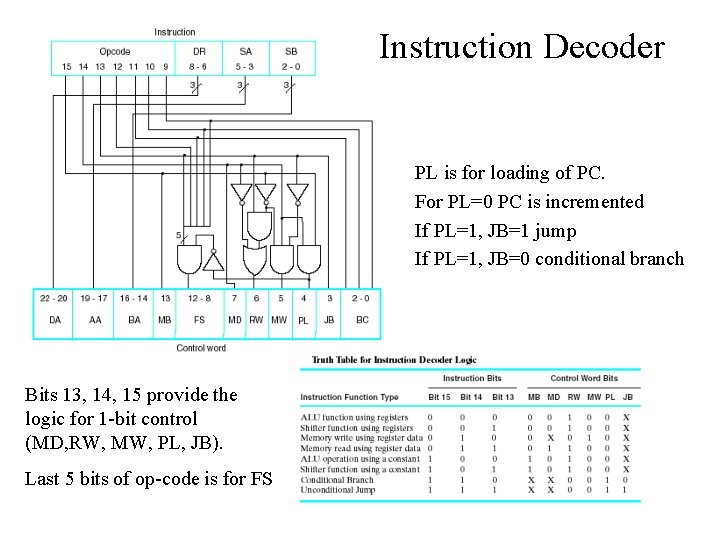

Instruction Decoder The instructional decoder is a combinational circuit that provides all the control words for the datapath, based on the contents of the fields of the instruction. Bit 13 = 1 jump Bit 13 = 0 conditional branch Bits 11 through 9 select condition for branch (BC) 000 C 001 N 010 V 011 Z 100 C 101 N 110 V 111 Z

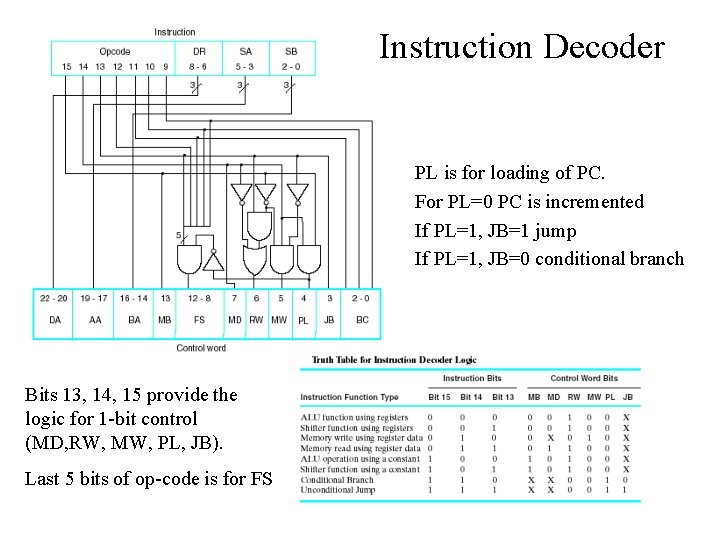

Instruction Decoder PL is for loading of PC. For PL=0 PC is incremented If PL=1, JB=1 jump If PL=1, JB=0 conditional branch Bits 13, 14, 15 provide the logic for 1 -bit control (MD, RW, MW, PL, JB). Last 5 bits of op-code is for FS

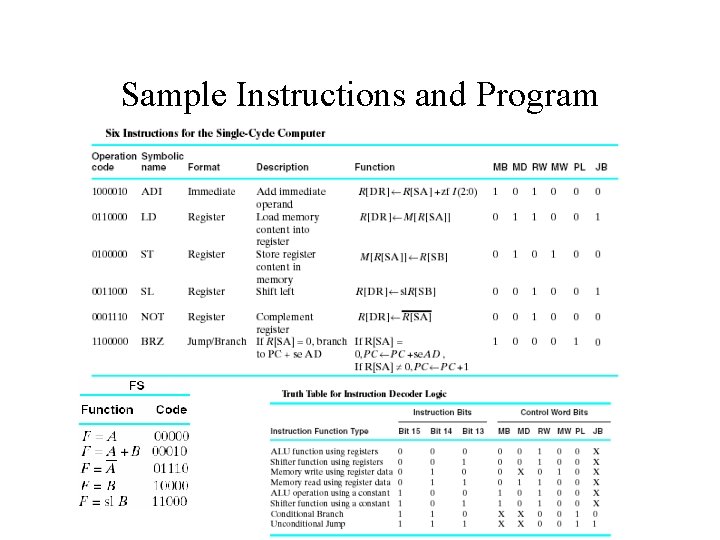

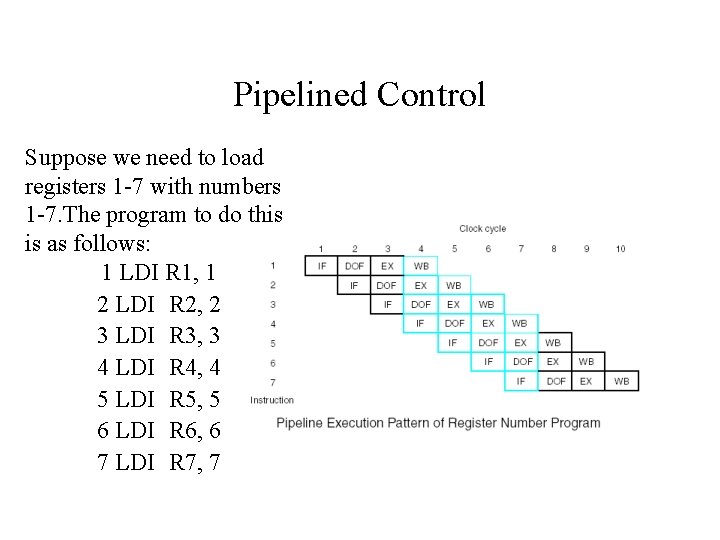

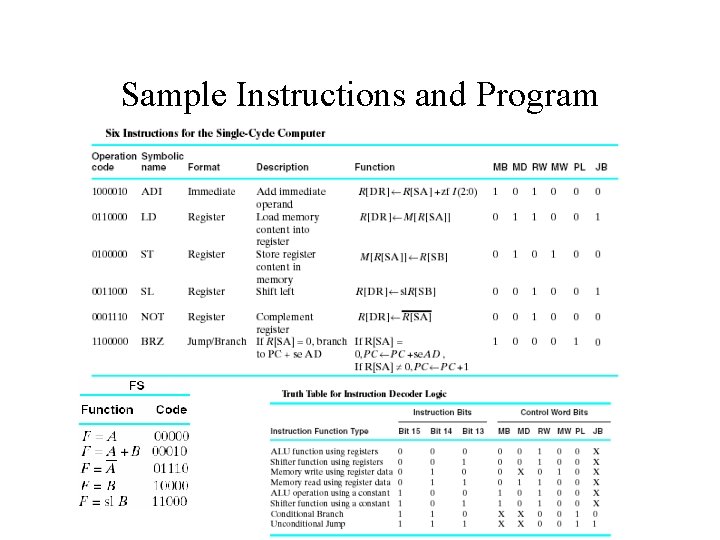

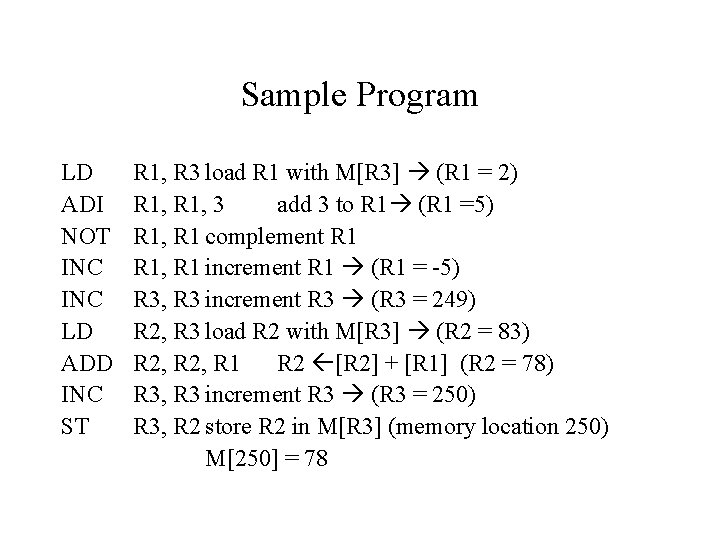

Sample Instructions and Program

![Sample Instructions and Program ADI DR SA I Opcode 1000010 RDR RSA zf I2 Sample Instructions and Program ADI DR, SA, I Op-code 1000010 R[DR] R[SA] +zf I(2:](https://slidetodoc.com/presentation_image/16d28367b1b48a2abe25b7309559f0f6/image-25.jpg)

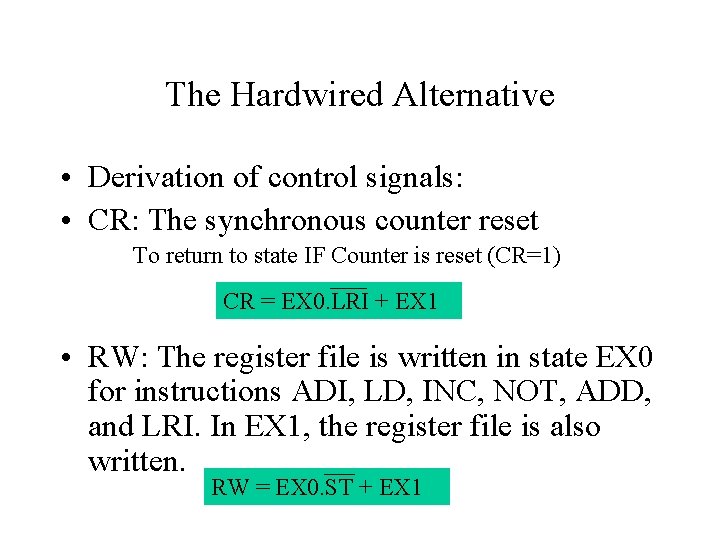

Sample Instructions and Program ADI DR, SA, I Op-code 1000010 R[DR] R[SA] +zf I(2: 0) MB MD RW MW PL JB 1 0 0 X MB is 1 constant is selected for B bus Op-code 1000010 FS for add (A (source reg) + B (zerofilled const. ) MD is 0 function unit output is selected for D bus RW is 1 D bus is written into DR register MW is 0 no write into memory At the beginning of next cycle DR is written and PC is incremented.

Sample Program Assume that R 3 contains 248, location 248 in memory contains 2, location 249 in memory contains 83 the result is to be placed in memory location 250 program that accomplishes the arithmetic expression 83 – (2 + 3) is as follows:

Sample Program LD ADI NOT INC LD ADD INC ST R 1, R 3 load R 1 with M[R 3] (R 1 = 2) R 1, 3 add 3 to R 1 (R 1 =5) R 1, R 1 complement R 1, R 1 increment R 1 (R 1 = -5) R 3, R 3 increment R 3 (R 3 = 249) R 2, R 3 load R 2 with M[R 3] (R 2 = 83) R 2, R 1 R 2 [R 2] + [R 1] (R 2 = 78) R 3, R 3 increment R 3 (R 3 = 250) R 3, R 2 store R 2 in M[R 3] (memory location 250) M[250] = 78

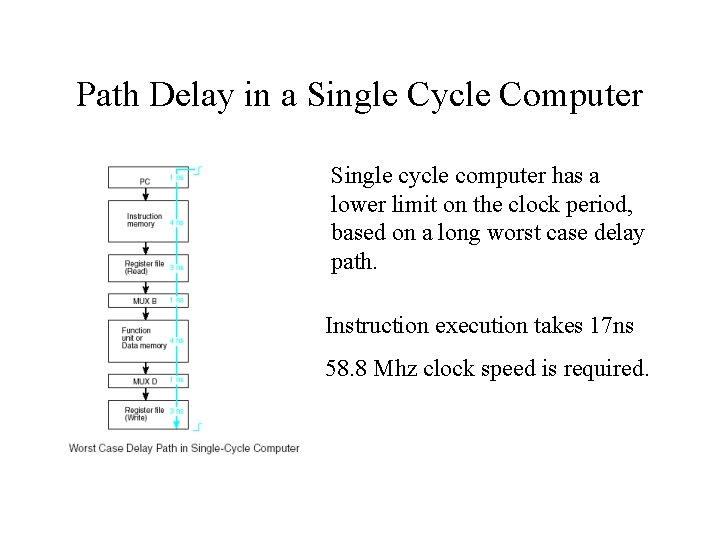

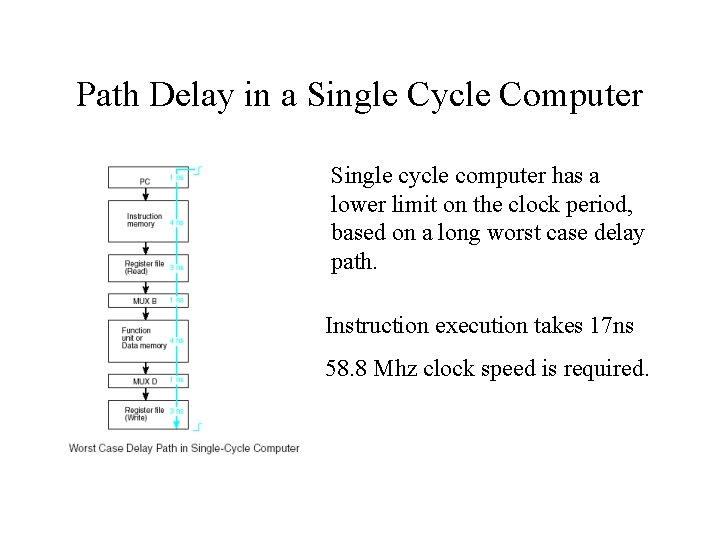

Path Delay in a Single Cycle Computer Single cycle computer has a lower limit on the clock period, based on a long worst case delay path. Instruction execution takes 17 ns 58. 8 Mhz clock speed is required.

Single Cycle Computer • Implementation of complex instructions is not possible • If there is only one memory for both instructions and data, at least two access to memory is needed for fetching the instruction and the operand.

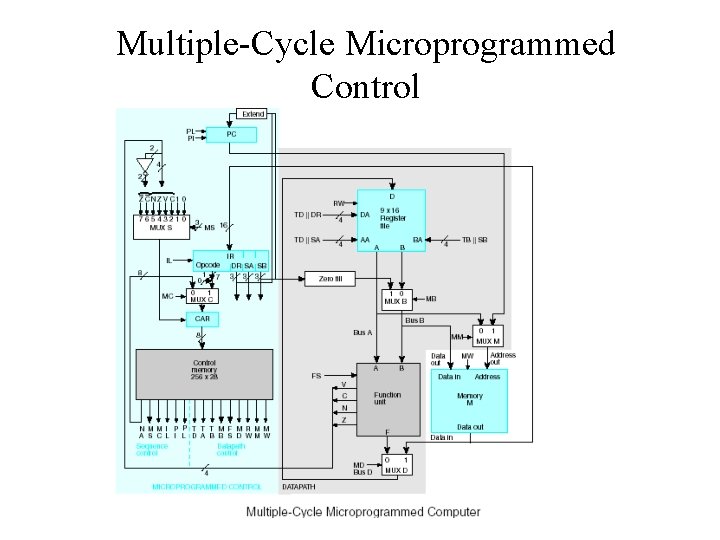

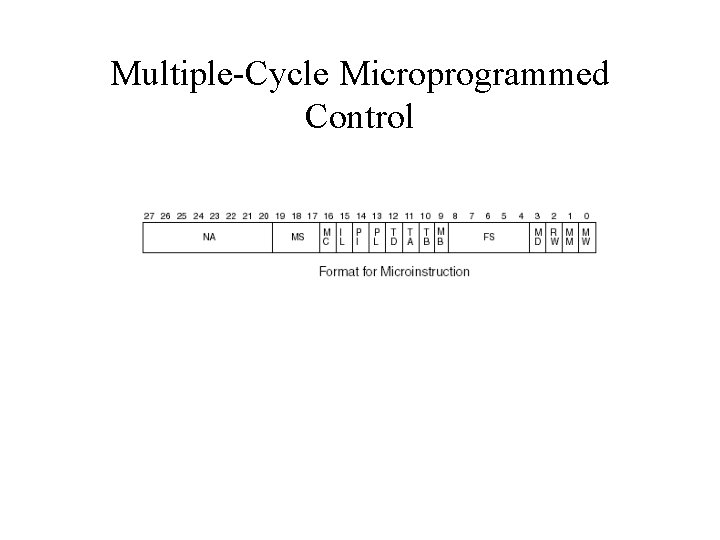

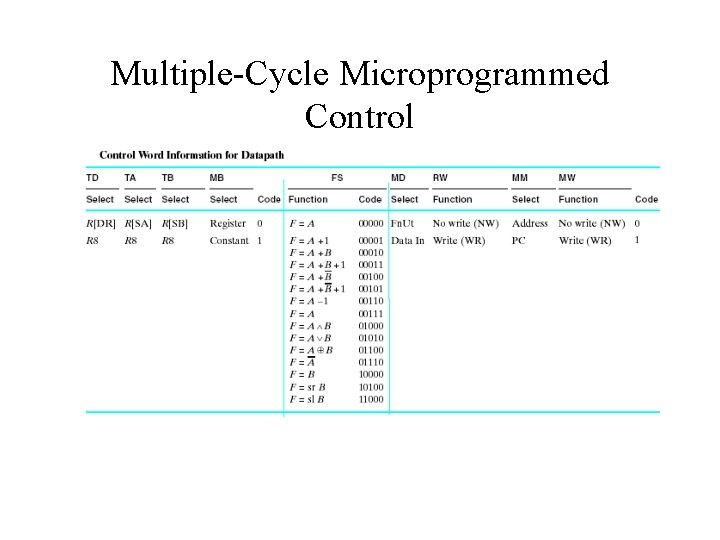

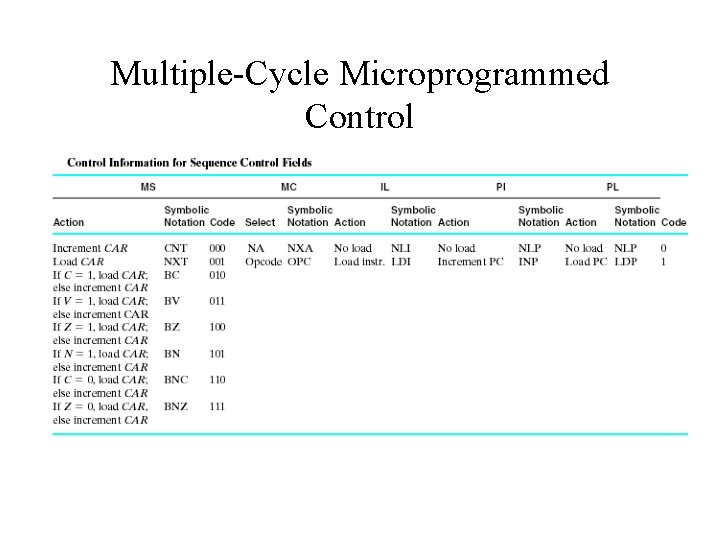

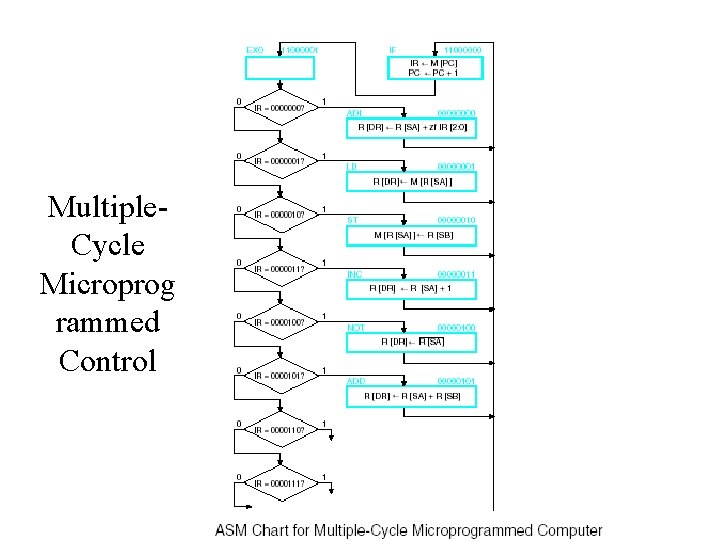

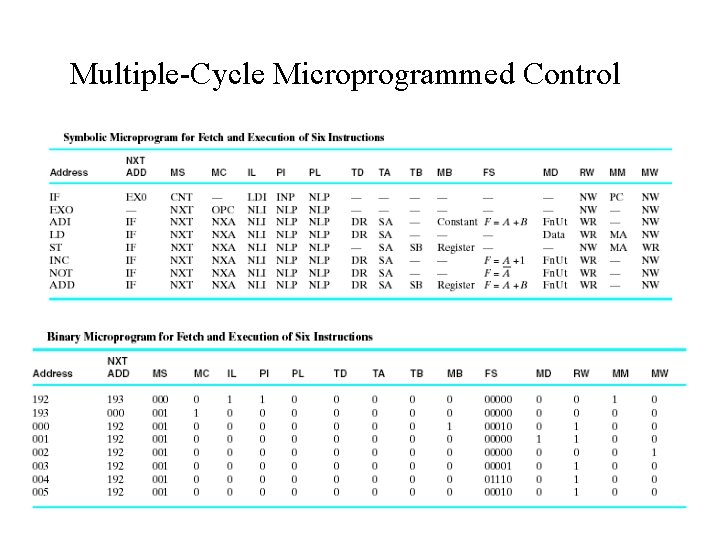

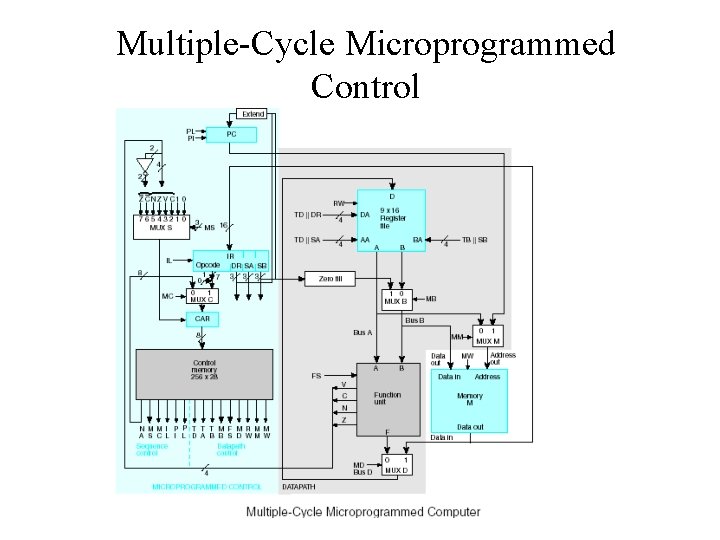

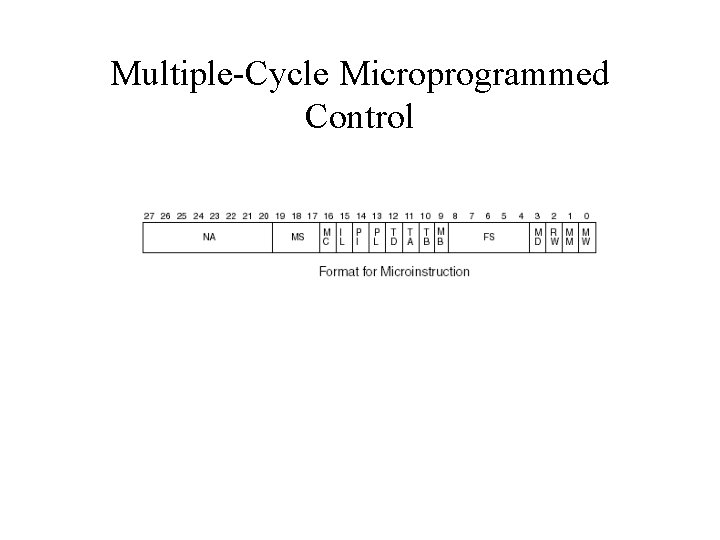

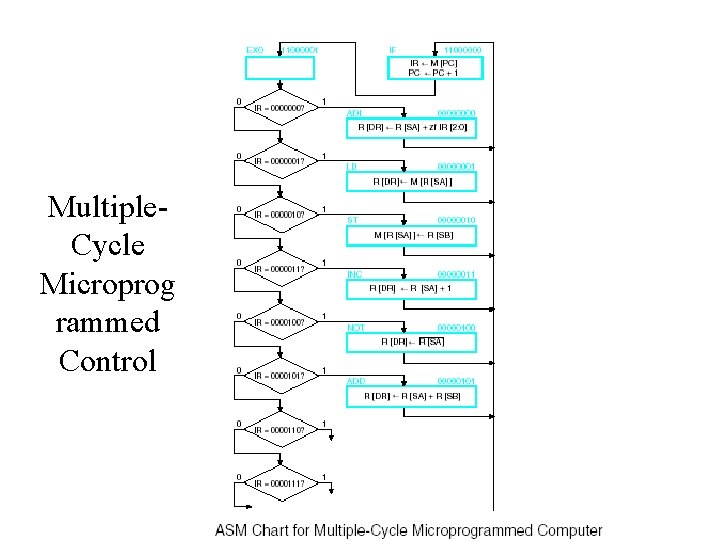

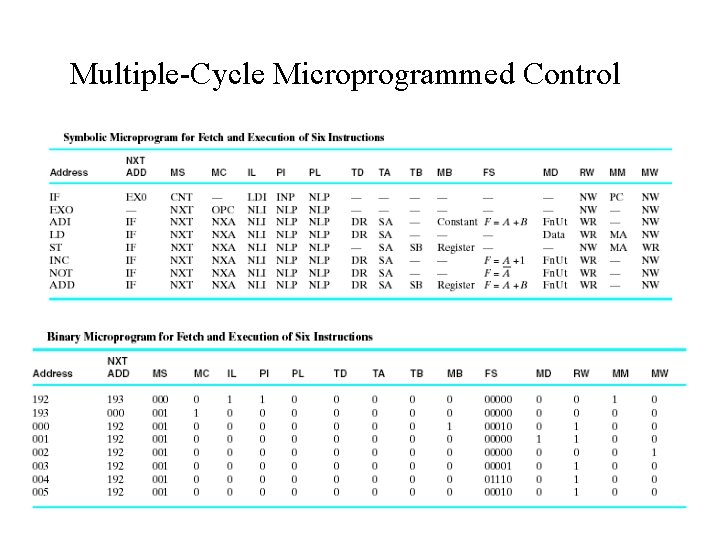

Multiple-Cycle Microprogrammed Control

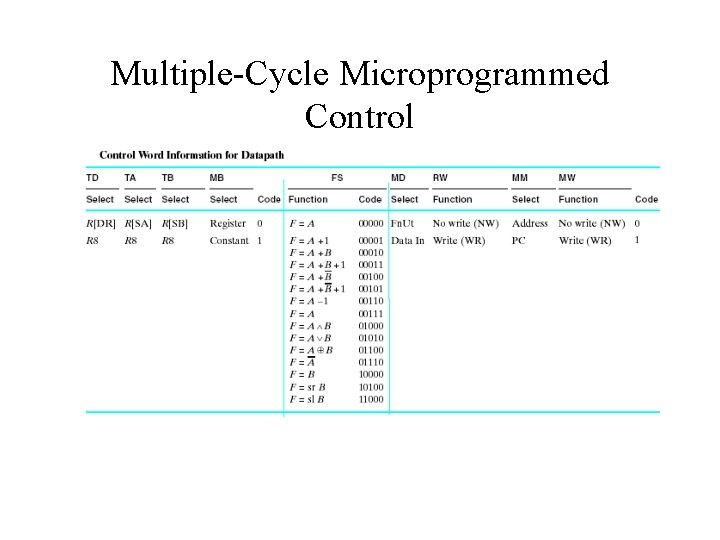

Multiple-Cycle Microprogrammed Control

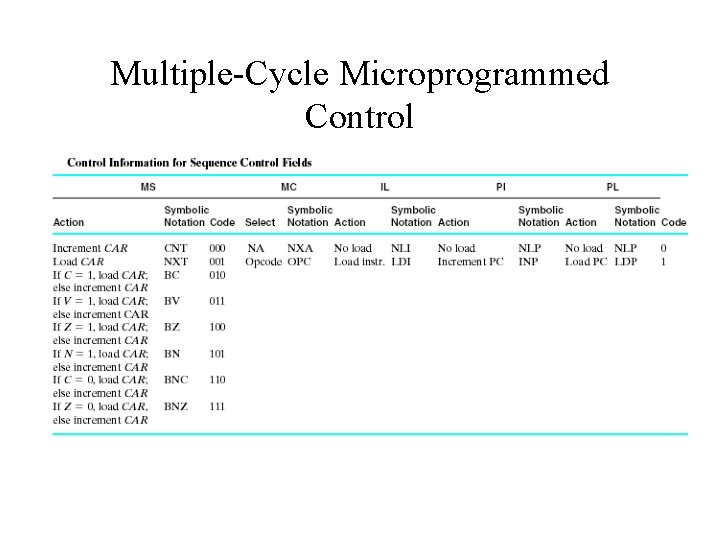

Multiple-Cycle Microprogrammed Control

Multiple-Cycle Microprogrammed Control

Multiple. Cycle Microprog rammed Control

Multiple-Cycle Microprogrammed Control

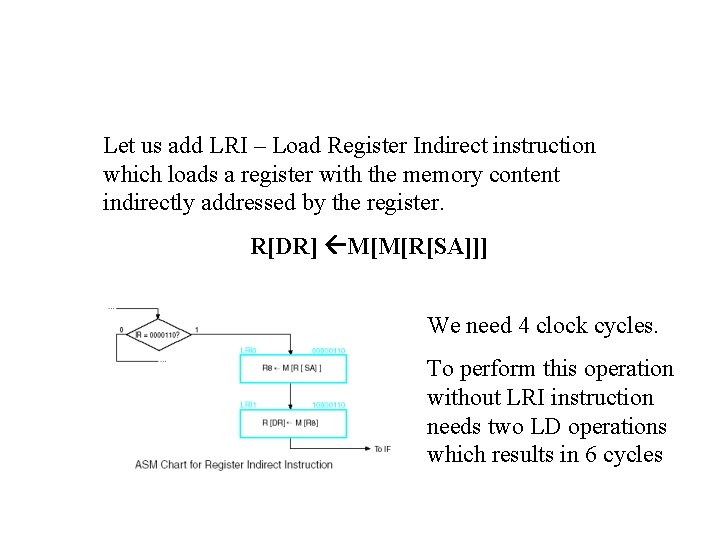

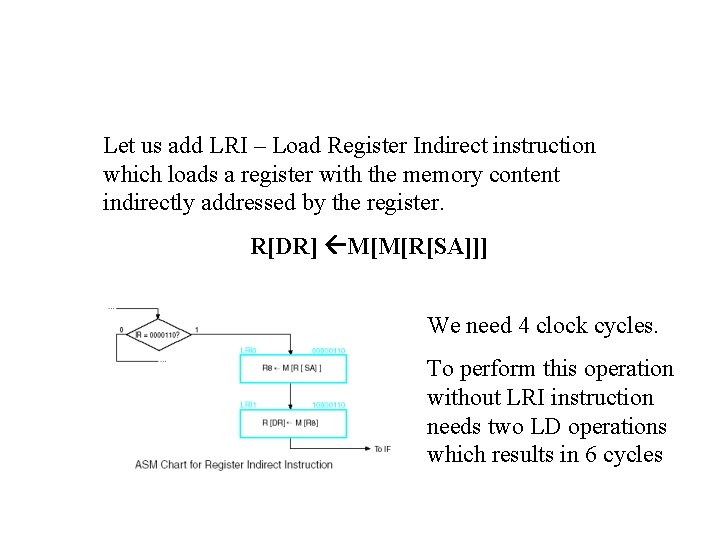

Let us add LRI – Load Register Indirect instruction which loads a register with the memory content indirectly addressed by the register. R[DR] M[M[R[SA]]] We need 4 clock cycles. To perform this operation without LRI instruction needs two LD operations which results in 6 cycles

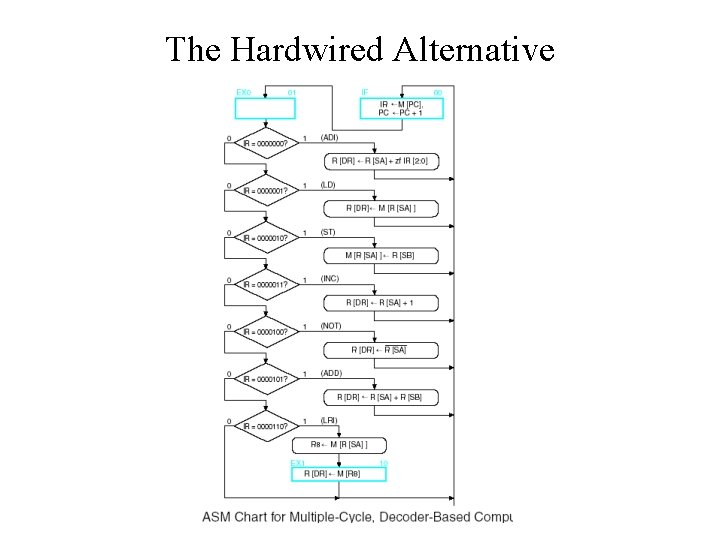

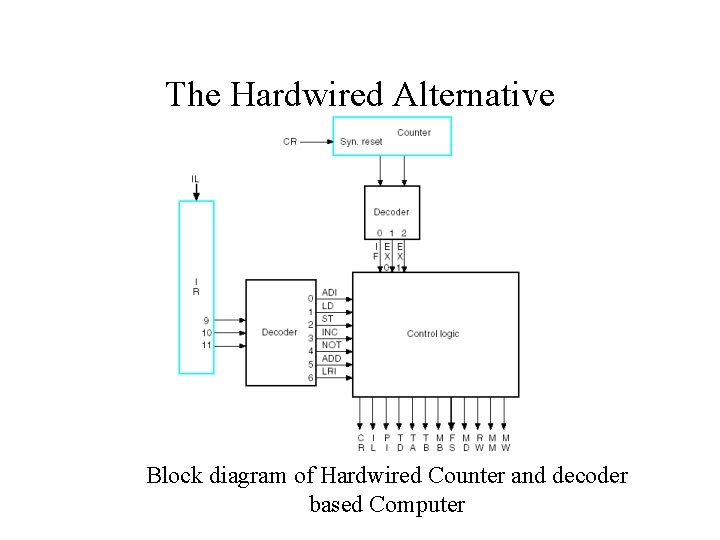

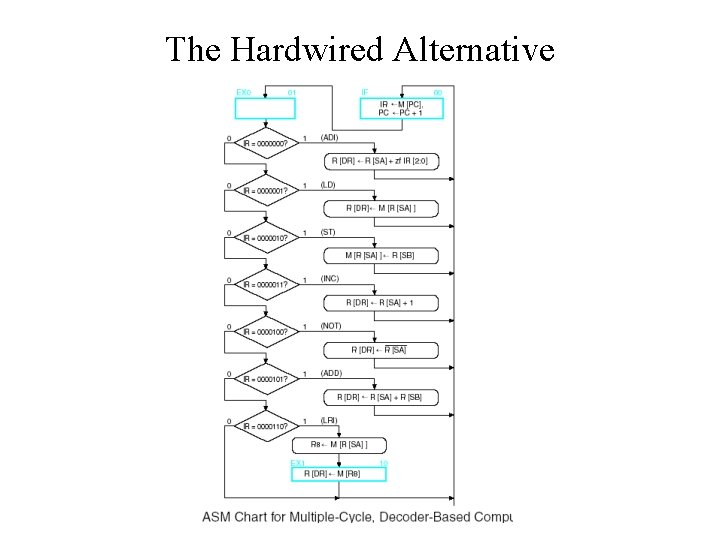

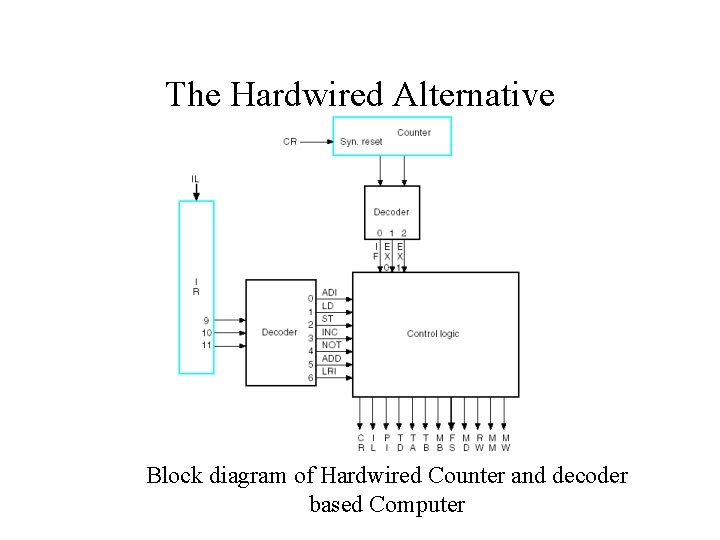

The Hardwired Alternative

The Hardwired Alternative Block diagram of Hardwired Counter and decoder based Computer

The Hardwired Alternative • Derivation of control signals: • CR: The synchronous counter reset To return to state IF Counter is reset (CR=1) CR = EX 0. LRI + EX 1 • RW: The register file is written in state EX 0 for instructions ADI, LD, INC, NOT, ADD, and LRI. In EX 1, the register file is also written. RW = EX 0. ST + EX 1

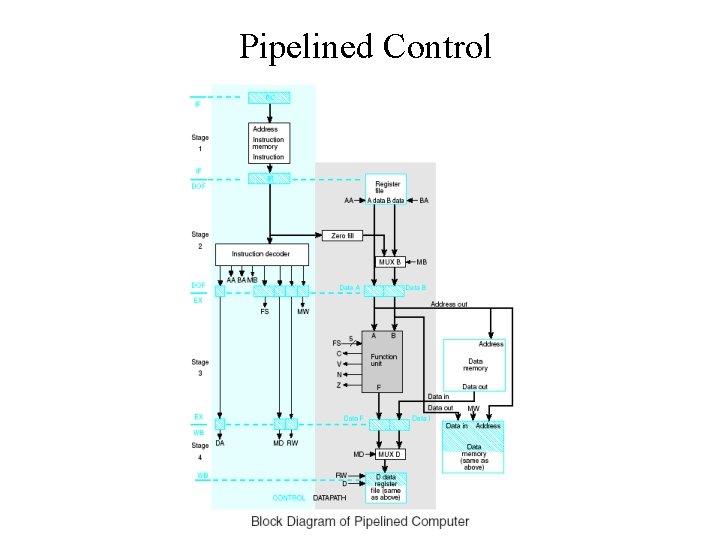

Pipelined Control

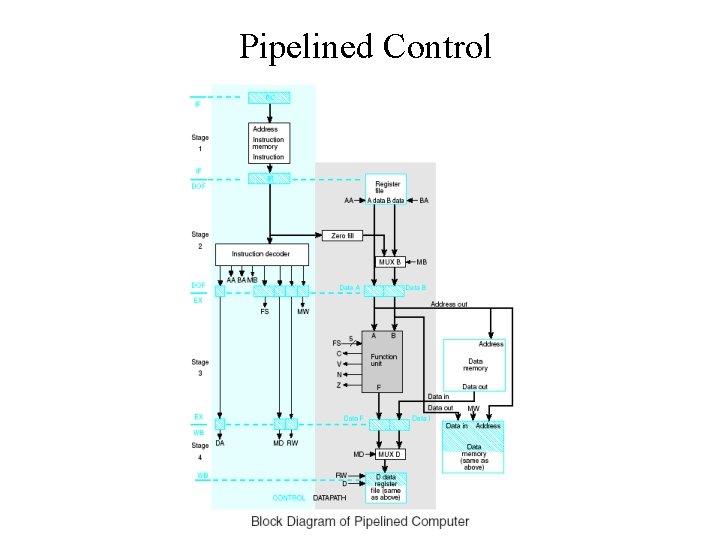

Pipelined Control

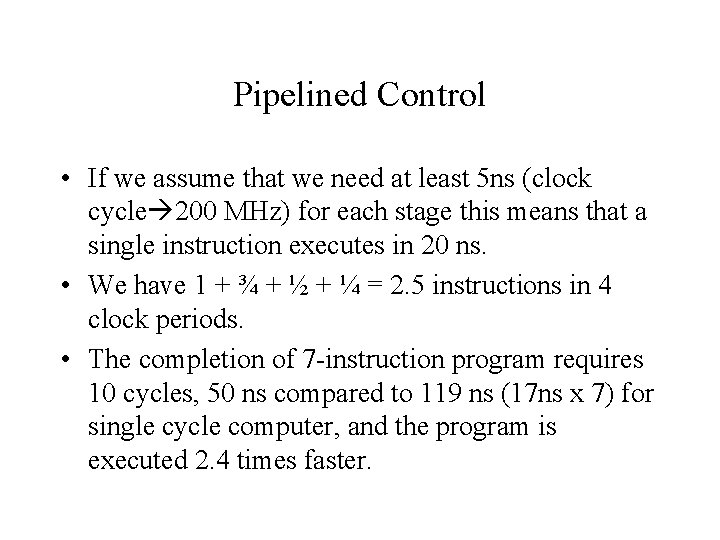

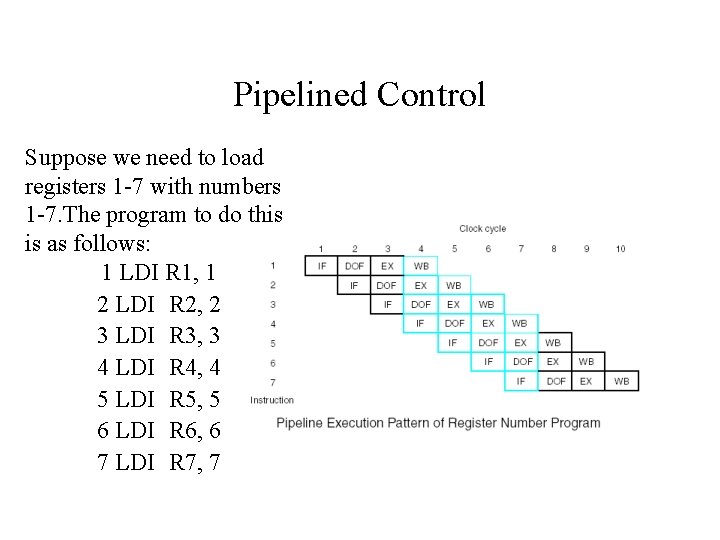

Pipelined Control Suppose we need to load registers 1 -7 with numbers 1 -7. The program to do this is as follows: 1 LDI R 1, 1 2 LDI R 2, 2 3 LDI R 3, 3 4 LDI R 4, 4 5 LDI R 5, 5 6 LDI R 6, 6 7 LDI R 7, 7

Pipelined Control • If we assume that we need at least 5 ns (clock cycle 200 MHz) for each stage this means that a single instruction executes in 20 ns. • We have 1 + ¾ + ½ + ¼ = 2. 5 instructions in 4 clock periods. • The completion of 7 -instruction program requires 10 cycles, 50 ns compared to 119 ns (17 ns x 7) for single cycle computer, and the program is executed 2. 4 times faster.

Pipelined Control • In the first three stages, the pipeline is filling, not all stages are active. • In the last three stages, the pipeline is emptying, not all stages are active. • In 20 ns – pipelined computer executes 4 instructions – Single cycle computer executes 20/17 = 1. 18 instructions. • The pipelined computer is 4/1. 18 = 3. 4 times faster