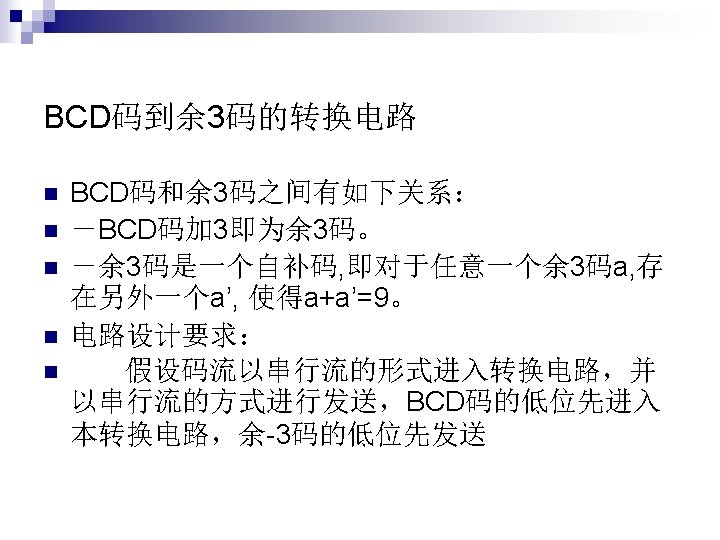

BCD 3 0 0000 0011 1 0001 0100

序列 BCD 余 3� 0 0000 0011 1 0001 0100 2 0010 0101 3 0011 0110 4 0100 0111 5 0101 1000 6 0110 1001 7 0111 1010 8 1000 1011 9 1001 1100 BCD到余 3码 转换表

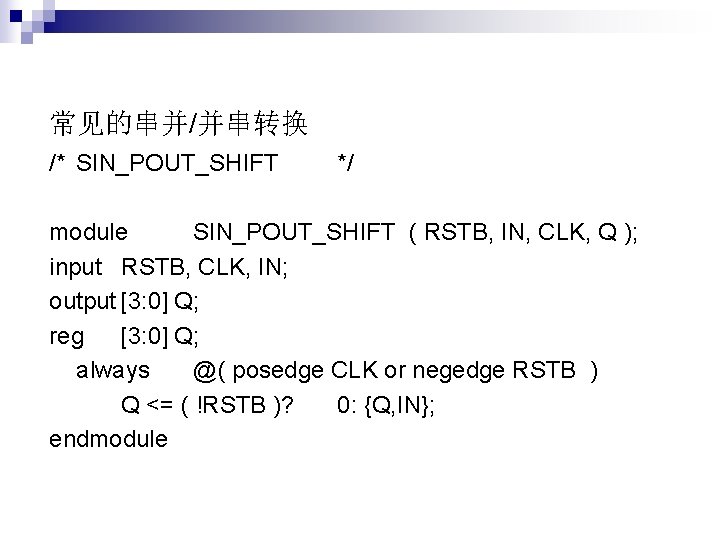

常见的串并/并串转换 /* SIN_POUT_SHIFT */ module SIN_POUT_SHIFT ( RSTB, IN, CLK, Q ); input RSTB, CLK, IN; output [3: 0] Q; reg [3: 0] Q; always @( posedge CLK or negedge RSTB ) Q <= ( !RSTB )? 0: {Q, IN}; endmodule

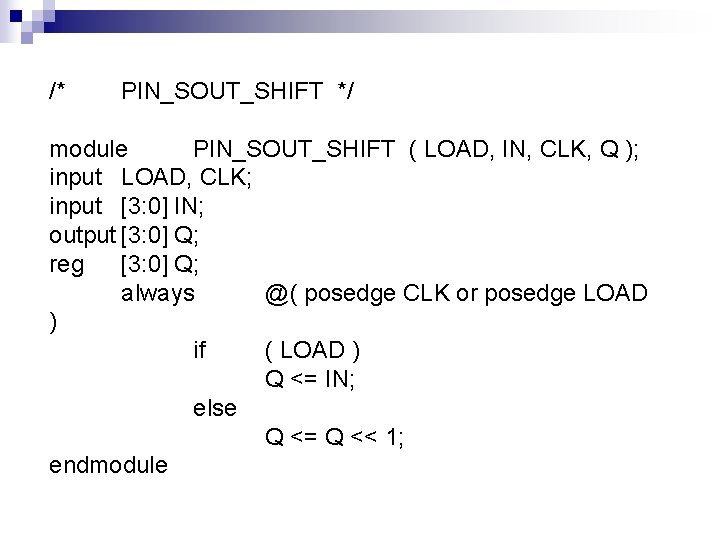

/* PIN_SOUT_SHIFT */ module PIN_SOUT_SHIFT ( LOAD, IN, CLK, Q ); input LOAD, CLK; input [3: 0] IN; output [3: 0] Q; reg [3: 0] Q; always @( posedge CLK or posedge LOAD ) if ( LOAD ) Q <= IN; else Q <= Q << 1; endmodule

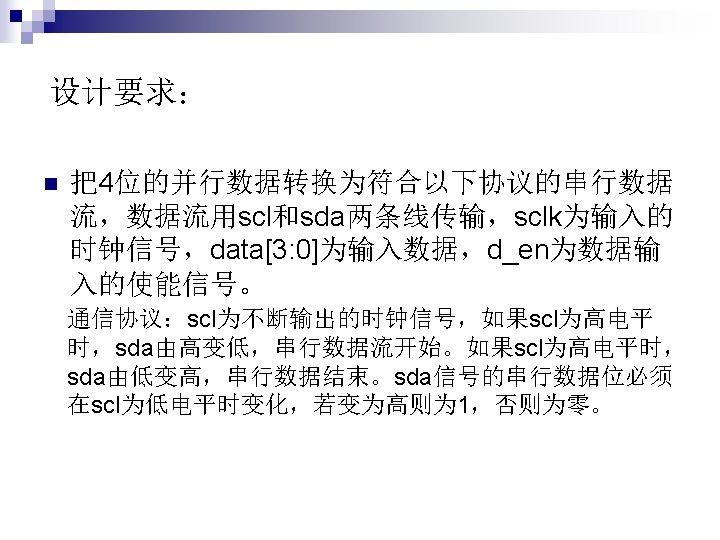

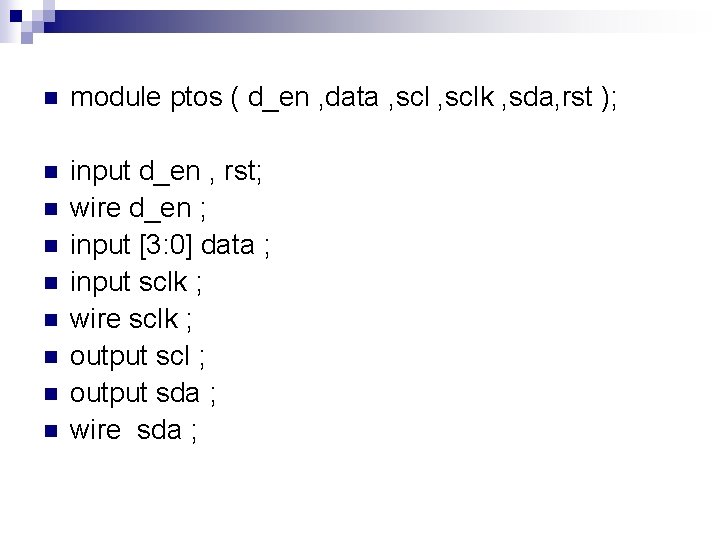

n module ptos ( d_en , data , sclk , sda, rst ); n input d_en , rst; wire d_en ; input [3: 0] data ; input sclk ; wire sclk ; output scl ; output sda ; wire sda ; n n n n

![n n n reg scl, link_sda, sdabuf; reg[3: 0] databuf; reg[7: 0] state; assign n n n reg scl, link_sda, sdabuf; reg[3: 0] databuf; reg[7: 0] state; assign](http://slidetodoc.com/presentation_image_h2/8396c9c750578c2f0d52d2b53648a6d3/image-10.jpg)

n n n reg scl, link_sda, sdabuf; reg[3: 0] databuf; reg[7: 0] state; assign sda=link_sda? sdabuf: 1'bz; parameter ready = 8'b 00000001, start = 8'b 00000010, bit 1 = 8'b 00000100, bit 2 = 8'b 00001000, bit 3 = 8'b 00010000, bit 4 = 8'b 00100000, bit 5 = 8'b 01000000, stop = 8'b 10000000;

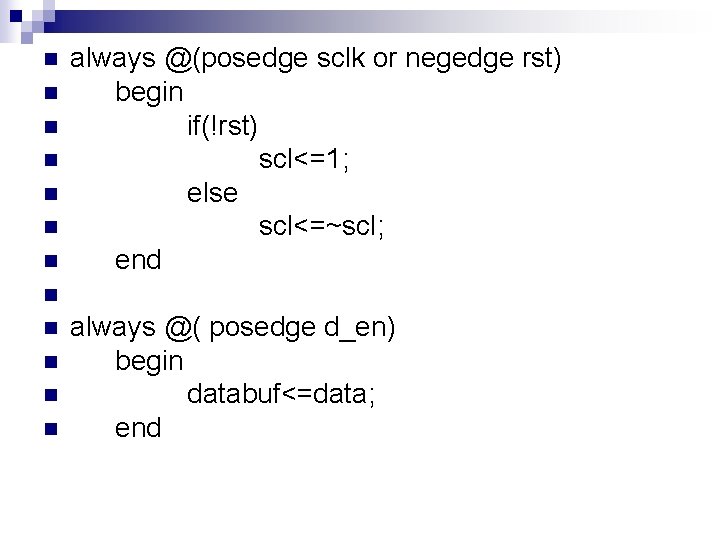

n n n n always @(posedge sclk or negedge rst) begin if(!rst) scl<=1; else scl<=~scl; end n n n always @( posedge d_en) begin databuf<=data; end

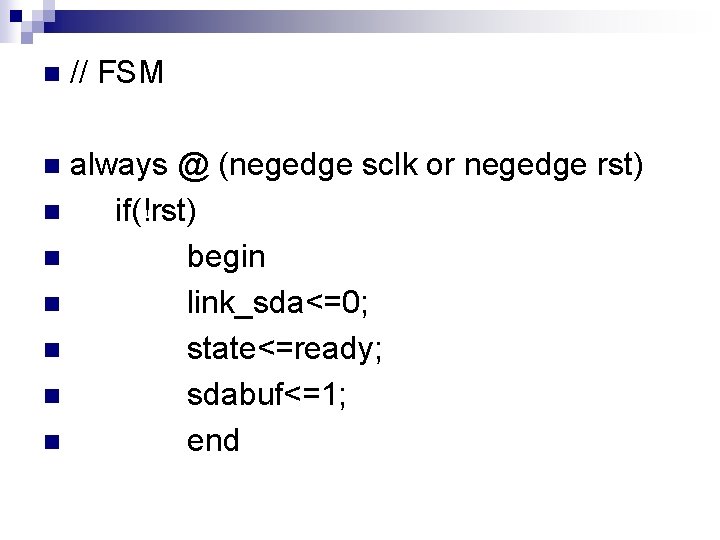

n // FSM always @ (negedge sclk or negedge rst) n if(!rst) n begin n link_sda<=0; n state<=ready; n sdabuf<=1; n end n

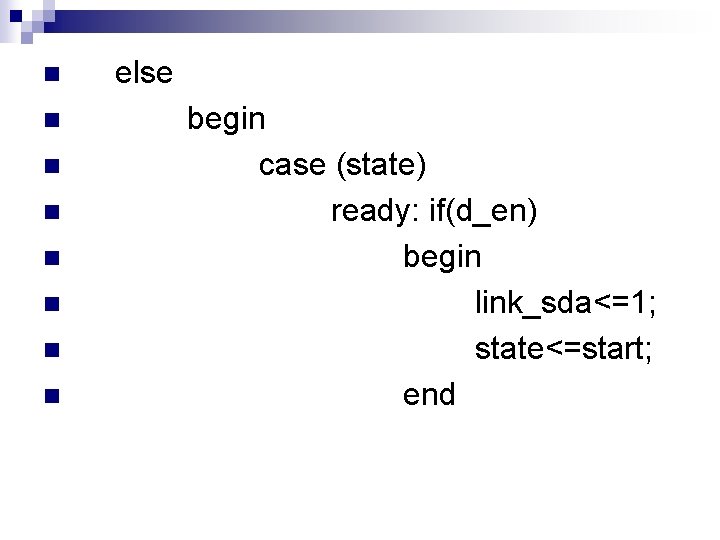

n n n n else begin case (state) ready: if(d_en) begin link_sda<=1; state<=start; end

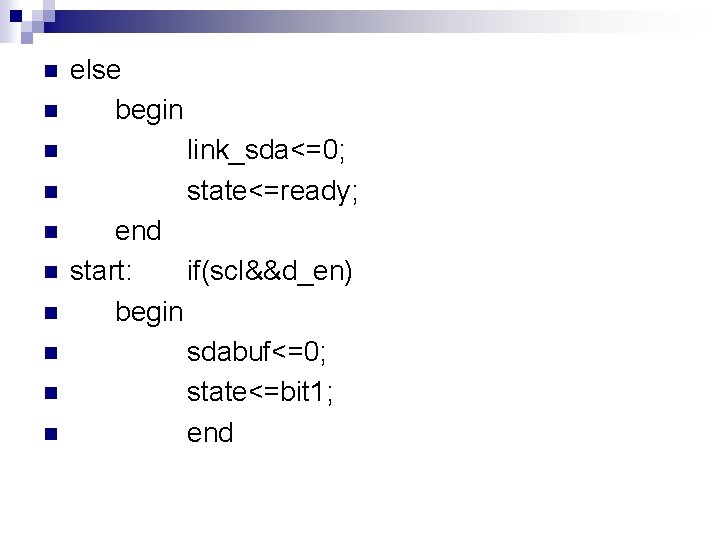

n n n n n else begin link_sda<=0; state<=ready; end start: if(scl&&d_en) begin sdabuf<=0; state<=bit 1; end

![n else state<=start; n bit 1: if(!scl) n begin n n n sdabuf<=databuf[3]; state n else state<=start; n bit 1: if(!scl) n begin n n n sdabuf<=databuf[3]; state](http://slidetodoc.com/presentation_image_h2/8396c9c750578c2f0d52d2b53648a6d3/image-15.jpg)

n else state<=start; n bit 1: if(!scl) n begin n n n sdabuf<=databuf[3]; state <=bit 2; end else state<=bit 1;

![n n n n bit 2: if (!scl) begin sdabuf<=databuf[2]; state<=bit 3; end else n n n n bit 2: if (!scl) begin sdabuf<=databuf[2]; state<=bit 3; end else](http://slidetodoc.com/presentation_image_h2/8396c9c750578c2f0d52d2b53648a6d3/image-16.jpg)

n n n n bit 2: if (!scl) begin sdabuf<=databuf[2]; state<=bit 3; end else state <=bit 2;

![n n n n bit 3: if(!scl) begin sdabuf<=databuf[1]; state <=bit 4; end else n n n n bit 3: if(!scl) begin sdabuf<=databuf[1]; state <=bit 4; end else](http://slidetodoc.com/presentation_image_h2/8396c9c750578c2f0d52d2b53648a6d3/image-17.jpg)

n n n n bit 3: if(!scl) begin sdabuf<=databuf[1]; state <=bit 4; end else state <=bit 3; bit 4: if(!scl) begin sdabuf<=databuf[0]; state<=bit 5; end else state <=bit 4;

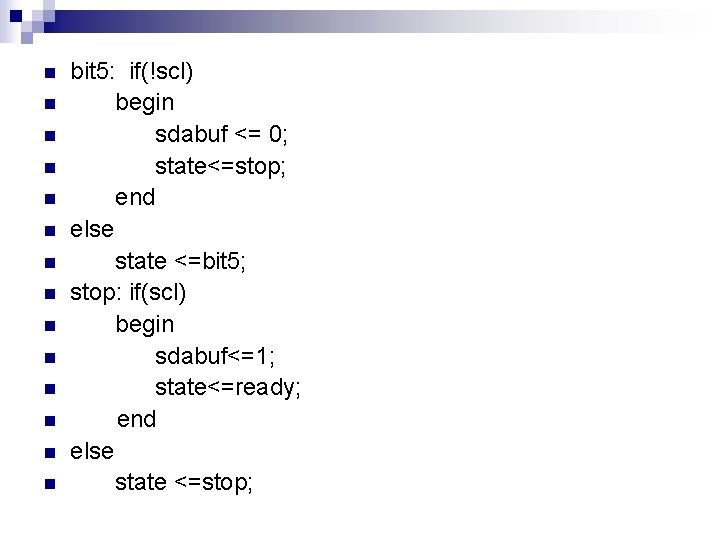

n n n n bit 5: if(!scl) begin sdabuf <= 0; state<=stop; end else state <=bit 5; stop: if(scl) begin sdabuf<=1; state<=ready; end else state <=stop;

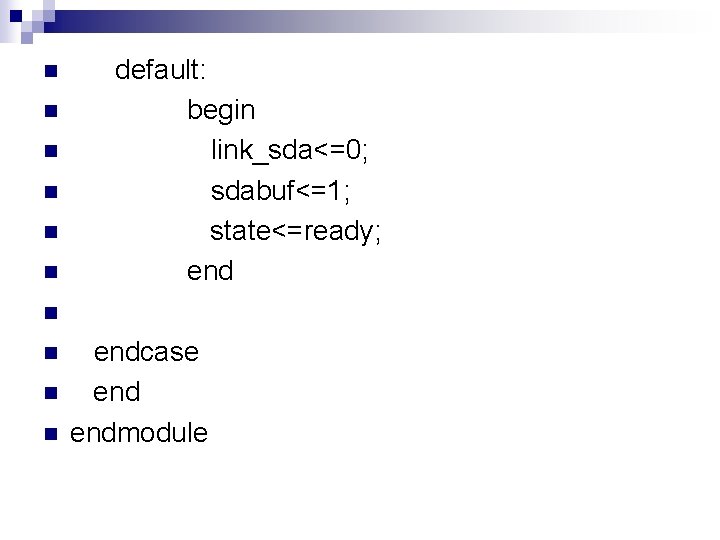

n n n default: begin link_sda<=0; sdabuf<=1; state<=ready; end n n endcase endmodule

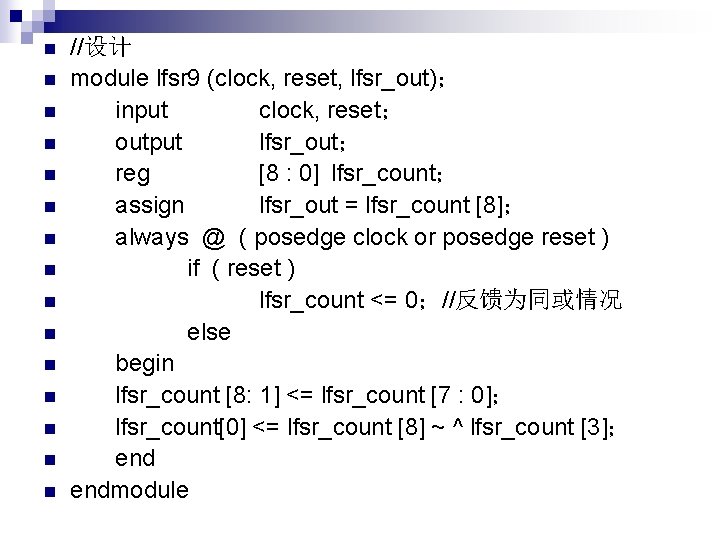

n n n n //设计 module lfsr 9 (clock, reset, lfsr_out); input clock, reset; output lfsr_out; reg [8 : 0] lfsr_count; assign lfsr_out = lfsr_count [8]; always @ ( posedge clock or posedge reset ) if ( reset ) lfsr_count <= 0;//反馈为同或情况 else begin lfsr_count [8: 1] <= lfsr_count [7 : 0]; lfsr_count[0] <= lfsr_count [8] ~ ^ lfsr_count [3]; endmodule

![lfsr _b[7]=lfsr_a[8]⊕lfsr_a[3] lfsr _b[6]=lfsr_a[7]⊕lfsr_a[2] lfsr _b[5]=lfsr_a[6]⊕lfsr_a[1] lfsr _b[4]=lfsr_a[5]⊕lfsr_a[0] lfsr _b[3]=lfsr_a[4]⊕lfsr_b[8]=lfsr_a[4]⊕lfsr_a[8]⊕lfsr_a[3] lfsr _b[3]=lfsr_a[3]⊕lfsr_b[7]=lfsr_a[3]⊕lfsr_a[7]⊕lfsr_a[2] lfsr _b[2]=lfsr_a[2]⊕lfsr_b[6]=lfsr_a[2]⊕lfsr_a[6]⊕lfsr_a[1] lfsr _b[7]=lfsr_a[8]⊕lfsr_a[3] lfsr _b[6]=lfsr_a[7]⊕lfsr_a[2] lfsr _b[5]=lfsr_a[6]⊕lfsr_a[1] lfsr _b[4]=lfsr_a[5]⊕lfsr_a[0] lfsr _b[3]=lfsr_a[4]⊕lfsr_b[8]=lfsr_a[4]⊕lfsr_a[8]⊕lfsr_a[3] lfsr _b[3]=lfsr_a[3]⊕lfsr_b[7]=lfsr_a[3]⊕lfsr_a[7]⊕lfsr_a[2] lfsr _b[2]=lfsr_a[2]⊕lfsr_b[6]=lfsr_a[2]⊕lfsr_a[6]⊕lfsr_a[1]](http://slidetodoc.com/presentation_image_h2/8396c9c750578c2f0d52d2b53648a6d3/image-27.jpg)

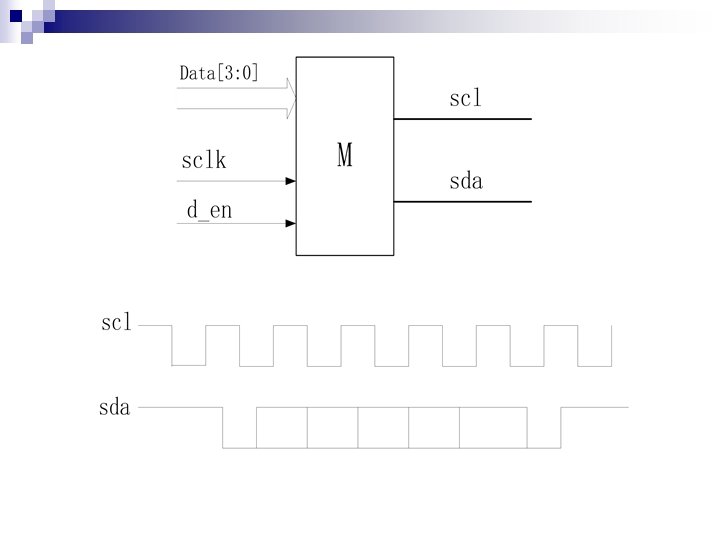

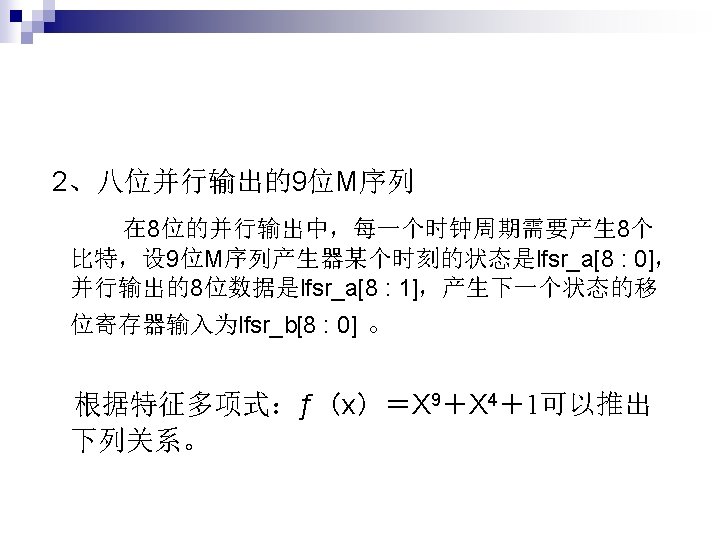

lfsr _b[7]=lfsr_a[8]⊕lfsr_a[3] lfsr _b[6]=lfsr_a[7]⊕lfsr_a[2] lfsr _b[5]=lfsr_a[6]⊕lfsr_a[1] lfsr _b[4]=lfsr_a[5]⊕lfsr_a[0] lfsr _b[3]=lfsr_a[4]⊕lfsr_b[8]=lfsr_a[4]⊕lfsr_a[8]⊕lfsr_a[3] lfsr _b[3]=lfsr_a[3]⊕lfsr_b[7]=lfsr_a[3]⊕lfsr_a[7]⊕lfsr_a[2] lfsr _b[2]=lfsr_a[2]⊕lfsr_b[6]=lfsr_a[2]⊕lfsr_a[6]⊕lfsr_a[1] lfsr _b[1]=lfsr_a[1]⊕lfsr_b[5]=lfsr_a[1]⊕lfsr_a[5]⊕lfsr_a[0] lfsr _b[8]=lfsr_a[0] fsr_out = lfsr_a [8 : 1]

![module lfsr 9 p (clock, reset, lfsr_out); input clock, reset; output [8 : 1] module lfsr 9 p (clock, reset, lfsr_out); input clock, reset; output [8 : 1]](http://slidetodoc.com/presentation_image_h2/8396c9c750578c2f0d52d2b53648a6d3/image-28.jpg)

module lfsr 9 p (clock, reset, lfsr_out); input clock, reset; output [8 : 1] lfsr_out; reg [8 : 0] lfsr_a; wire [8 : 0] lfsr_b; assign lfsr_out = lfsr_a [8 : 1]; assign lfsr_b[7 : 4] = lfsr_a[8 : 5] ^ lfsr_a[3 : 0]; assign lfsr_b[3 : 0] = lfsr_a[4 : 1] ^ lfsr_a[8 : 5] ^ lfsr_a[3 : 0] assign lfsr_b[8] = lfsr_a [0]; always @ ( posedge clock or posedge reset ) if ( reset ) lfsr_a <= 9`h 1 ff;//反�� 异或情况 else lfsr_a[8 : 0] <= lfsr_b[8 : 0]; endmodule

- Slides: 38