A TimingDriven SoftMacro Resynthesis Method in Interaction with

- Slides: 51

A Timing-Driven Soft-Macro Resynthesis Method in Interaction with Chip Floorplanning Hsiao-Pin Su 1 2 Allen C. -H. Wu 1 1 Department Youn-Long Lin 1 of Computer Science Tsing Hua University Hsinchu, Taiwan, R. O. C 2 Taiwan Semiconductor Manufacturing Co. , Ltd. {Email: robin@nthucad. cs. nthu. edu. tw}

Outline l Introduction l Motivation l The Proposed Method l Experiments l Conclusions

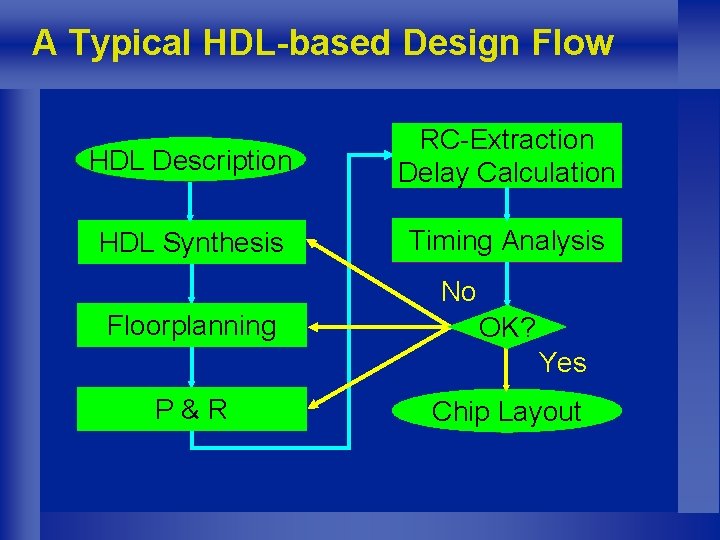

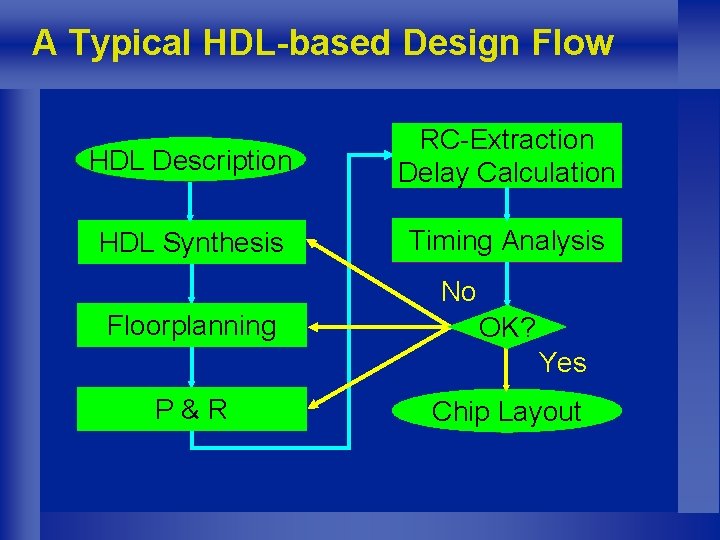

A Typical HDL-based Design Flow HDL Description RC-Extraction Delay Calculation HDL Synthesis Timing Analysis No Floorplanning OK? Yes P&R Chip Layout

Motivation l Develop a complete chip design method which incorporates a soft-macro placement and resynthesis method in interaction with chip floorplanning for area and timing improvement.

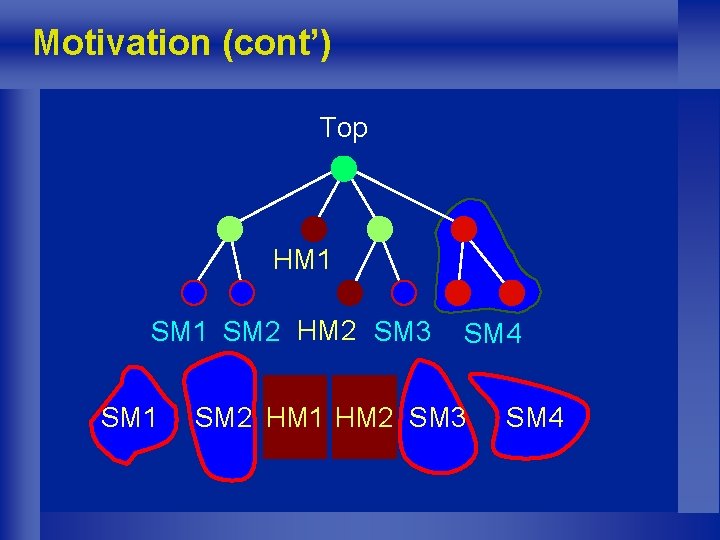

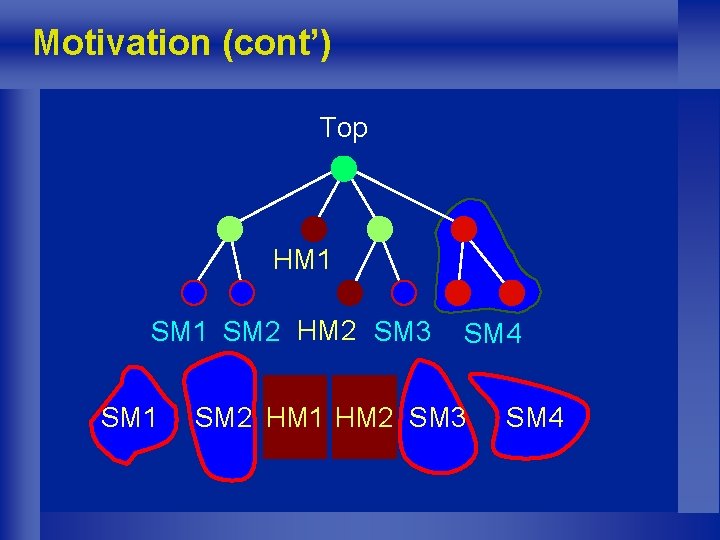

Motivation (cont’) Top HM 1 SM 2 HM 2 SM 3 SM 1 SM 4 SM 2 HM 1 HM 2 SM 3 SM 4

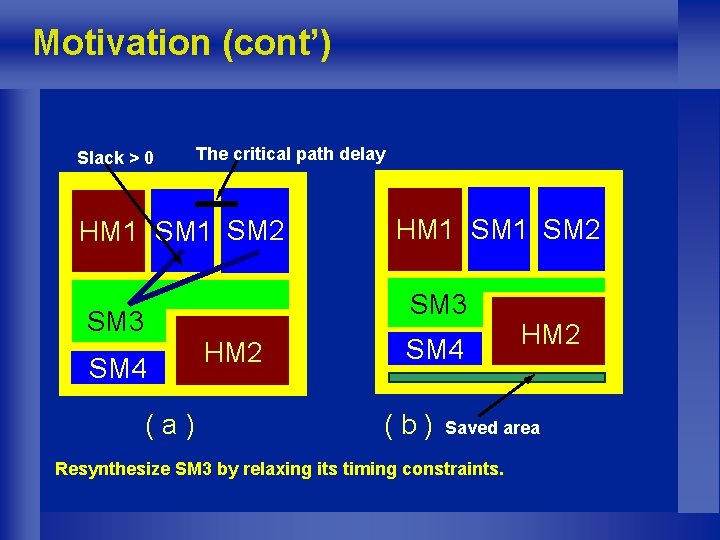

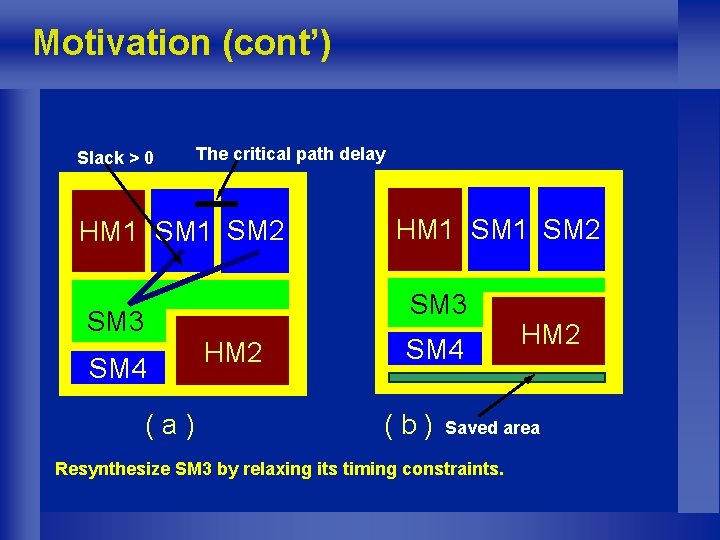

Motivation (cont’) Slack > 0 The critical path delay HM 1 SM 2 SM 3 SM 4 (a) HM 2 HM 1 SM 2 SM 3 SM 4 (b) HM 2 Saved area Resynthesize SM 3 by relaxing its timing constraints.

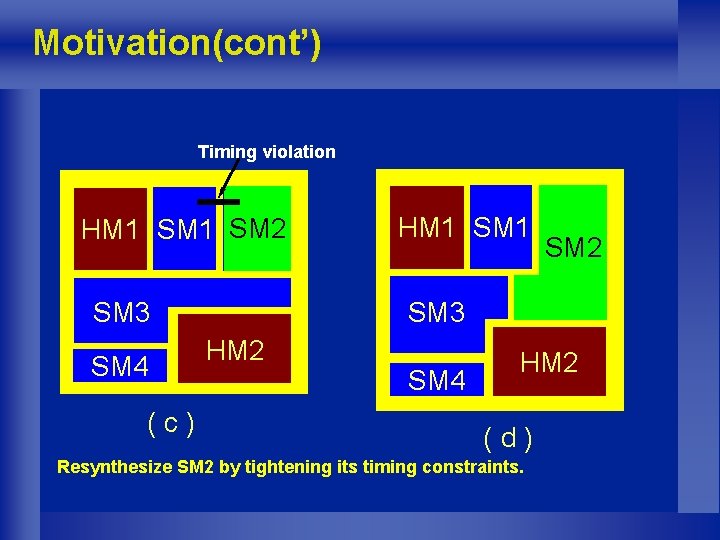

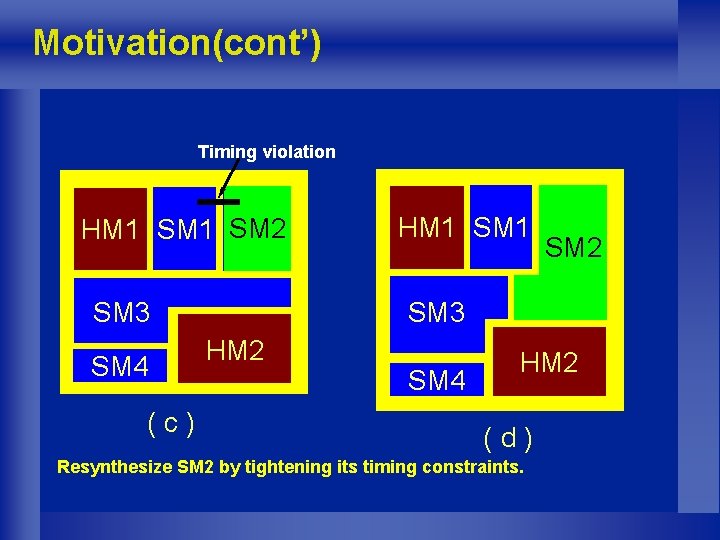

Motivation(cont’) Timing violation HM 1 SM 2 SM 3 SM 4 (c) HM 1 SM 2 SM 3 HM 2 SM 4 HM 2 (d) Resynthesize SM 2 by tightening its timing constraints.

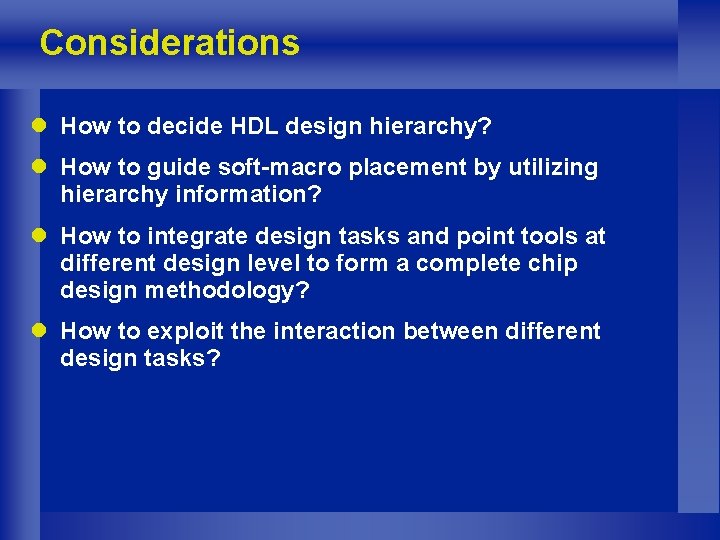

Considerations l How to decide HDL design hierarchy? l How to guide soft-macro placement by utilizing hierarchy information? l How to integrate design tasks and point tools at different design level to form a complete chip design methodology? l How to exploit the interaction between different design tasks?

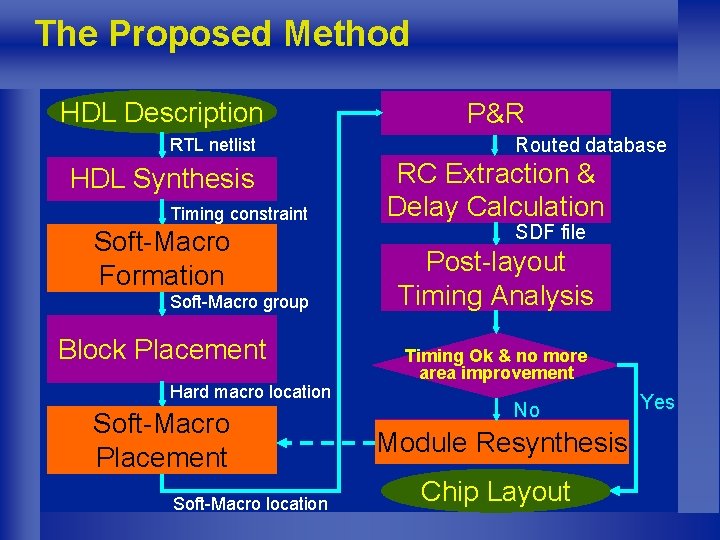

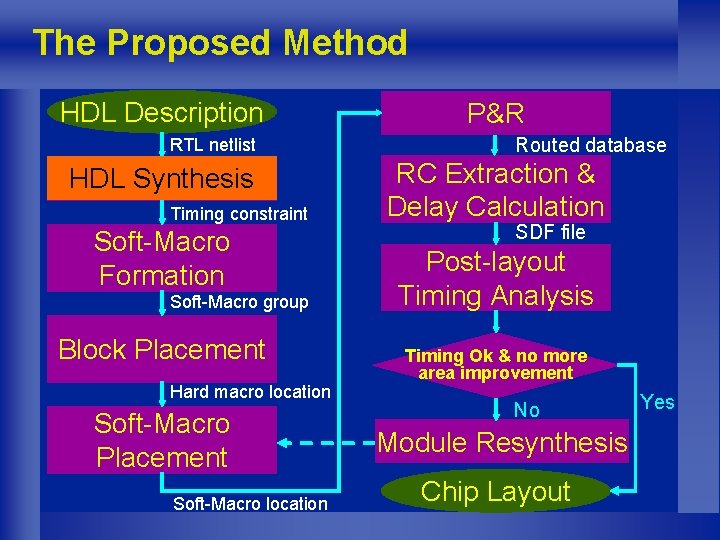

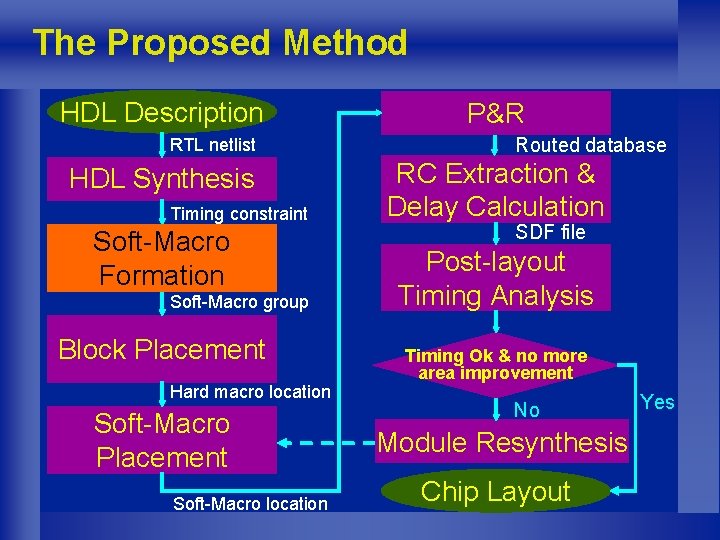

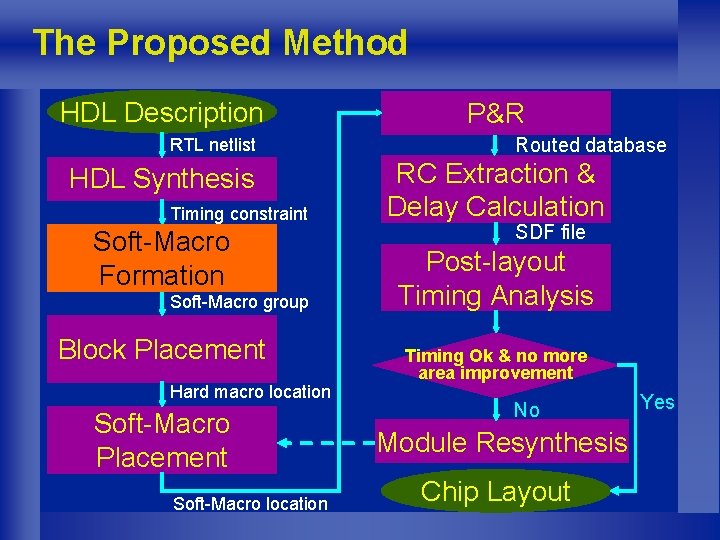

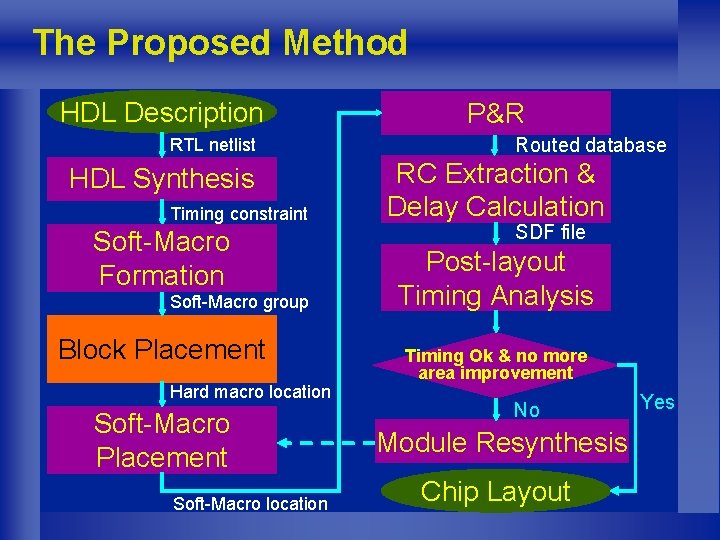

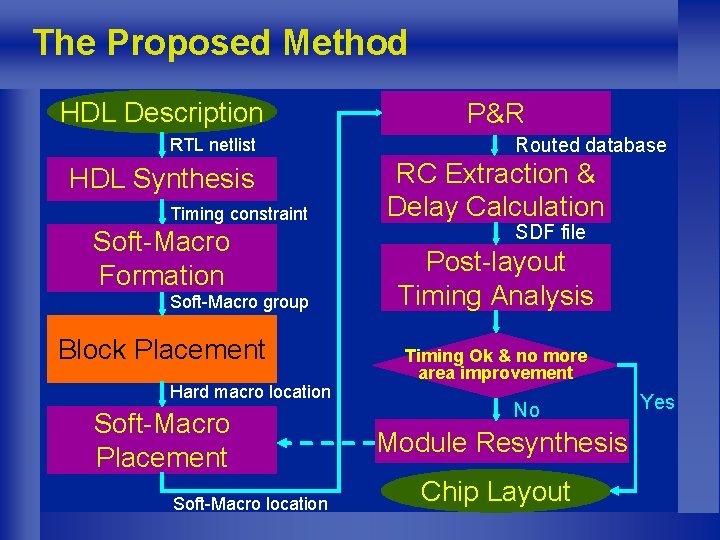

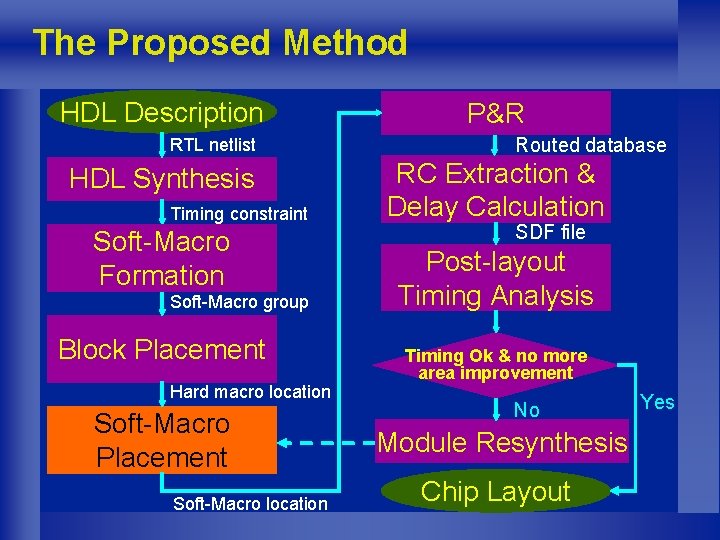

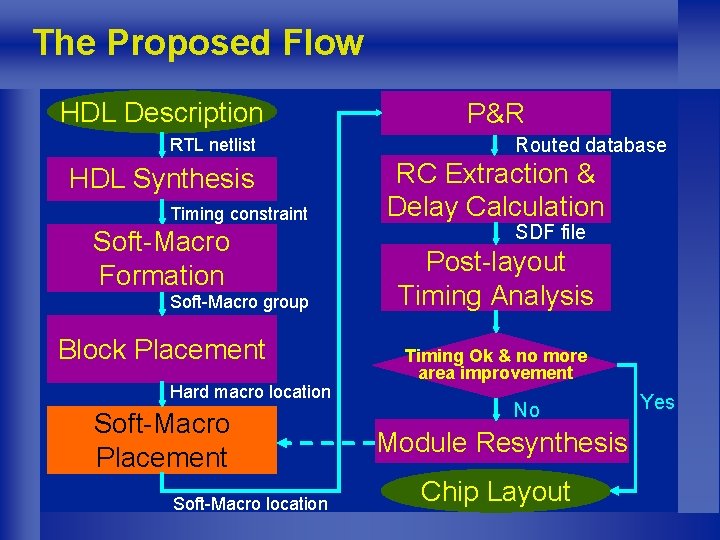

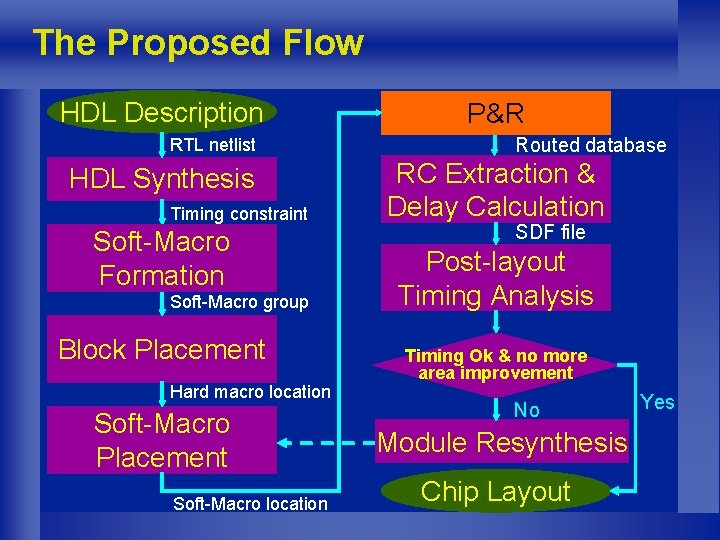

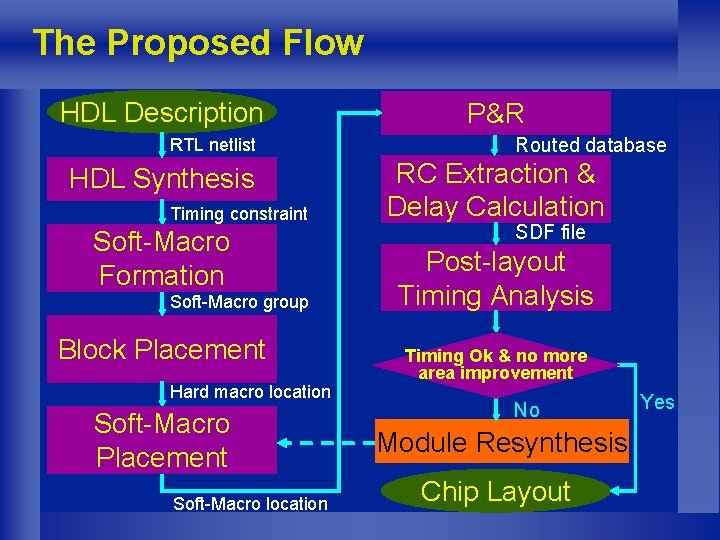

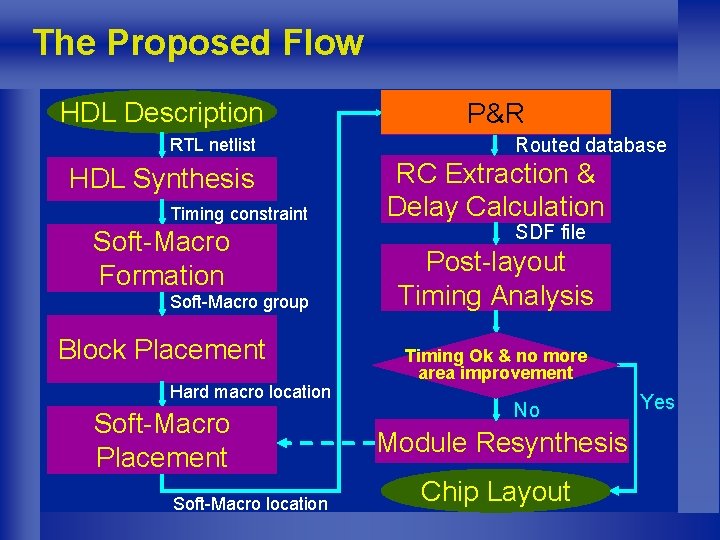

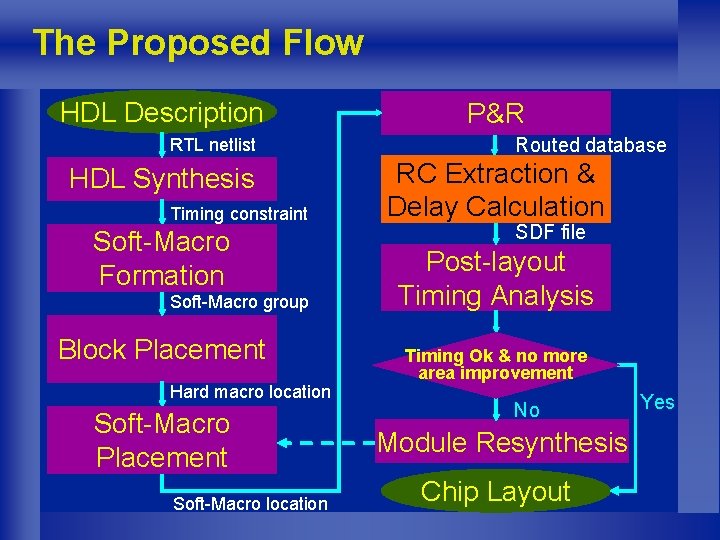

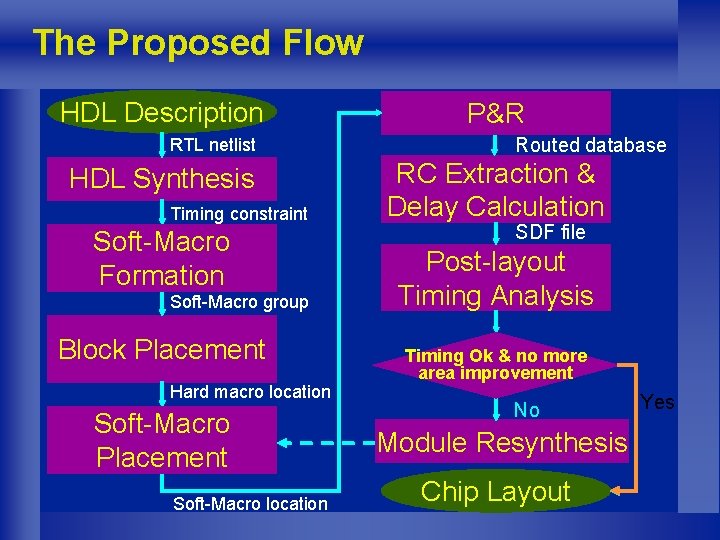

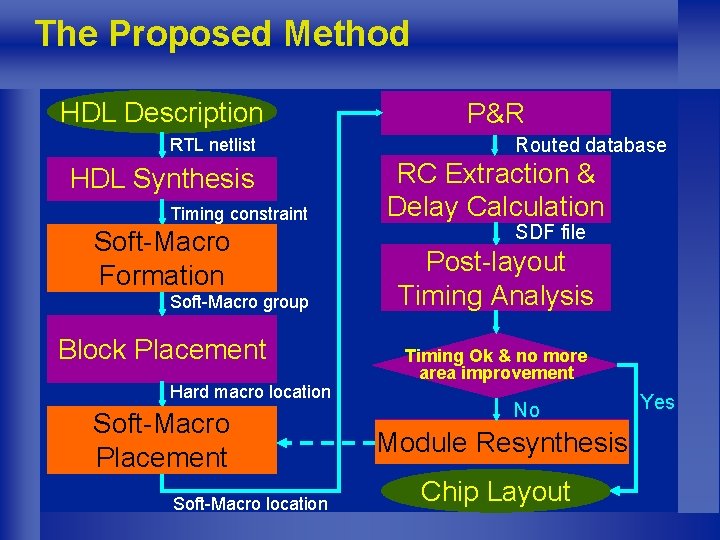

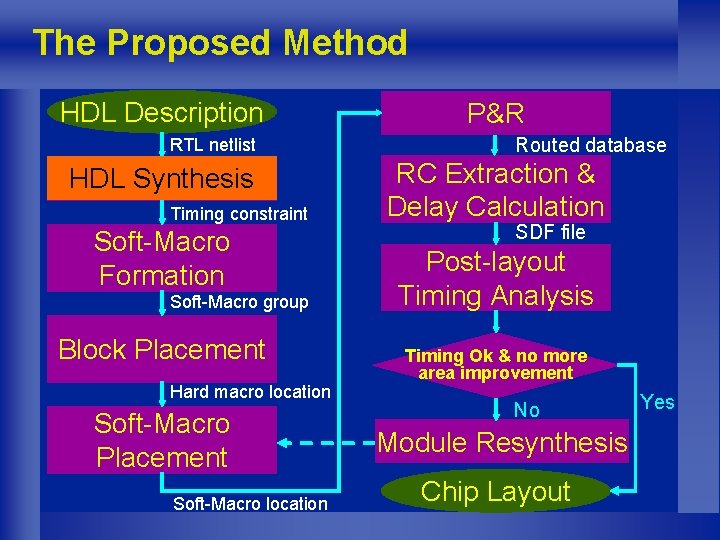

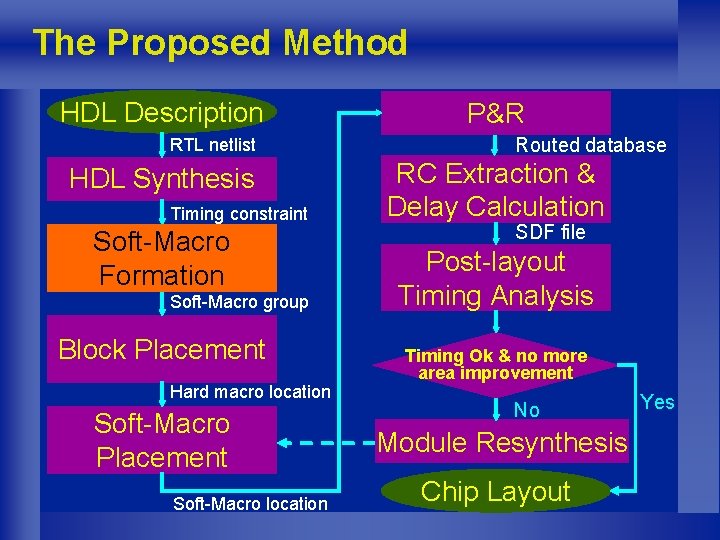

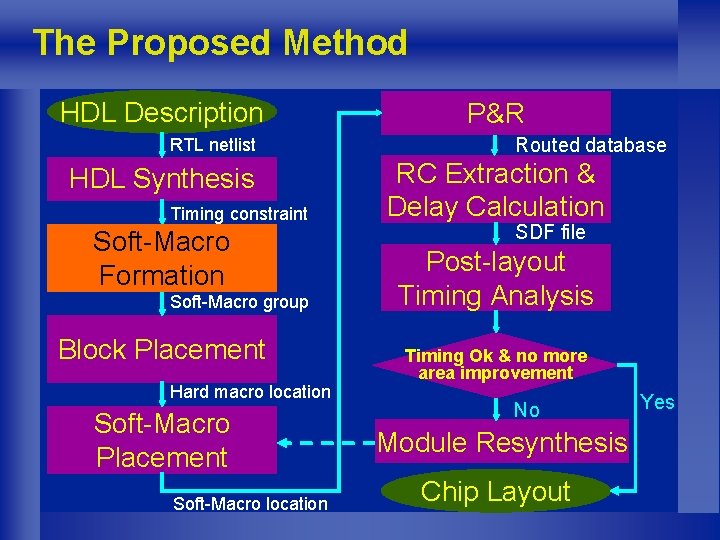

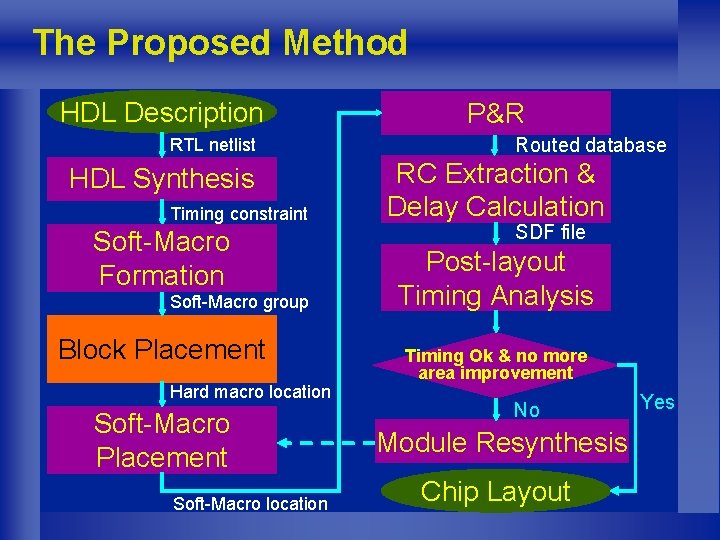

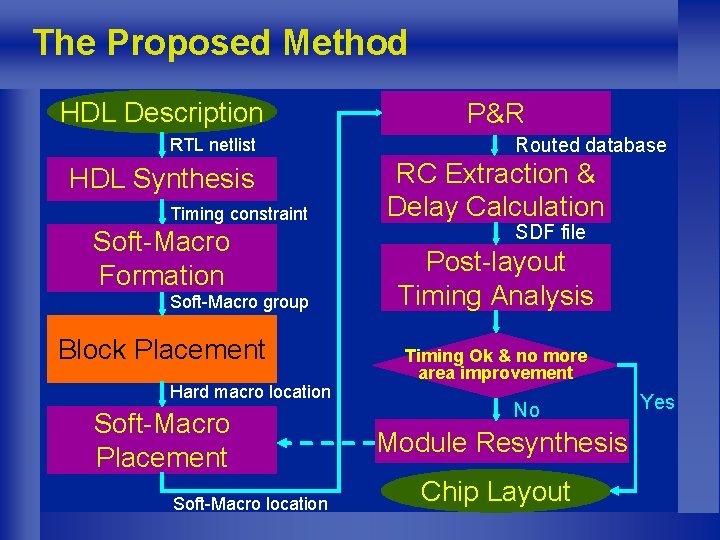

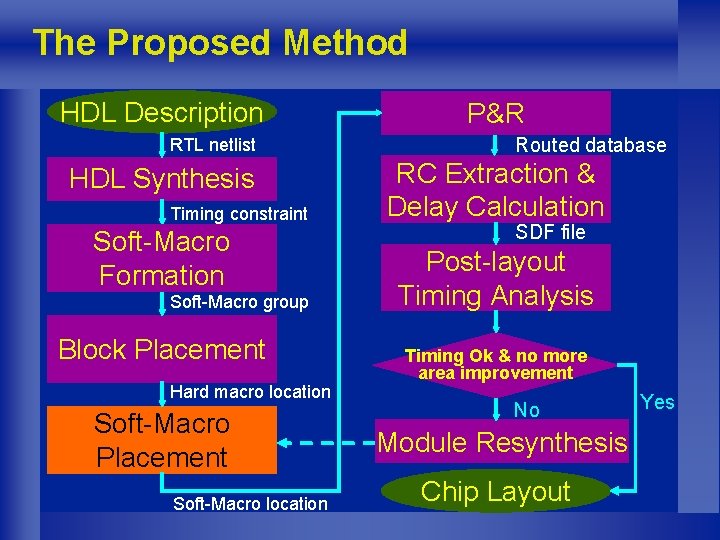

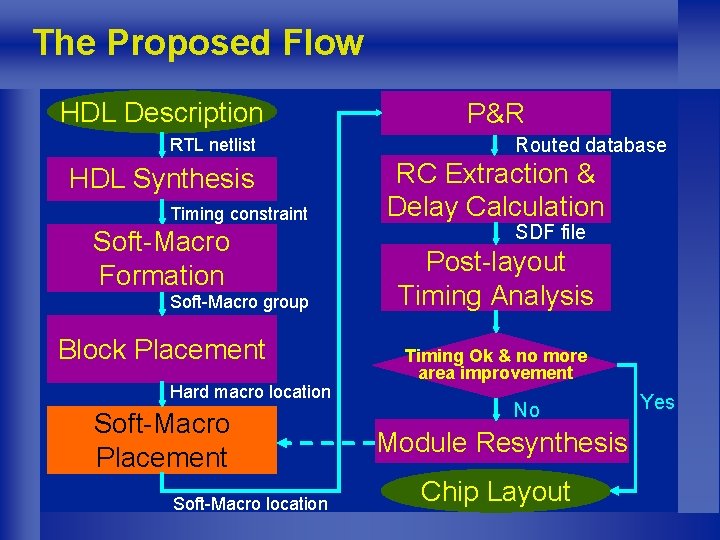

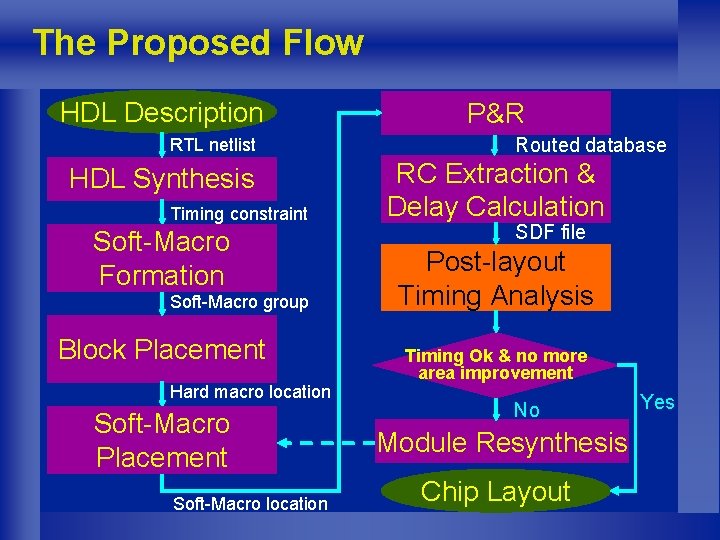

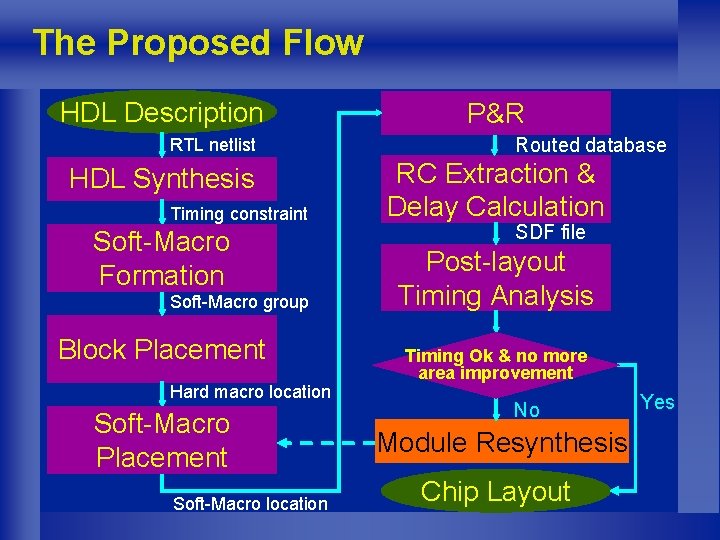

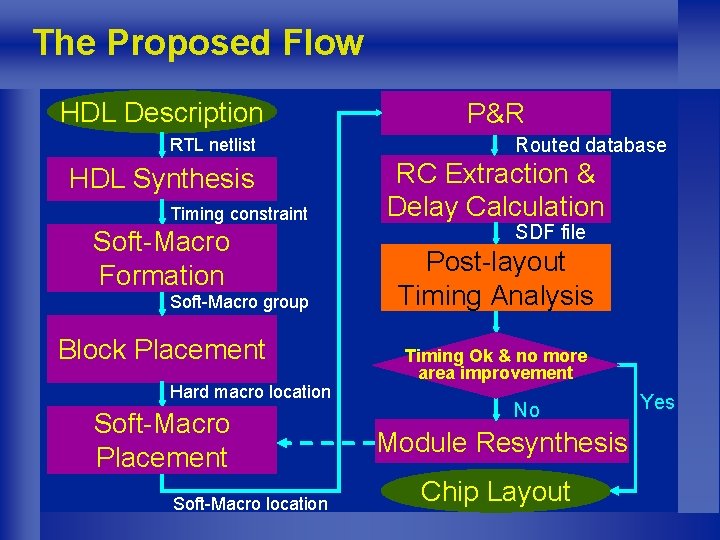

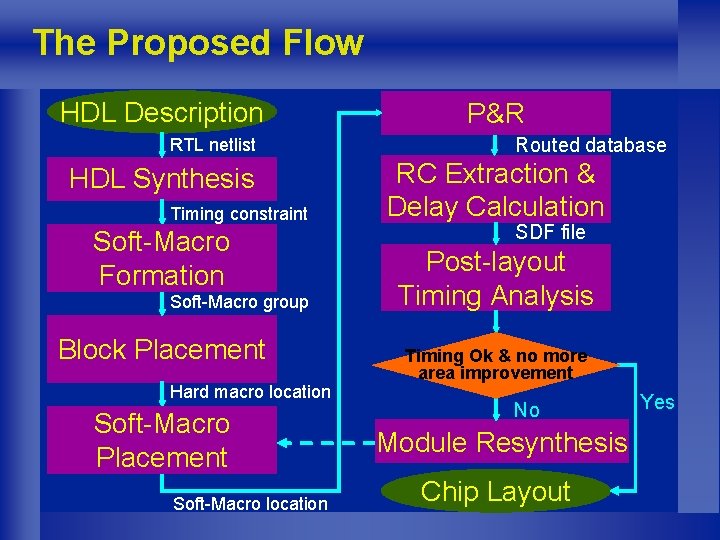

The Proposed Method HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

The Proposed Method HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

The Proposed Method HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

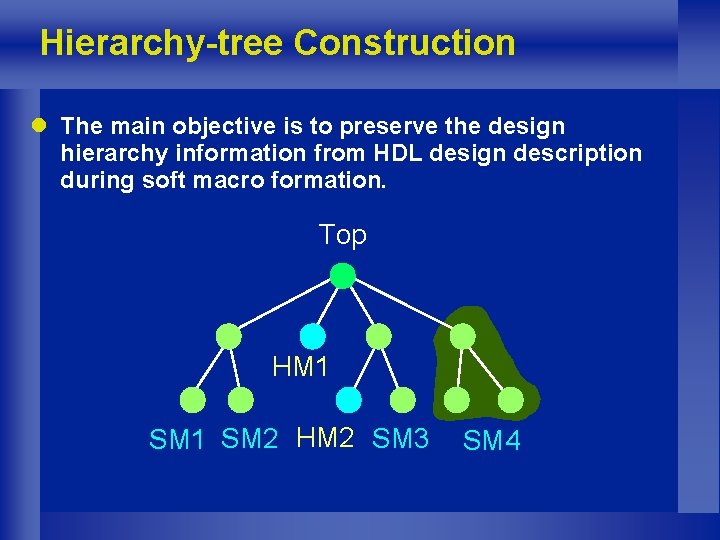

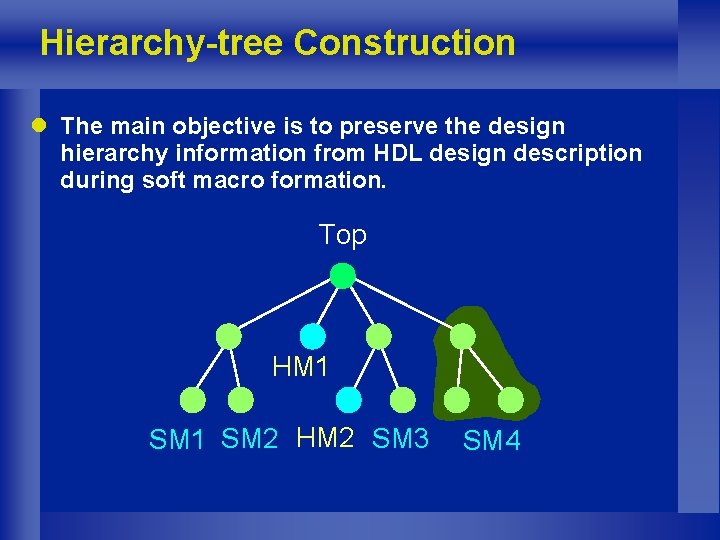

Hierarchy-tree Construction l The main objective is to preserve the design hierarchy information from HDL design description during soft macro formation. Top HM 1 SM 2 HM 2 SM 3 SM 4

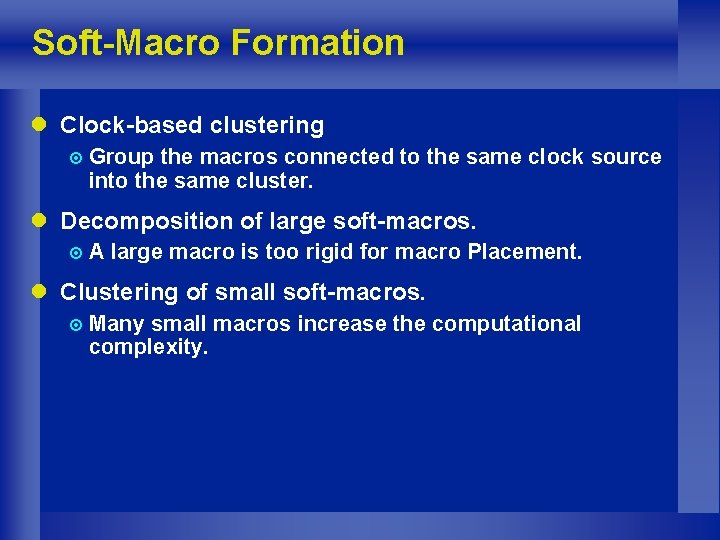

Soft-Macro Formation l Clock-based clustering ¤ Group the macros connected to the same clock source into the same cluster. l Decomposition of large soft-macros. ¤A large macro is too rigid for macro Placement. l Clustering of small soft-macros. ¤ Many small macros increase the computational complexity.

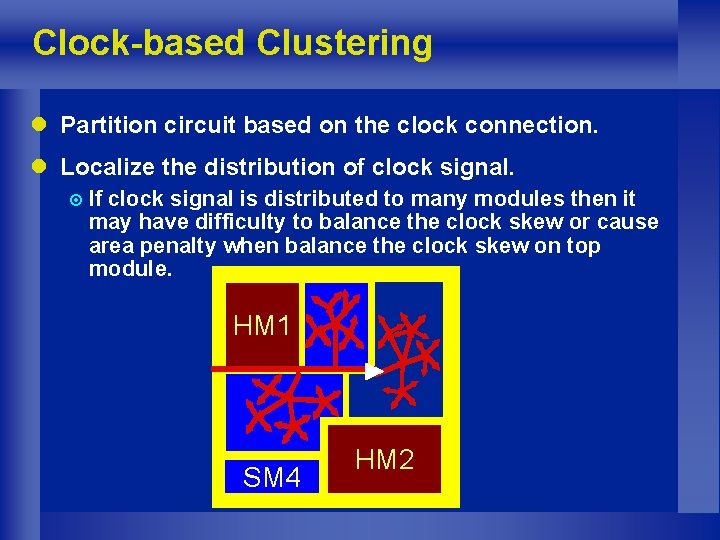

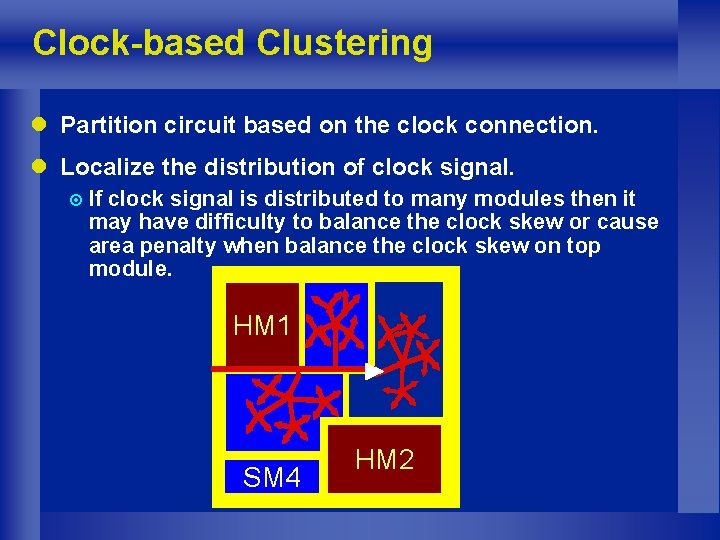

Clock-based Clustering l Partition circuit based on the clock connection. l Localize the distribution of clock signal. ¤ If clock signal is distributed to many modules then it may have difficulty to balance the clock skew or cause area penalty when balance the clock skew on top module. HM 1 SM 4 HM 2

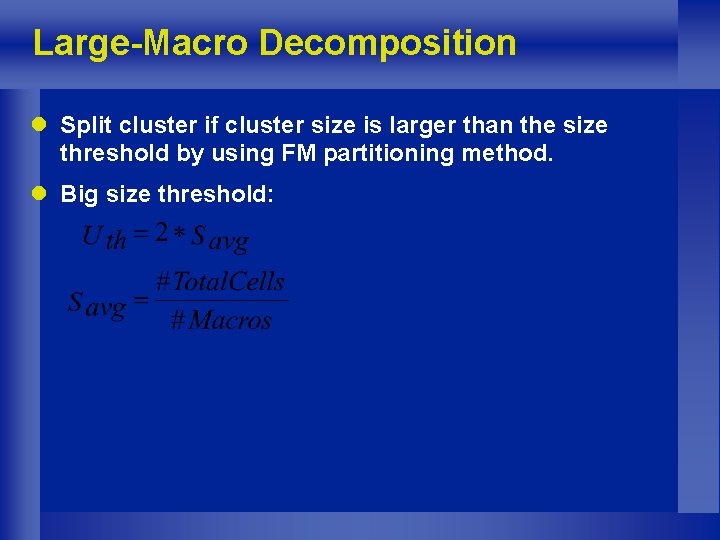

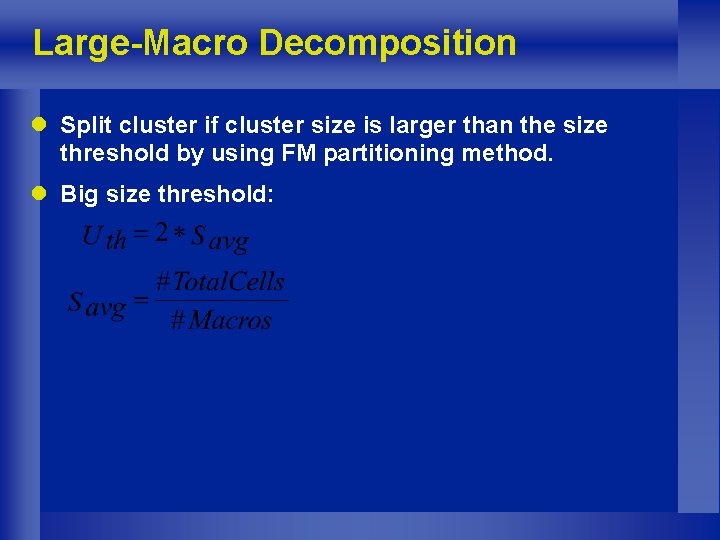

Large-Macro Decomposition l Split cluster if cluster size is larger than the size threshold by using FM partitioning method. l Big size threshold:

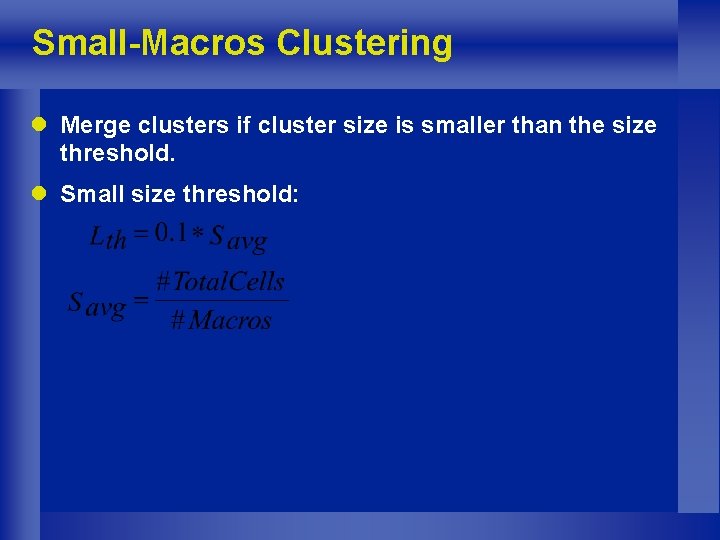

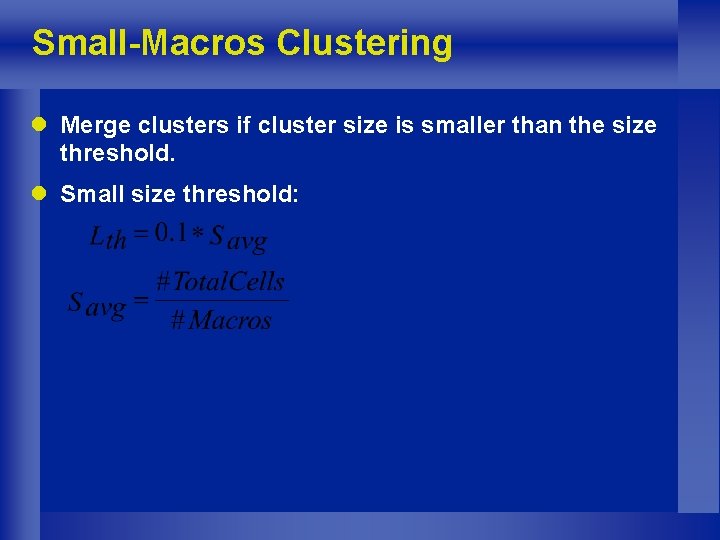

Small-Macros Clustering l Merge clusters if cluster size is smaller than the size threshold. l Small size threshold:

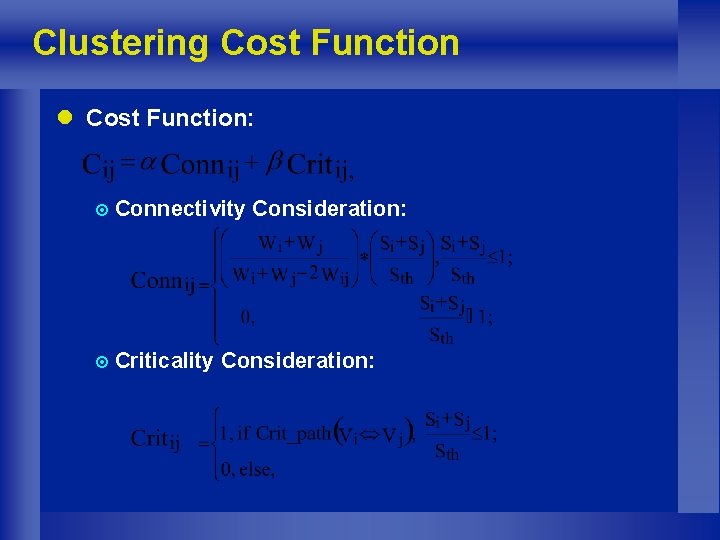

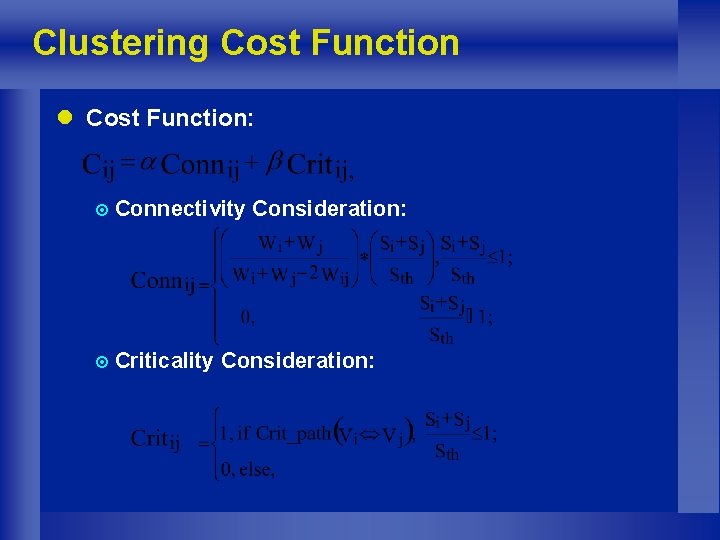

Clustering Cost Function l Cost Function: ¤ Connectivity ¤ Criticality Consideration:

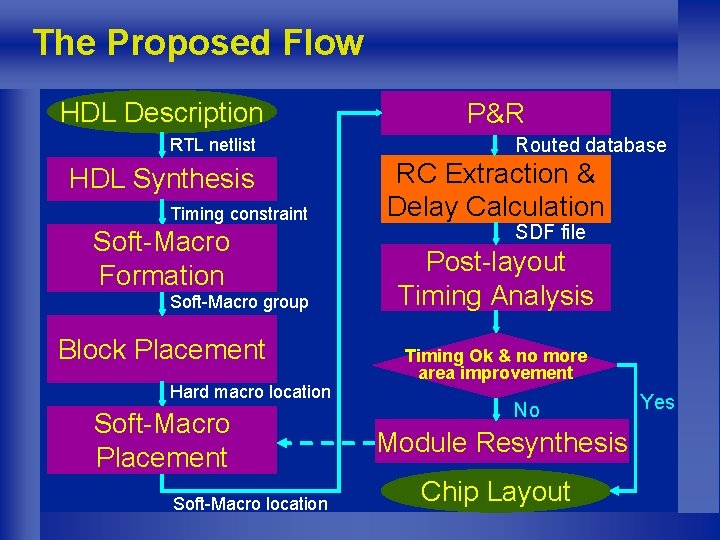

The Proposed Method HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

The Proposed Method HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

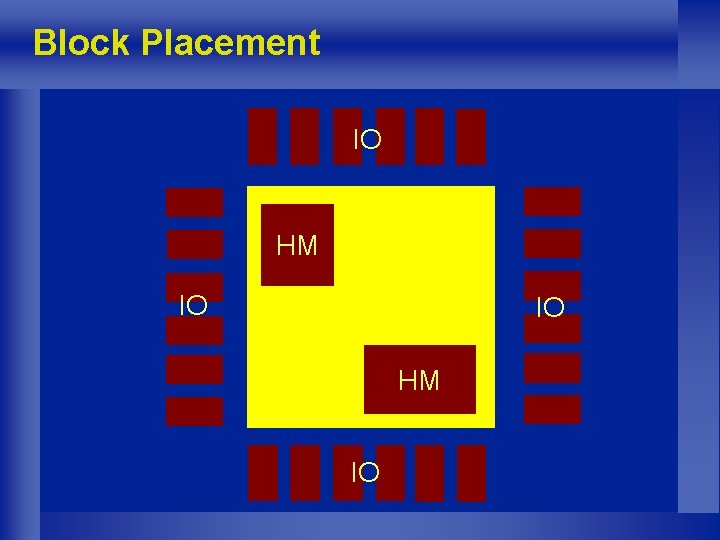

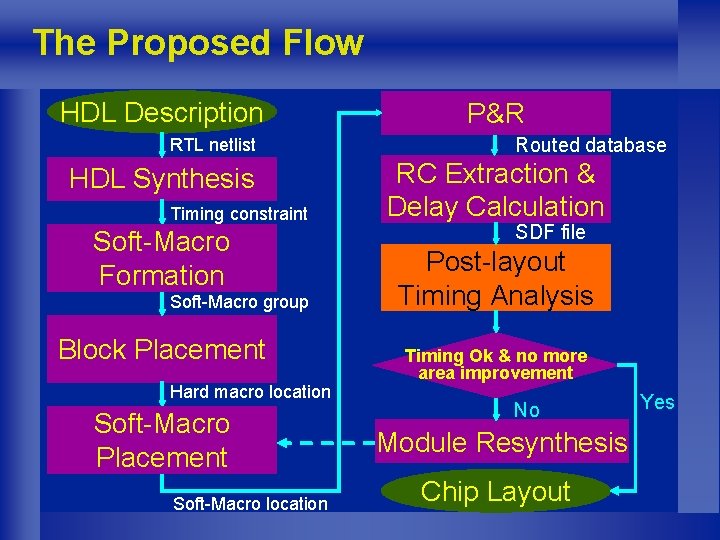

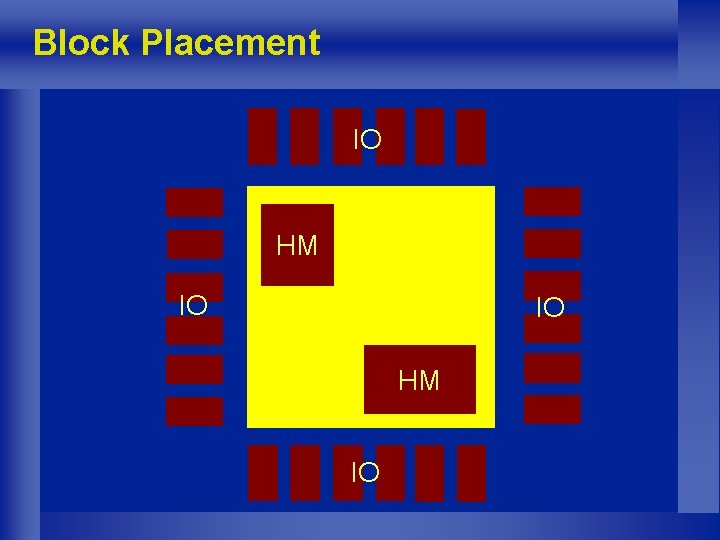

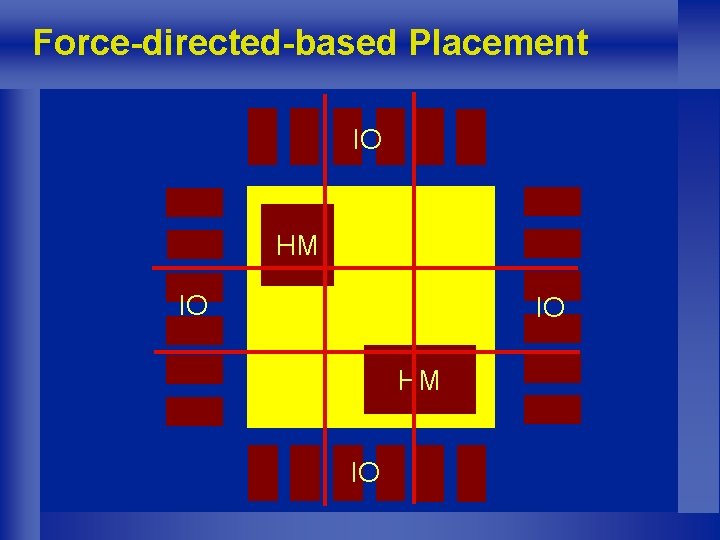

Block Placement IO HM IO

The Proposed Method HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

The Proposed Method HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

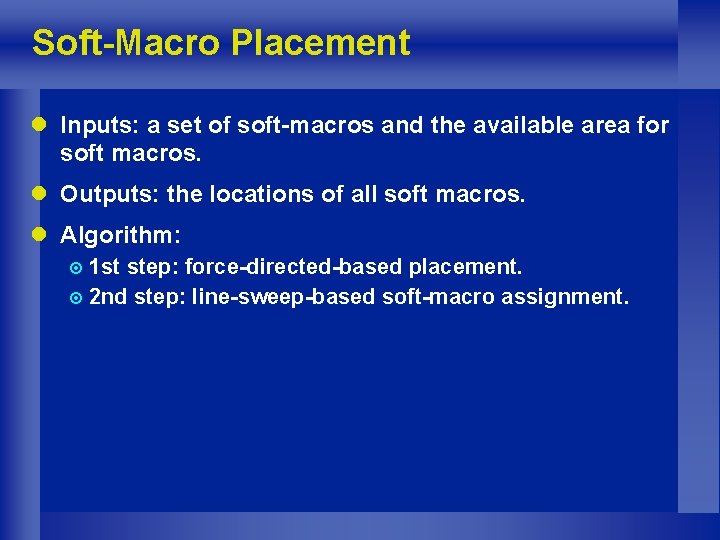

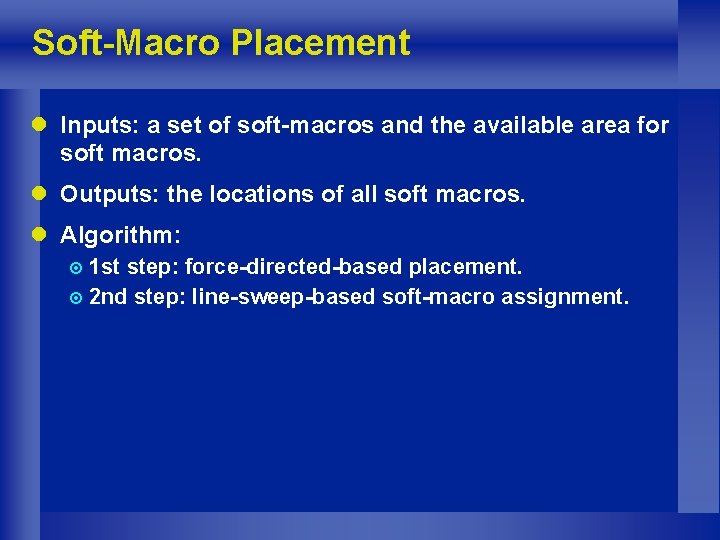

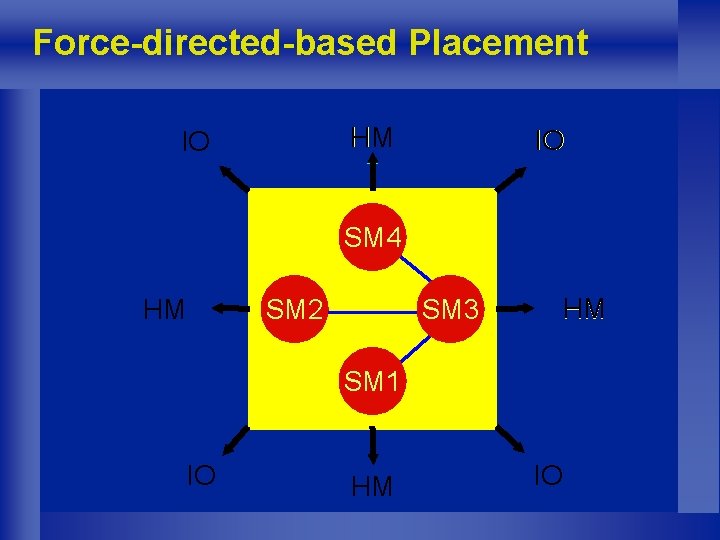

Soft-Macro Placement l Inputs: a set of soft-macros and the available area for soft macros. l Outputs: the locations of all soft macros. l Algorithm: ¤ 1 st step: force-directed-based placement. ¤ 2 nd step: line-sweep-based soft-macro assignment.

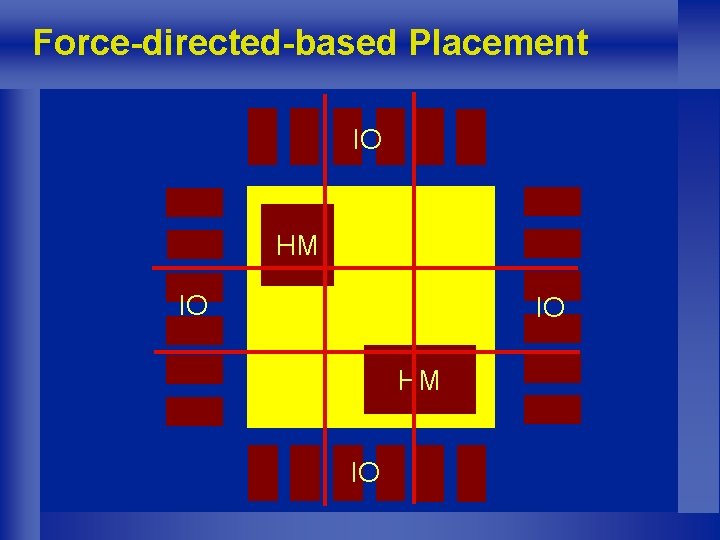

Force-directed-based Placement IO HM IO

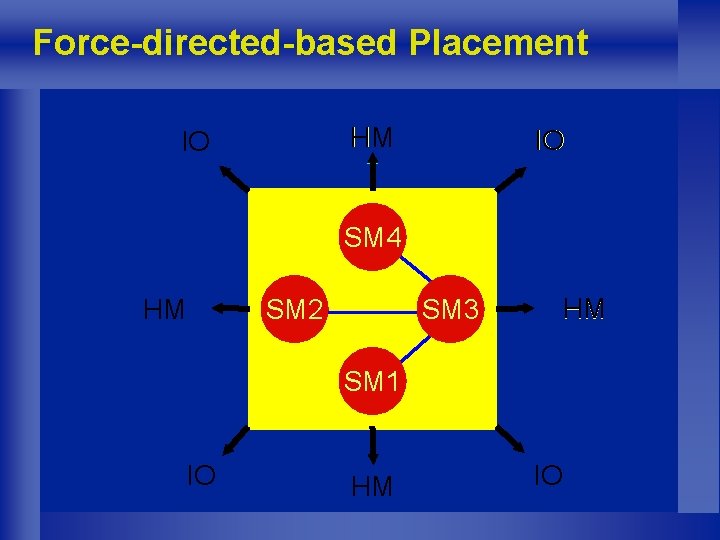

Force-directed-based Placement HM IO IO SM 4 HM SM 2 SM 3 HM SM 1 IO HM IO

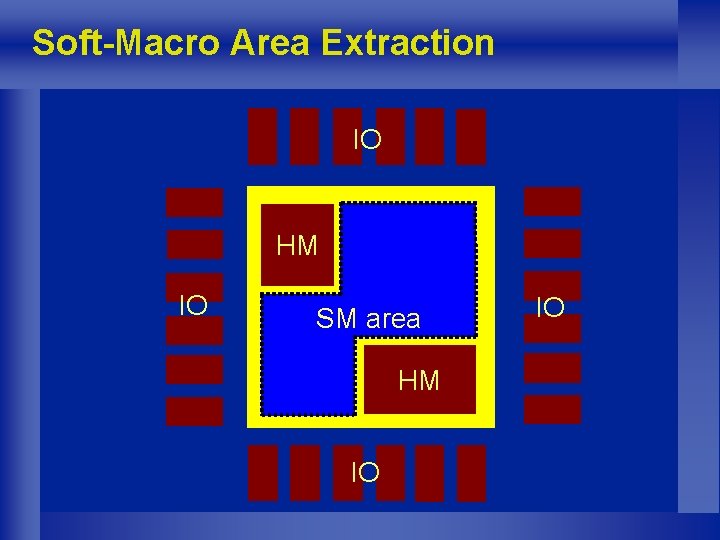

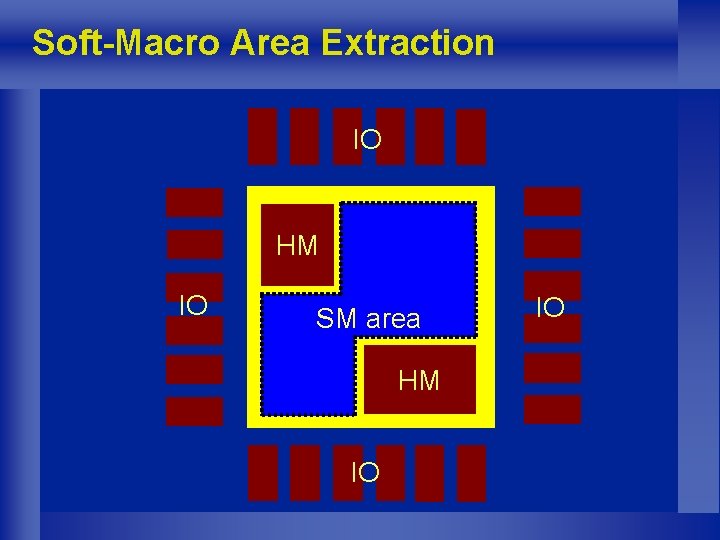

Soft-Macro Area Extraction IO HM IO SM area HM IO IO

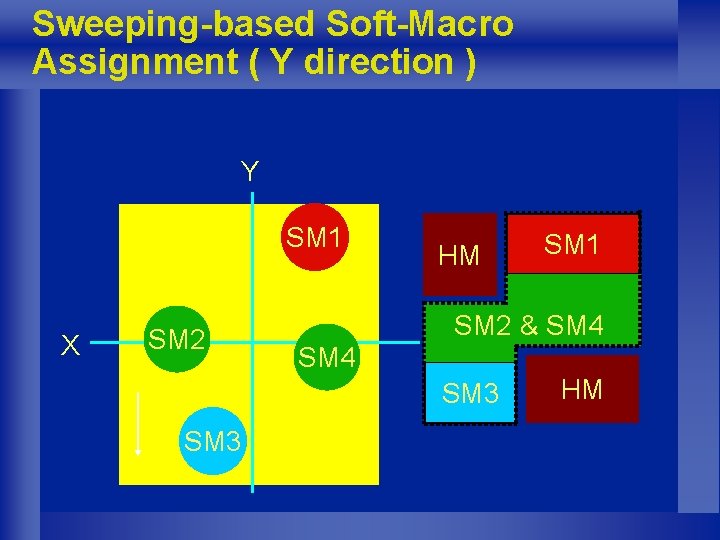

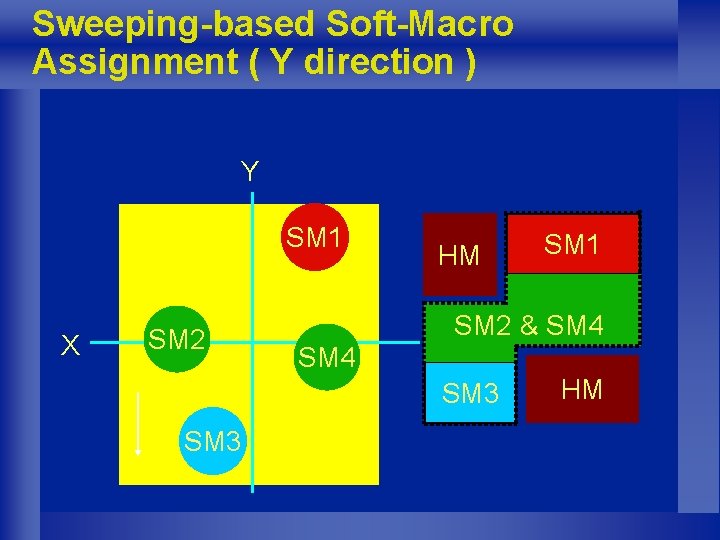

Sweeping-based Soft-Macro Assignment ( Y direction ) Y SM 1 X SM 2 HM SM 2 SM 4 SM & area SM 4 SM 3 SM 1 HM

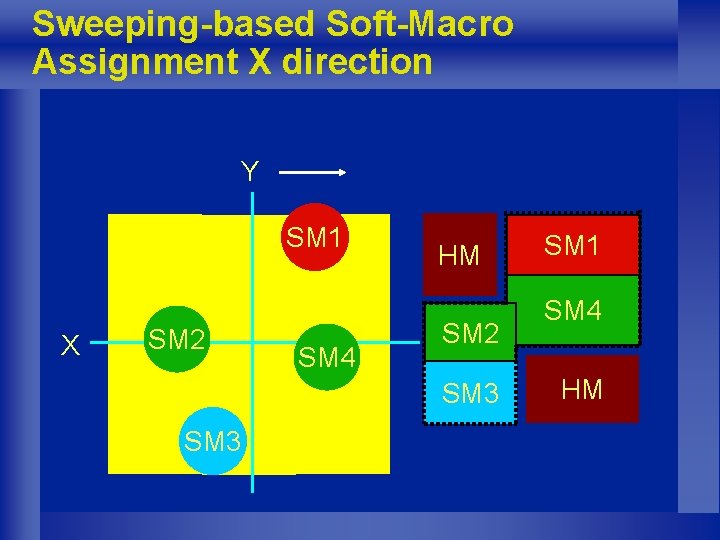

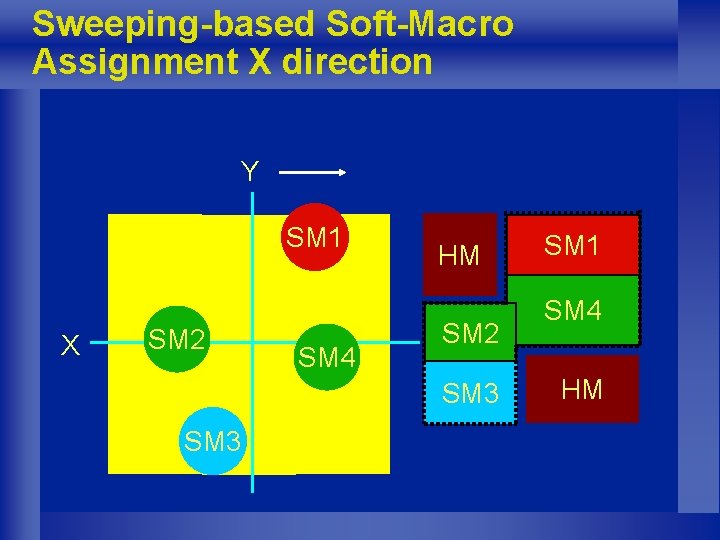

Sweeping-based Soft-Macro Assignment X direction Y SM 1 X SM 2 SM 4 HM SM 4 SM area SM 2 SM 3 SM 1 HM

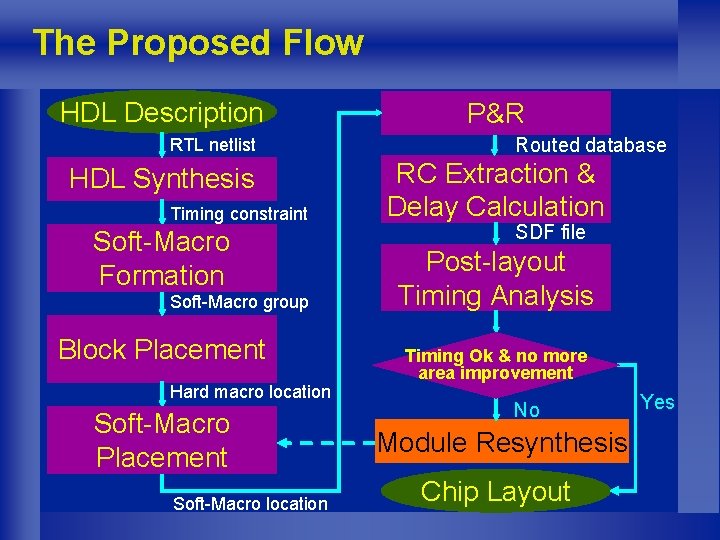

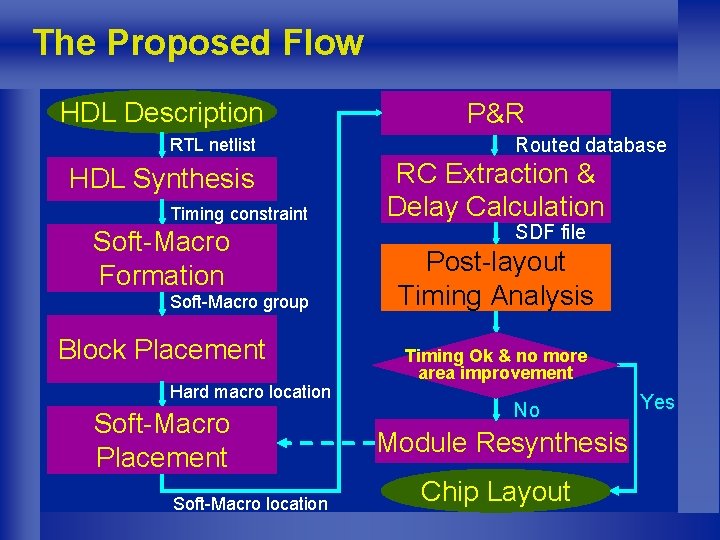

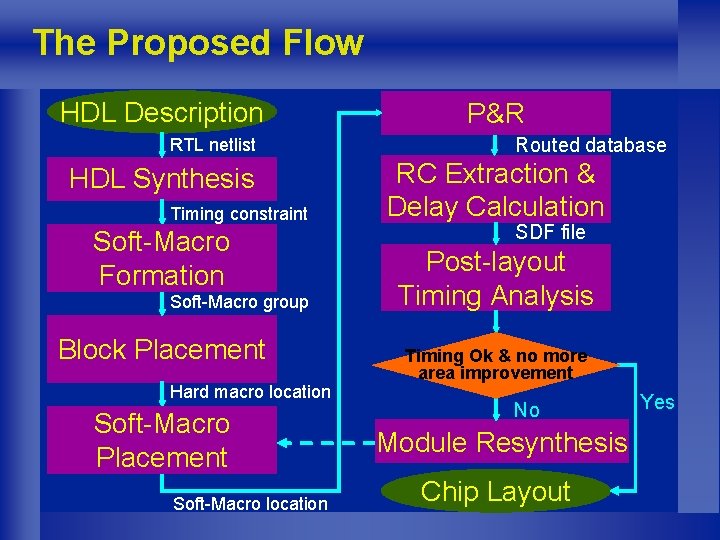

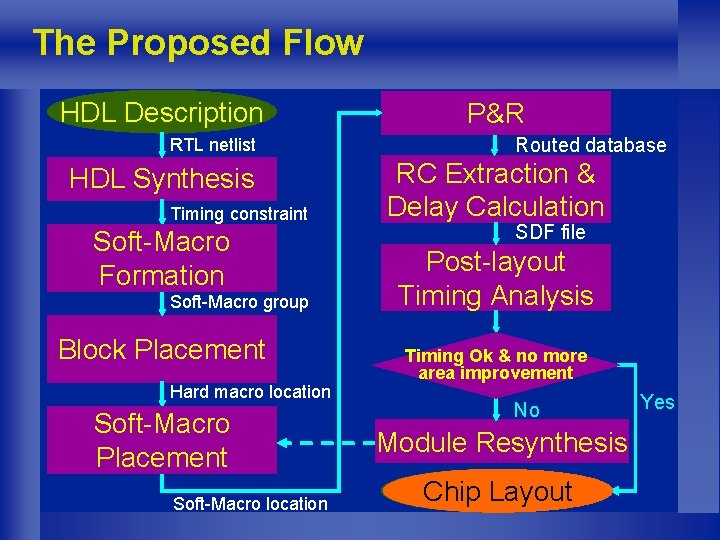

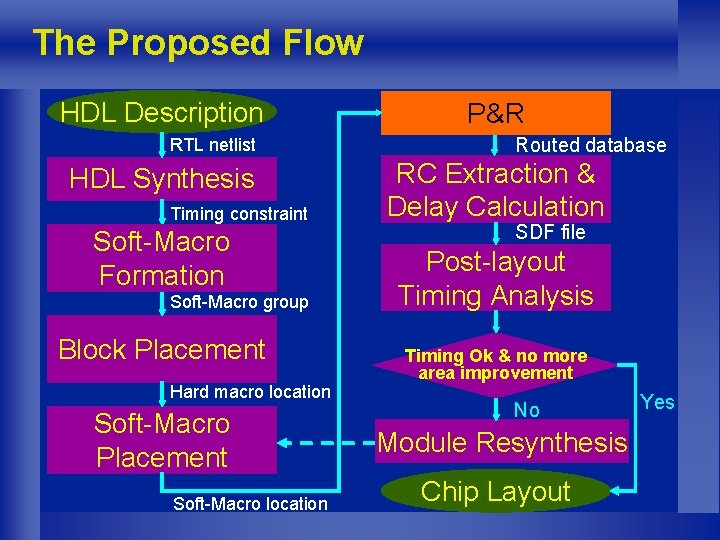

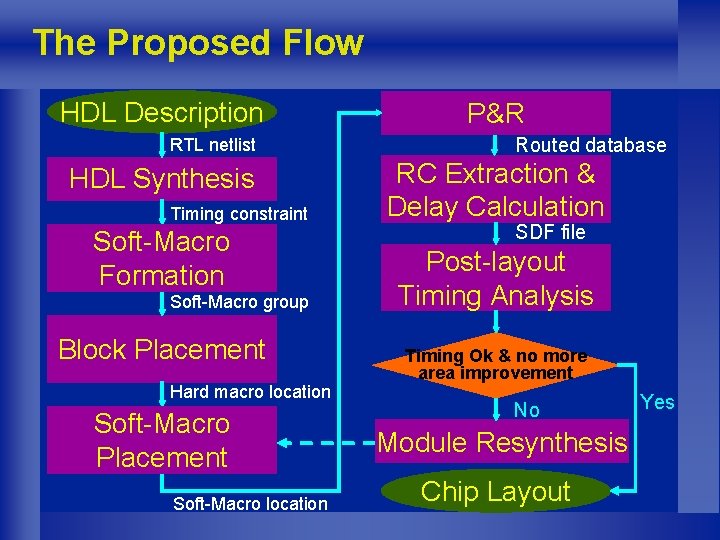

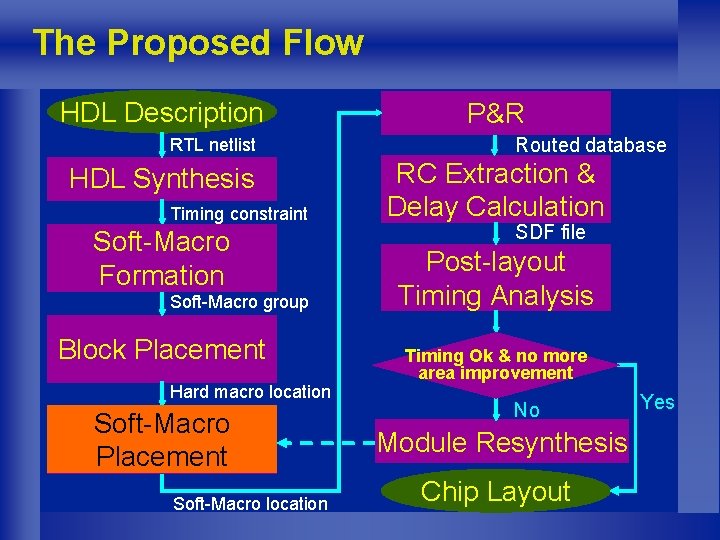

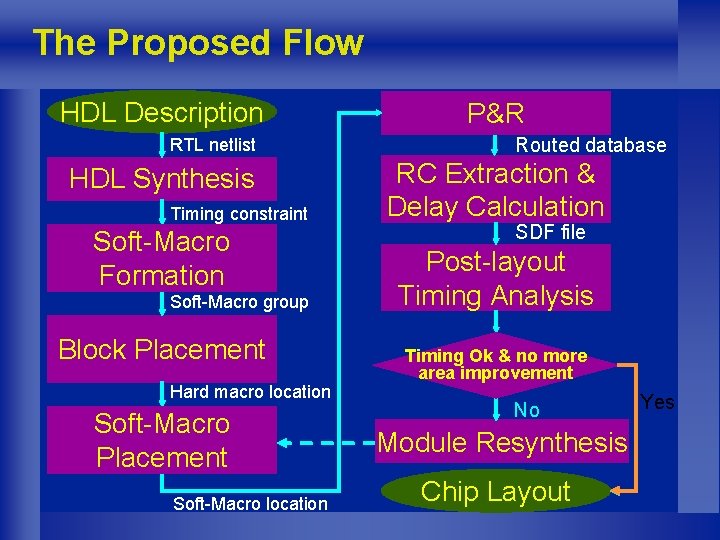

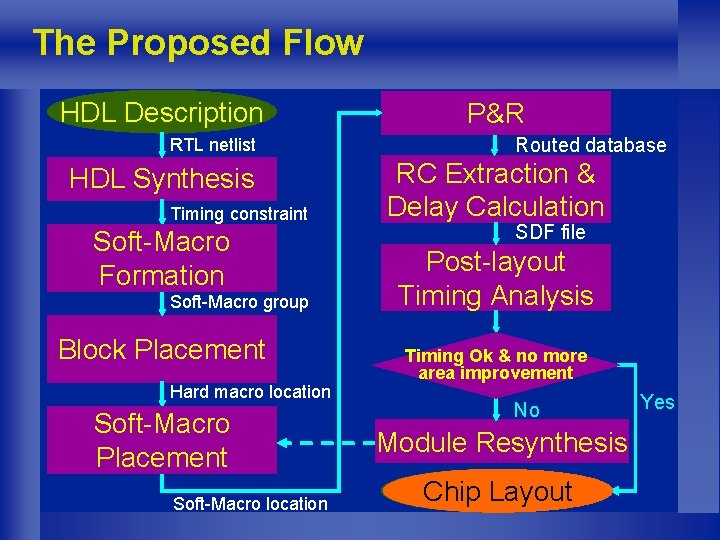

The Proposed Flow HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

The Proposed Flow HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

The Proposed Flow HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

The Proposed Flow HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

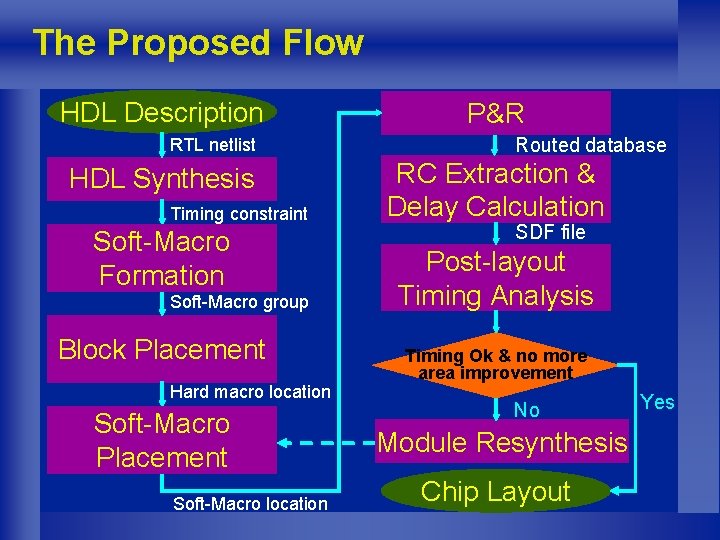

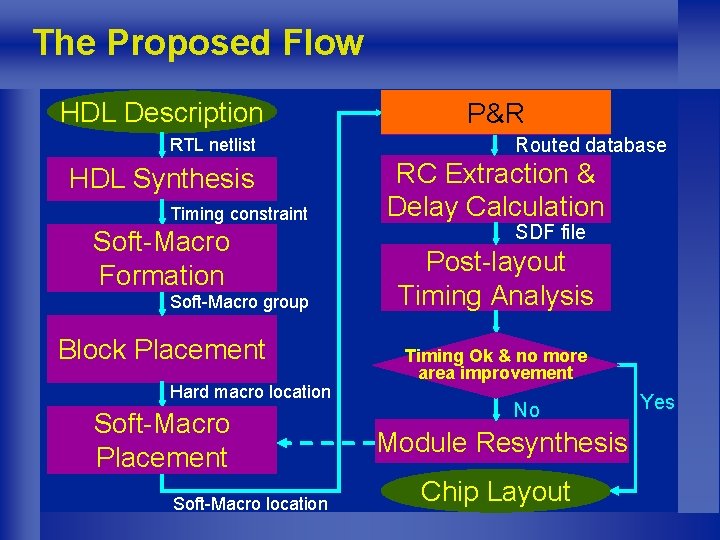

The Proposed Flow HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

The Proposed Flow HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

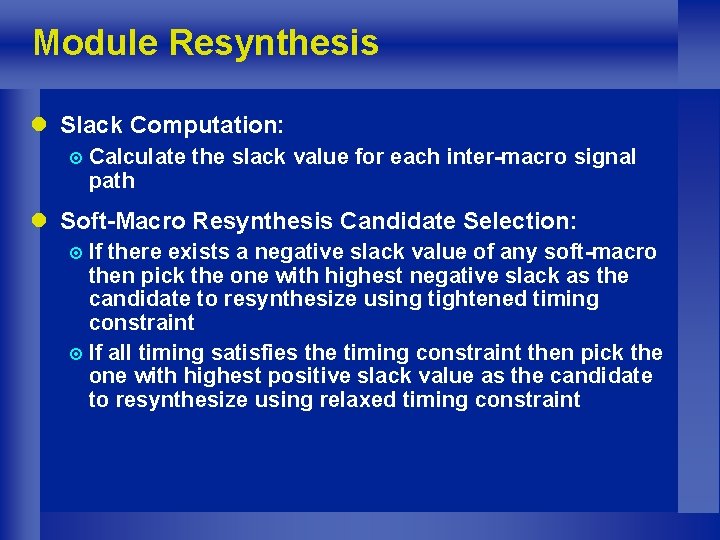

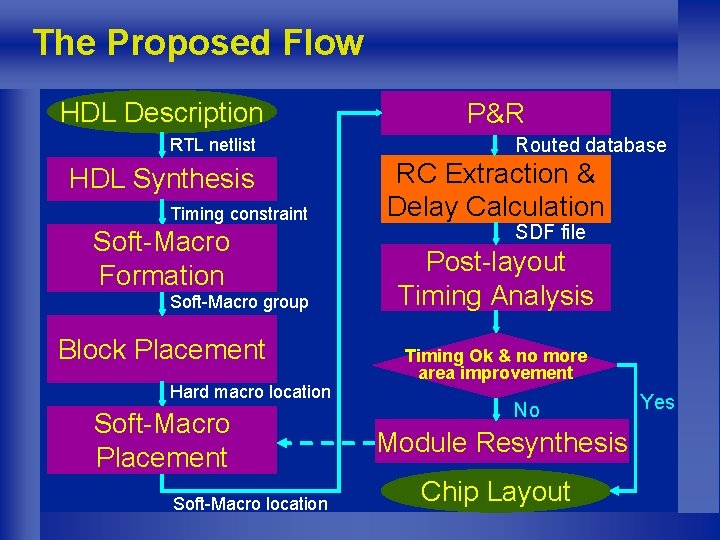

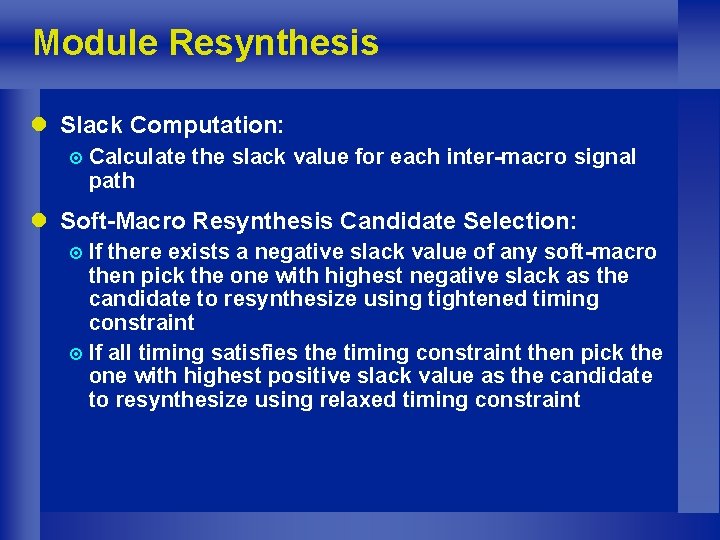

Module Resynthesis l Slack Computation: ¤ Calculate path the slack value for each inter-macro signal l Soft-Macro Resynthesis Candidate Selection: ¤ If there exists a negative slack value of any soft-macro then pick the one with highest negative slack as the candidate to resynthesize using tightened timing constraint ¤ If all timing satisfies the timing constraint then pick the one with highest positive slack value as the candidate to resynthesize using relaxed timing constraint

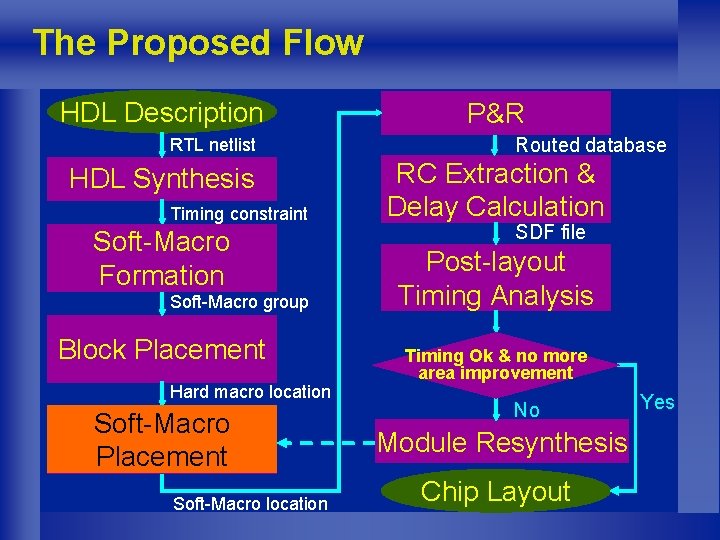

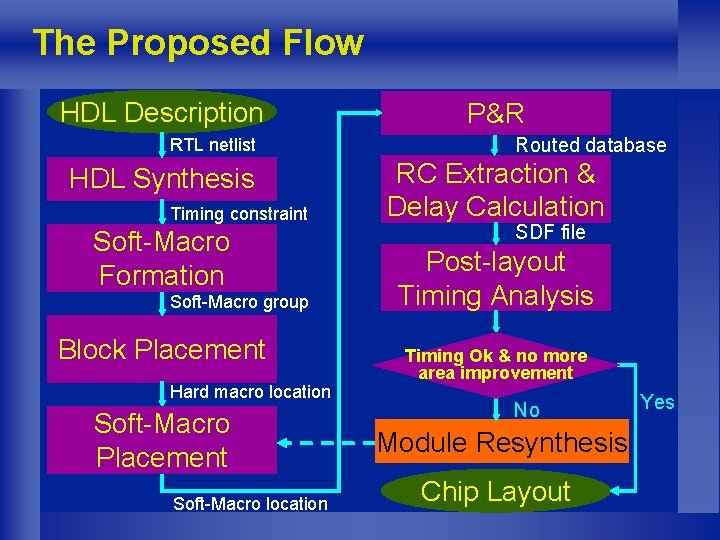

The Proposed Flow HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

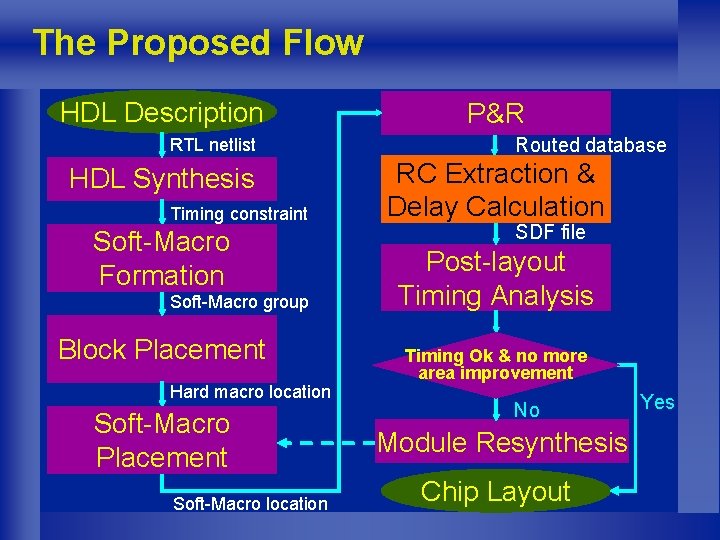

The Proposed Flow HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

The Proposed Flow HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

The Proposed Flow HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

The Proposed Flow HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

The Proposed Flow HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

The Proposed Flow HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

The Proposed Flow HDL Description RTL netlist HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Block Placement Hard macro location Soft-Macro Placement Soft-Macro location P&R Routed database RC Extraction & Delay Calculation SDF file Post-layout Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

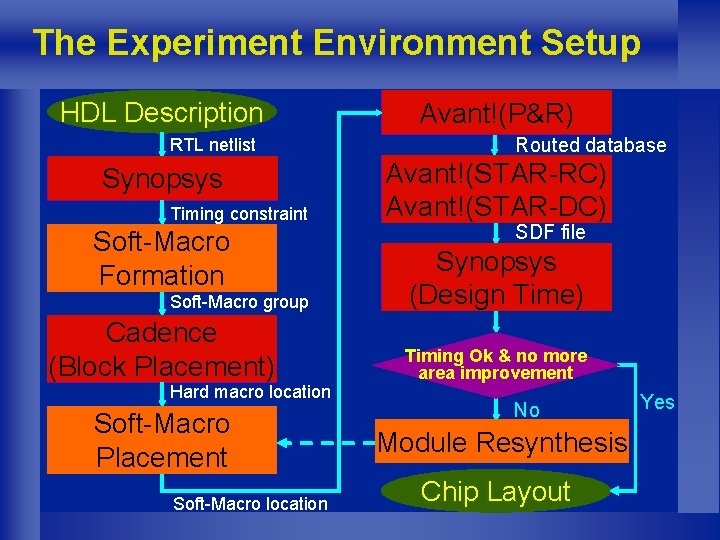

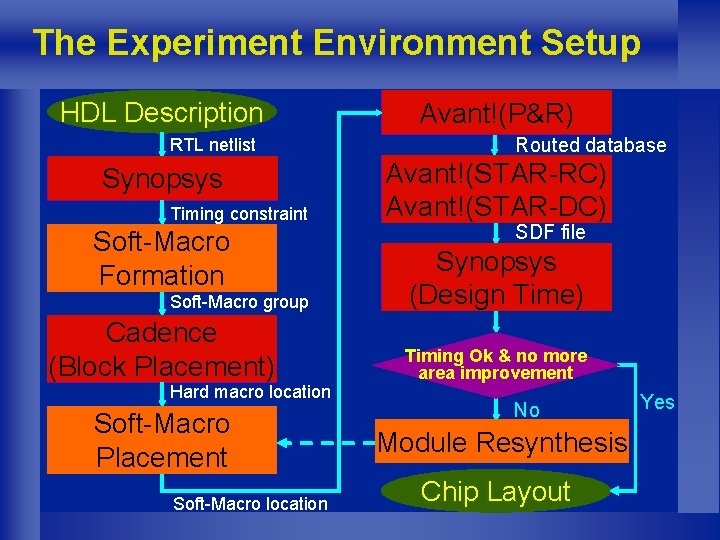

The Experiment Environment Setup HDL Description RTL netlist Synopsys HDL Synthesis Timing constraint Soft-Macro Formation Soft-Macro group Cadence Block Placement (Block Placement) Hard macro location Soft-Macro Placement Soft-Macro location Avant!(P&R) P&R Routed database Avant!(STAR-RC) RC Extraction & Avant!(STAR-DC) Delay Calculation SDF file Synopsys Post-layout (Design Time) Timing Analysis Timing Ok & no more area improvement No Module Resynthesis Chip Layout Yes

Benchmarks

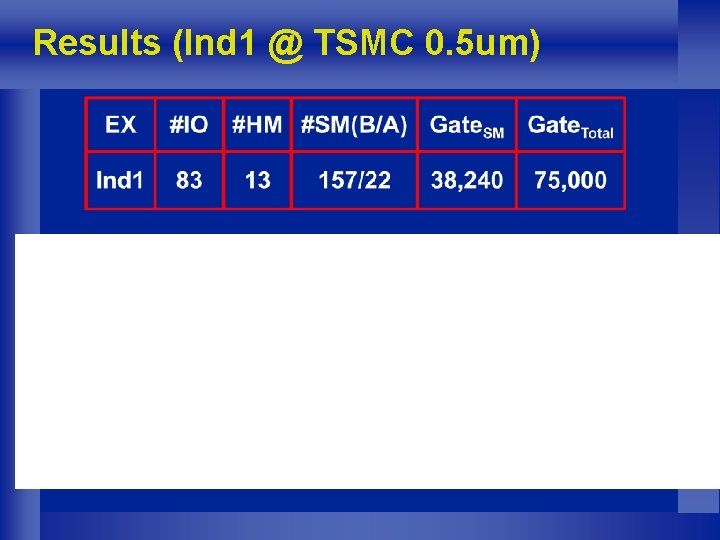

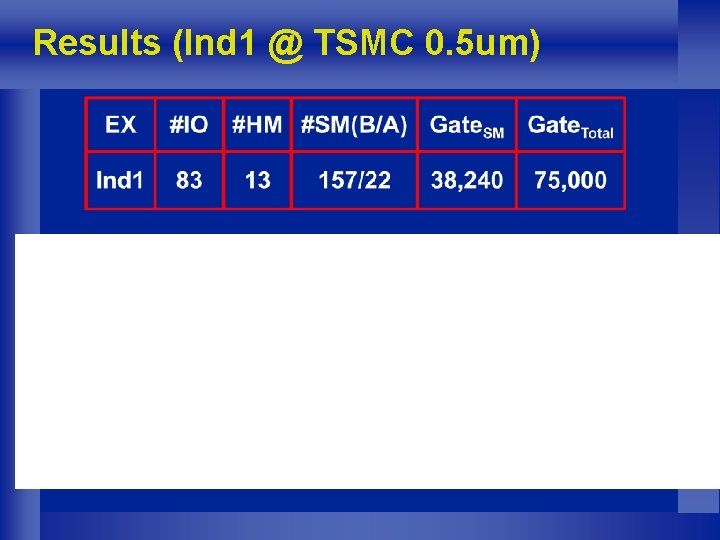

Results (Ind 1 @ TSMC 0. 5 um)

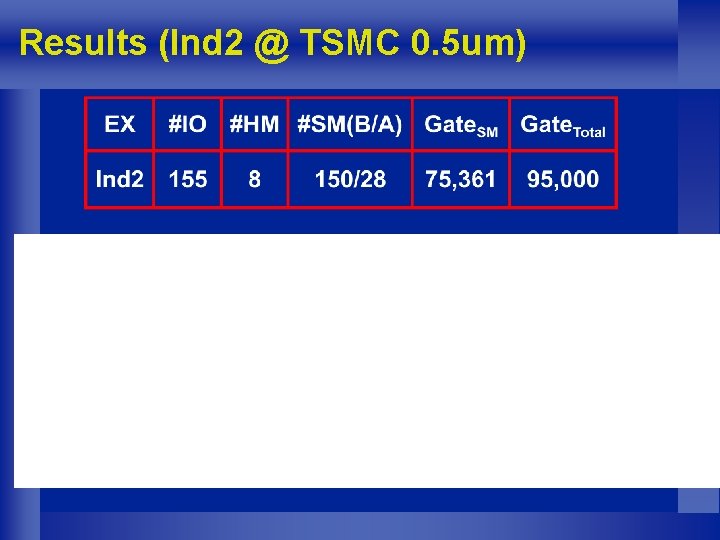

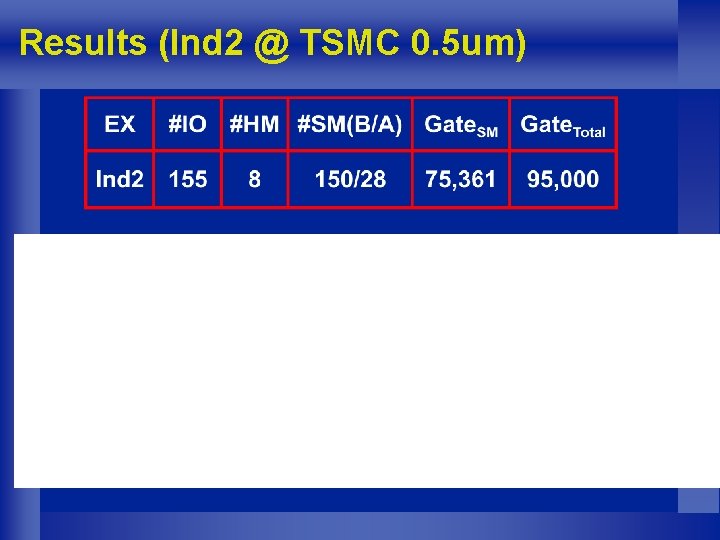

Results (Ind 2 @ TSMC 0. 5 um)

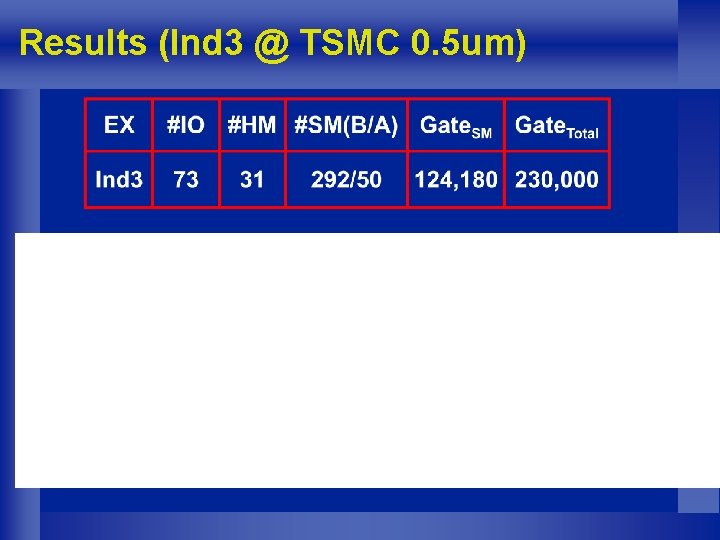

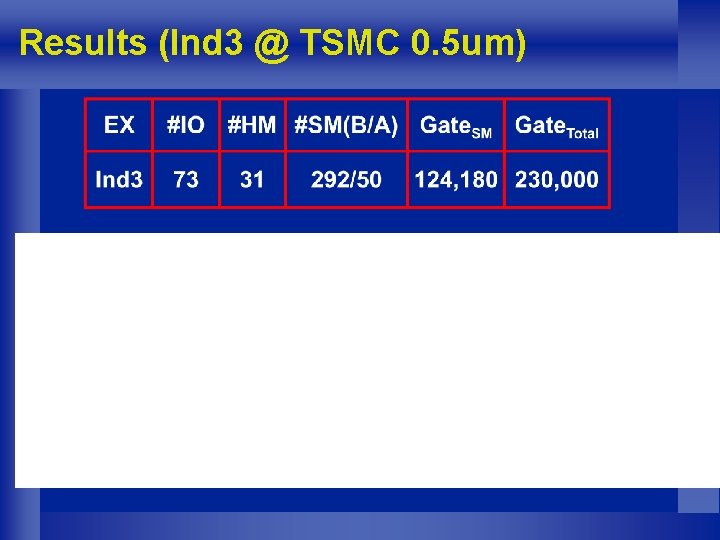

Results (Ind 3 @ TSMC 0. 5 um)

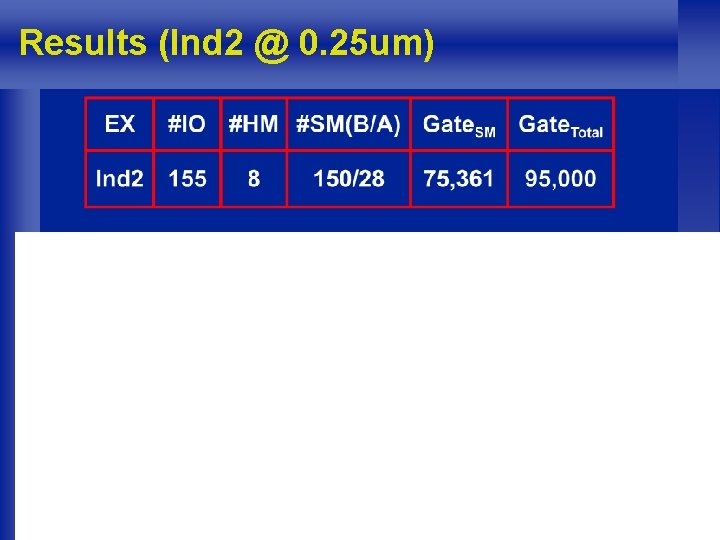

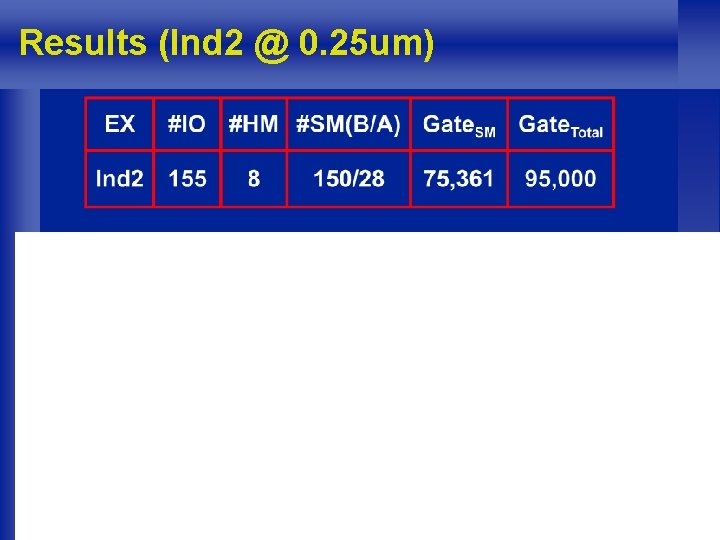

Results (Ind 2 @ 0. 25 um)

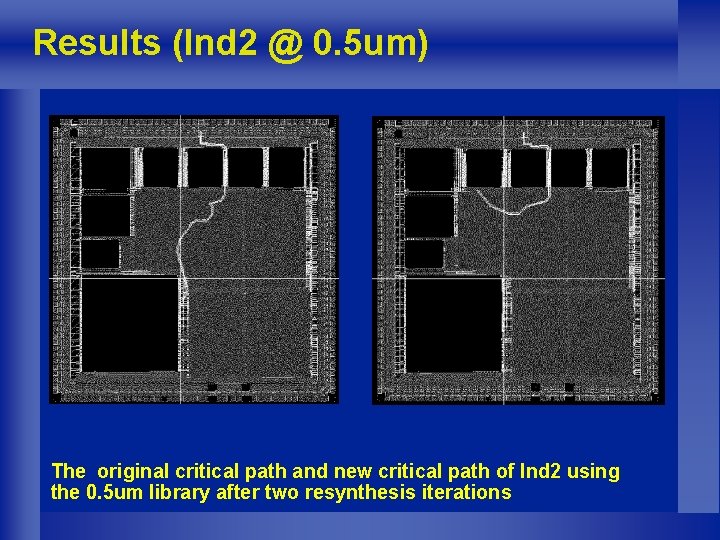

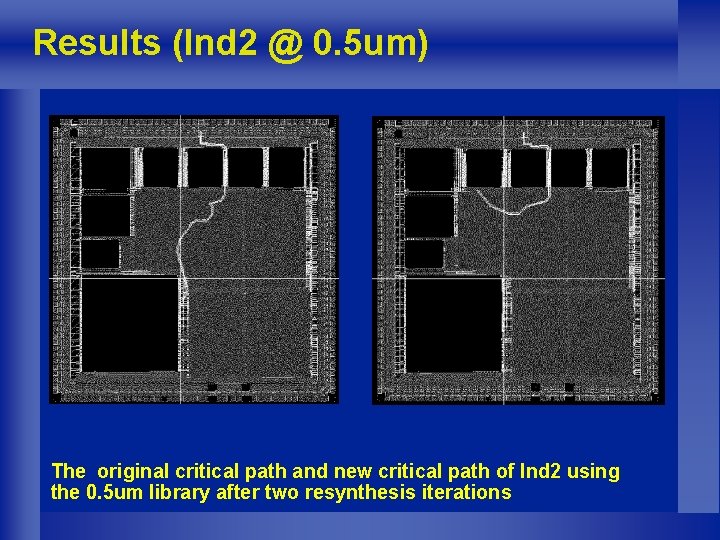

Results (Ind 2 @ 0. 5 um) The original critical path and new critical path of Ind 2 using the 0. 5 um library after two resynthesis iterations

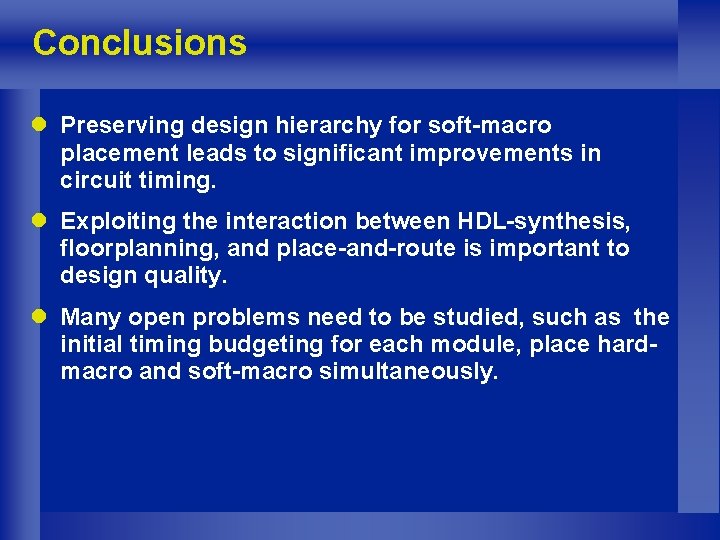

Conclusions l Preserving design hierarchy for soft-macro placement leads to significant improvements in circuit timing. l Exploiting the interaction between HDL-synthesis, floorplanning, and place-and-route is important to design quality. l Many open problems need to be studied, such as the initial timing budgeting for each module, place hardmacro and soft-macro simultaneously.