Robust FPGA Resynthesis Based on FaultTolerant Boolean Matching

Robust FPGA Resynthesis Based on Fault-Tolerant Boolean Matching Yu Hu 1, Zhe Feng 1, Lei He 1 and Rupak Majumdar 2 1 Electrical Engineering Dept. , UCLA 2 Computer Science Dept. , UCLA Presented by Wei-Lun Hung Address comments to lhe@ee. ucla. edu

Outline l Background and Motivation l Preliminaries l Robust Resynthesis Algorithms l Experimental Results l Conclusion and Future Work

Background l Late CMOS scaling reduces device reliability l Single event upset (SEU) due to cosmic rays ¤ Affects ¢ Permanent soft error rate (SER) ¤ Affects ¢ configuration SRAM cells in FPGAs combinational circuits and FFs Transient SER

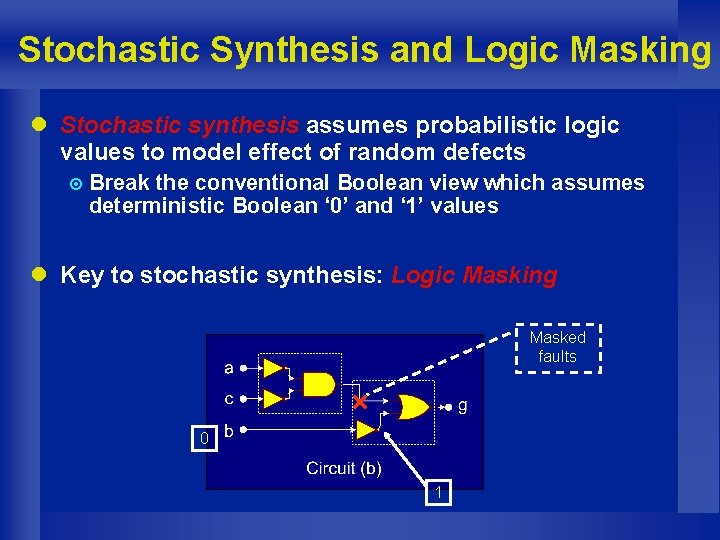

Stochastic Synthesis and Logic Masking l Stochastic synthesis assumes probabilistic logic values to model effect of random defects ¤ Break the conventional Boolean view which assumes deterministic Boolean ‘ 0’ and ‘ 1’ values l Key to stochastic synthesis: Logic Masking Masked faults 0 1

Stochastic Synthesis and Logic Masking (cont. ) l Stochastic Synthesis intelligently places logic masking. l Logic Masking reduces the probability of the propagation of random faults ¤ Maximizes the stochastic yield l However, logic synthesis to maximize yield rate w/o explicit redundancy and testing has not been studied for fault tolerance! l Key questions ¤ How much does logic masking affect robustness? ¤ How and where to place logic masking?

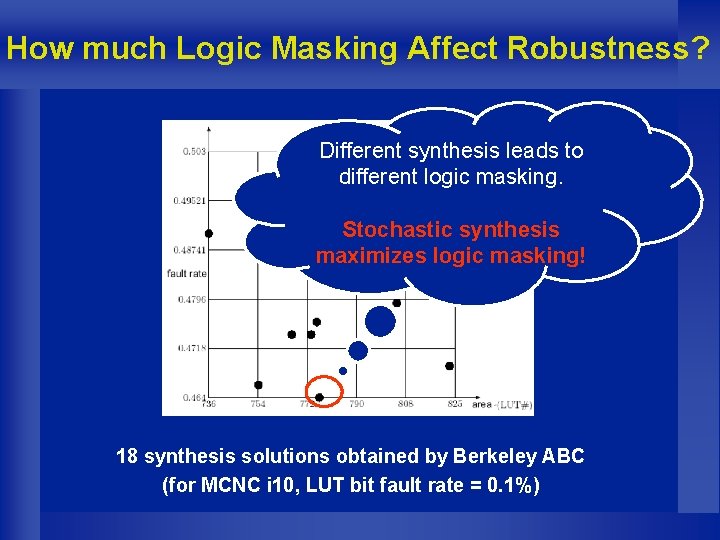

How much Logic Masking Affect Robustness? Different synthesis leads to different logic masking. Stochastic synthesis maximizes logic masking! 18 synthesis solutions obtained by Berkeley ABC (for MCNC i 10, LUT bit fault rate = 0. 1%)

How and Where to Place Logic Masking? — Our Major Contributions l Propose a Robust FPGA resynthesis (ROSE) ¤ Maximize the stochastic yield rate for FPGAs ¤ No need to locate faults ¤ Use the same synthesis for different chips of one FPGA application l Proposed a new PLB template for robustness l ROSE + Robust Template reduces fault rate by 25% with 1% fewer LUTs, and increases MTBF by 31% while preserving the logic depth ¤ compared to Berkeley ABC

Outline l Background l Preliminaries l Robust Resynthesis l Experimental Results l Conclusion and Future Work

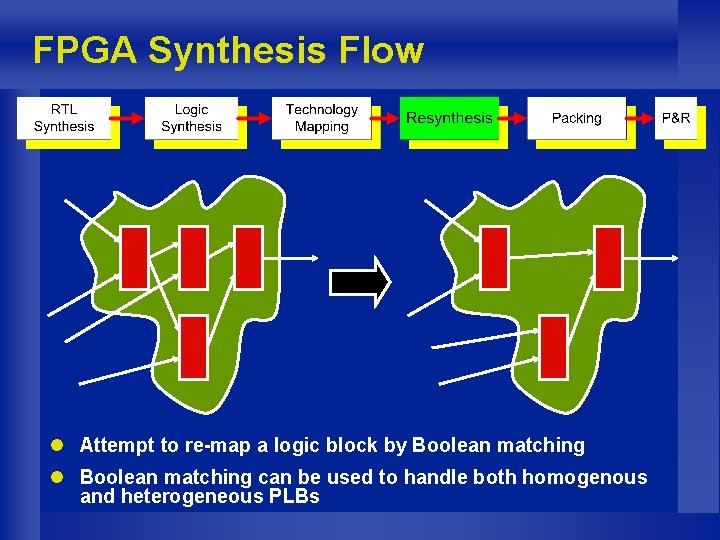

FPGA Synthesis Flow l Attempt to re-map a logic block by Boolean matching l Boolean matching can be used to handle both homogenous and heterogeneous PLBs

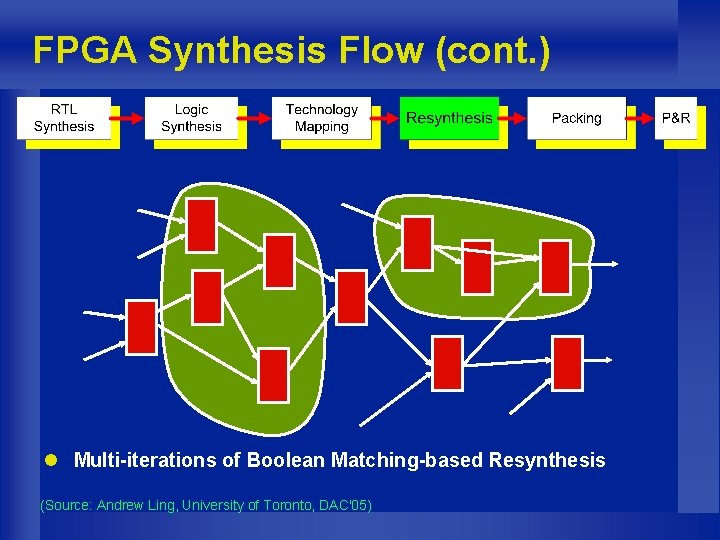

FPGA Synthesis Flow (cont. ) l Multi-iterations of Boolean Matching-based Resynthesis (Source: Andrew Ling, University of Toronto, DAC'05)

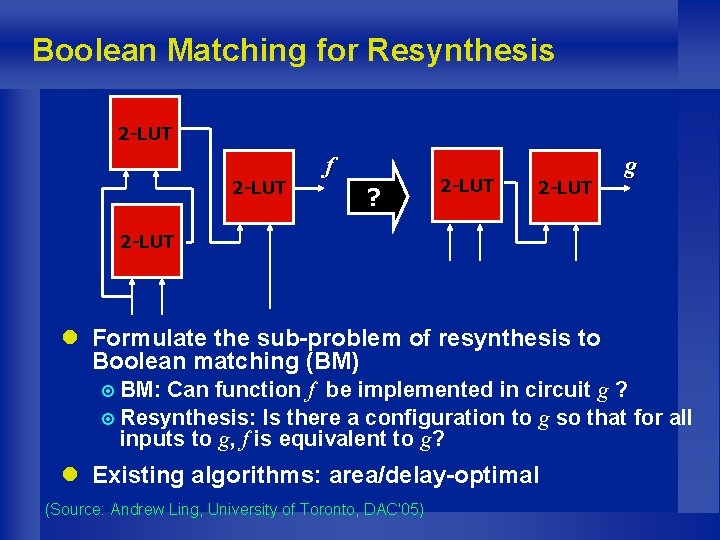

Boolean Matching for Resynthesis 2 -LUT f ? 2 -LUT g 2 -LUT l Formulate the sub-problem of resynthesis to Boolean matching (BM) ¤ BM: Can function f be implemented in circuit g ? ¤ Resynthesis: Is there a configuration to g so that for all inputs to g, f is equivalent to g? l Existing algorithms: area/delay-optimal (Source: Andrew Ling, University of Toronto, DAC'05)

Outline l Background l Preliminaries l Robust Resynthesis ¤ Problem Formulation ¤ FTBM Algorithm ¤ Robust PLB Template l Experimental Results l Conclusion and Future Work

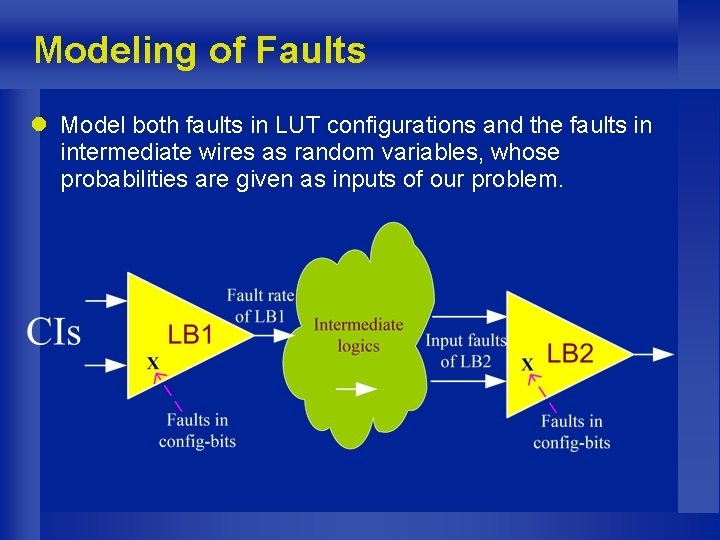

Modeling of Faults l Model both faults in LUT configurations and the faults in intermediate wires as random variables, whose probabilities are given as inputs of our problem.

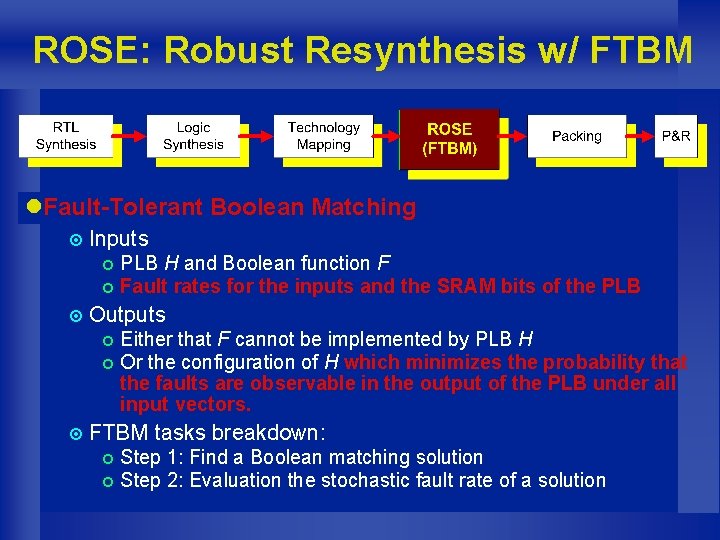

ROSE: Robust Resynthesis w/ FTBM l Boolean Matching l. Fault-Tolerant Boolean Matching ¤ Inputs ¢ ¢ PLB H and Boolean function F Fault rates for the inputs and the SRAM bits of the PLB ¤ Outputs ¢ ¢ Either that F cannot be implemented by PLB H Or the configuration of H which minimizes the probability that the faults are observable in the output of the PLB under all input vectors. ¤ FTBM ¢ ¢ tasks breakdown: Step 1: Find a Boolean matching solution Step 2: Evaluation the stochastic fault rate of a solution

FTBM Step 1: SAT Encoding for FTBM Conjunctive Normal Form (CNF) l If implementable, multiple configurations might exist l The one with minimal fault rate is needed!

FTBM Step 2: Fault Rate Calculation Based on SSAT l Simulation-based fault rate calculation ¤ Not scalable for multiple defects l SAT-based fault rate calculation ¤ Intelligently modeling random defects Deterministic SAT vs. SSAT Deterministic SAT Stochastic SAT

SSAT Encoding for Fault Rate Calculation Faults in intermediate wires Faults in LUT configurations Binary search is performed to find the maximal β

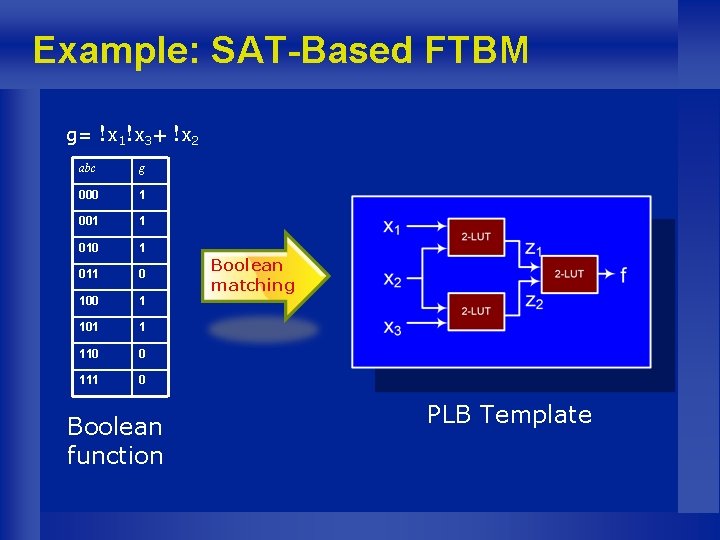

Example: SAT-Based FTBM g= !x 1!x 3+ !x 2 abc g 000 1 001 1 010 1 011 0 100 1 101 1 110 0 111 0 Boolean function Boolean matching PLB Template

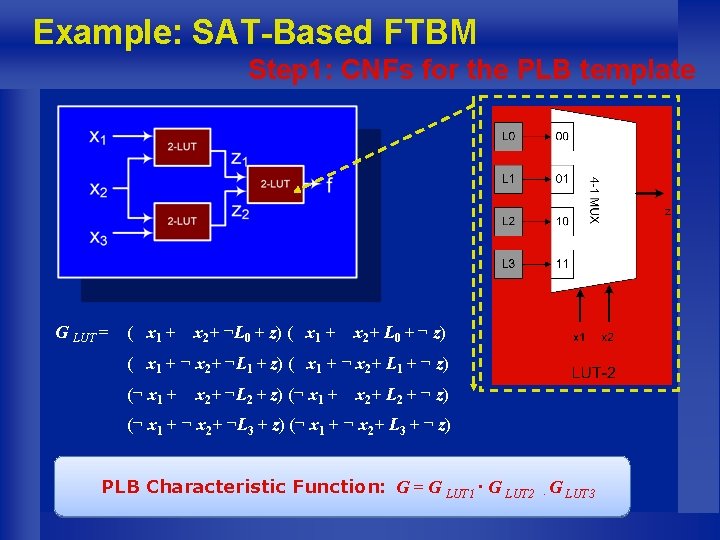

Example: SAT-Based FTBM Step 1: CNFs for the PLB template G LUT = ( x 1 + x 2+ ¬L 0 + z) ( x 1 + x 2+ L 0 + ¬ z) ( x 1 + ¬ x 2+ ¬L 1 + z) ( x 1 + ¬ x 2+ L 1 + ¬ z) (¬ x 1 + x 2+ ¬L 2 + z) (¬ x 1 + x 2+ L 2 + ¬ z) (¬ x 1 + ¬ x 2+ ¬L 3 + z) (¬ x 1 + ¬ x 2+ L 3 + ¬ z) PLB Characteristic Function: G = G LUT 1 · G LUT 2 · G LUT 3

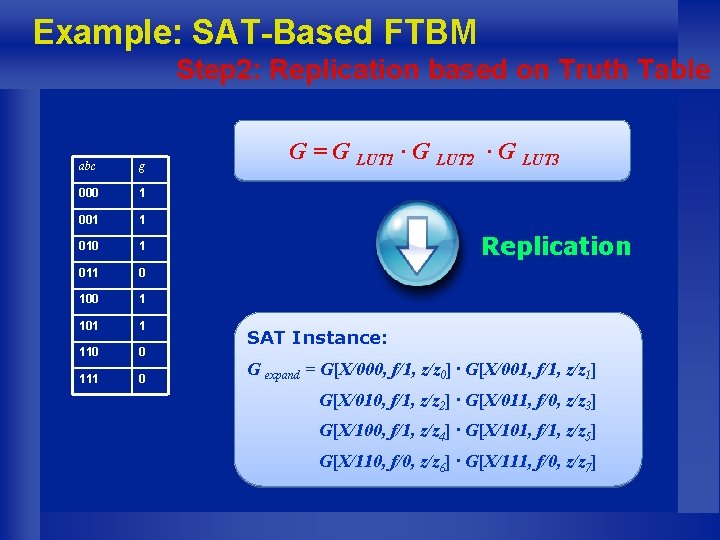

Example: SAT-Based FTBM Step 2: Replication based on Truth Table abc g 000 1 001 1 010 1 011 0 100 1 101 1 110 0 111 0 G = G LUT 1 · G LUT 2 · G LUT 3 Replication SAT Instance: G expand = G[X/000, f/1, z/z 0] · G[X/001, f/1, z/z 1] G[X/010, f/1, z/z 2] · G[X/011, f/0, z/z 3] G[X/100, f/1, z/z 4] · G[X/101, f/1, z/z 5] G[X/110, f/0, z/z 6] · G[X/111, f/0, z/z 7]

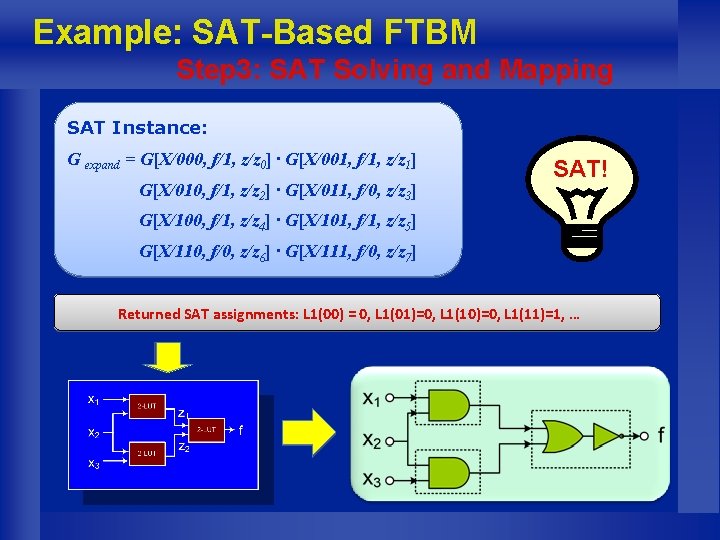

Example: SAT-Based FTBM Step 3: SAT Solving and Mapping SAT Instance: G expand = G[X/000, f/1, z/z 0] · G[X/001, f/1, z/z 1] G[X/010, f/1, z/z 2] · G[X/011, f/0, z/z 3] SAT! G[X/100, f/1, z/z 4] · G[X/101, f/1, z/z 5] G[X/110, f/0, z/z 6] · G[X/111, f/0, z/z 7] Returned SAT assignments: L 1(00) = 0, L 1(01)=0, L 1(10)=0, L 1(11)=1, …

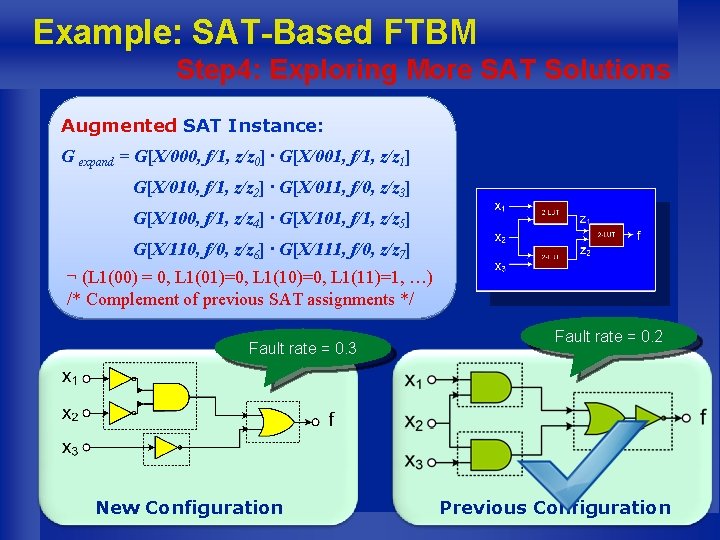

Example: SAT-Based FTBM Step 4: Exploring More SAT Solutions Augmented SAT Instance: G expand = G[X/000, f/1, z/z 0] · G[X/001, f/1, z/z 1] G[X/010, f/1, z/z 2] · G[X/011, f/0, z/z 3] G[X/100, f/1, z/z 4] · G[X/101, f/1, z/z 5] G[X/110, f/0, z/z 6] · G[X/111, f/0, z/z 7] ¬ (L 1(00) = 0, L 1(01)=0, L 1(10)=0, L 1(11)=1, …) /* Complement of previous SAT assignments */ Fault rate = 0. 3 New Configuration Fault rate = 0. 2 Previous Configuration

![PLB Templates for SAT-based Resynthesis l Area efficient templates [A. Ling, DAC’ 05] l PLB Templates for SAT-based Resynthesis l Area efficient templates [A. Ling, DAC’ 05] l](http://slidetodoc.com/presentation_image_h/00465114a4269bdad4c4d76041928454/image-23.jpg)

PLB Templates for SAT-based Resynthesis l Area efficient templates [A. Ling, DAC’ 05] l Proposed robust template w/ path-reconvergence ¤ Can be configured by existing FPGAs

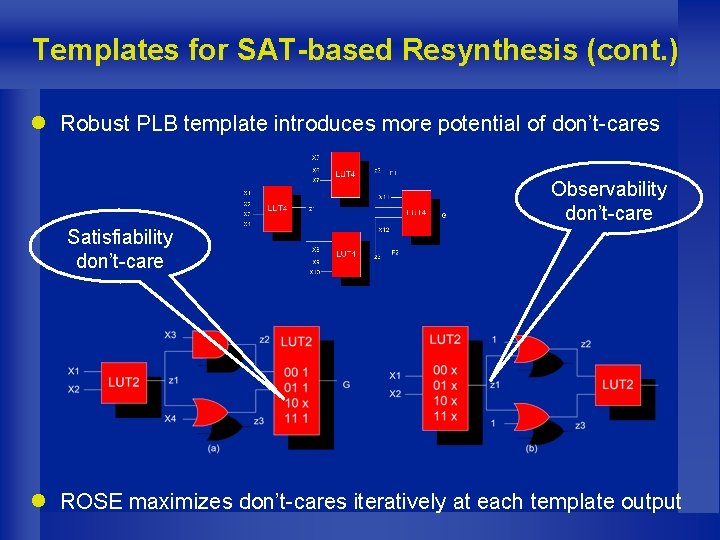

Templates for SAT-based Resynthesis (cont. ) l Robust PLB template introduces more potential of don’t-cares Observability don’t-care Satisfiability don’t-care l ROSE maximizes don’t-cares iteratively at each template output

Outline l Background l Preliminaries l Robust Resynthesis l Experimental Results l Conclusion and Future Work

Experimental Settings l Implementation in OAGear ¤ SAT-BM uses mini. SAT 2. 0 l QUIP benchmarks are tested ¤ Are first mapped with 4 -LUTs by Berkeley ABC l Resynthesis settings ¤ One traversal is performed ¤ Blocks with up to 10 inputs are considered l The fault rate of the chip is calculated by Monte Carlo simulation with 20 K random vectors assuming the single fault l Results are verified by ABC equivalency checkers

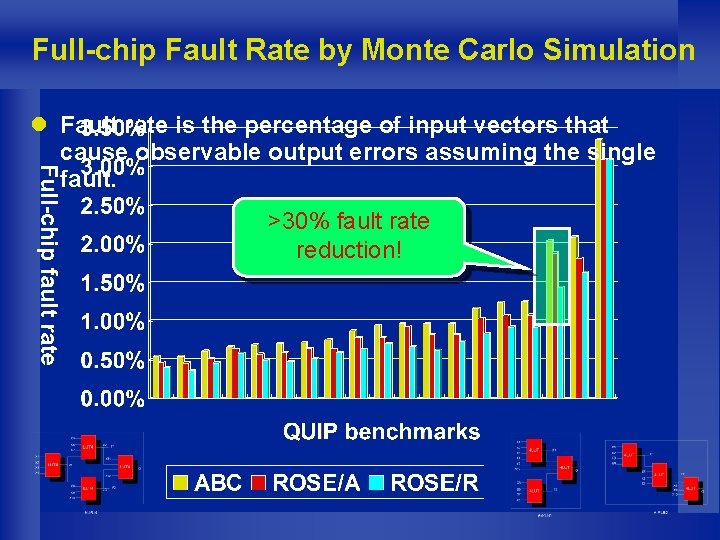

Full-chip Fault Rate by Monte Carlo Simulation l Fault rate is the percentage of input vectors that cause observable output errors assuming the single fault. >30% fault rate reduction!

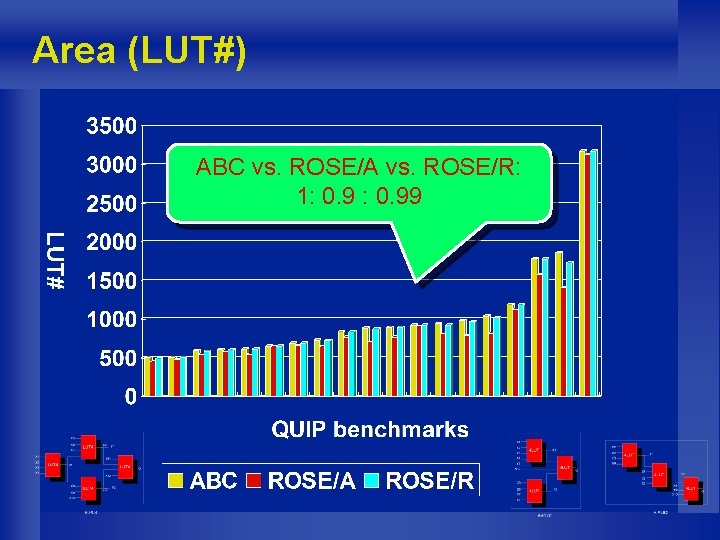

Area (LUT#) ABC vs. ROSE/A vs. ROSE/R: 1: 0. 99

![Estimation of Mean Time Between Failure l SER modeling: [Mukherjee, HPCA, 2005] l Assume Estimation of Mean Time Between Failure l SER modeling: [Mukherjee, HPCA, 2005] l Assume](http://slidetodoc.com/presentation_image_h/00465114a4269bdad4c4d76041928454/image-29.jpg)

Estimation of Mean Time Between Failure l SER modeling: [Mukherjee, HPCA, 2005] l Assume max-size FPGA: 330, 000 LUTs 31% MTBF increase!

Outline l Background l Preliminaries l Robust Resynthesis l Experimental Results l Conclusion and Future Work

Conclusions and Future Work l Developed ROSE and a robust template. ¤ ROSE is an orthogonal approach compared to existing fault-tolerant technique. ¤ Virtually no overhead on power, delay and area l In the future, we will consider ¤ Multiple correlated faults, ¤ Alternative algorithms, ¤ Extension to standard cell-based circuits, ¤ Impacts on testability.

Robust FPGA Resynthesis Based on Fault-Tolerant Boolean Matching Yu Hu, Zhe Feng, Rupak Majumdar and Lei He University of California, Los Angeles

- Slides: 32