SATBased Logic Optimization and Resynthesis Alan Mishchenko Robert

SAT-Based Logic Optimization and Resynthesis Alan Mishchenko Robert Brayton UC Berkeley

Outline • • Motivation for resynthesis Brief history of don’t-cares Our contribution Algorithm overview Algorithm components Experimental results Conclusion 2

Motivation • Several stages of design flow benefit from resynthesis – – post-mapping area optimization critical path synthesis placement-aware resynthesis high-effort technology-independent synthesis • Requirements for a resynthesis engine – substantial logic restructuring – capability to be tuned for solving a variety of optimization tasks – reasonable runtime for large designs • Our solution – SAT-based resynthesis with don’t-cares using resubstitution 3

Brief History of Don’t-Cares • • Previous century work (1960 -2000) Complete rather than compatible don’t-cares (2002) SAT-based don’t-care optimization (2005) Interpolation-based optimization with don’t-cares without explicitly computing don’t-cares (this talk) 4

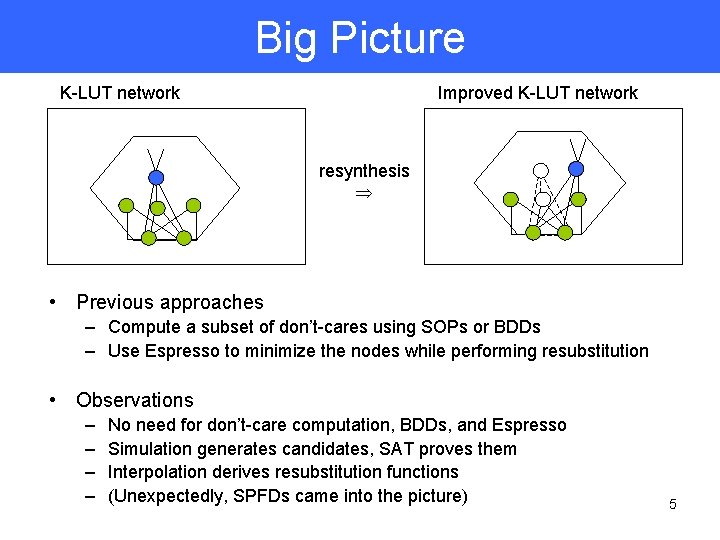

Big Picture K-LUT network Improved K-LUT network resynthesis • Previous approaches – Compute a subset of don’t-cares using SOPs or BDDs – Use Espresso to minimize the nodes while performing resubstitution • Observations – – No need for don’t-care computation, BDDs, and Espresso Simulation generates candidates, SAT proves them Interpolation derives resubstitution functions (Unexpectedly, SPFDs came into the picture) 5

Contributions • Improved SAT-based resubstitution – evaluates multiple candidates simulation and SAT – utilizes internal don’t cares without computing them – derives resubstitution functions via interpolation using SAT solver • Improved windowing – structural analysis avoids non-reconvergent paths, generating windows with more internal flexibilities – new rugged window computation works for large networks containing nodes with multiple fanouts • Experiments on industrial benchmarks 6

Background Summary • Assuming the audience is familiar with: – – – Networks and nodes Cuts and cones Don’t-cares and resubstitution Optimization with don’t-cares Interpolation Structural choices 7

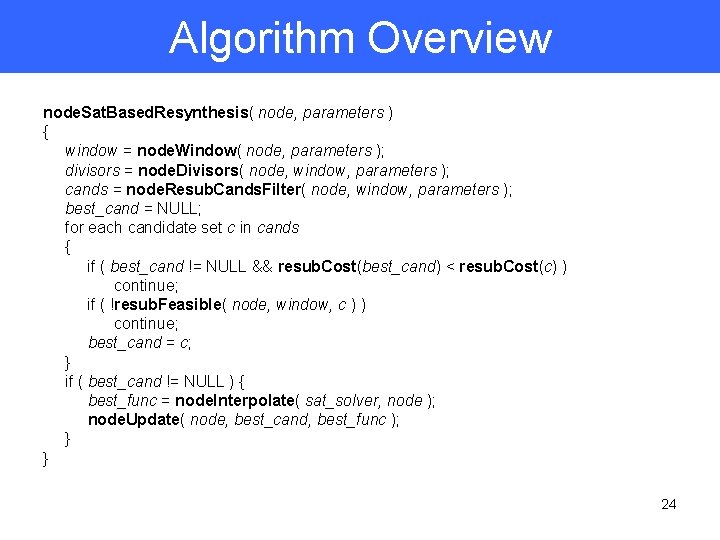

Proposed Algorithm • Consider all or some nodes in some order – – – Windowing Divisor selection Candidate set filtering using simulation Checking resubstitution using SAT Computing resubstitution function Updating the network 8

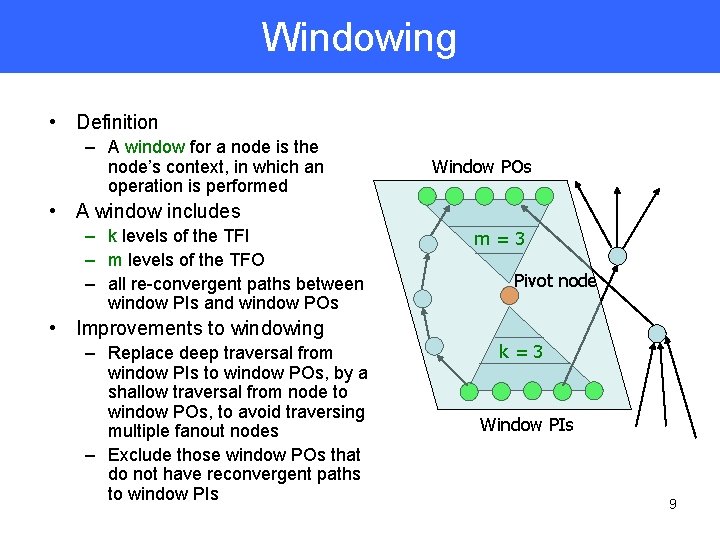

Windowing • Definition – A window for a node is the node’s context, in which an operation is performed Window POs • A window includes – k levels of the TFI – m levels of the TFO – all re-convergent paths between window PIs and window POs • Improvements to windowing – Replace deep traversal from window PIs to window POs, by a shallow traversal from node to window POs, to avoid traversing multiple fanout nodes – Exclude those window POs that do not have reconvergent paths to window PIs m=3 Pivot node k=3 Window PIs 9

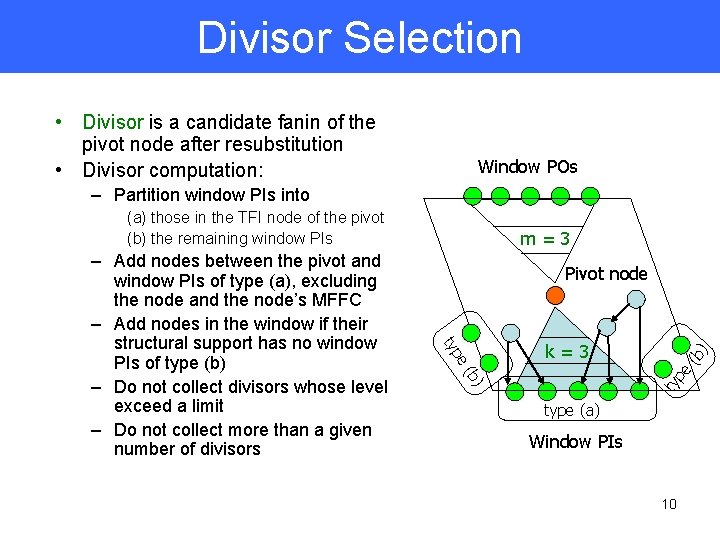

Divisor Selection • Divisor is a candidate fanin of the pivot node after resubstitution • Divisor computation: Window POs – Partition window PIs into (a) those in the TFI node of the pivot (b) the remaining window PIs Pivot node ) (b b) e( k=3 ty pe typ – Add nodes between the pivot and window PIs of type (a), excluding the node and the node’s MFFC – Add nodes in the window if their structural support has no window PIs of type (b) – Do not collect divisors whose level exceed a limit – Do not collect more than a given number of divisors m=3 type (a) Window PIs 10

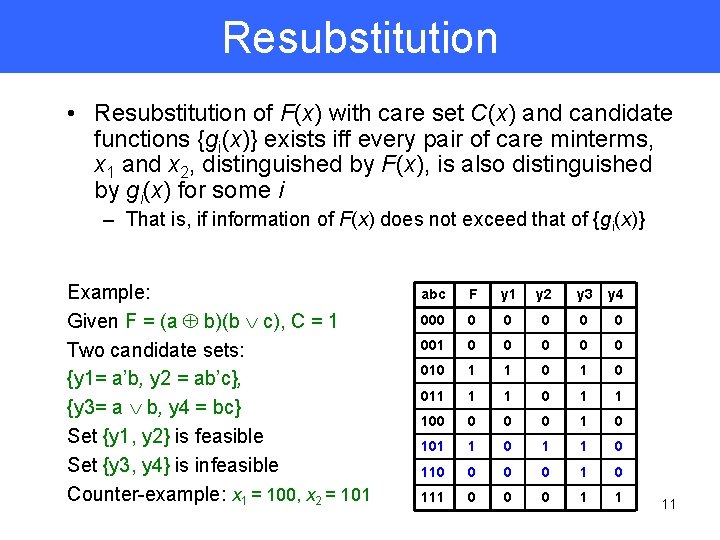

Resubstitution • Resubstitution of F(x) with care set C(x) and candidate functions {gi(x)} exists iff every pair of care minterms, x 1 and x 2, distinguished by F(x), is also distinguished by gi(x) for some i – That is, if information of F(x) does not exceed that of {gi(x)} Example: Given F = (a b)(b c), C = 1 Two candidate sets: {y 1= a’b, y 2 = ab’c}, {y 3= a b, y 4 = bc} Set {y 1, y 2} is feasible Set {y 3, y 4} is infeasible Counter-example: x 1 = 100, x 2 = 101 abc F y 1 y 2 y 3 y 4 000 0 0 001 0 0 010 1 1 0 011 1 1 0 1 1 100 0 1 0 101 1 0 110 0 1 0 111 0 0 0 1 1 11

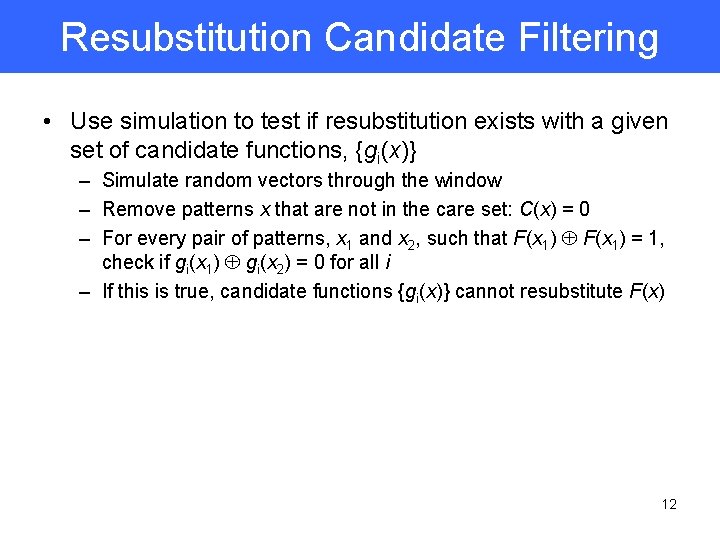

Resubstitution Candidate Filtering • Use simulation to test if resubstitution exists with a given set of candidate functions, {gi(x)} – Simulate random vectors through the window – Remove patterns x that are not in the care set: C(x) = 0 – For every pair of patterns, x 1 and x 2, such that F(x 1) = 1, check if gi(x 1) gi(x 2) = 0 for all i – If this is true, candidate functions {gi(x)} cannot resubstitute F(x) 12

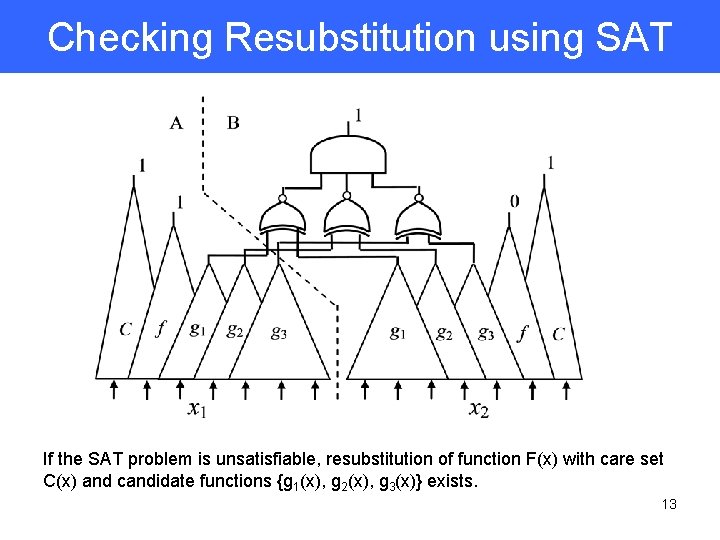

Checking Resubstitution using SAT If the SAT problem is unsatisfiable, resubstitution of function F(x) with care set C(x) and candidate functions {g 1(x), g 2(x), g 3(x)} exists. 13

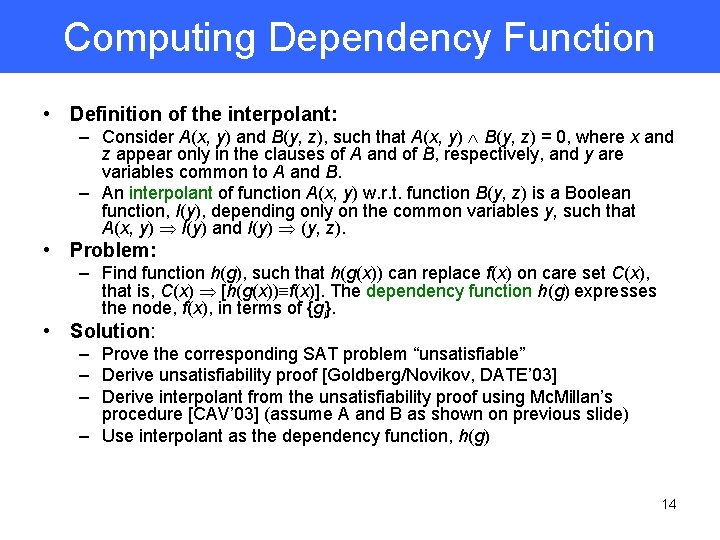

Computing Dependency Function • Definition of the interpolant: – Consider A(x, y) and B(y, z), such that A(x, y) B(y, z) = 0, where x and z appear only in the clauses of A and of B, respectively, and y are variables common to A and B. – An interpolant of function A(x, y) w. r. t. function B(y, z) is a Boolean function, I(y), depending only on the common variables y, such that A(x, y) I(y) and I(y) (y, z). • Problem: – Find function h(g), such that h(g(x)) can replace f(x) on care set C(x), that is, C(x) [h(g(x)) f(x)]. The dependency function h(g) expresses the node, f(x), in terms of {gi}. • Solution: – Prove the corresponding SAT problem “unsatisfiable” – Derive unsatisfiability proof [Goldberg/Novikov, DATE’ 03] – Derive interpolant from the unsatisfiability proof using Mc. Millan’s procedure [CAV’ 03] (assume A and B as shown on previous slide) – Use interpolant as the dependency function, h(g) 14

Resynthesis Heuristics • Resynthesis is attempted for each node • Window, divisors, and resubstitution candidates are computed • Heuristics for different minimization criteria: – Area • Try replacing each fanin whose reference counter is 1 – Net count • Try replacing each fanin – Delay • Try replacing each fanin that is on the critical path 15

Experimental Results • Implementation of SAT-based resynthesis – ABC: Logic synthesis and verification system developed at UC Berkeley – SAT solver used is Mini. Sat-C_v 1. 14. 1 by Niklas Een and Niklas Sörensson • Outline of experiments – Perform technology-independent synthesis: resyn; if – Perform high-quality FPGA mapping: if – Perform resynthesis • without choices: imfs –W 66; imfs –a –W 66; imfs -W 66 • with choices (script is more complicated) – Measure gain in area, delay, net count • Commands used in the scripts – if is a new efficient FPGA mapper based on priority cuts – imfs is the new logic optimization and resynthesis engine described in the present paper, – resyn is a fast logic synthesis script that performs 5 iterations of AIG rewriting, – choice is a logic synthesis script that performs 15 passes of AIG rewriting and collects three snapshots of the current network: the original, the final, and an intermediate AIG saved after the first 5 rewriting passes. • Computer used – ? – Runtime is several minutes for the largest designs in the tables 16

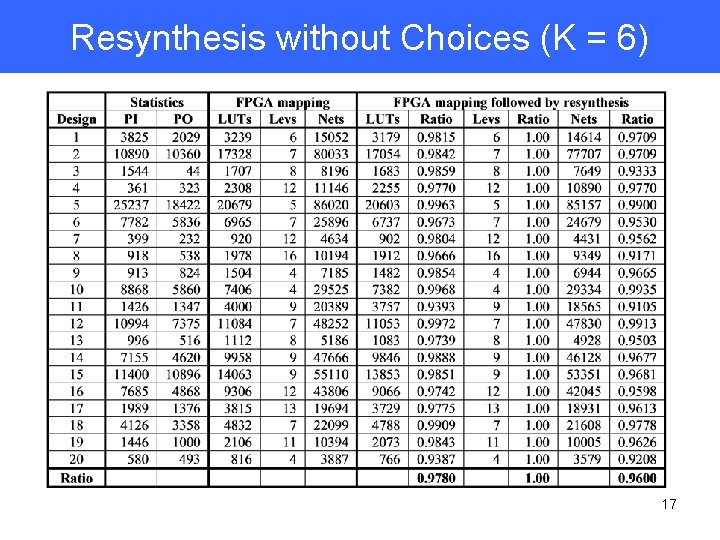

Resynthesis without Choices (K = 6) 17

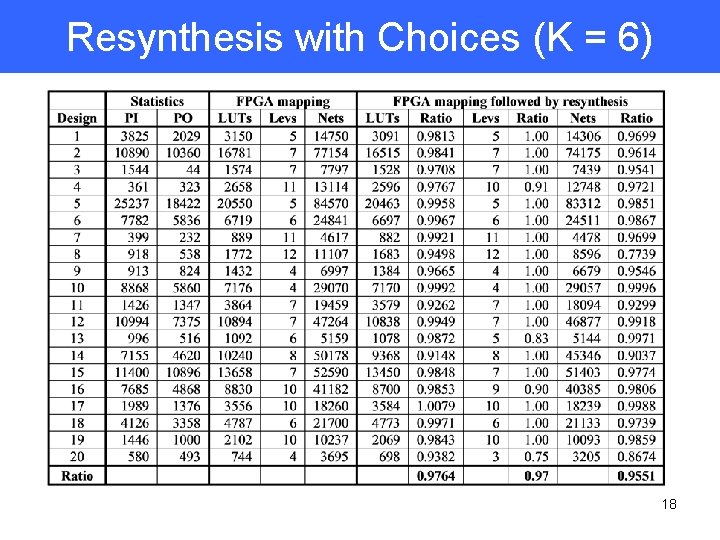

Resynthesis with Choices (K = 6) 18

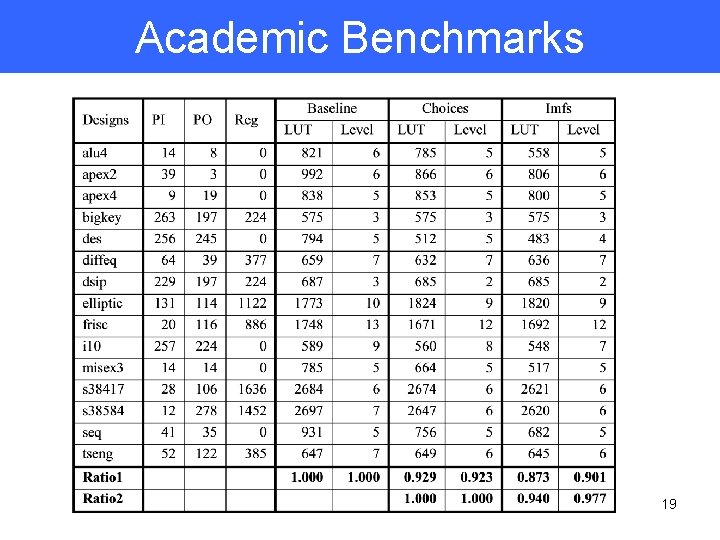

Academic Benchmarks 19

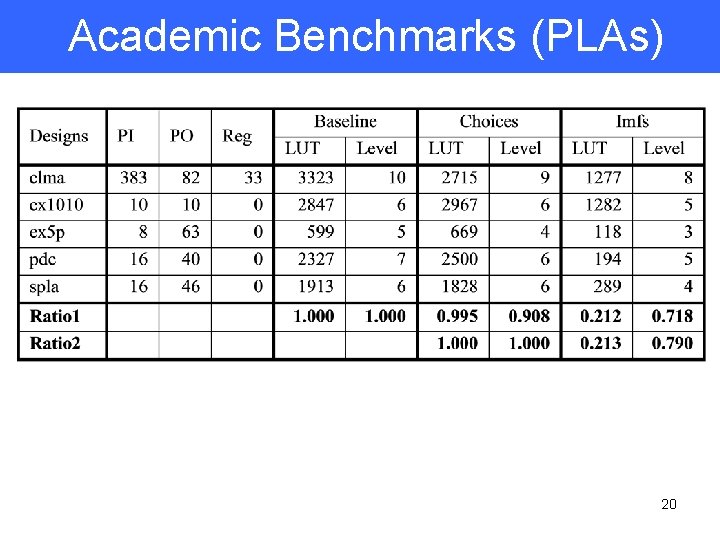

Academic Benchmarks (PLAs) 20

Conclusion • Introduced and motivated resynthesis after mapping • Proposed a new SAT-based solution – uses SAT solver for all aspects of functional manipulation – uses rugged windowing scheme without previous limitations – designed for scalability and applicable to large industrial circuits • Showed promising experimental results – reduction: 2. 0 -2. 4% of area, 0 -3% in delay, 4. 0 -5. 5% in net count – improvements are modest, but on top of a very strong synthesis – more substantial improvements on academic benchmarks • Future work – improving quality by implementing better candidate selection – improving runtime by fine-tuning simulation and SAT – customizing the package for timing-driven resynthesis and rewiring after placement – global circuit restructuring using interpolation 21

The End 22

Potential Applications • Technology-dependent – Resynthesis for LUTs and standard-cells to improve area, delay, power, the number of nets, etc – Timing-driven resynthesis and rewiring after placement • Technology-independent – optimization of logic networks to minimize number of factored form literals – optimization for AIGs to minimize AIG nodes (and record choices) 23

Algorithm Overview node. Sat. Based. Resynthesis( node, parameters ) { window = node. Window( node, parameters ); divisors = node. Divisors( node, window, parameters ); cands = node. Resub. Cands. Filter( node, window, parameters ); best_cand = NULL; for each candidate set c in cands { if ( best_cand != NULL && resub. Cost(best_cand) < resub. Cost(c) ) continue; if ( !resub. Feasible( node, window, c ) ) continue; best_cand = c; } if ( best_cand != NULL ) { best_func = node. Interpolate( sat_solver, node ); node. Update( node, best_cand, best_func ); } } 24

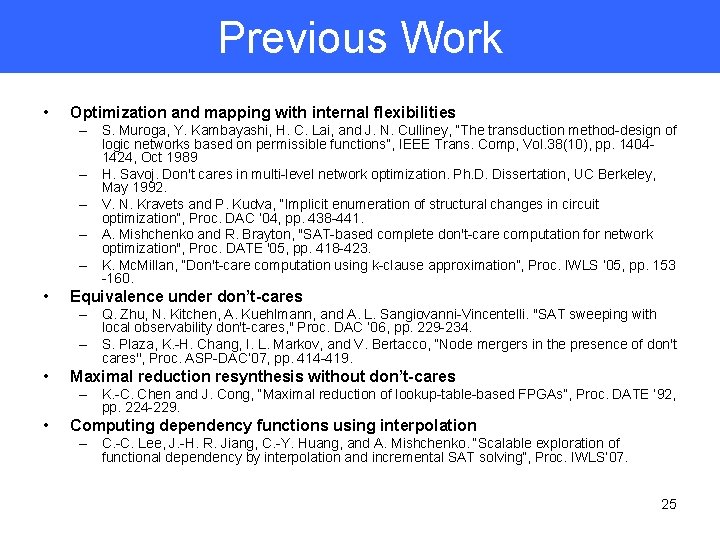

Previous Work • Optimization and mapping with internal flexibilities – S. Muroga, Y. Kambayashi, H. C. Lai, and J. N. Culliney, “The transduction method-design of logic networks based on permissible functions”, IEEE Trans. Comp, Vol. 38(10), pp. 14041424, Oct 1989 – H. Savoj. Don't cares in multi-level network optimization. Ph. D. Dissertation, UC Berkeley, May 1992. – V. N. Kravets and P. Kudva, “Implicit enumeration of structural changes in circuit optimization”, Proc. DAC ’ 04, pp. 438 -441. – A. Mishchenko and R. Brayton, "SAT-based complete don't-care computation for network optimization", Proc. DATE '05, pp. 418 -423. – K. Mc. Millan, “Don't-care computation using k-clause approximation”, Proc. IWLS ’ 05, pp. 153 -160. • Equivalence under don’t-cares – Q. Zhu, N. Kitchen, A. Kuehlmann, and A. L. Sangiovanni-Vincentelli. "SAT sweeping with local observability don't-cares, " Proc. DAC ’ 06, pp. 229 -234. – S. Plaza, K. -H. Chang, I. L. Markov, and V. Bertacco, “Node mergers in the presence of don't cares'', Proc. ASP-DAC’ 07, pp. 414 -419. • Maximal reduction resynthesis without don’t-cares – K. -C. Chen and J. Cong, “Maximal reduction of lookup-table-based FPGAs”, Proc. DATE ’ 92, pp. 224 -229. • Computing dependency functions using interpolation – C. -C. Lee, J. -H. R. Jiang, C. -Y. Huang, and A. Mishchenko. “Scalable exploration of functional dependency by interpolation and incremental SAT solving”, Proc. IWLS’ 07. 25

- Slides: 25