Wykad 8 1 Dr Galina Cariowa Legenda Zezwolenie

- Slides: 59

Wykład № 8 1 Dr Galina Cariowa

Legenda Zezwolenie Dekoder, koder Demultiplekser, multiplekser 2

Bloki funkcjonalne – układy kombinacyjne odpowiadające pewnym funkcjom kombinacyjnym, mającym specjalne znaczenie w projektowaniu układów cyfrowych. 3

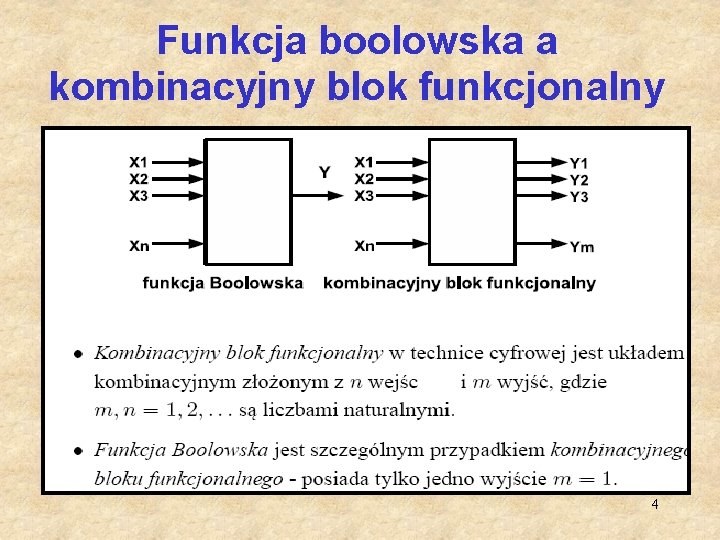

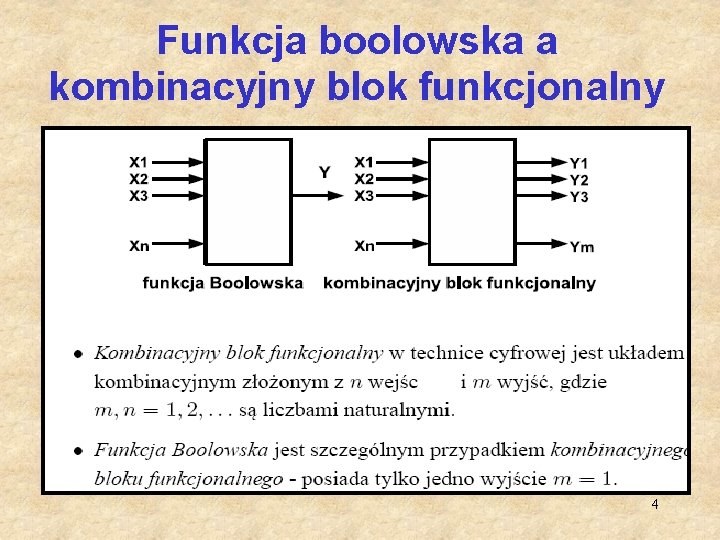

Funkcja boolowska a kombinacyjny blok funkcjonalny 4

Kombinacyjne układy funkcjonalne: - dekodery; - demultipleksery; - kodery; - multipleksery; - i inne. 5

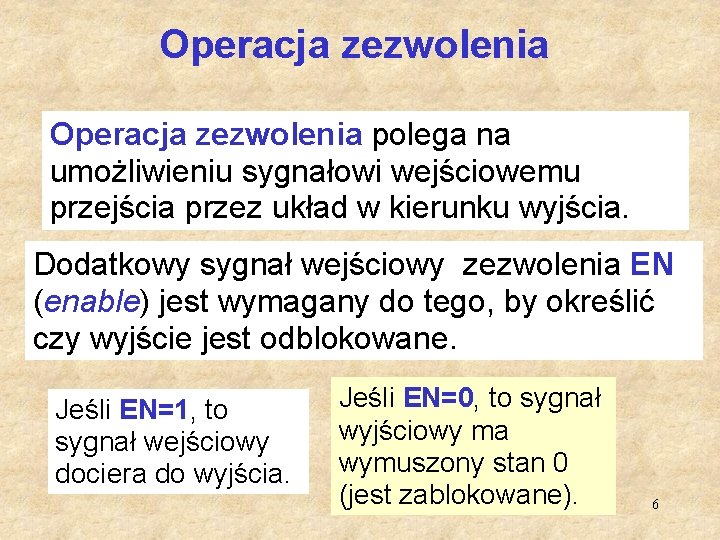

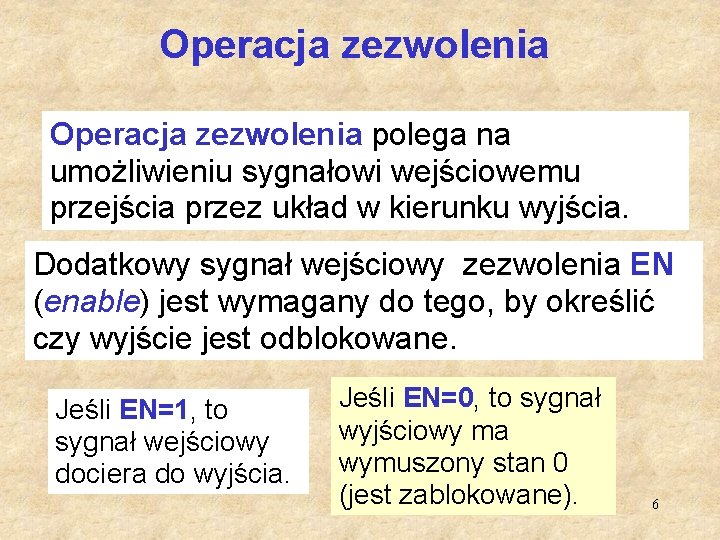

Operacja zezwolenia polega na umożliwieniu sygnałowi wejściowemu przejścia przez układ w kierunku wyjścia. Dodatkowy sygnał wejściowy zezwolenia EN (enable) jest wymagany do tego, by określić czy wyjście jest odblokowane. Jeśli EN=1, to sygnał wejściowy dociera do wyjścia. Jeśli EN=0, to sygnał wyjściowy ma wymuszony stan 0 (jest zablokowane). 6

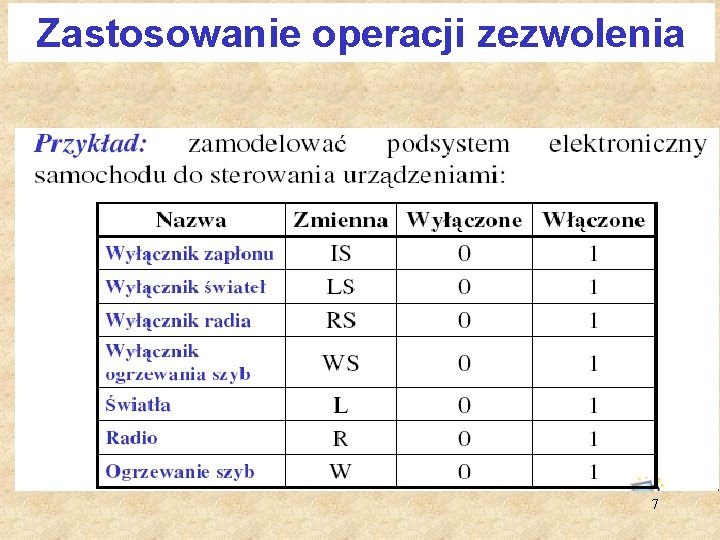

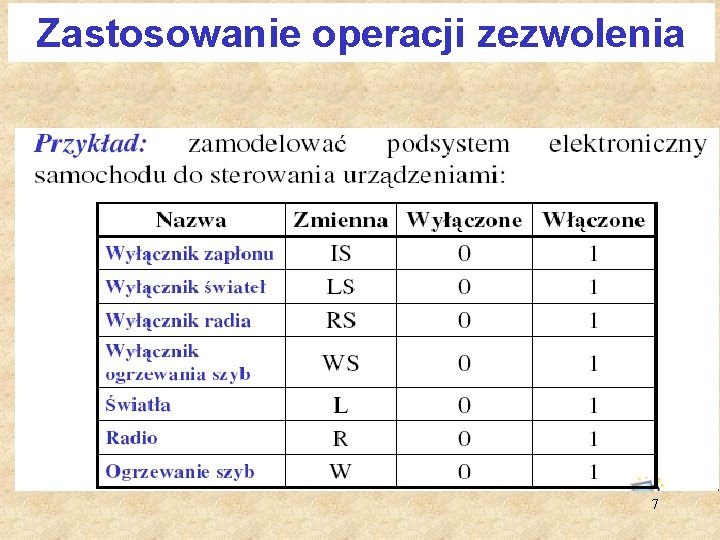

Zastosowanie operacji zezwolenia 7

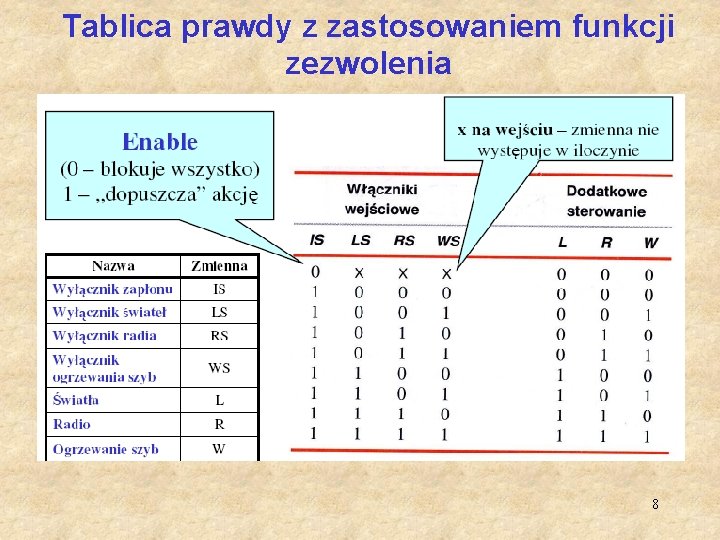

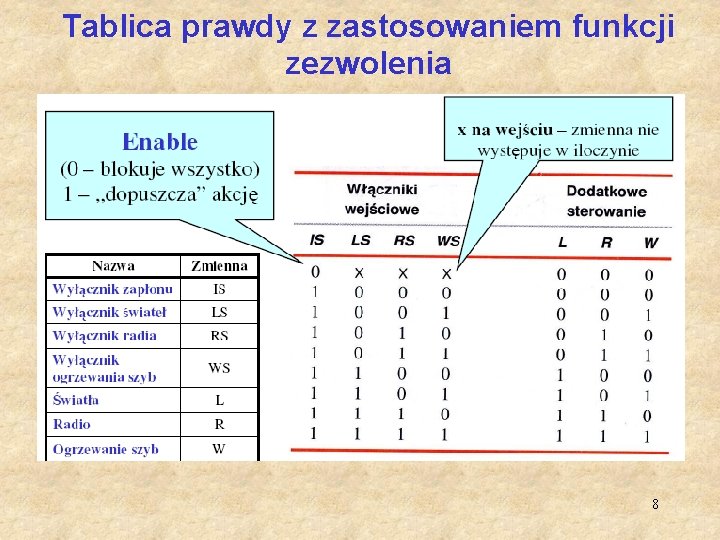

Tablica prawdy z zastosowaniem funkcji zezwolenia 8

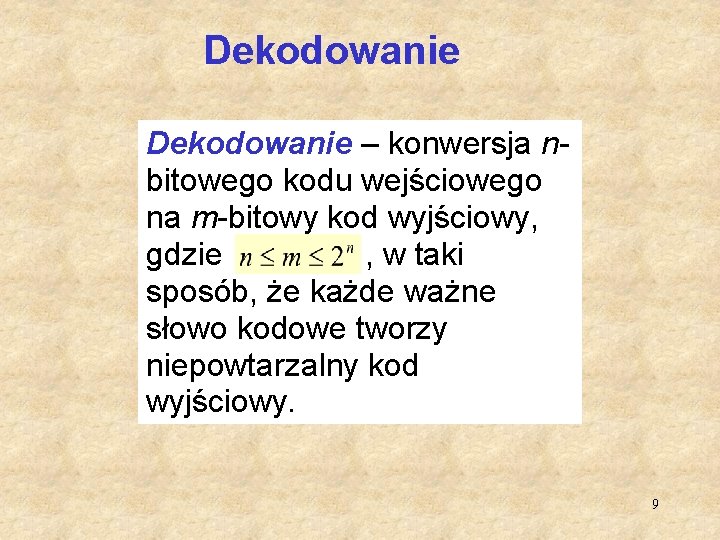

Dekodowanie – konwersja nbitowego kodu wejściowego na m-bitowy kod wyjściowy, gdzie , w taki sposób, że każde ważne słowo kodowe tworzy niepowtarzalny kod wyjściowy. 9

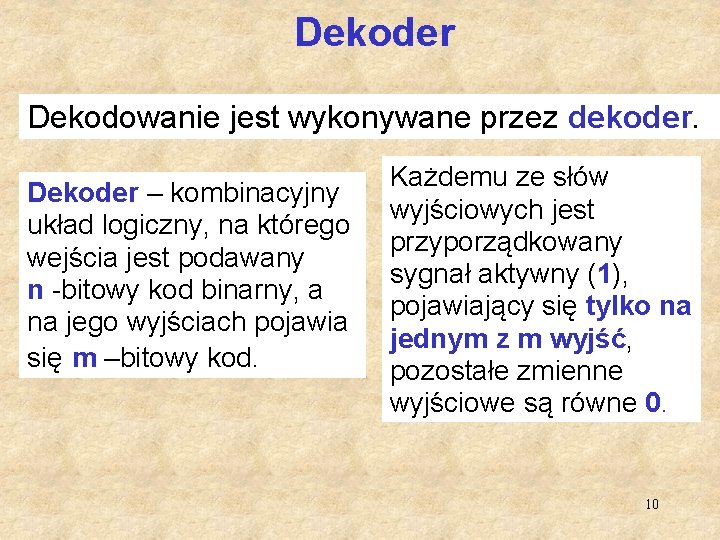

Dekoder Dekodowanie jest wykonywane przez dekoder. Dekoder – kombinacyjny układ logiczny, na którego wejścia jest podawany n -bitowy kod binarny, a na jego wyjściach pojawia się m –bitowy kod. Każdemu ze słów wyjściowych jest przyporządkowany sygnał aktywny (1), pojawiający się tylko na jednym z m wyjść, pozostałe zmienne wyjściowe są równe 0. 10

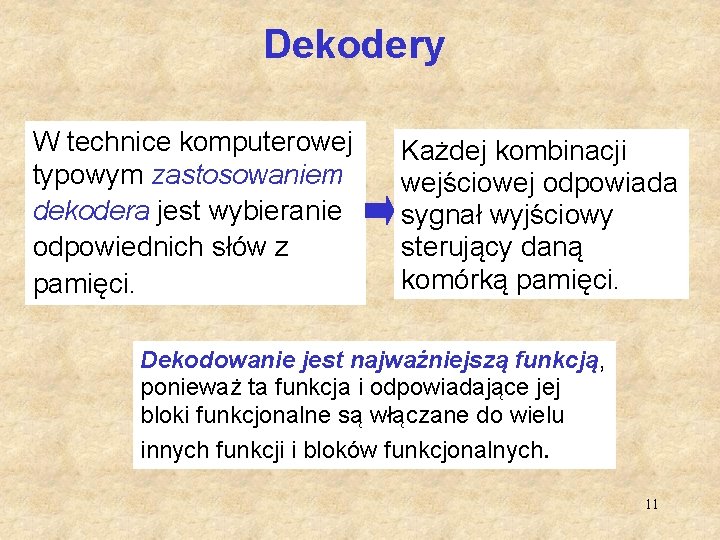

Dekodery W technice komputerowej typowym zastosowaniem dekodera jest wybieranie odpowiednich słów z pamięci. Każdej kombinacji wejściowej odpowiada sygnał wyjściowy sterujący daną komórką pamięci. Dekodowanie jest najważniejszą funkcją, ponieważ ta funkcja i odpowiadające jej bloki funkcjonalne są włączane do wielu innych funkcji i bloków funkcjonalnych. 11

Dekoder „n na m linii”, , generuje (lub mniej) mintermów z n zmiennych wejściowych. 12

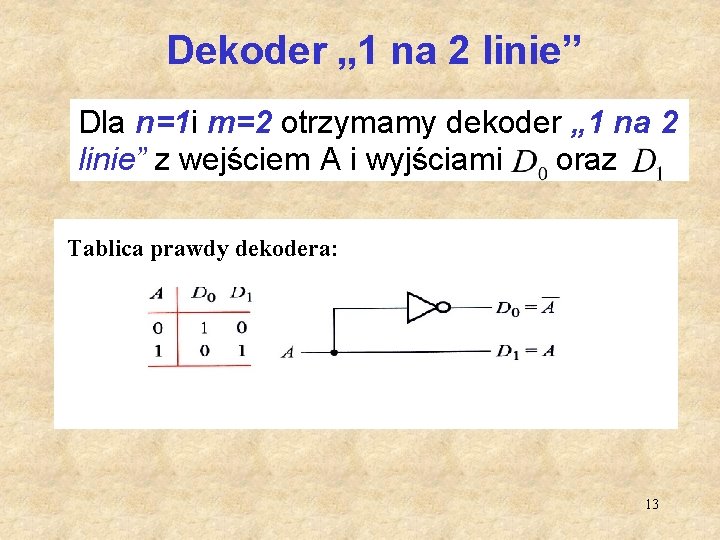

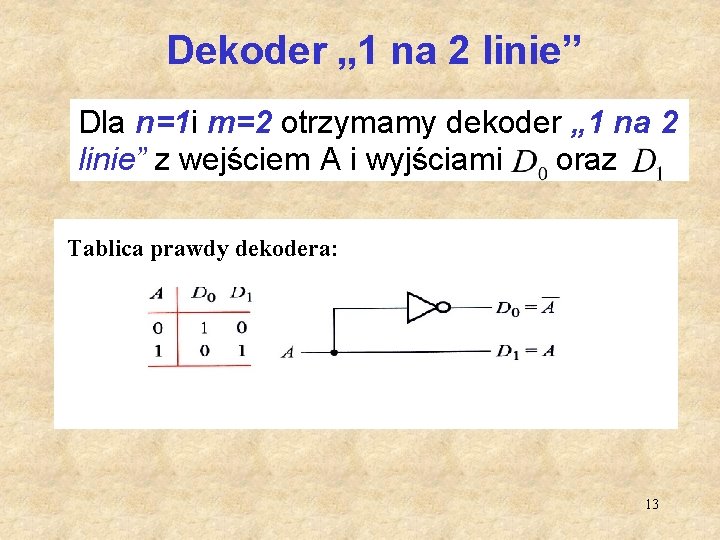

Dekoder „ 1 na 2 linie” Dla n=1 i m=2 otrzymamy dekoder „ 1 na 2 linie” z wejściem A i wyjściami oraz Tablica prawdy dekodera: 13

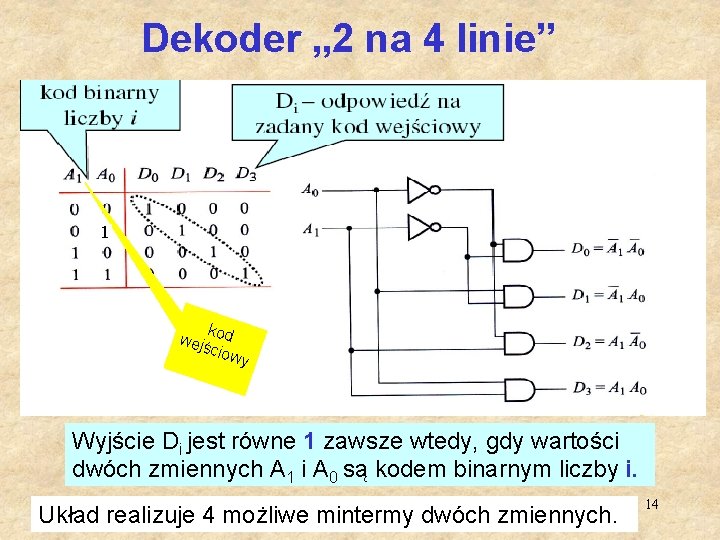

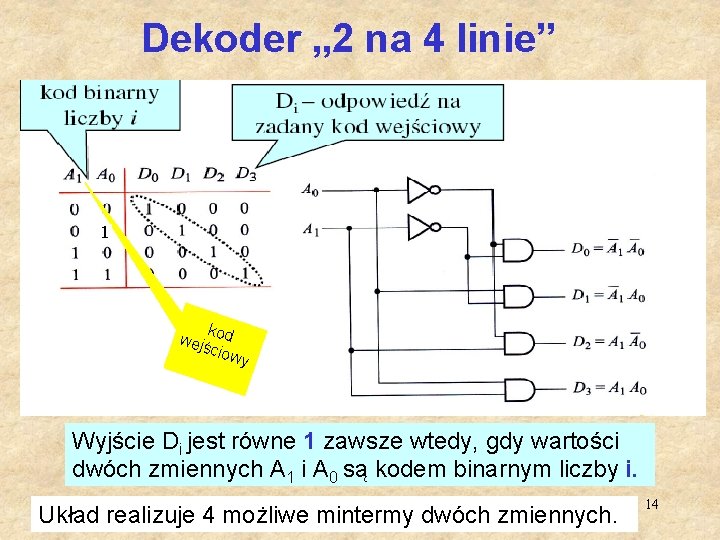

Dekoder „ 2 na 4 linie” 1 k wejś od ciow y Wyjście Di jest równe 1 zawsze wtedy, gdy wartości dwóch zmiennych A 1 i A 0 są kodem binarnym liczby i. Układ realizuje 4 możliwe mintermy dwóch zmiennych. 14

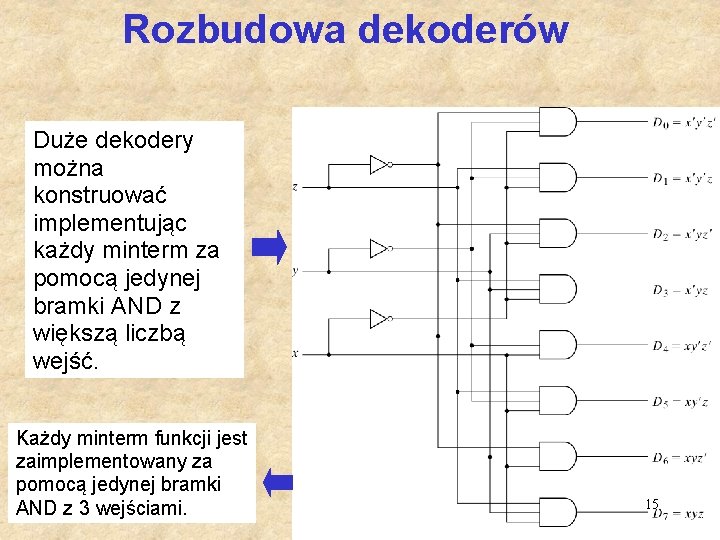

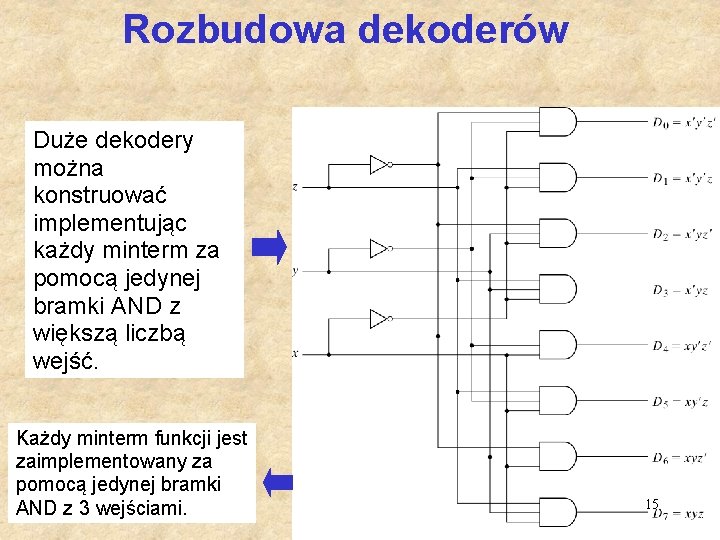

Rozbudowa dekoderów Duże dekodery można konstruować implementując każdy minterm za pomocą jedynej bramki AND z większą liczbą wejść. Każdy minterm funkcji jest zaimplementowany za pomocą jedynej bramki AND z 3 wejściami. 15

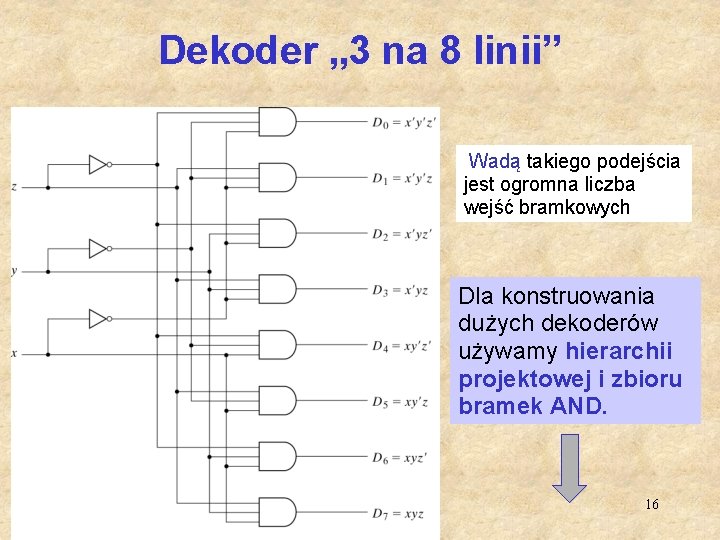

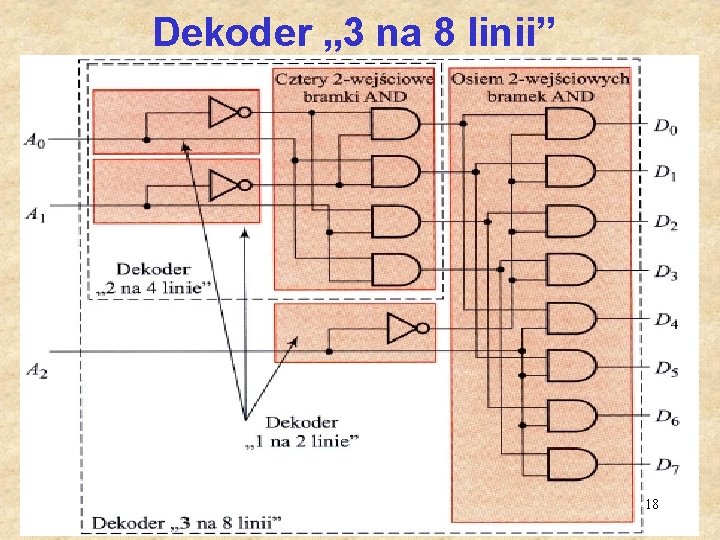

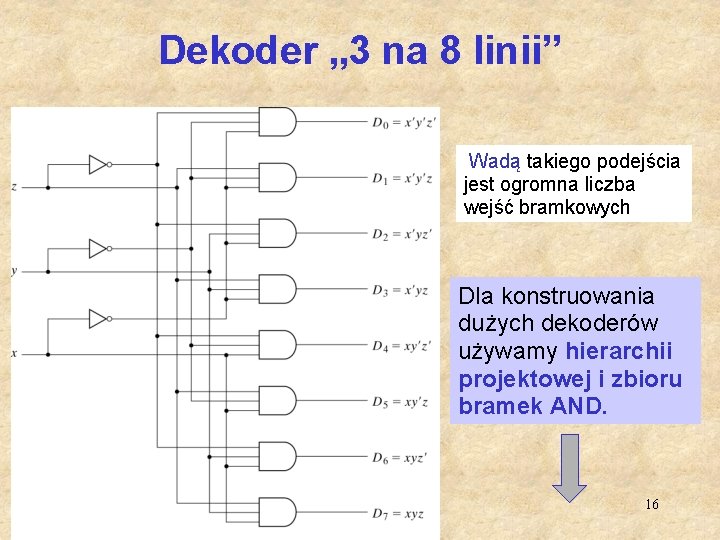

Dekoder „ 3 na 8 linii” Wadą takiego podejścia jest ogromna liczba wejść bramkowych Dla konstruowania dużych dekoderów używamy hierarchii projektowej i zbioru bramek AND. 16

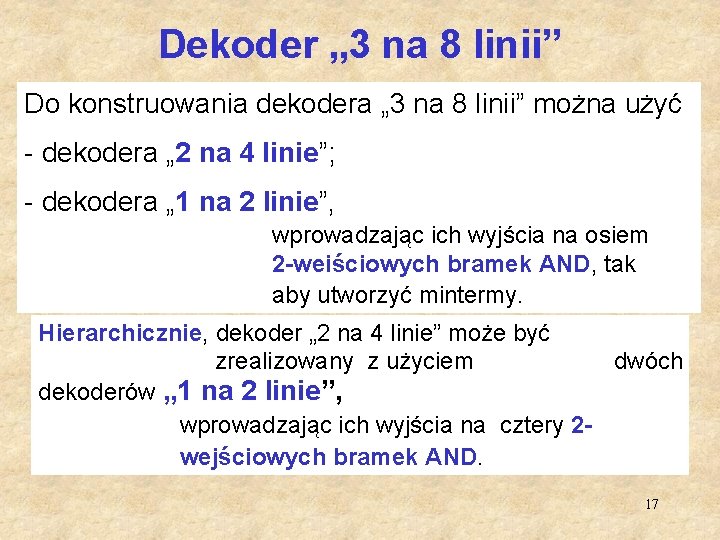

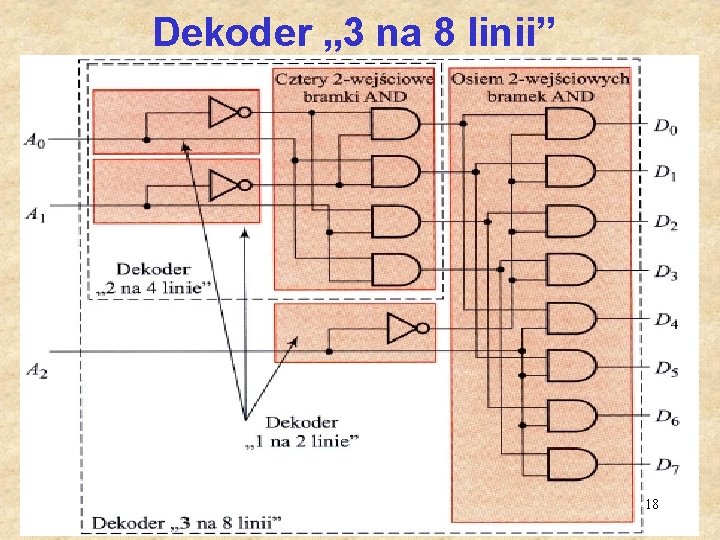

Dekoder „ 3 na 8 linii” Do konstruowania dekodera „ 3 na 8 linii” można użyć - dekodera „ 2 na 4 linie”; - dekodera „ 1 na 2 linie”, wprowadzając ich wyjścia na osiem 2 -weiściowych bramek AND, tak aby utworzyć mintermy. Hierarchicznie, dekoder „ 2 na 4 linie” może być zrealizowany z użyciem dwóch dekoderów „ 1 na 2 linie”, wprowadzając ich wyjścia na cztery 2 wejściowych bramek AND. 17

Dekoder „ 3 na 8 linii” 18

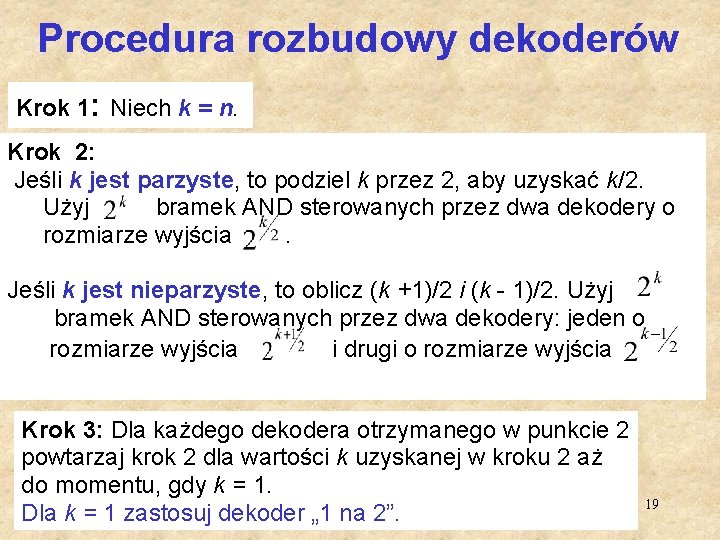

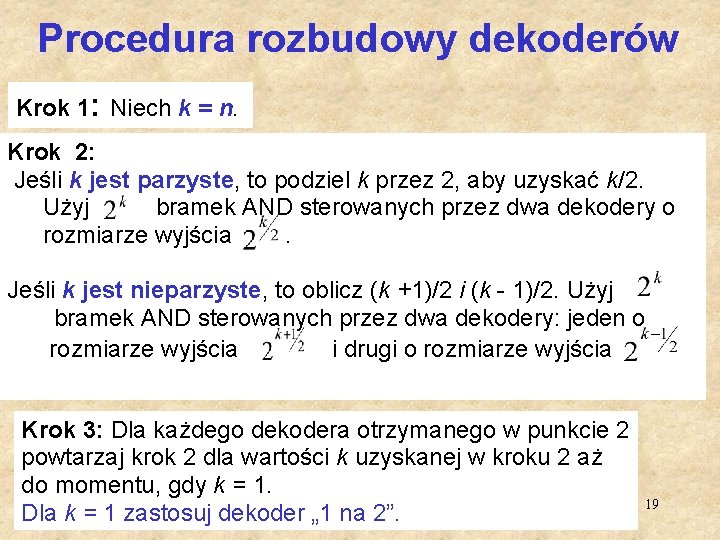

Procedura rozbudowy dekoderów Krok 1: Niech k = n. Krok 2: Jeśli k jest parzyste, to podziel k przez 2, aby uzyskać k/2. Użyj bramek AND sterowanych przez dwa dekodery o rozmiarze wyjścia. Jeśli k jest nieparzyste, to oblicz (k +1)/2 i (k - 1)/2. Użyj bramek AND sterowanych przez dwa dekodery: jeden o rozmiarze wyjścia i drugi o rozmiarze wyjścia Krok 3: Dla każdego dekodera otrzymanego w punkcie 2 powtarzaj krok 2 dla wartości k uzyskanej w kroku 2 aż do momentu, gdy k = 1. Dla k = 1 zastosuj dekoder „ 1 na 2”. 19

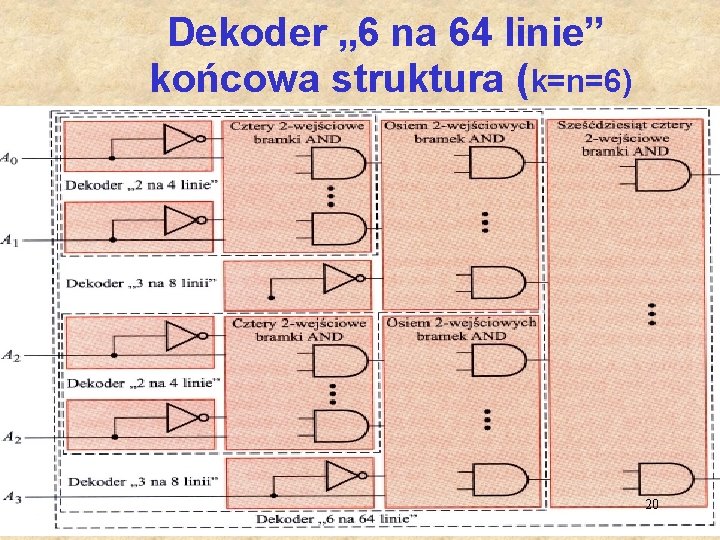

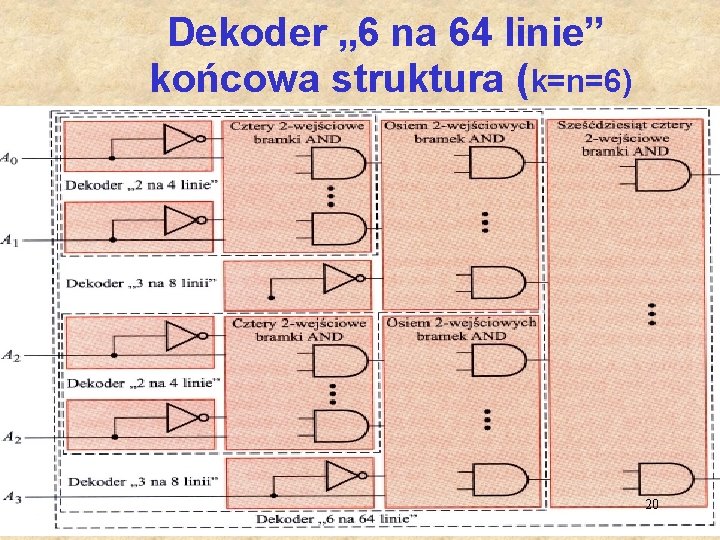

Dekoder „ 6 na 64 linie” końcowa struktura (k=n=6) 20

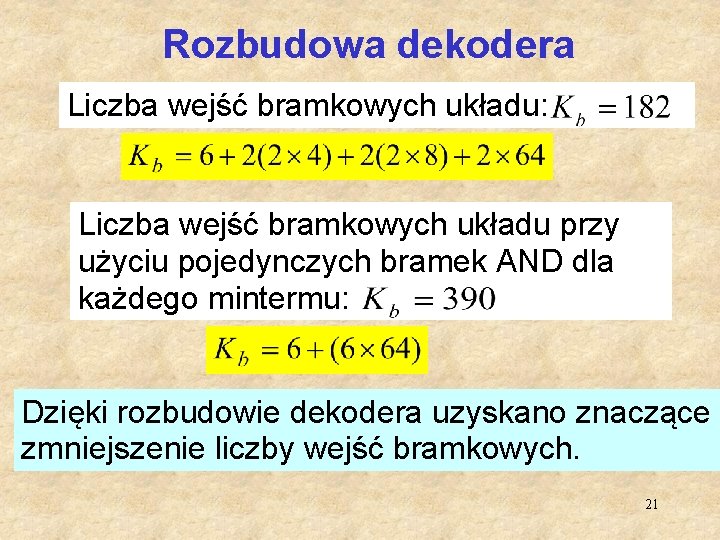

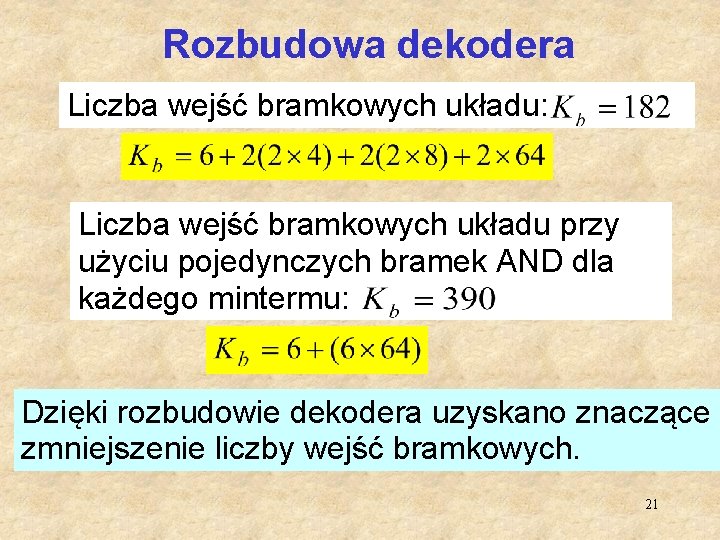

Rozbudowa dekodera Liczba wejść bramkowych układu: Liczba wejść bramkowych układu przy użyciu pojedynczych bramek AND dla każdego mintermu: Dzięki rozbudowie dekodera uzyskano znaczące zmniejszenie liczby wejść bramkowych. 21

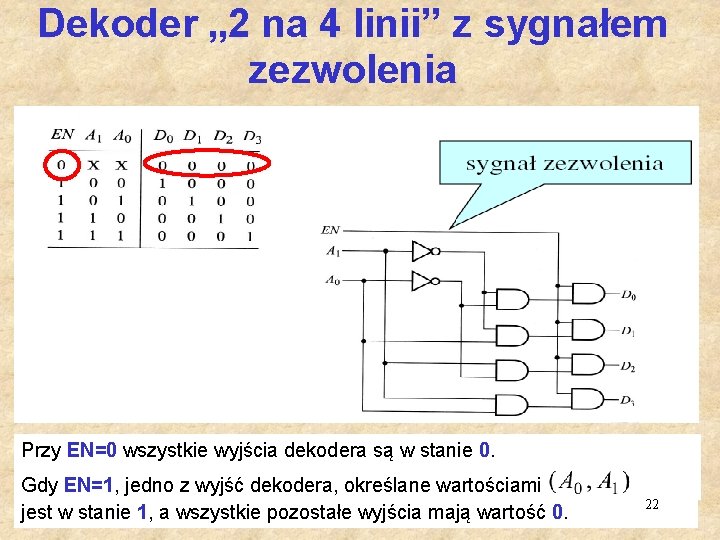

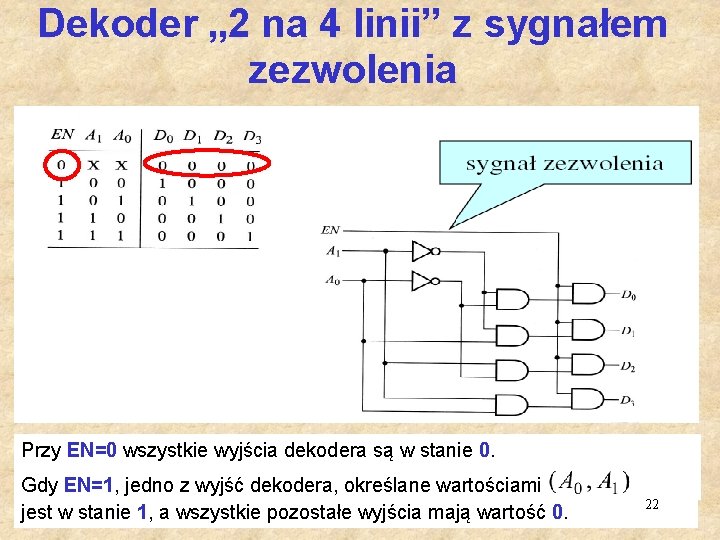

Dekoder „ 2 na 4 linii” z sygnałem zezwolenia Przy EN=0 wszystkie wyjścia dekodera są w stanie 0. Gdy EN=1, jedno z wyjść dekodera, określane wartościami jest w stanie 1, a wszystkie pozostałe wyjścia mają wartość 0. 22

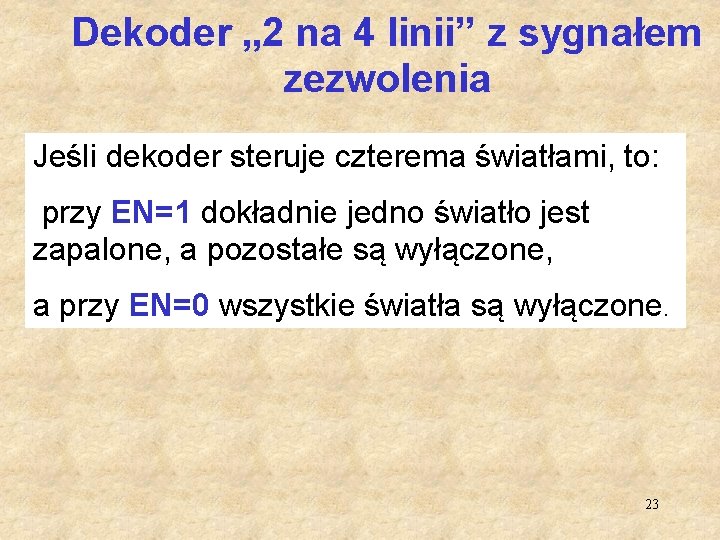

Dekoder „ 2 na 4 linii” z sygnałem zezwolenia Jeśli dekoder steruje czterema światłami, to: przy EN=1 dokładnie jedno światło jest zapalone, a pozostałe są wyłączone, a przy EN=0 wszystkie światła są wyłączone. 23

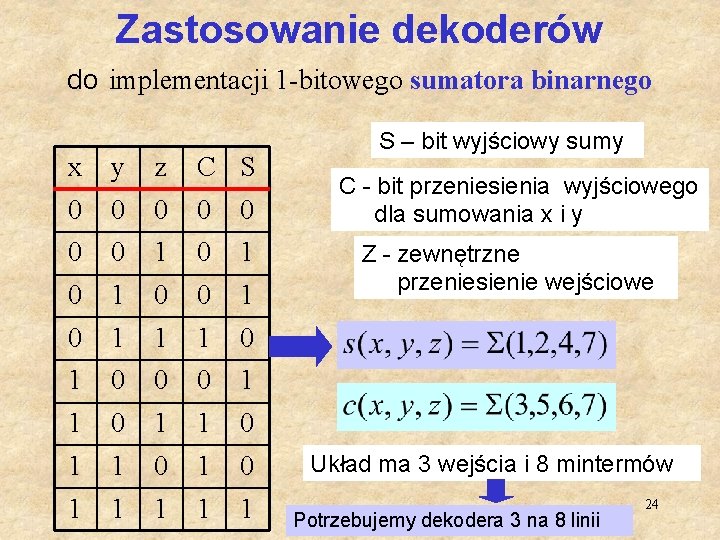

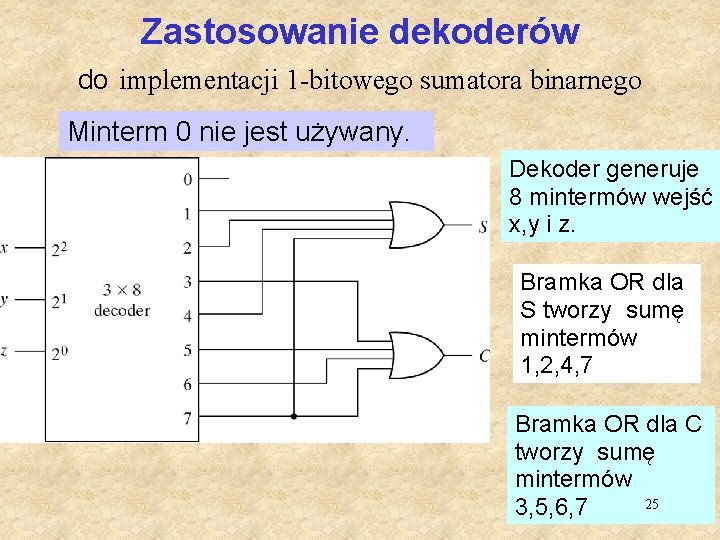

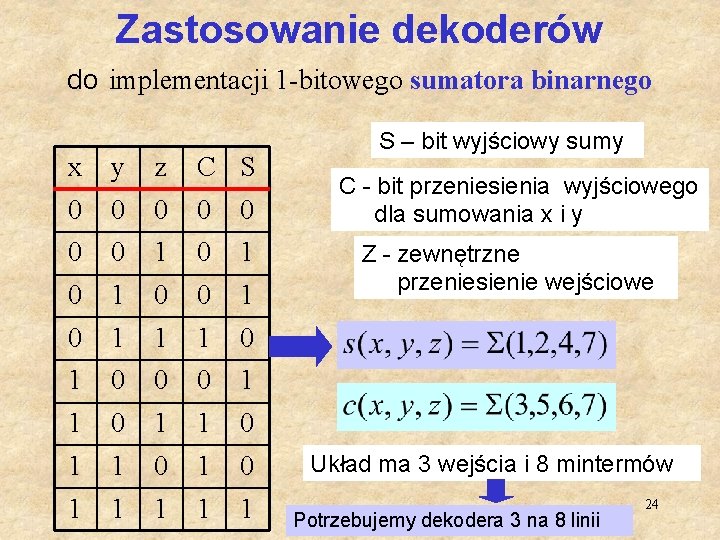

Zastosowanie dekoderów do implementacji 1 -bitowego sumatora binarnego x y z C S 0 0 0 0 1 0 1 0 1 1 1 0 0 0 1 1 0 1 1 1 S – bit wyjściowy sumy C - bit przeniesienia wyjściowego dla sumowania x i y Z - zewnętrzne przeniesienie wejściowe Układ ma 3 wejścia i 8 mintermów Potrzebujemy dekodera 3 na 8 linii 24

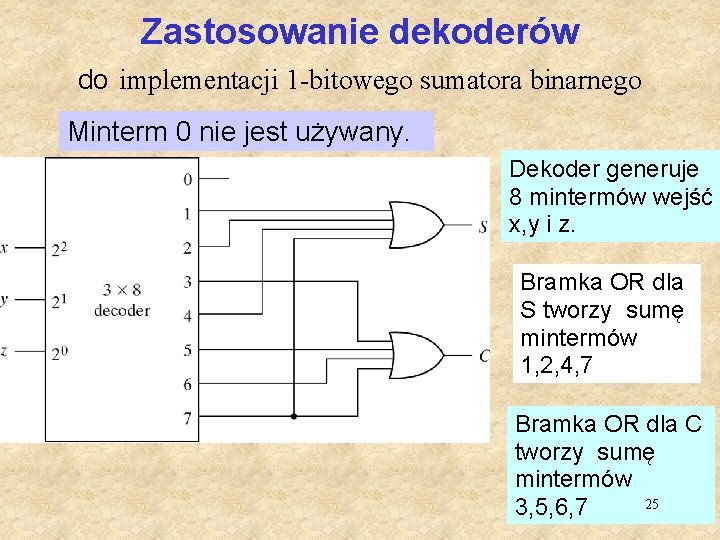

Zastosowanie dekoderów do implementacji 1 -bitowego sumatora binarnego Minterm 0 nie jest używany. Dekoder generuje 8 mintermów wejść x, y i z. Bramka OR dla S tworzy sumę mintermów 1, 2, 4, 7 Bramka OR dla C tworzy sumę mintermów 25 3, 5, 6, 7

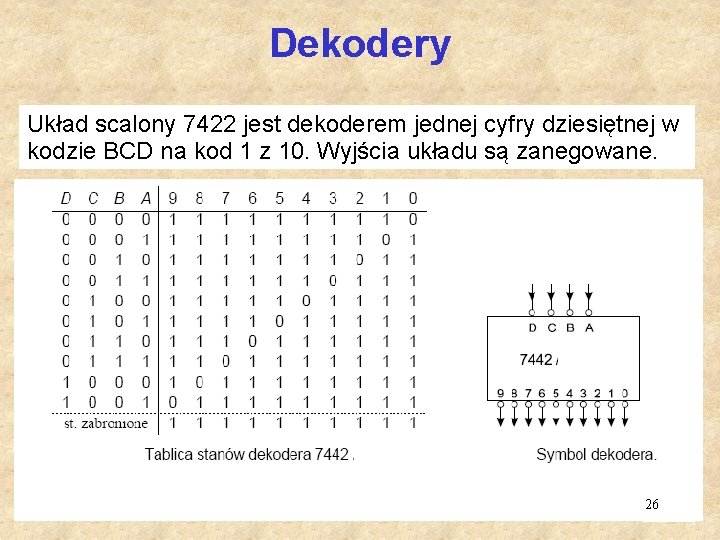

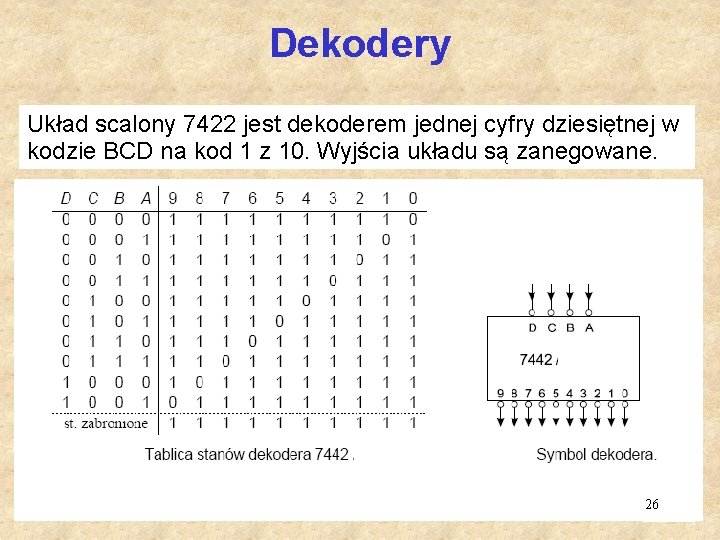

Dekodery Układ scalony 7422 jest dekoderem jednej cyfry dziesiętnej w kodzie BCD na kod 1 z 10. Wyjścia układu są zanegowane. 26

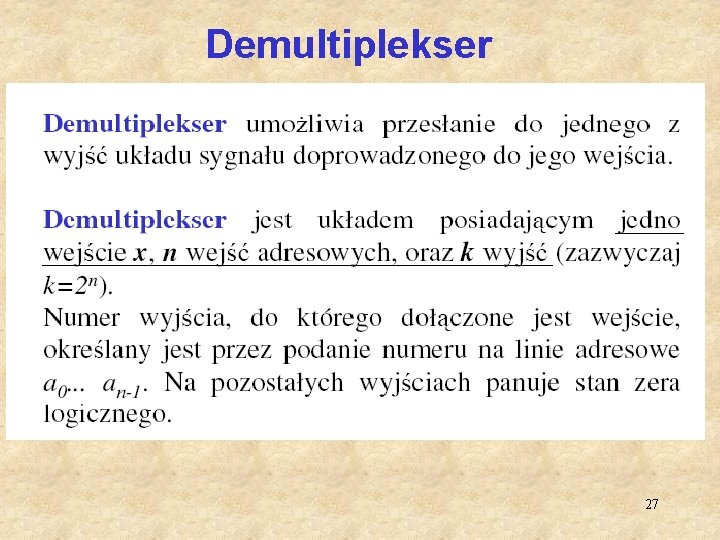

Demultiplekser 27

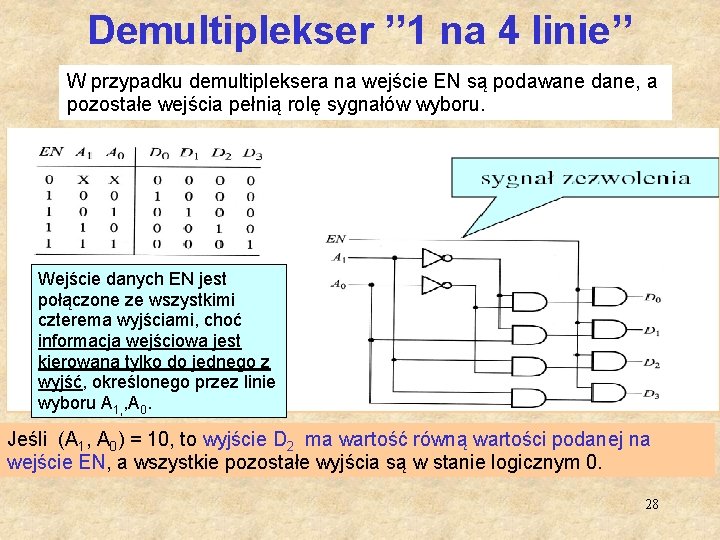

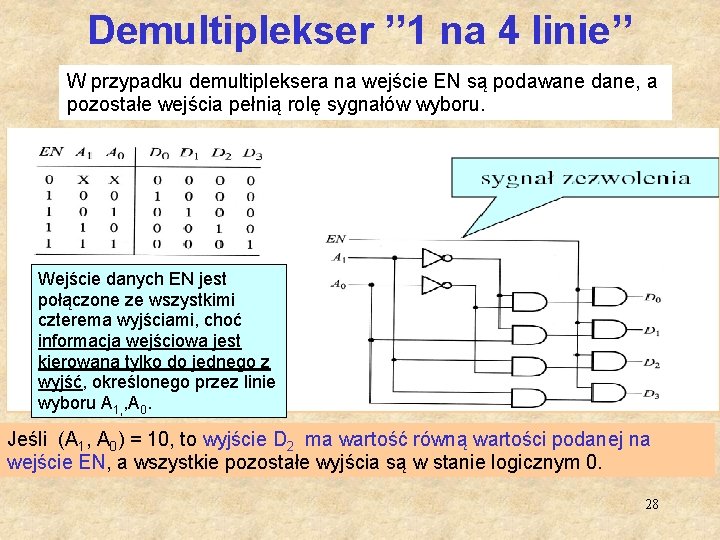

Demultiplekser ’’ 1 na 4 linie’’ W przypadku demultipleksera na wejście EN są podawane dane, a pozostałe wejścia pełnią rolę sygnałów wyboru. Demultiplekser Wejście danych EN jest połączone ze wszystkimi czterema wyjściami, choć informacja wejściowa jest kierowana tylko do jednego z wyjść, określonego przez linie wyboru A 1, , A 0. Jeśli (A 1, A 0) = 10, to wyjście D 2 ma wartość równą wartości podanej na wejście EN, a wszystkie pozostałe wyjścia są w stanie logicznym 0. 28

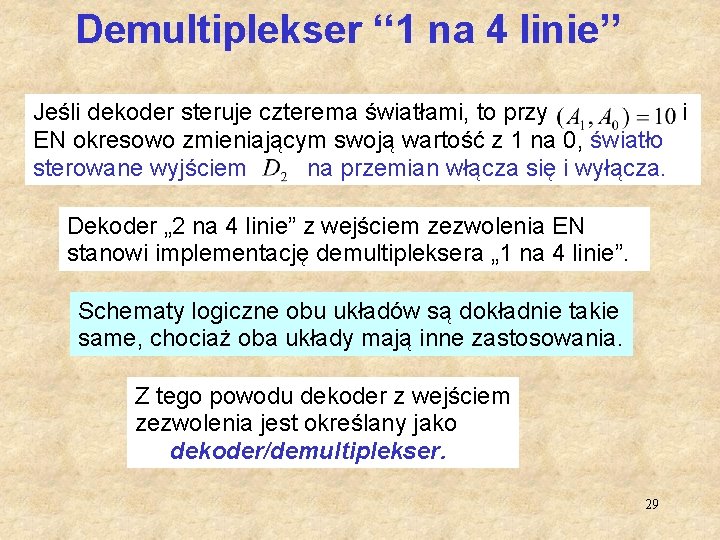

Demultiplekser ‘‘ 1 na 4 linie’’ Jeśli dekoder steruje czterema światłami, to przy i EN okresowo zmieniającym swoją wartość z 1 na 0, światło sterowane wyjściem na przemian włącza się i wyłącza. Dekoder „ 2 na 4 linie” z wejściem zezwolenia EN stanowi implementację demultipleksera „ 1 na 4 linie”. Schematy logiczne obu układów są dokładnie takie same, chociaż oba układy mają inne zastosowania. Z tego powodu dekoder z wejściem zezwolenia jest określany jako dekoder/demultiplekser. 29

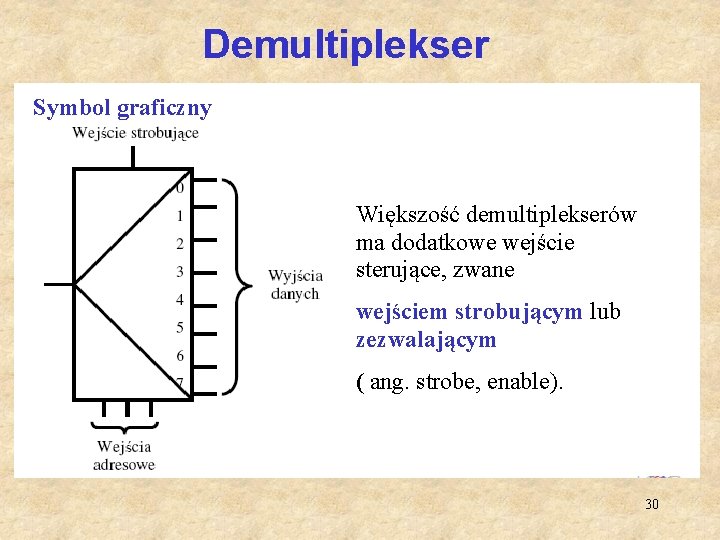

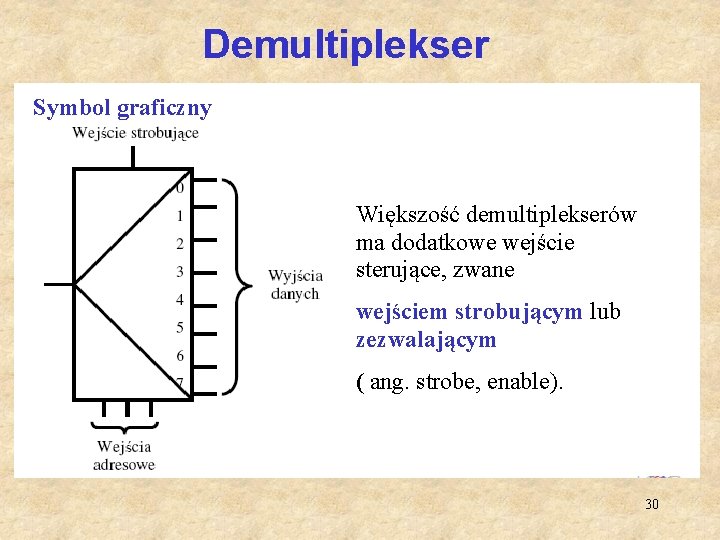

Demultiplekser Symbol graficzny Model mechaniczny Większość demultiplekserów ma dodatkowe wejście sterujące, zwane wejściem strobującym lub zezwalającym ( ang. strobe, enable). 30

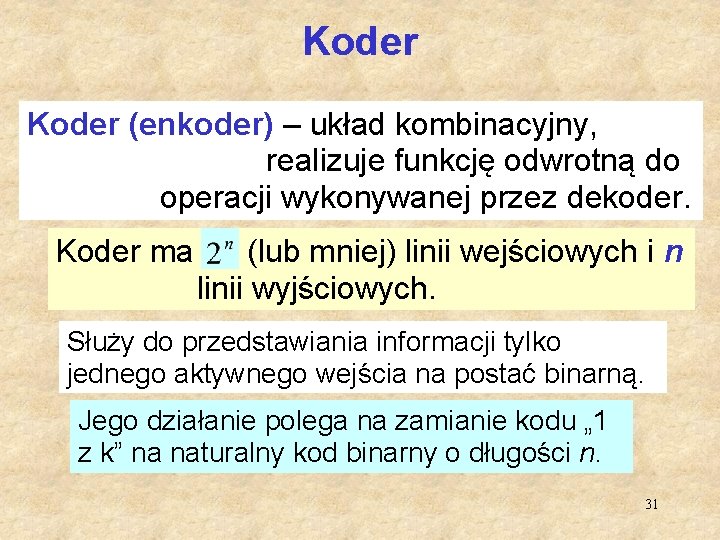

Koder (enkoder) – układ kombinacyjny, realizuje funkcję odwrotną do operacji wykonywanej przez dekoder. Koder ma (lub mniej) linii wejściowych i n linii wyjściowych. Służy do przedstawiania informacji tylko jednego aktywnego wejścia na postać binarną. Jego działanie polega na zamianie kodu „ 1 z k” na naturalny kod binarny o długości n. 31

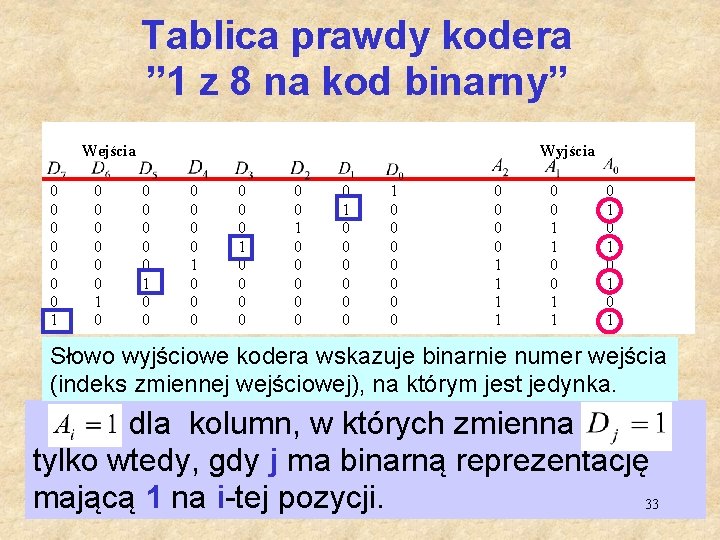

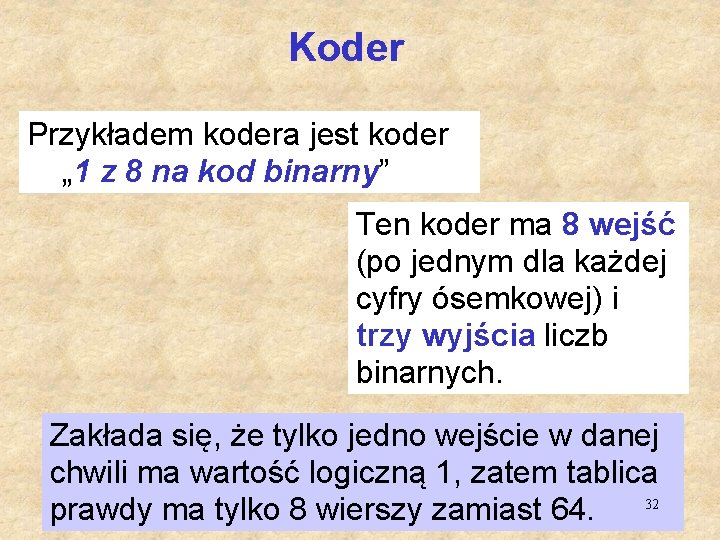

Koder Przykładem kodera jest koder „ 1 z 8 na kod binarny” Ten koder ma 8 wejść (po jednym dla każdej cyfry ósemkowej) i trzy wyjścia liczb binarnych. Zakłada się, że tylko jedno wejście w danej chwili ma wartość logiczną 1, zatem tablica 32 prawdy ma tylko 8 wierszy zamiast 64.

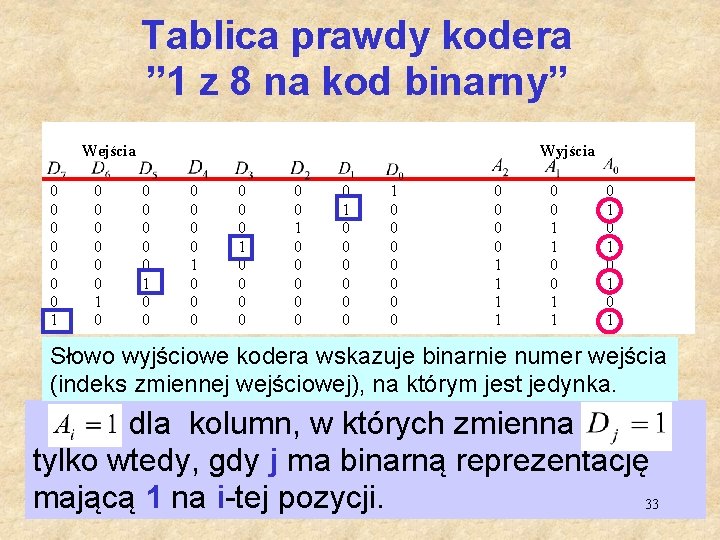

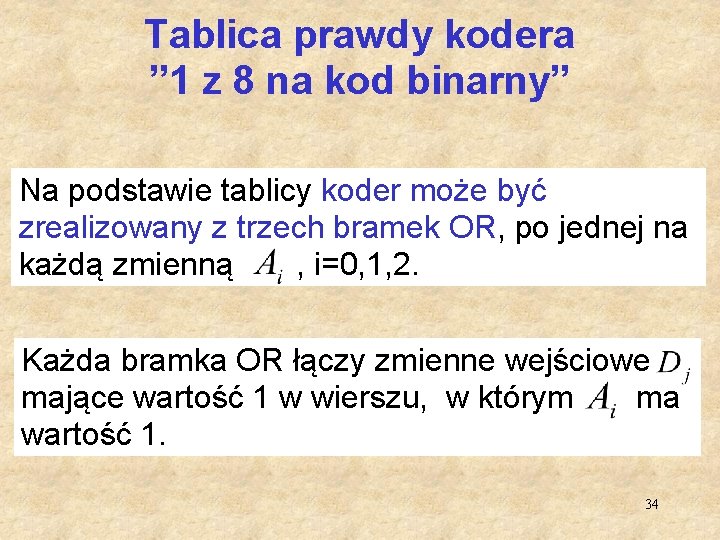

Tablica prawdy kodera ” 1 z 8 na kod binarny” Wejścia 0 0 0 0 1 0 Wyjścia 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 1 1 0 0 1 1 0 1 0 1 Słowo wyjściowe kodera wskazuje binarnie numer wejścia (indeks zmiennej wejściowej), na którym jest jedynka. dla kolumn, w których zmienna tylko wtedy, gdy j ma binarną reprezentację mającą 1 na i-tej pozycji. 33

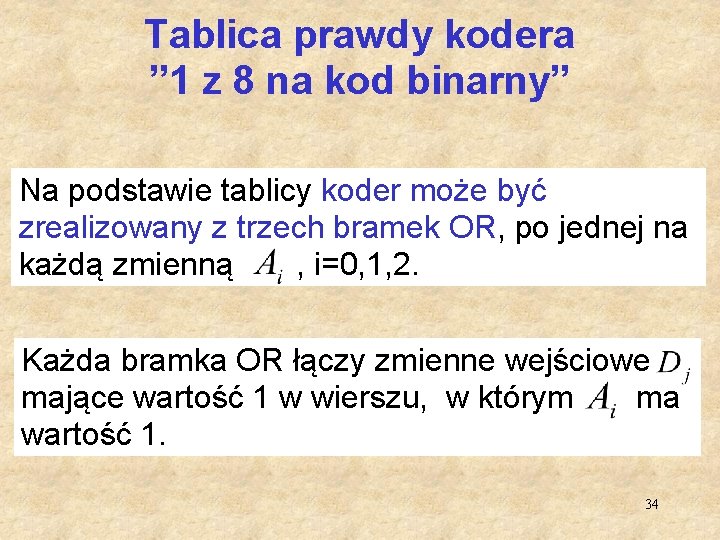

Tablica prawdy kodera ” 1 z 8 na kod binarny” Na podstawie tablicy koder może być zrealizowany z trzech bramek OR, po jednej na każdą zmienną , i=0, 1, 2. Każda bramka OR łączy zmienne wejściowe mające wartość 1 w wierszu, w którym ma wartość 1. 34

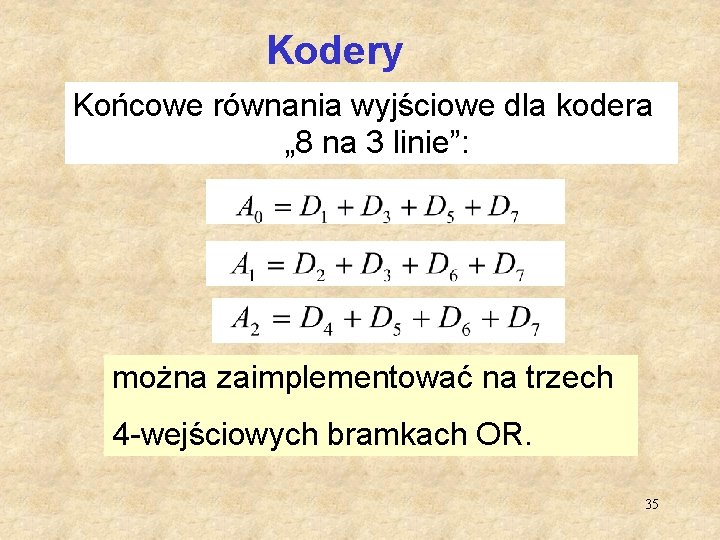

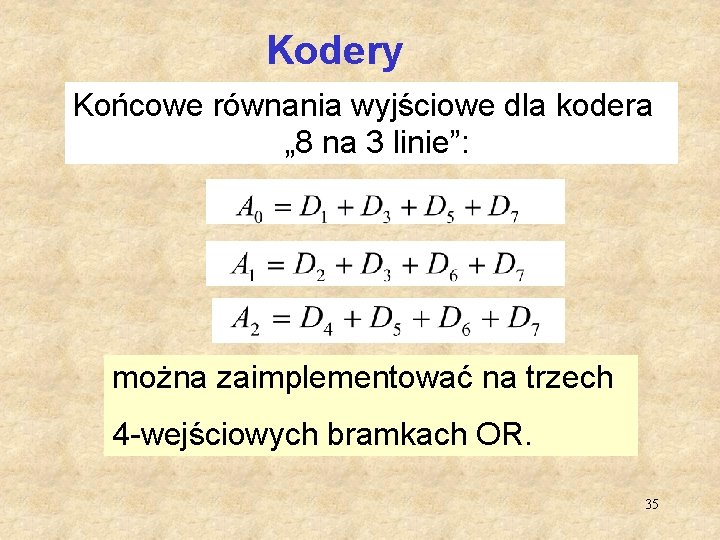

Kodery Końcowe równania wyjściowe dla kodera „ 8 na 3 linie”: b można zaimplementować na trzech 4 -wejściowych bramkach OR. 35

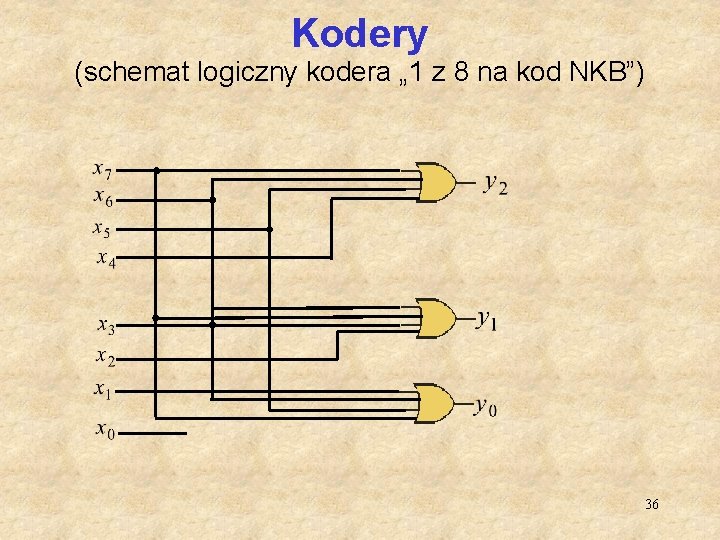

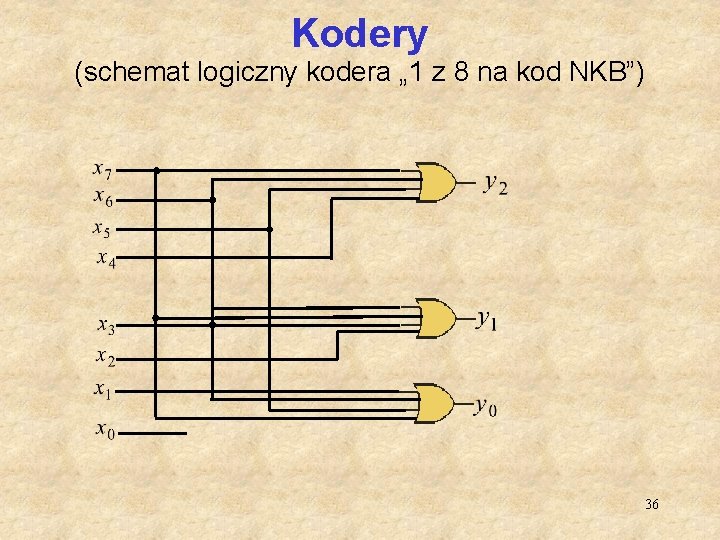

Kodery (schemat logiczny kodera „ 1 z 8 na kod NKB”) 36

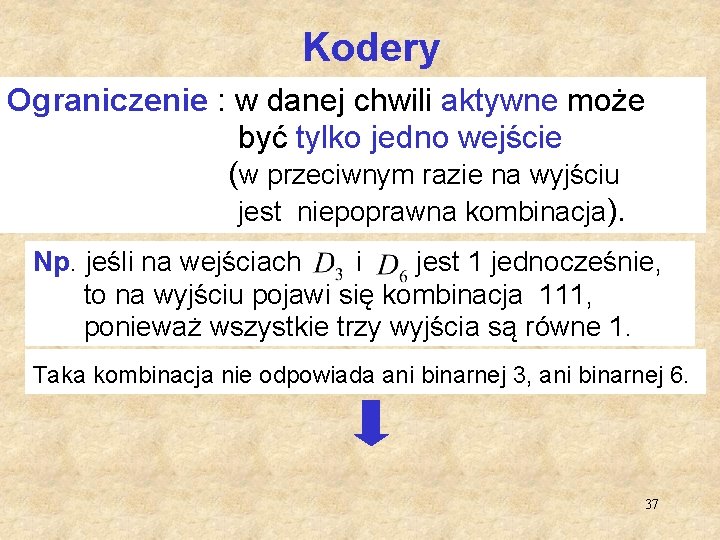

Kodery Ograniczenie : w danej chwili aktywne może być tylko jedno wejście (w przeciwnym razie na wyjściu jest niepoprawna kombinacja). Np. jeśli na wejściach i jest 1 jednocześnie, to na wyjściu pojawi się kombinacja 111, ponieważ wszystkie trzy wyjścia są równe 1. Taka kombinacja nie odpowiada ani binarnej 3, ani binarnej 6. 37

Kodery Rozwiązanie: zastosowanie dodatkowego układu kodera, który określi na wejściu priorytet dla liczb o wyższych indeksach. Koder priorytetowy (ang. priority enkoder) – realizuje funkcję rozstrzygającą priorytet, czyli pierwszeństwo sygnałów (określa na wejściu priorytet dla liczb o wyższych indeksach). 38

Koder priorytetowy Jeśli dwa lub więcej wejść ma wartość równą 1 w tym samym czasie, to wejście mające najwyższy priorytet ma pierwszeństwo. Jeśli na wejściach D 3 i D 6 jest 1 jednocześnie, to na wyjściu pojawi się kombinacja 110, ponieważ D 6 ma wyższy priorytet od D 3. 39

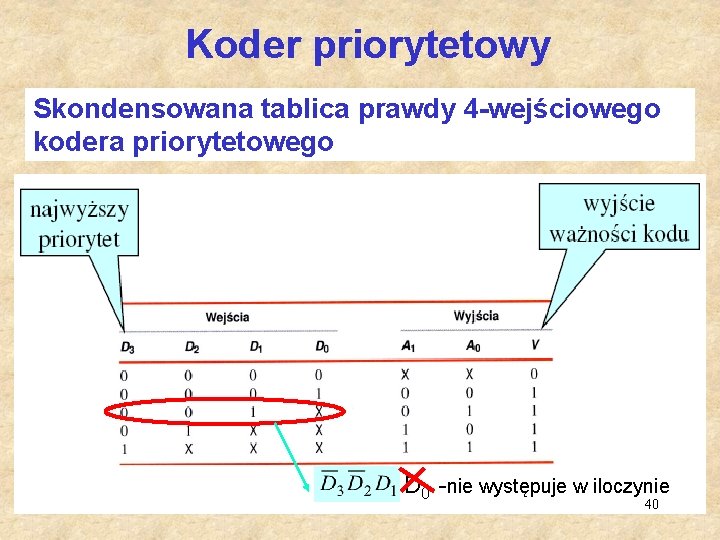

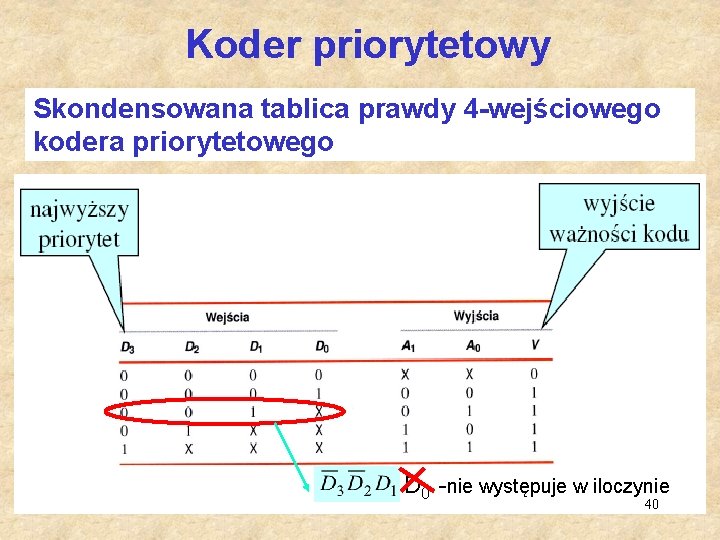

Koder priorytetowy Skondensowana tablica prawdy 4 -wejściowego kodera priorytetowego D 0 -nie występuje w iloczynie 40

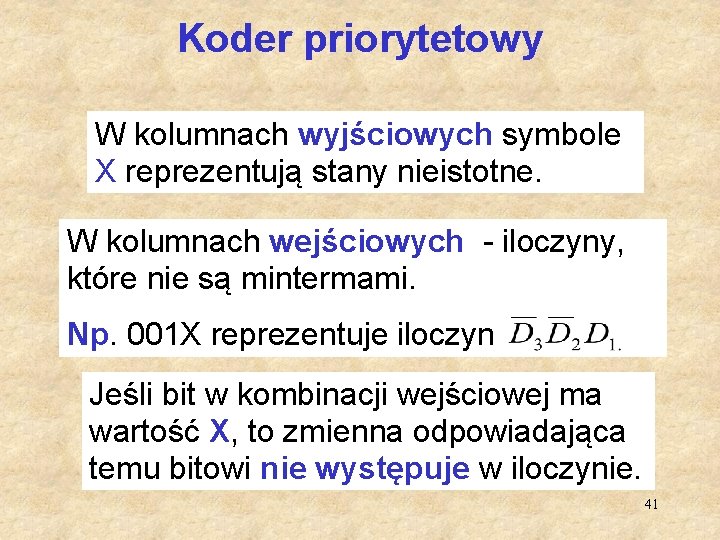

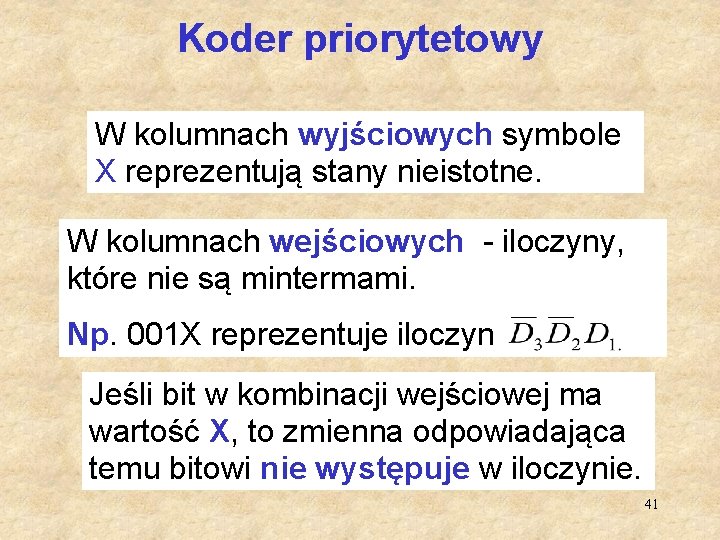

Koder priorytetowy W kolumnach wyjściowych symbole X reprezentują stany nieistotne. W kolumnach wejściowych - iloczyny, które nie są mintermami. Np. 001 X reprezentuje iloczyn Jeśli bit w kombinacji wejściowej ma wartość X, to zmienna odpowiadająca temu bitowi nie występuje w iloczynie. 41

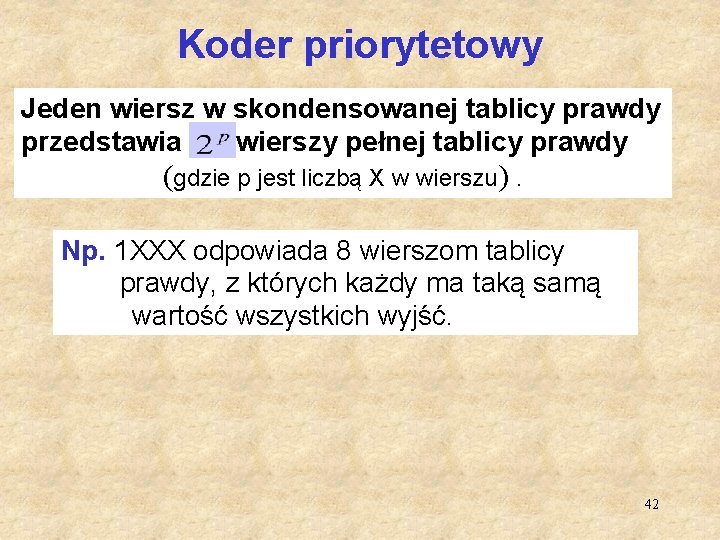

Koder priorytetowy Jeden wiersz w skondensowanej tablicy prawdy przedstawia wierszy pełnej tablicy prawdy (gdzie p jest liczbą X w wierszu). Np. 1 XXX odpowiada 8 wierszom tablicy prawdy, z których każdy ma taką samą wartość wszystkich wyjść. 42

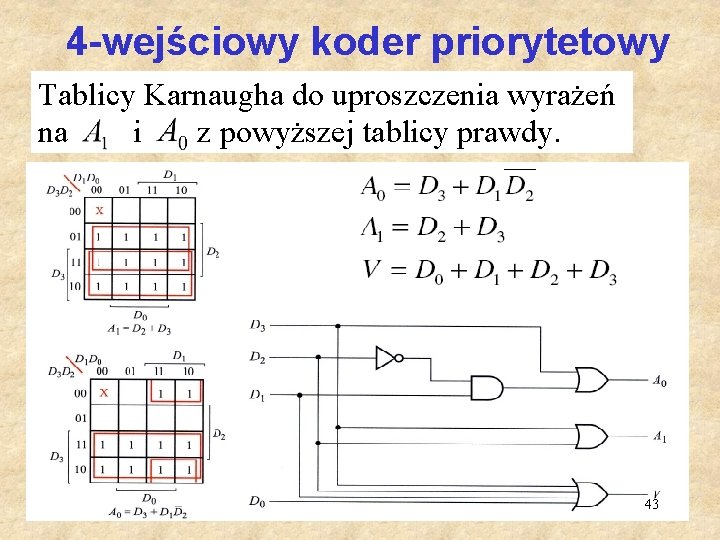

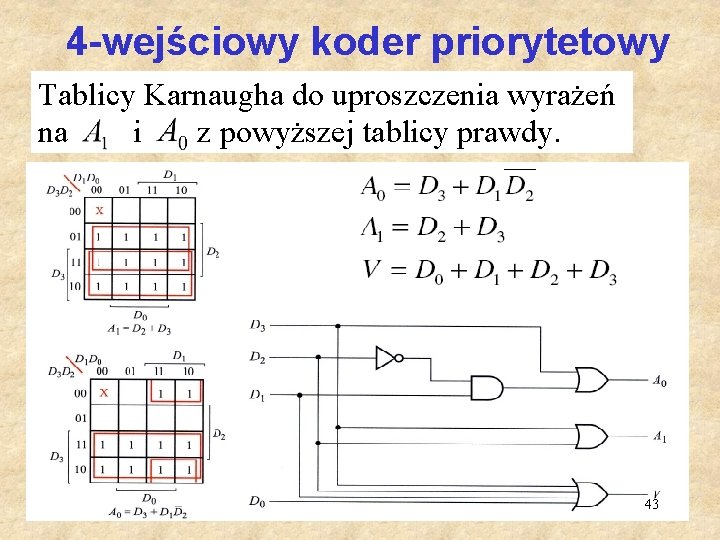

4 -wejściowy koder priorytetowy Tablicy Karnaugha do uproszczenia wyrażeń na i z powyższej tablicy prawdy. 43

Kodery i dekodery Omówione układy dekoderów i koderów nazywane są także konwerterami kodów. Innym przykładem konwertera kodu może być konwerter kodu NKB na kod Gray’a (i odwrotnie). W serii układów TTL produkowane są także inne konwertery kodów: 74184 – konwerter kodu BCD na kod binarny; 74185 – konwerter kodu binarnego na kod BCD. 44

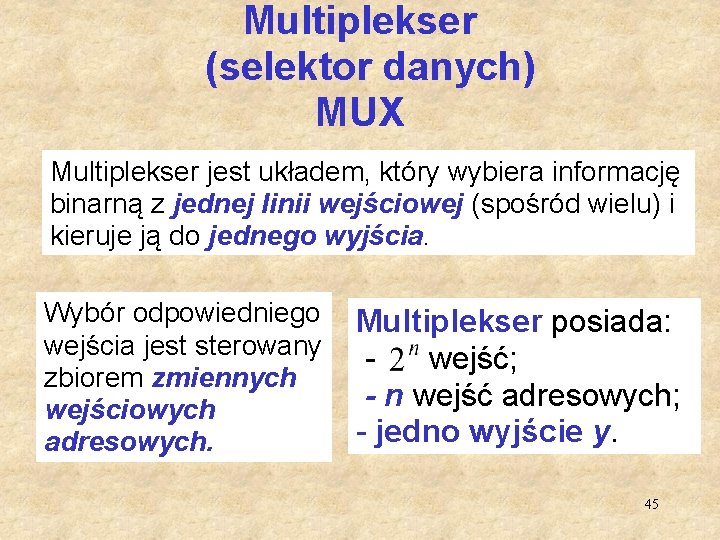

Multiplekser (selektor danych) MUX Multiplekser jest układem, który wybiera informację binarną z jednej linii wejściowej (spośród wielu) i kieruje ją do jednego wyjścia. Wybór odpowiedniego wejścia jest sterowany zbiorem zmiennych wejściowych adresowych. Multiplekser posiada: wejść; - n wejść adresowych; - jedno wyjście y. 45

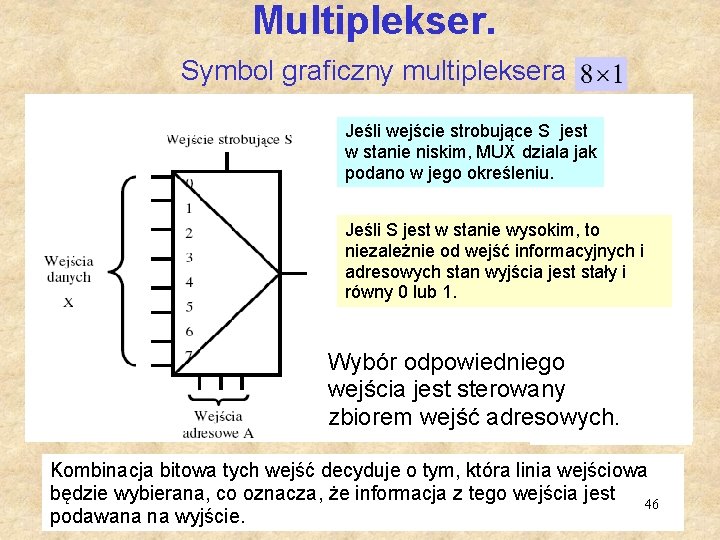

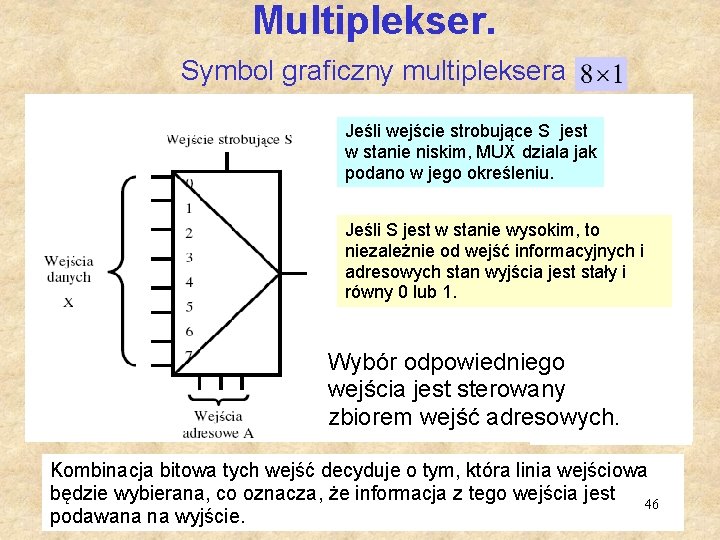

Multiplekser. Symbol graficzny multipleksera Jeśli wejście strobujące S jest w stanie niskim, MUX dziala jak podano w jego określeniu. Jeśli S jest w stanie wysokim, to niezależnie od wejść informacyjnych i adresowych stan wyjścia jest stały i równy 0 lub 1. Wybór odpowiedniego wejścia jest sterowany zbiorem wejść adresowych. Kombinacja bitowa tych wejść decyduje o tym, która linia wejściowa będzie wybierana, co oznacza, że informacja z tego wejścia jest 46 podawana na wyjście.

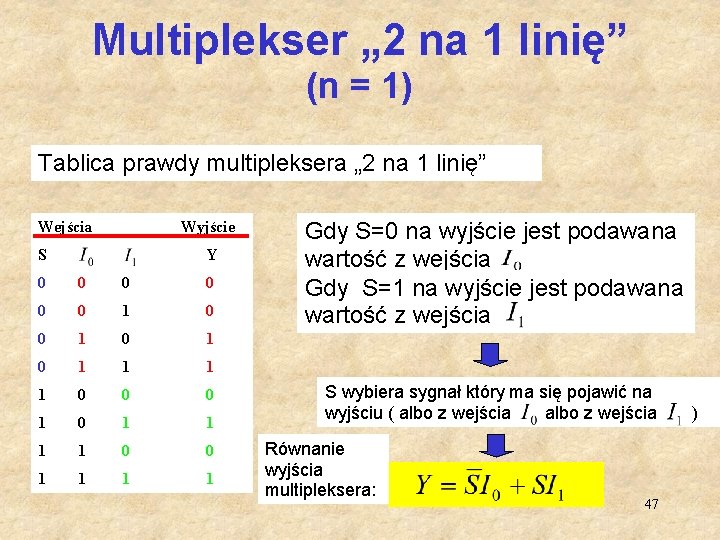

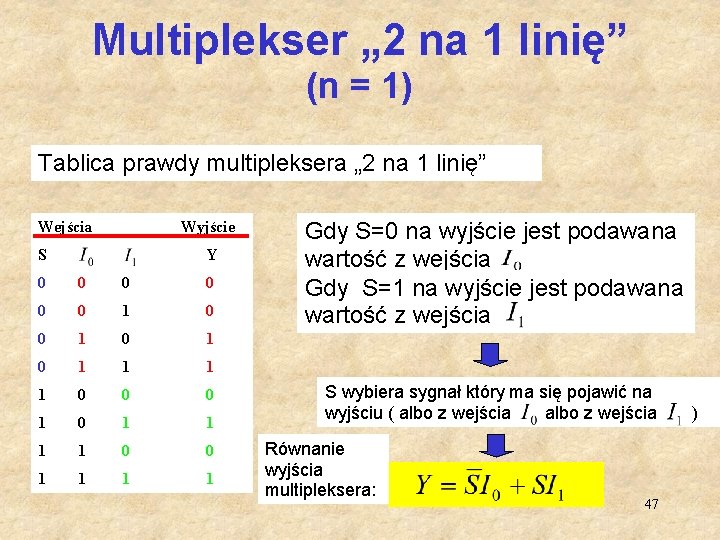

Multiplekser „ 2 na 1 linię” (n = 1) Tablica prawdy multipleksera „ 2 na 1 linię” Wejścia Wyjście S Y 0 0 0 1 0 1 1 0 0 0 1 1 1 1 0 0 1 1 Gdy S=0 na wyjście jest podawana wartość z wejścia Gdy S=1 na wyjście jest podawana wartość z wejścia S wybiera sygnał który ma się pojawić na wyjściu ( albo z wejścia Równanie wyjścia multipleksera: 47 )

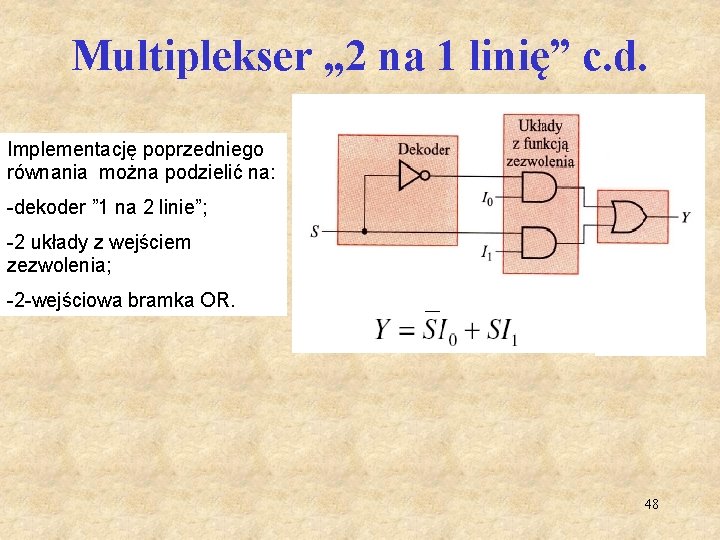

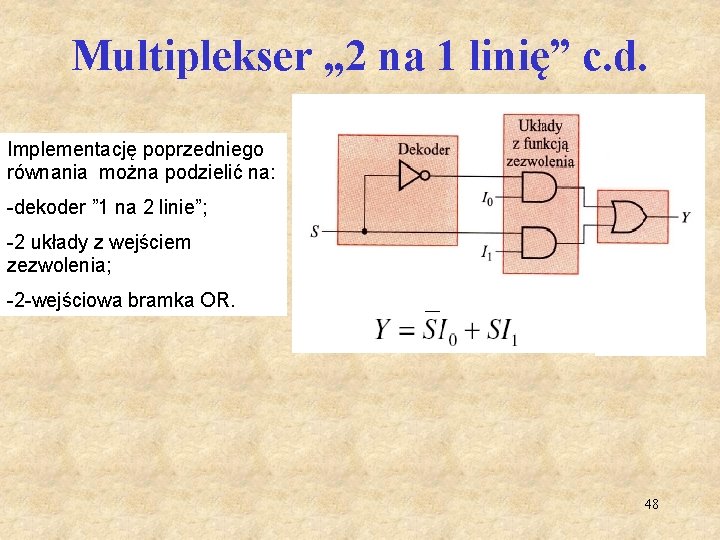

Multiplekser „ 2 na 1 linię” c. d. Implementację poprzedniego równania można podzielić na: -dekoder ” 1 na 2 linie”; -2 układy z wejściem zezwolenia; -2 -wejściowa bramka OR. 48

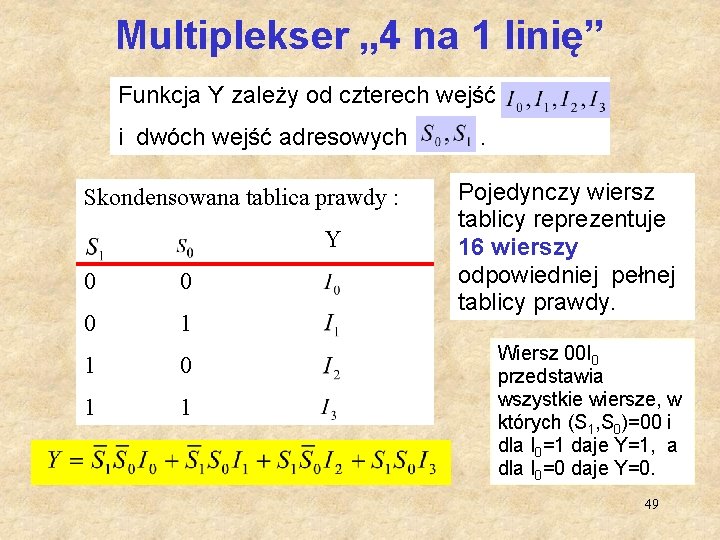

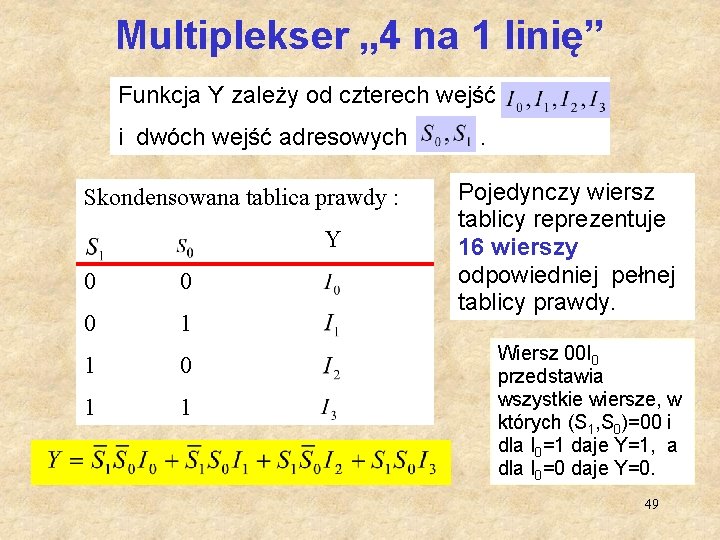

Multiplekser „ 4 na 1 linię” Funkcja Y zależy od czterech wejść i dwóch wejść adresowych Skondensowana tablica prawdy : Y 0 0 0 1 1 . Pojedynczy wiersz tablicy reprezentuje 16 wierszy odpowiedniej pełnej tablicy prawdy. Wiersz 00 I 0 przedstawia wszystkie wiersze, w których (S 1, S 0)=00 i dla I 0=1 daje Y=1, a dla I 0=0 daje Y=0. 49

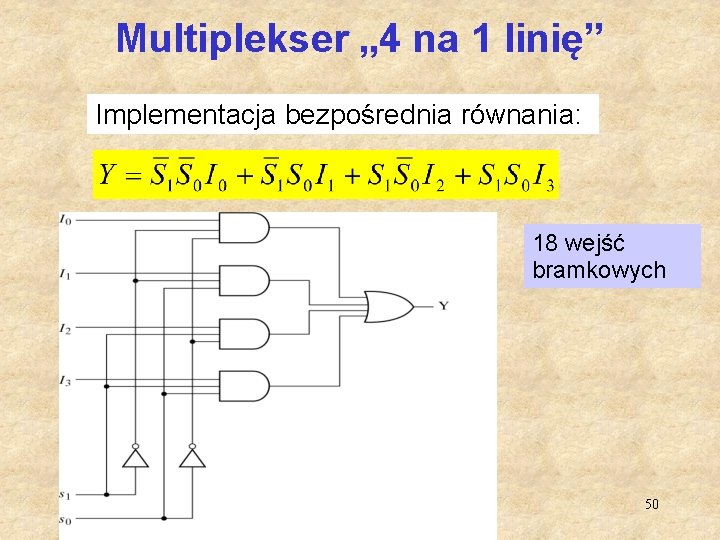

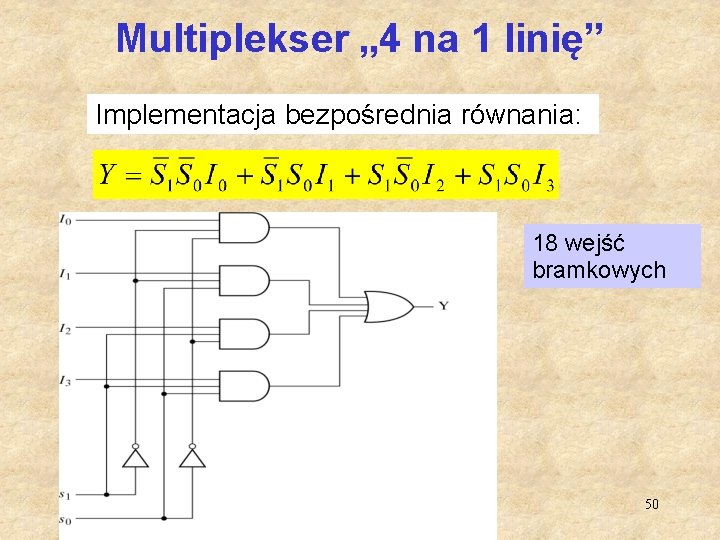

Multiplekser „ 4 na 1 linię” Implementacja bezpośrednia równania: 18 wejść bramkowych 50

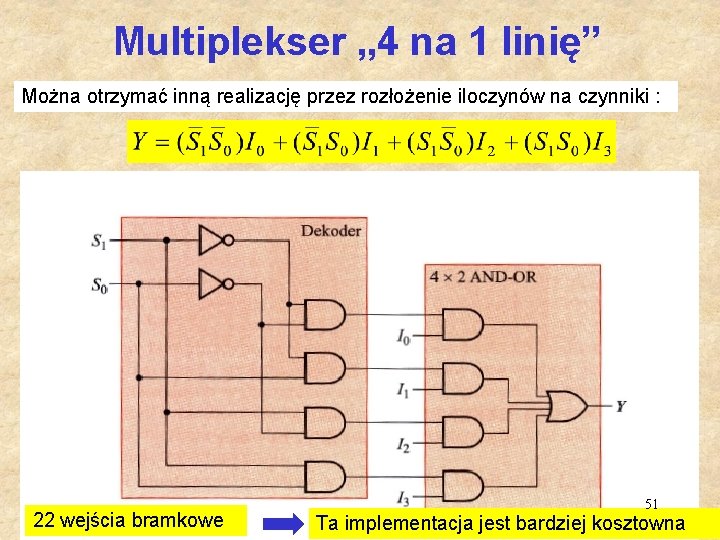

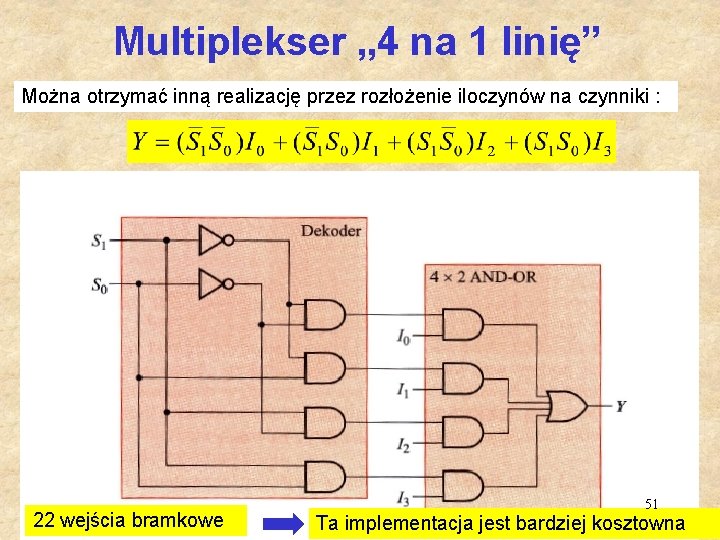

Multiplekser „ 4 na 1 linię” Można otrzymać inną realizację przez rozłożenie iloczynów na czynniki : 22 wejścia bramkowe 51 Ta implementacja jest bardziej kosztowna

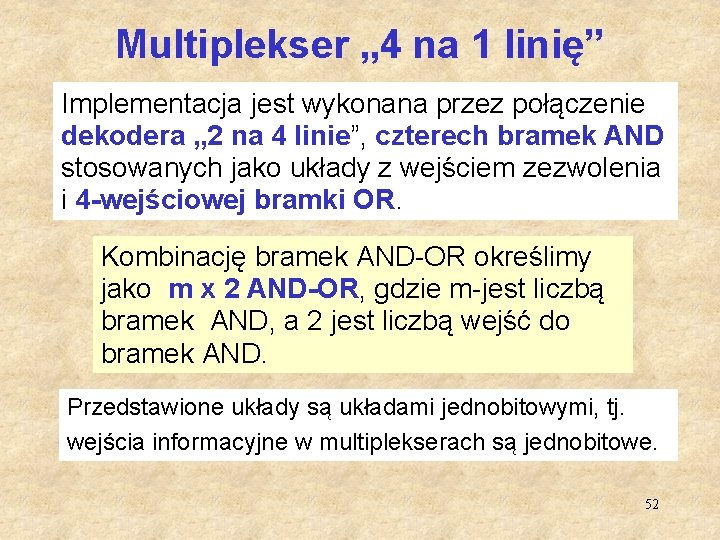

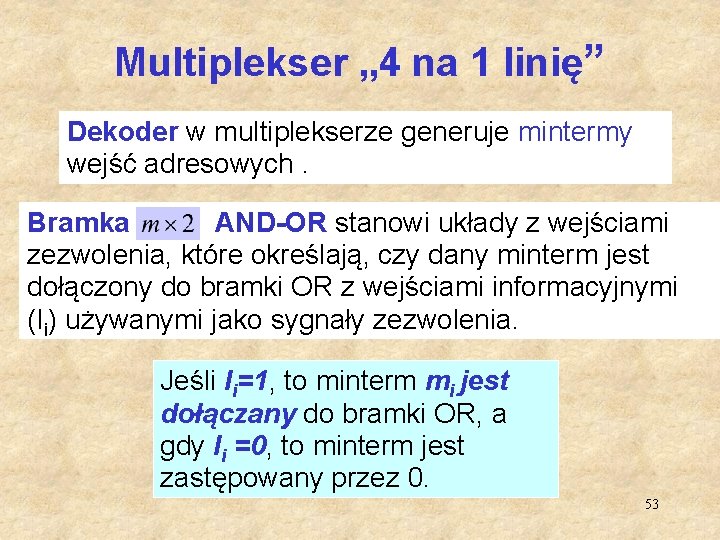

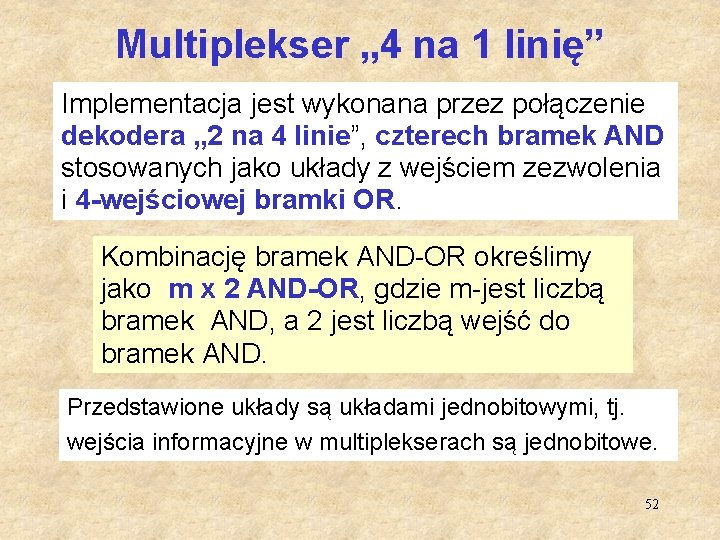

Multiplekser „ 4 na 1 linię” Implementacja jest wykonana przez połączenie dekodera „ 2 na 4 linie”, czterech bramek AND stosowanych jako układy z wejściem zezwolenia i 4 -wejściowej bramki OR. Kombinację bramek AND-OR określimy jako m x 2 AND-OR, gdzie m-jest liczbą bramek AND, a 2 jest liczbą wejść do bramek AND. Przedstawione układy są układami jednobitowymi, tj. wejścia informacyjne w multiplekserach są jednobitowe. 52

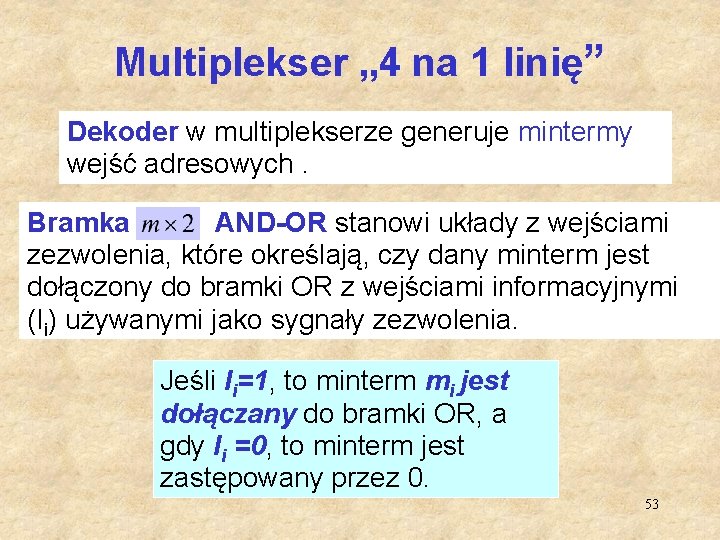

Multiplekser „ 4 na 1 linię” Dekoder w multiplekserze generuje mintermy wejść adresowych. Bramka AND-OR stanowi układy z wejściami zezwolenia, które określają, czy dany minterm jest dołączony do bramki OR z wejściami informacyjnymi (Ii) używanymi jako sygnały zezwolenia. Jeśli Ii=1, to minterm mi jest dołączany do bramki OR, a gdy Ii =0, to minterm jest zastępowany przez 0. 53

Rozbudowa multiplekserów Multipleksery mogą być rozbudowane, gdy rozpatrujemy większe rozmiary n wektorów bitów wejściowych. Rozbudowując multiplekser, opieramy się na strukturze układu multipleksera „ 4 na 1 linię”, który składa się z dekodera, układów z wejściami zezwolenia i bramki OR. 54

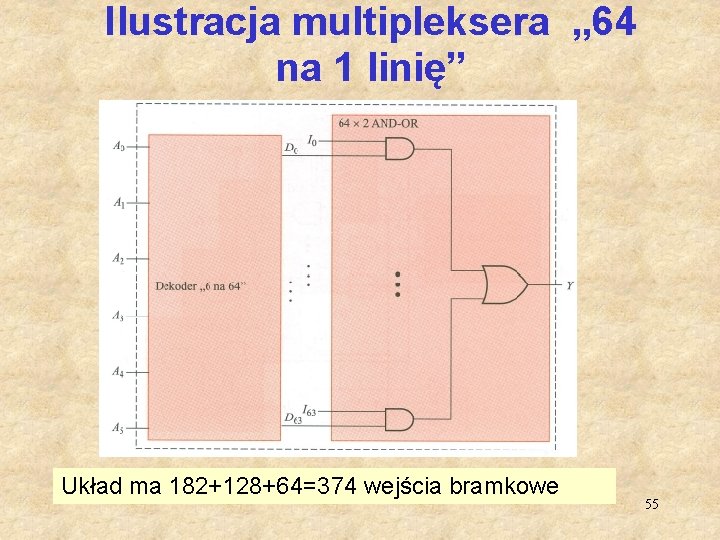

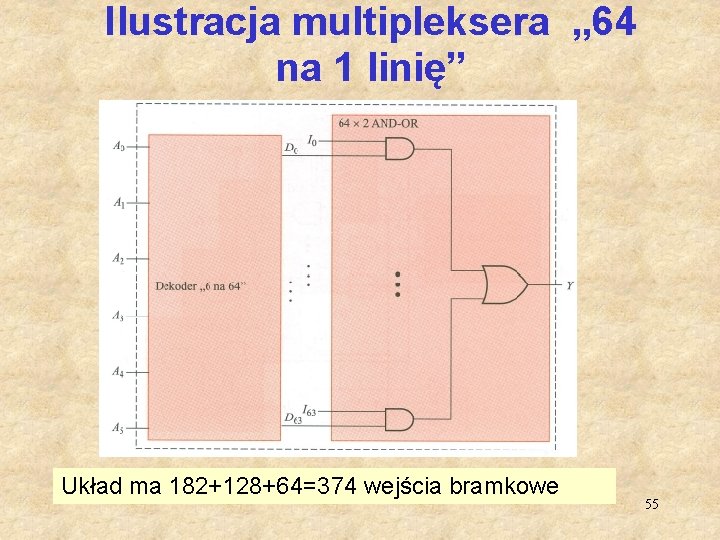

Ilustracja multipleksera „ 64 na 1 linię” Układ ma 182+128+64=374 wejścia bramkowe 55

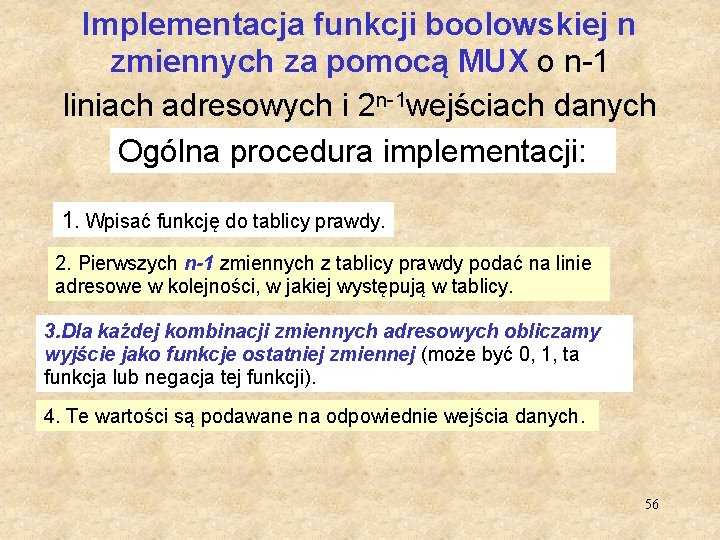

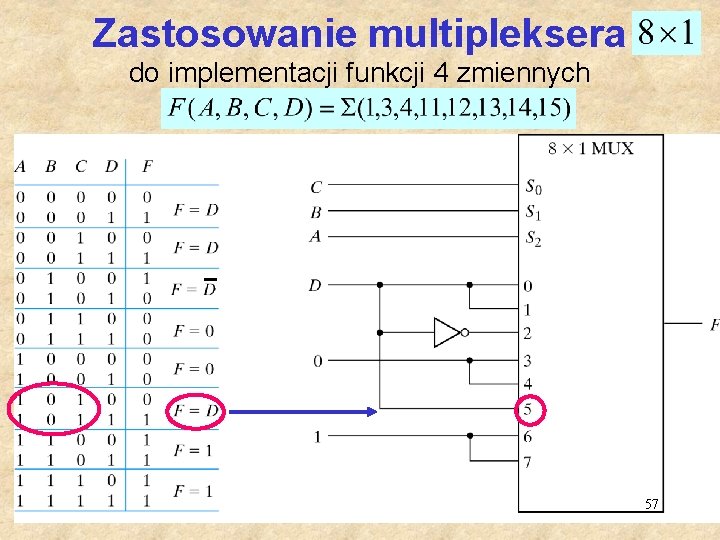

Implementacja funkcji boolowskiej n zmiennych za pomocą MUX o n-1 liniach adresowych i 2 n-1 wejściach danych Ogólna procedura implementacji: 1. Wpisać funkcję do tablicy prawdy. 2. Pierwszych n-1 zmiennych z tablicy prawdy podać na linie adresowe w kolejności, w jakiej występują w tablicy. 3. Dla każdej kombinacji zmiennych adresowych obliczamy wyjście jako funkcje ostatniej zmiennej (może być 0, 1, ta funkcja lub negacja tej funkcji). 4. Te wartości są podawane na odpowiednie wejścia danych. 56

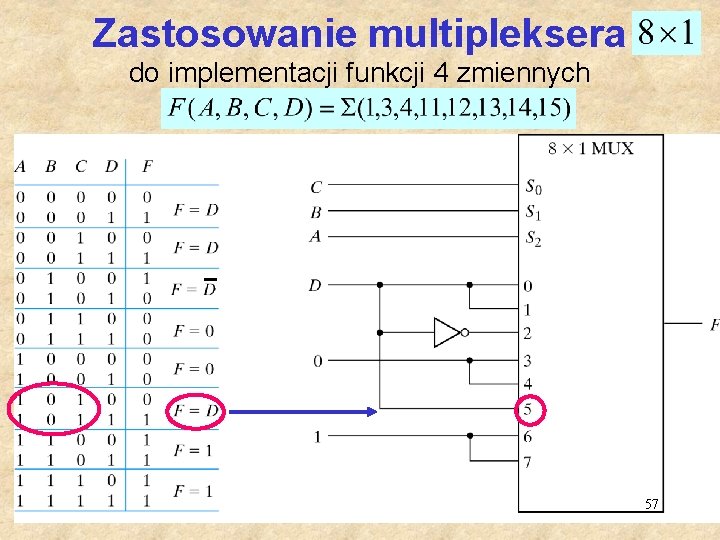

Zastosowanie multipleksera do implementacji funkcji 4 zmiennych 57

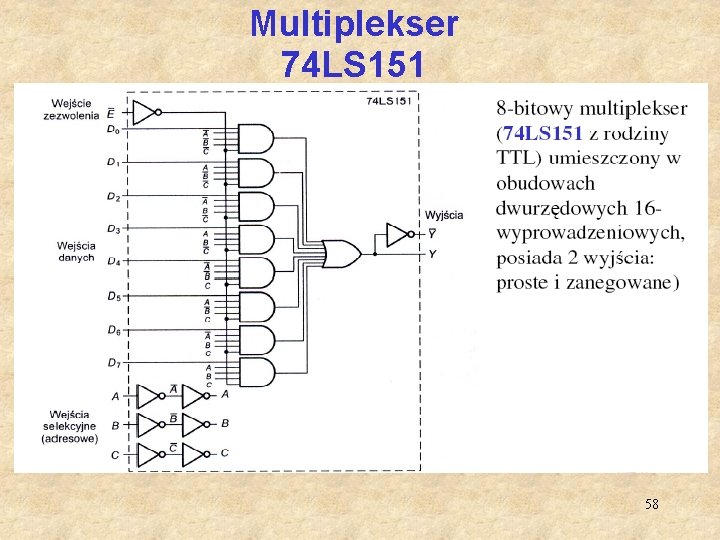

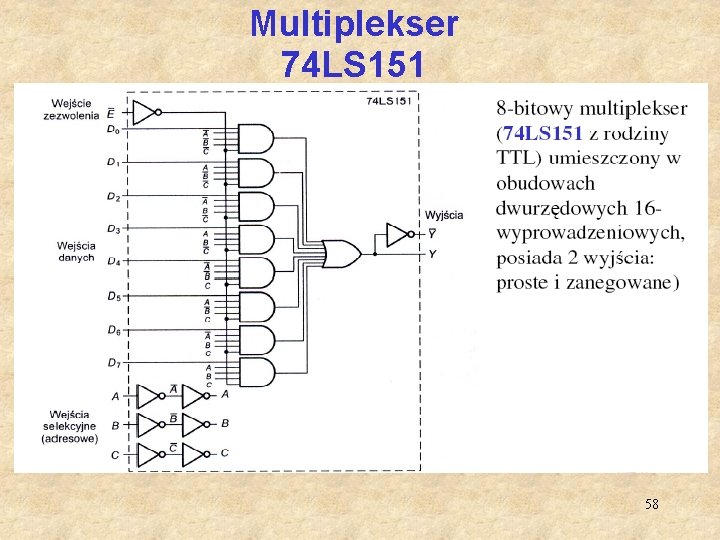

Multiplekser 74 LS 151 58

Dziękuję za uwagę 59

Wynik dodawania

Wynik dodawania Demultiplekser symbol

Demultiplekser symbol Cariova

Cariova Galina neledva

Galina neledva Paulina galina

Paulina galina Pardon

Pardon Galina gerasimova

Galina gerasimova Galina vakhrusheva

Galina vakhrusheva Matematički elementi topografske karte

Matematički elementi topografske karte Proprietà periodiche

Proprietà periodiche Legenda o potopu

Legenda o potopu Linha continua larga

Linha continua larga Legenda o valentinovu

Legenda o valentinovu Legenda o poznańskich koziołkach plan wydarzeń

Legenda o poznańskich koziołkach plan wydarzeń Legende o nastanku rima

Legende o nastanku rima Legenda peta

Legenda peta Legenda

Legenda Legenda o nastanku rima

Legenda o nastanku rima Legenda o nastanku hrvatskog grba

Legenda o nastanku hrvatskog grba Zemljevid slovenije pokrajine

Zemljevid slovenije pokrajine Legenda

Legenda Legenda o orle srebrnopiórym i radomskim grodzie

Legenda o orle srebrnopiórym i radomskim grodzie Legenda

Legenda Król który chciał się pozbyć smoka

Król który chciał się pozbyć smoka Osnutak rima

Osnutak rima Legenda desenho técnico a3 abnt

Legenda desenho técnico a3 abnt Sveti nikola svetac

Sveti nikola svetac Legenda figura

Legenda figura Dolazak hrvata strip

Dolazak hrvata strip Kaj prikazuje zemljevid

Kaj prikazuje zemljevid Biała i czarna legenda napoleona

Biała i czarna legenda napoleona Orientacija v prostoru

Orientacija v prostoru Kartografske boje

Kartografske boje Legenda o lajkoniku

Legenda o lajkoniku Como colocar legenda em imagem abnt

Como colocar legenda em imagem abnt Crita rakyat diwarisake kanthi cara

Crita rakyat diwarisake kanthi cara Legenda

Legenda Gênero textual legenda

Gênero textual legenda Legenda do desenho tecnico

Legenda do desenho tecnico Mapch

Mapch Limes romanus

Limes romanus Legenda o ljubavi

Legenda o ljubavi Veronika deseniška legenda

Veronika deseniška legenda Legenda o založení rima

Legenda o založení rima Sestavine zemljevida

Sestavine zemljevida Legenda peta

Legenda peta Migratiestrategie

Migratiestrategie Legenda o syrence warszawskiej - plan wydarzeń

Legenda o syrence warszawskiej - plan wydarzeń Ciklus o glembajevima

Ciklus o glembajevima Sta je narodna balada

Sta je narodna balada Legenda diagrama unifilar

Legenda diagrama unifilar Legenda

Legenda Skąd pochodzi nazwa andrzejki

Skąd pochodzi nazwa andrzejki Kaj je legenda na zemljevidu

Kaj je legenda na zemljevidu Legenda desenho técnico a4

Legenda desenho técnico a4 Lucija grgic

Lucija grgic Filozofija

Filozofija Romeniski skaiciai

Romeniski skaiciai Opowiadanie fantastyczne o gradzie

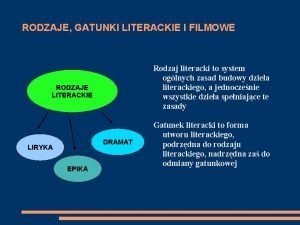

Opowiadanie fantastyczne o gradzie Gatunki literackie

Gatunki literackie