VHDL Structural Architecture ENG 2410 Week 5 VHDL

- Slides: 15

VHDL Structural Architecture ENG 2410 Week #5

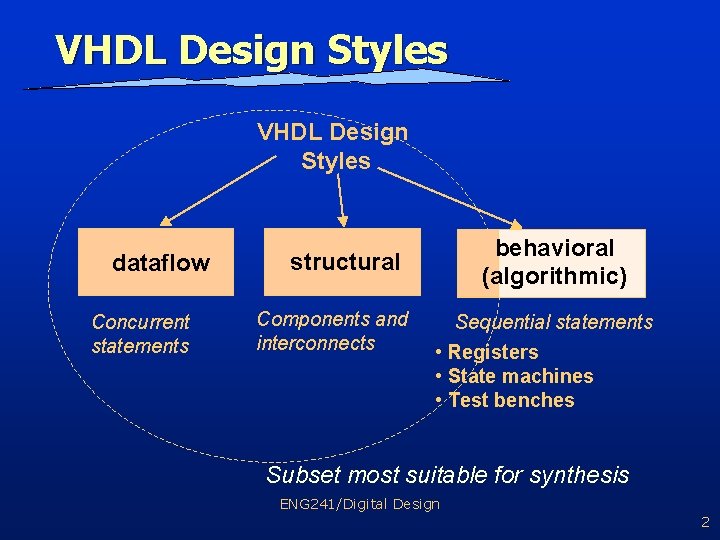

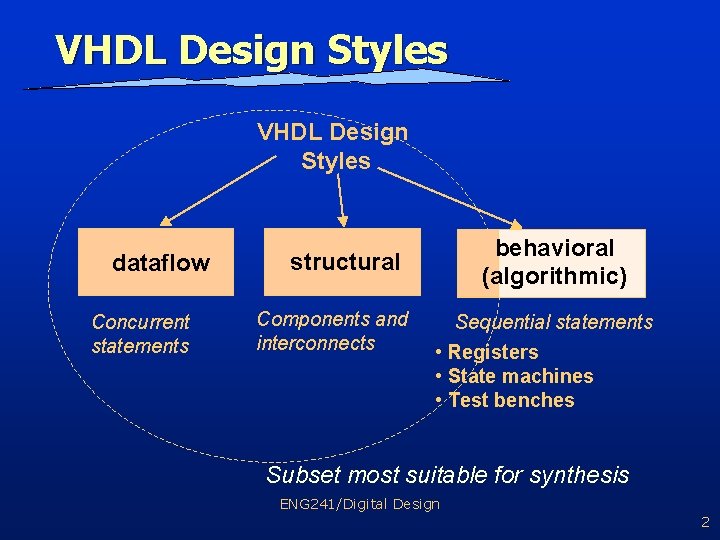

VHDL Design Styles dataflow Concurrent statements behavioral (algorithmic) structural Components and interconnects Sequential statements • Registers • State machines • Test benches Subset most suitable for synthesis ENG 241/Digital Design 2

Example – 4 -bit Equality Specifications: o Input: 2 vectors A(3: 0) and B(3: 0) o Output: One bit, E, which is 1 if A and B are bitwise equal, 0 otherwise ENG 241/Digital Design 3

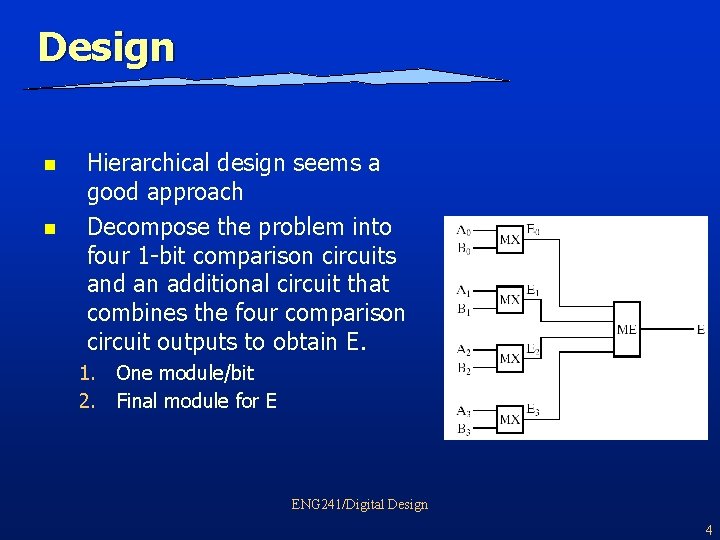

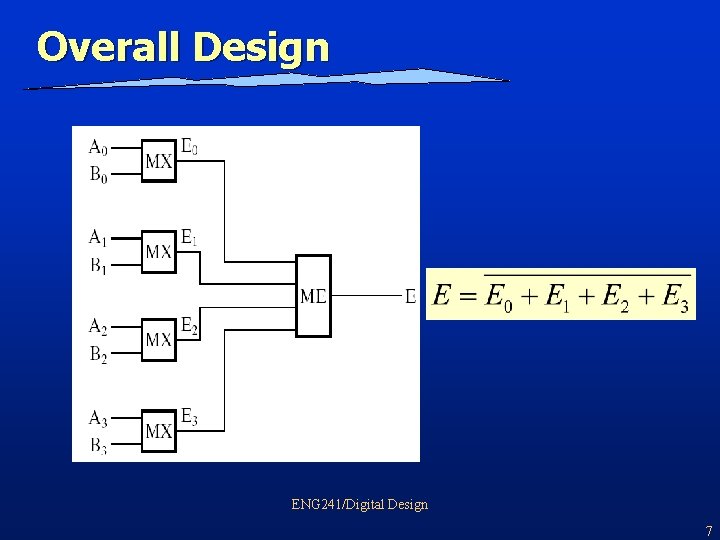

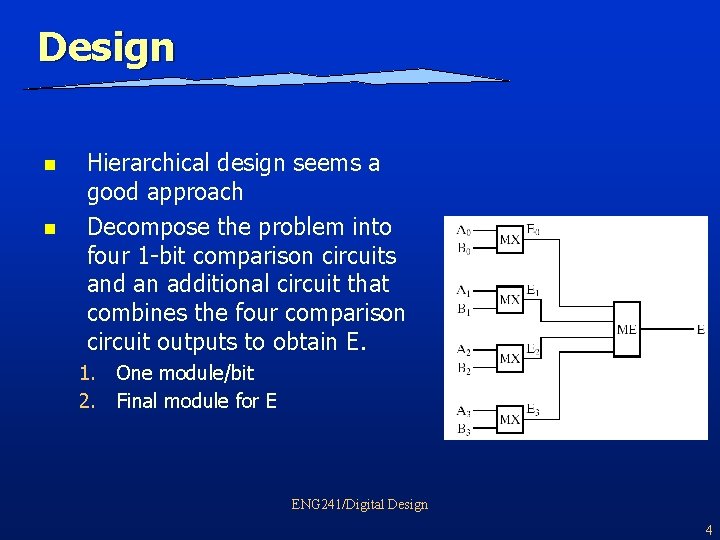

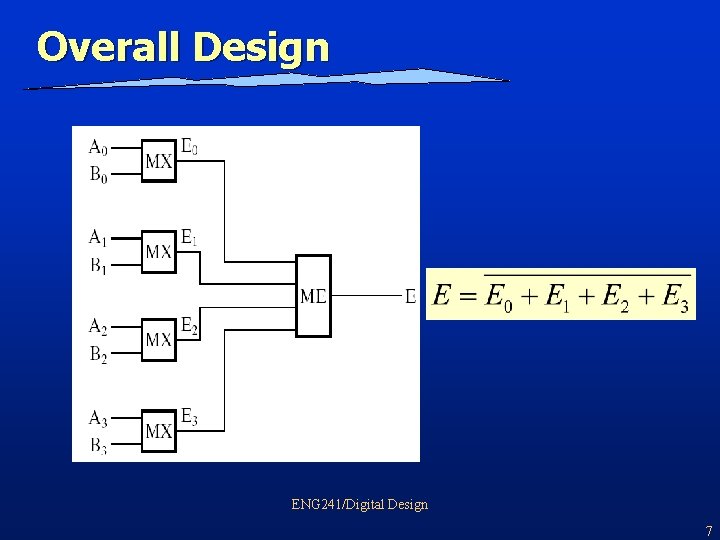

Design n n Hierarchical design seems a good approach Decompose the problem into four 1 -bit comparison circuits and an additional circuit that combines the four comparison circuit outputs to obtain E. 1. One module/bit 2. Final module for E ENG 241/Digital Design 4

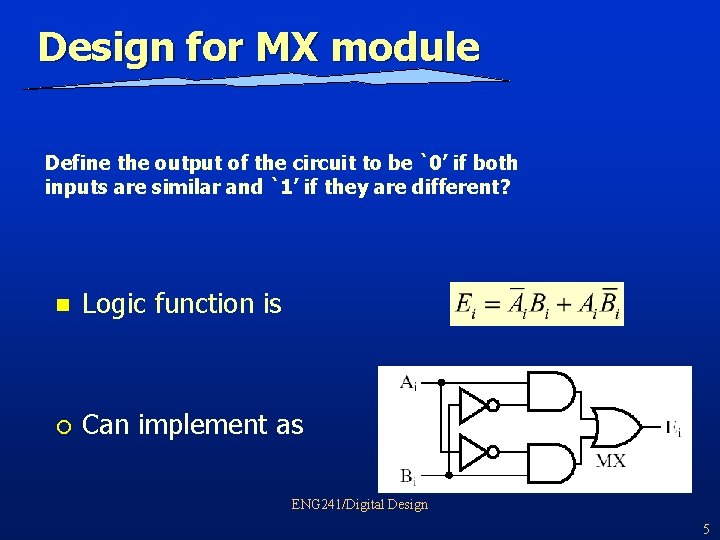

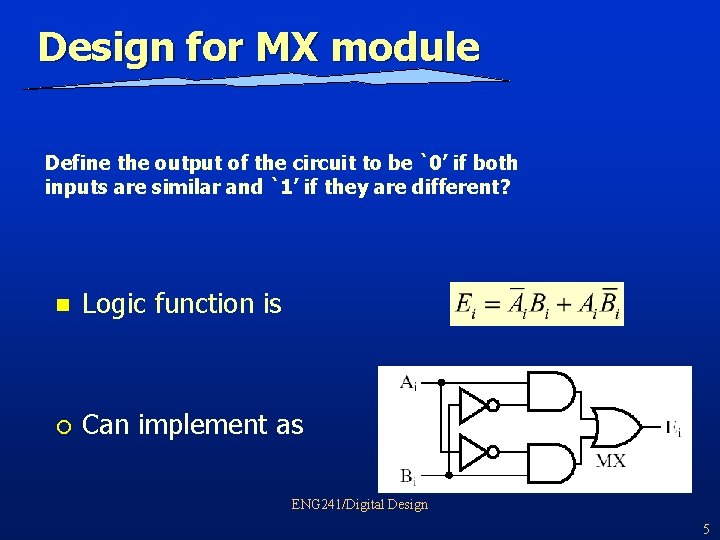

Design for MX module Define the output of the circuit to be `0’ if both inputs are similar and `1’ if they are different? n Logic function is ¡ Can implement as ENG 241/Digital Design 5

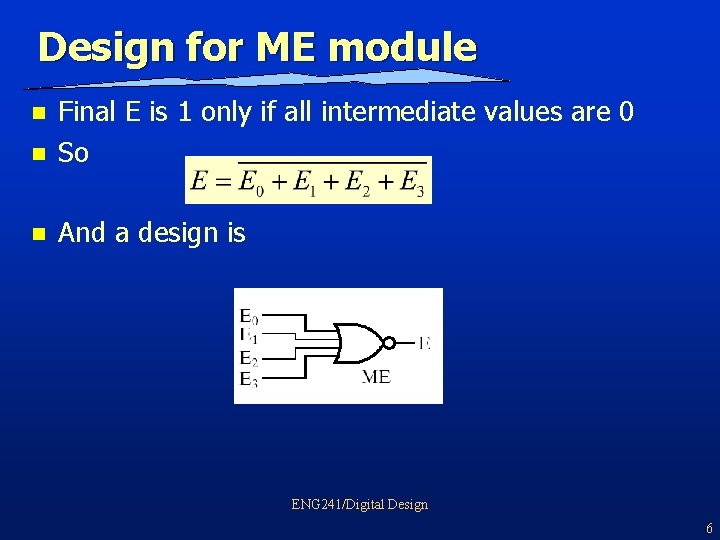

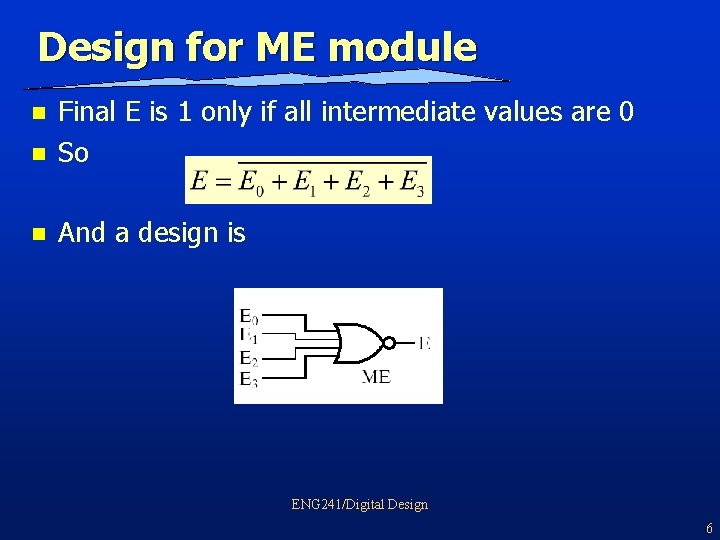

Design for ME module n Final E is 1 only if all intermediate values are 0 So n And a design is n ENG 241/Digital Design 6

Overall Design ENG 241/Digital Design 7

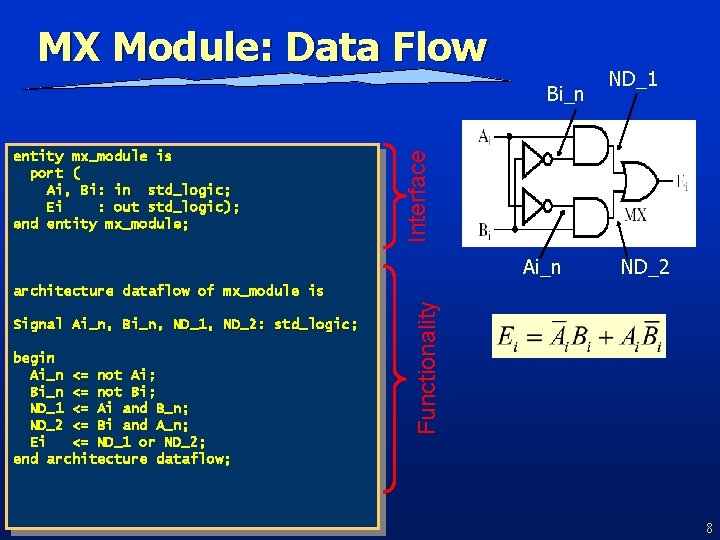

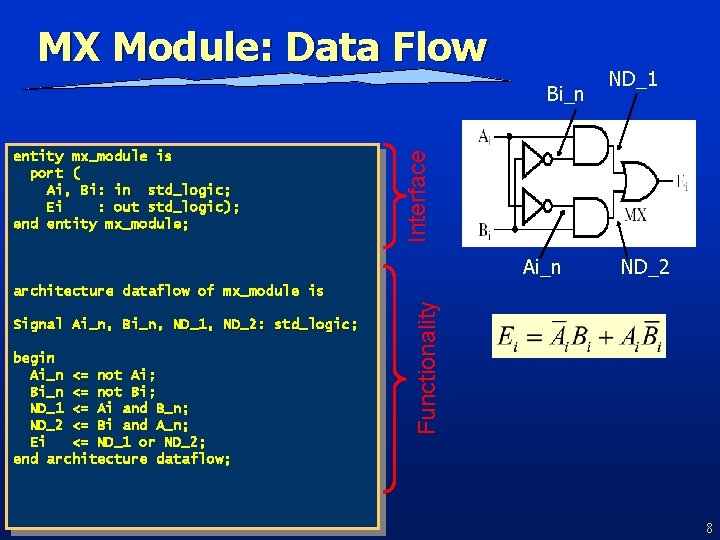

MX Module: Data Flow entity mx_module is port ( Ai, Bi: in std_logic; Ei : out std_logic); end entity mx_module; Interface Bi_n ND_1 Ai_n ND_2 Signal Ai_n, Bi_n, ND_1, ND_2: std_logic; begin Ai_n <= not Ai; Bi_n <= not Bi; ND_1 <= Ai and B_n; ND_2 <= Bi and A_n; Ei <= ND_1 or ND_2; end architecture dataflow; Functionality architecture dataflow of mx_module is 8

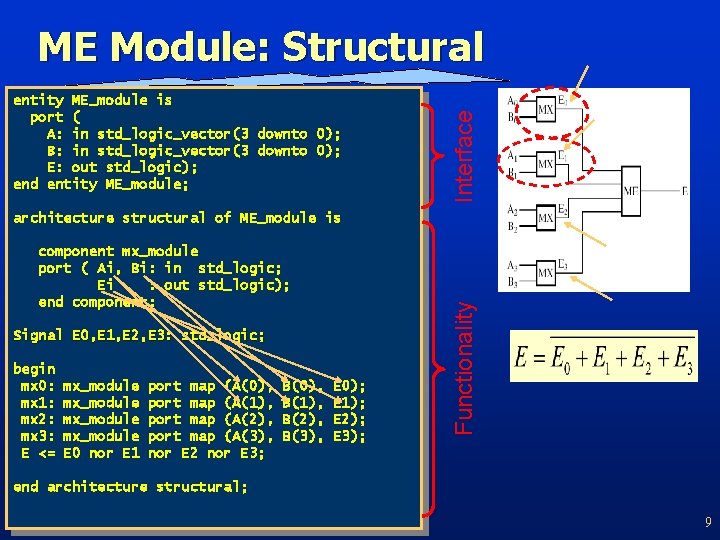

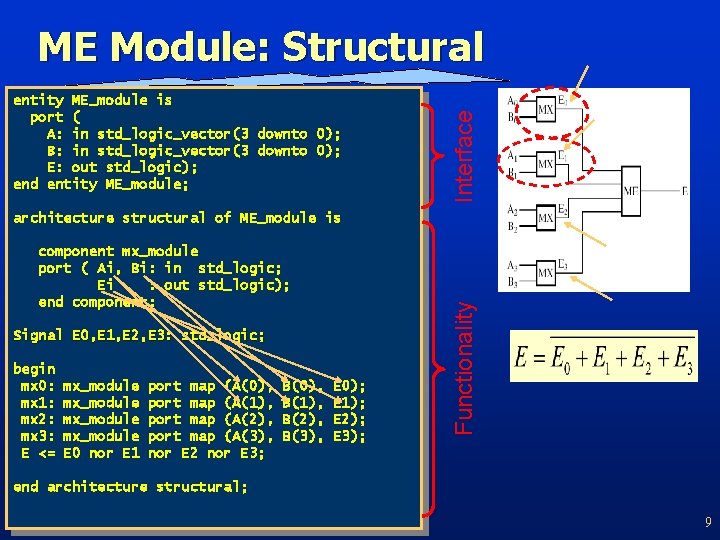

entity ME_module is port ( A: in std_logic_vector(3 downto 0); B: in std_logic_vector(3 downto 0); E: out std_logic); end entity ME_module; Interface ME Module: Structural component mx_module port ( Ai, Bi: in std_logic; Ei : out std_logic); end component; Signal E 0, E 1, E 2, E 3: std_logic; begin mx 0: mx 1: mx 2: mx 3: E <= mx_module E 0 nor E 1 port map (A(0), port map (A(1), port map (A(2), port map (A(3), nor E 2 nor E 3; B(0), B(1), B(2), B(3), E 0); E 1); E 2); E 3); Functionality architecture structural of ME_module is end architecture structural; 9

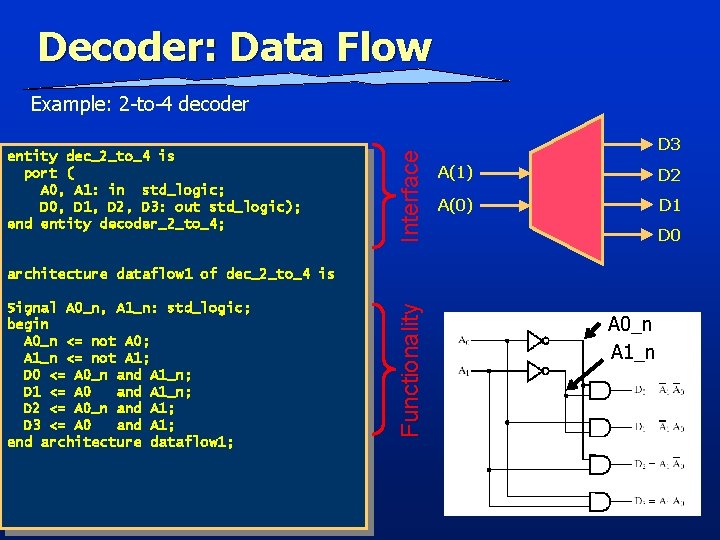

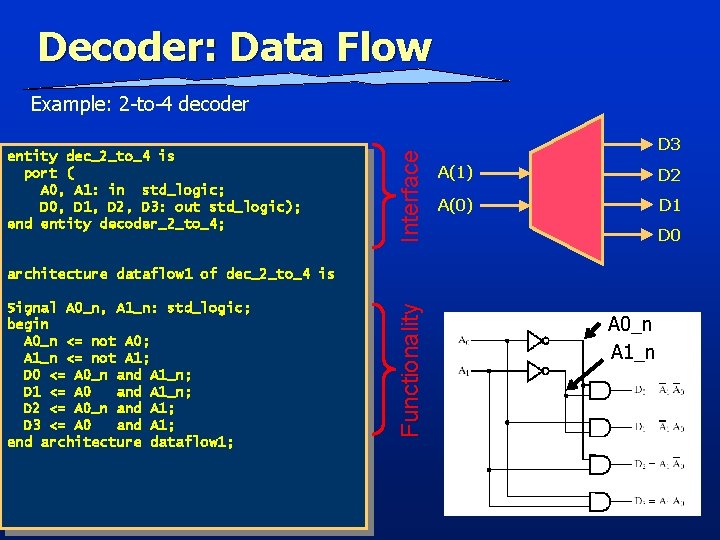

Decoder: Data Flow entity dec_2_to_4 is port ( A 0, A 1: in std_logic; D 0, D 1, D 2, D 3: out std_logic); end entity decoder_2_to_4; Interface Example: 2 -to-4 decoder D 3 A(1) D 2 A(0) D 1 D 0 Signal A 0_n, A 1_n: std_logic; begin A 0_n <= not A 0; A 1_n <= not A 1; D 0 <= A 0_n and A 1_n; D 1 <= A 0 and A 1_n; D 2 <= A 0_n and A 1; D 3 <= A 0 and A 1; end architecture dataflow 1; Functionality architecture dataflow 1 of dec_2_to_4 is A 0_n A 1_n 10

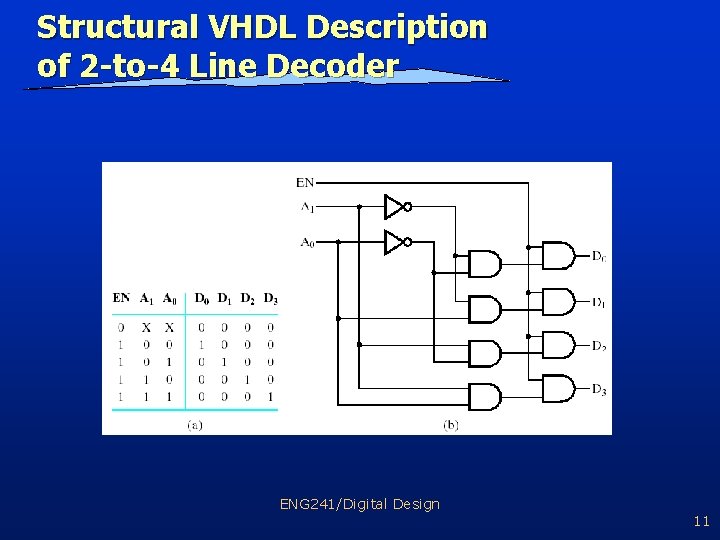

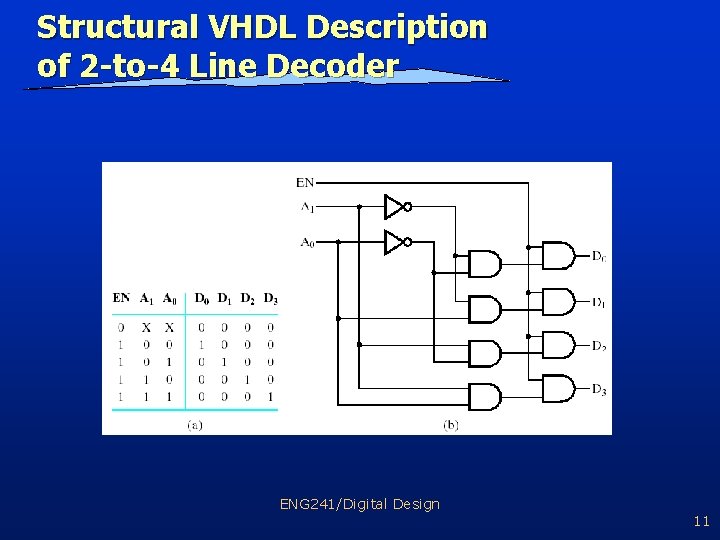

Structural VHDL Description of 2 -to-4 Line Decoder ENG 241/Digital Design 11

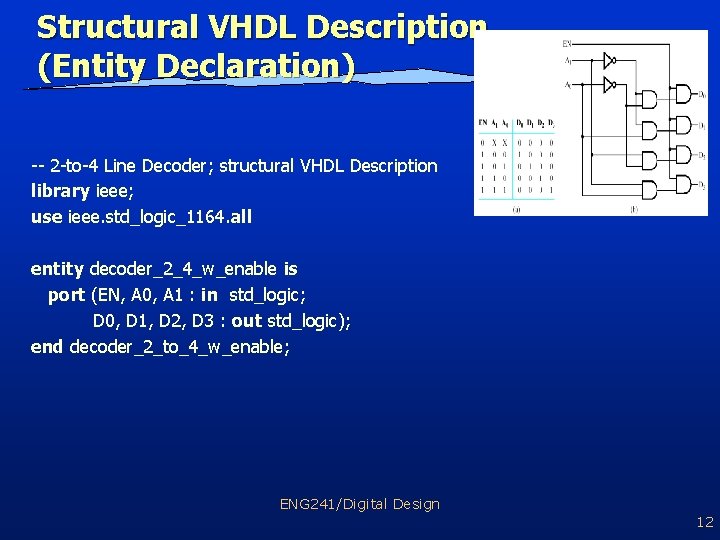

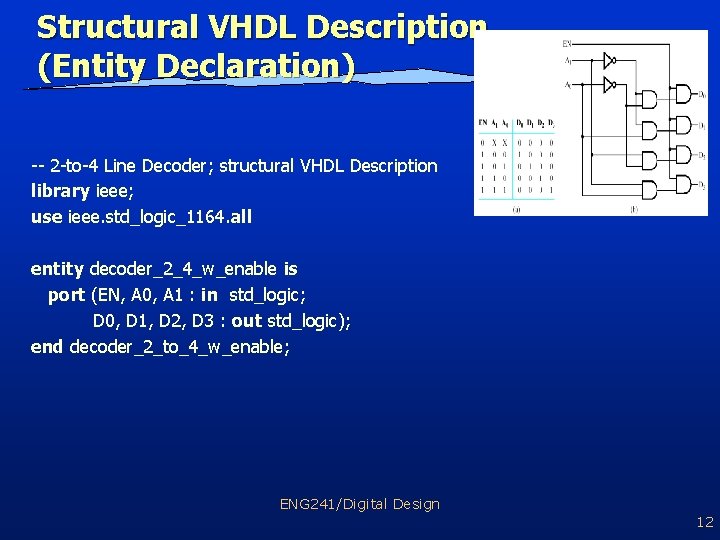

Structural VHDL Description (Entity Declaration) -- 2 -to-4 Line Decoder; structural VHDL Description library ieee; use ieee. std_logic_1164. all entity decoder_2_4_w_enable is port (EN, A 0, A 1 : in std_logic; D 0, D 1, D 2, D 3 : out std_logic); end decoder_2_to_4_w_enable; ENG 241/Digital Design 12

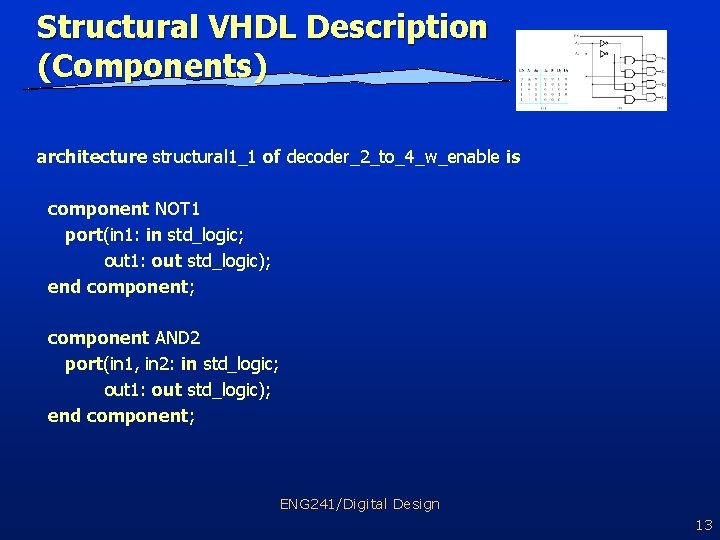

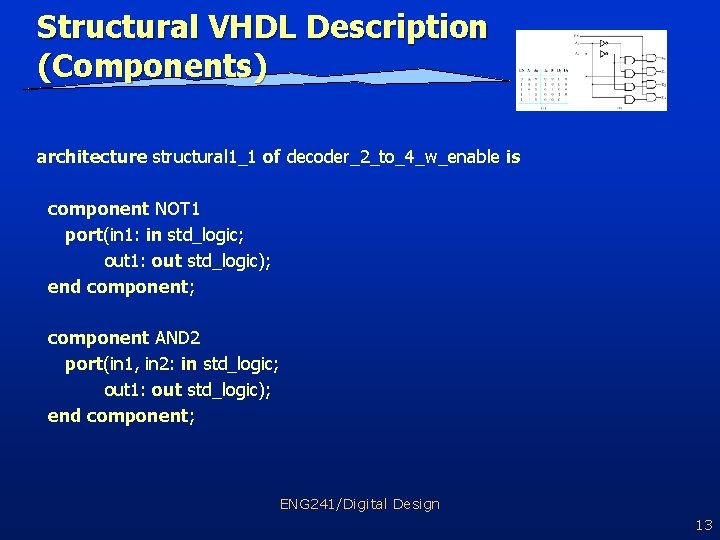

Structural VHDL Description (Components) architecture structural 1_1 of decoder_2_to_4_w_enable is component NOT 1 port(in 1: in std_logic; out 1: out std_logic); end component; component AND 2 port(in 1, in 2: in std_logic; out 1: out std_logic); end component; ENG 241/Digital Design 13

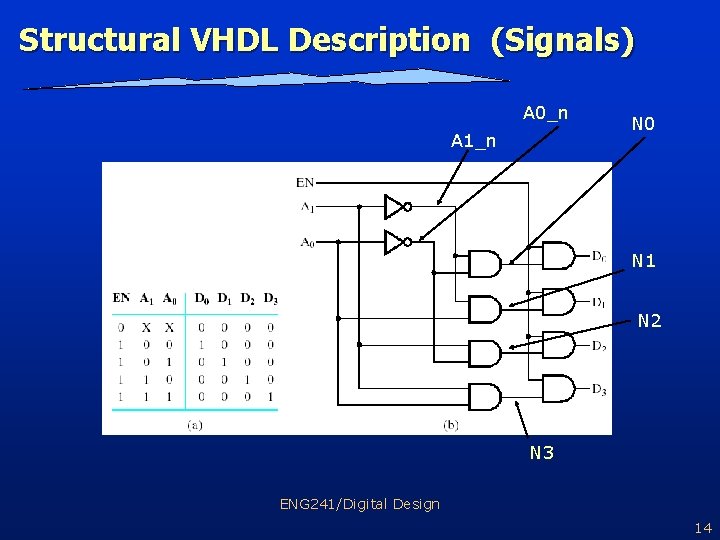

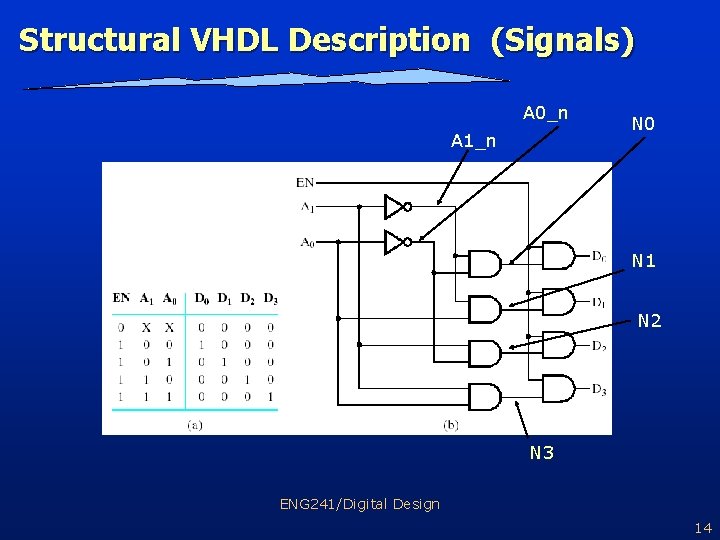

Structural VHDL Description (Signals) A 0_n A 1_n N 0 N 1 N 2 N 3 ENG 241/Digital Design 14

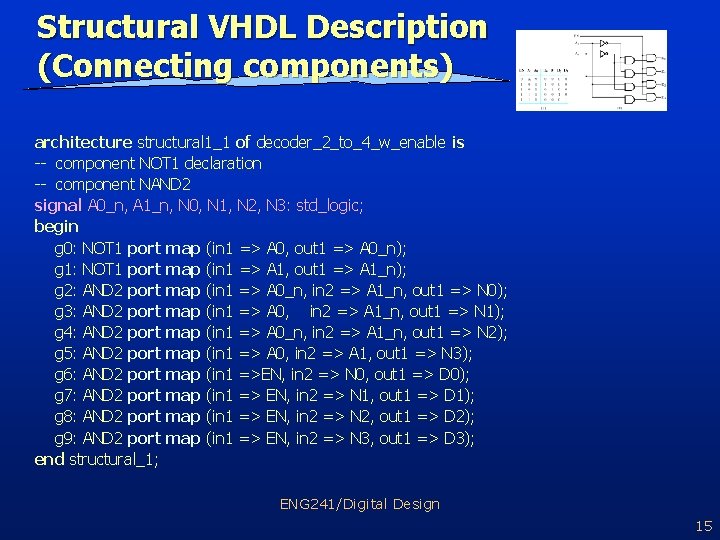

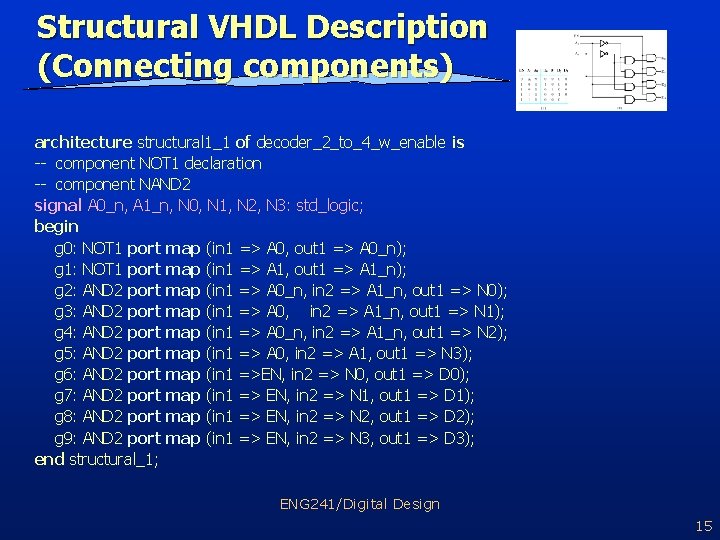

Structural VHDL Description (Connecting components) architecture structural 1_1 of decoder_2_to_4_w_enable is -- component NOT 1 declaration -- component NAND 2 signal A 0_n, A 1_n, N 0, N 1, N 2, N 3: std_logic; begin g 0: NOT 1 port map (in 1 => A 0, out 1 => A 0_n); g 1: NOT 1 port map (in 1 => A 1, out 1 => A 1_n); g 2: AND 2 port map (in 1 => A 0_n, in 2 => A 1_n, out 1 => N 0); g 3: AND 2 port map (in 1 => A 0, in 2 => A 1_n, out 1 => N 1); g 4: AND 2 port map (in 1 => A 0_n, in 2 => A 1_n, out 1 => N 2); g 5: AND 2 port map (in 1 => A 0, in 2 => A 1, out 1 => N 3); g 6: AND 2 port map (in 1 =>EN, in 2 => N 0, out 1 => D 0); g 7: AND 2 port map (in 1 => EN, in 2 => N 1, out 1 => D 1); g 8: AND 2 port map (in 1 => EN, in 2 => N 2, out 1 => D 2); g 9: AND 2 port map (in 1 => EN, in 2 => N 3, out 1 => D 3); end structural_1; ENG 241/Digital Design 15