ENG 2410 Digital Design Week 4 Combinational Logic

ENG 2410 Digital Design: Week #4 “Combinational Logic Design” S. Areibi School of Engineering University of Guelph

Week #4: Topics ¡ Decoders l ¡ Encoders l ¡ Priority Encoders Multiplexers l ¡ Combinational circuit Implementation Combinational Circuit Implementation Demultiplexers

Resources Chapter #4, Mano Sections l l l 4. 1 4. 3 4. 4 4. 5 4. 6 Combinational Circuits Decoding Encoding Multiplexers Comb Function Implementations

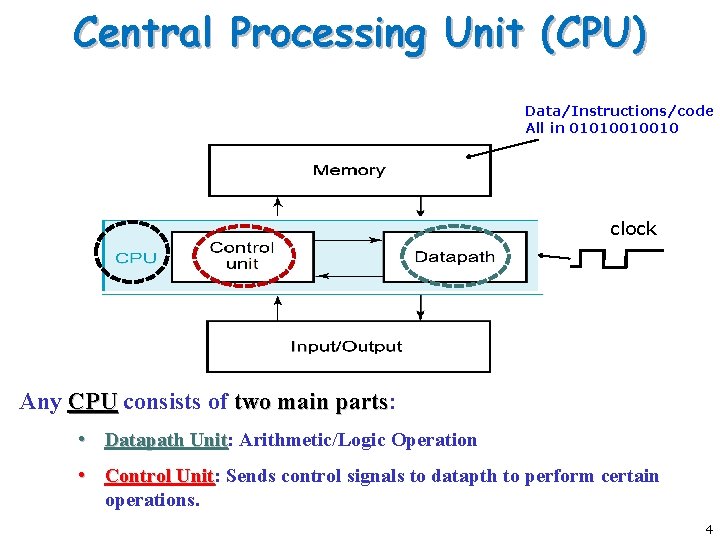

Central Processing Unit (CPU) Data/Instructions/code All in 01010010010 clock Any CPU consists of two main parts: parts • Datapath Unit: Unit Arithmetic/Logic Operation • Control Unit: Unit Sends control signals to datapth to perform certain operations. 4

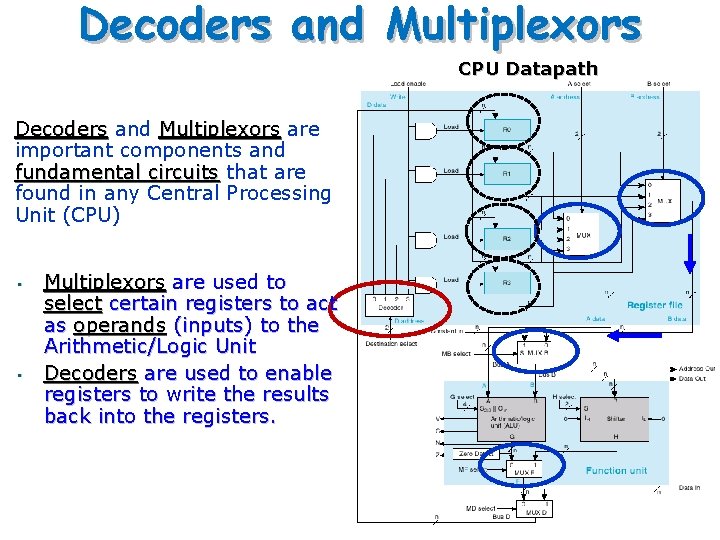

Decoders and Multiplexors CPU Datapath Decoders and Multiplexors are important components and fundamental circuits that are found in any Central Processing Unit (CPU) • • Multiplexors are used to select certain registers to act as operands (inputs) to the Arithmetic/Logic Unit Decoders are used to enable registers to write the results back into the registers.

Decoders

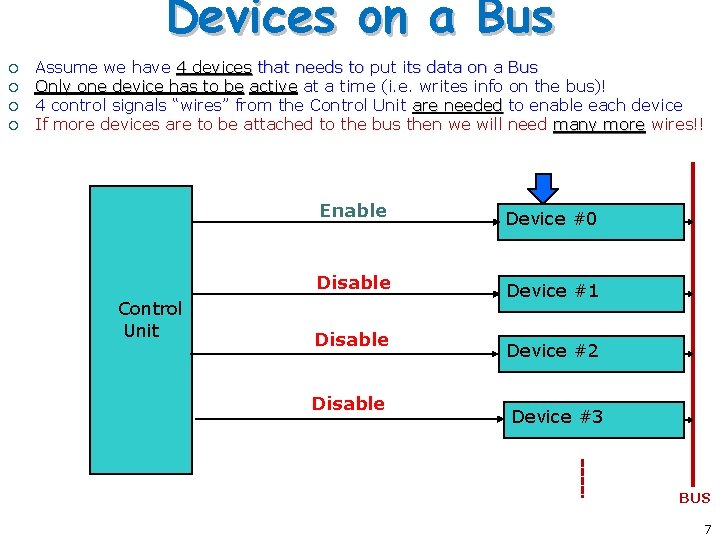

Devices on a Bus ¡ ¡ Assume we have 4 devices that needs to put its data on a Bus Only one device has to be active at a time (i. e. writes info on the bus)! 4 control signals “wires” from the Control Unit are needed to enable each device If more devices are to be attached to the bus then we will need many more wires!! Control Unit Enable Device #0 Disable Device #1 Disable Device #2 Device #3 BUS 7

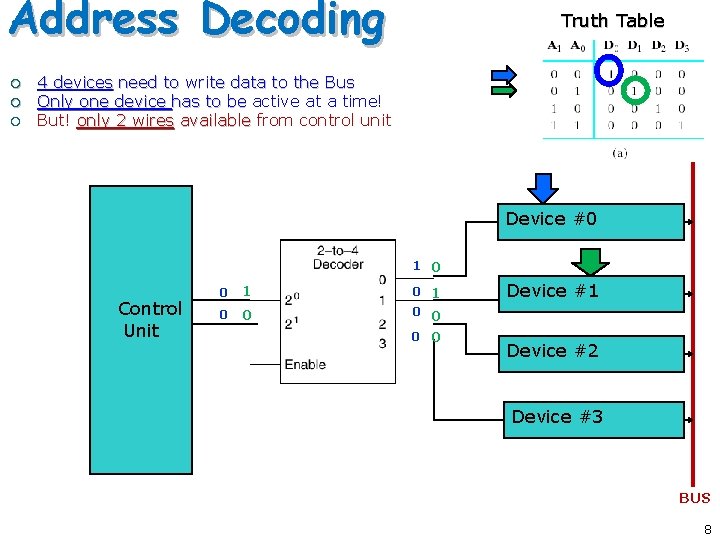

Address Decoding ¡ ¡ ¡ Truth Table 4 devices need to write data to the Bus Only one device has to be active at a time! But! only 2 wires available from control unit Device #0 1 0 Control Unit 0 1 0 0 0 0 Device #1 Device #2 Device #3 BUS 8

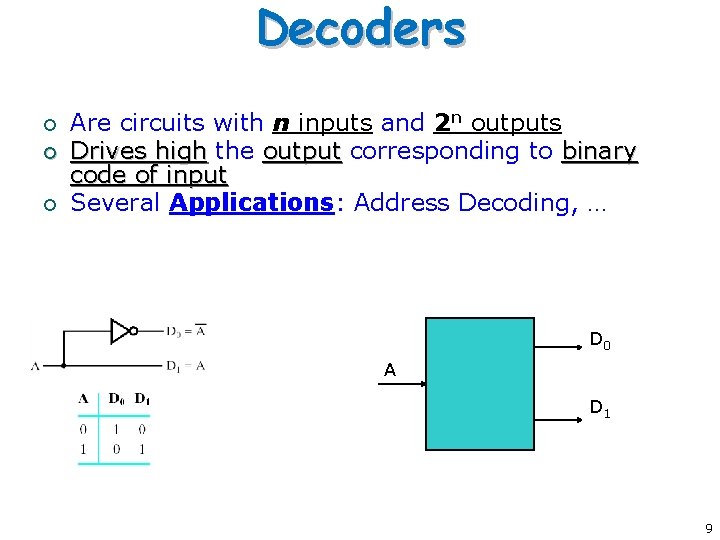

Decoders ¡ ¡ ¡ Are circuits with n inputs and 2 n outputs Drives high the output corresponding to binary code of input Several Applications: Address Decoding, … D 0 A D 1 9

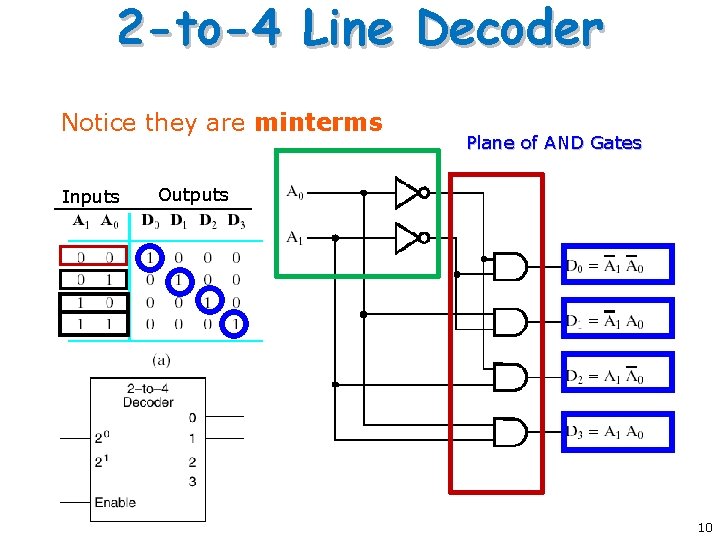

2 -to-4 Line Decoder Notice they are minterms Inputs Plane of AND Gates Outputs 10

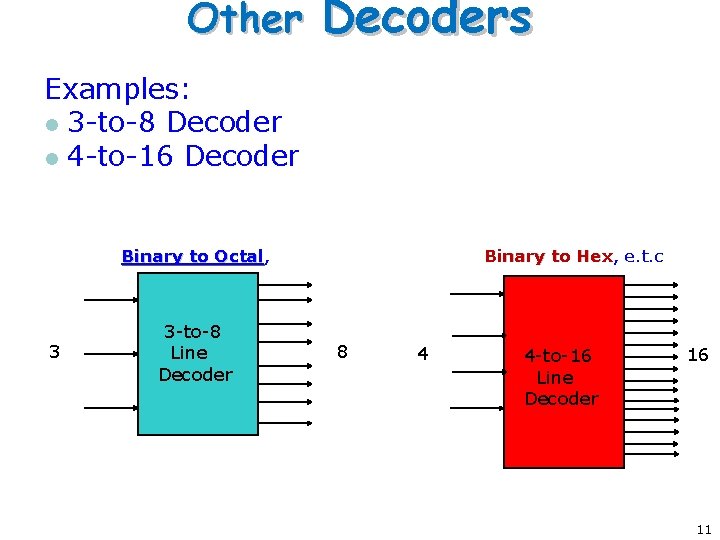

Other Decoders Examples: l 3 -to-8 Decoder l 4 -to-16 Decoder Binary to Hex, Hex e. t. c Binary to Octal, Octal 3 3 -to-8 Line Decoder 8 4 4 -to-16 Line Decoder 16 11

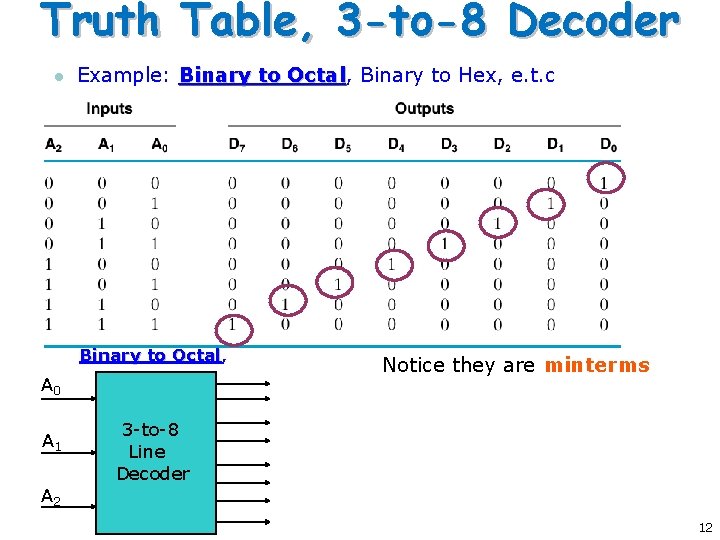

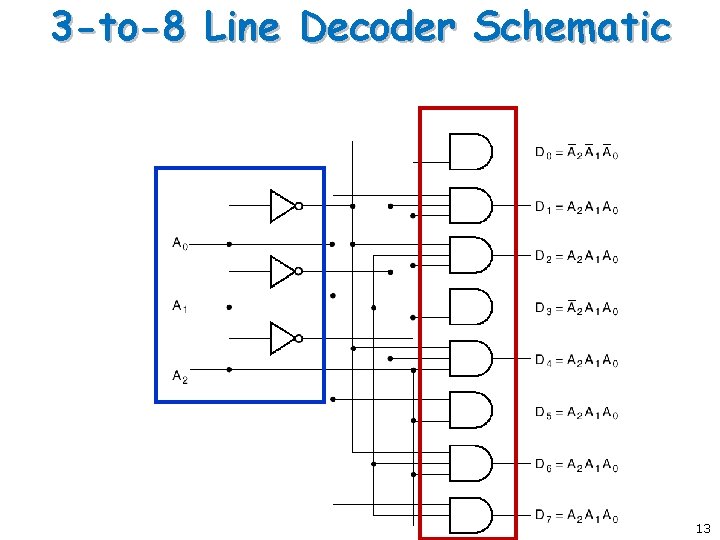

Truth Table, 3 -to-8 Decoder l Example: Binary to Octal, Octal Binary to Hex, e. t. c Binary to Octal, Octal A 0 A 1 Notice they are minterms 3 -to-8 Line Decoder A 2 12

3 -to-8 Line Decoder Schematic 13

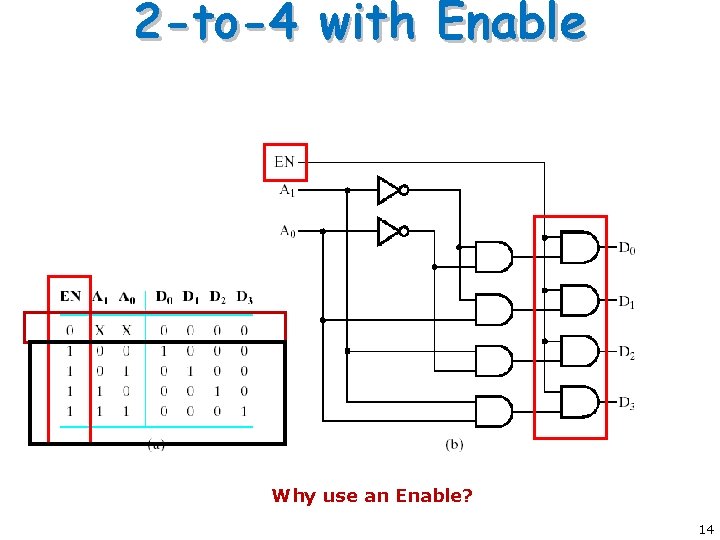

2 -to-4 with Enable Why use an Enable? 14

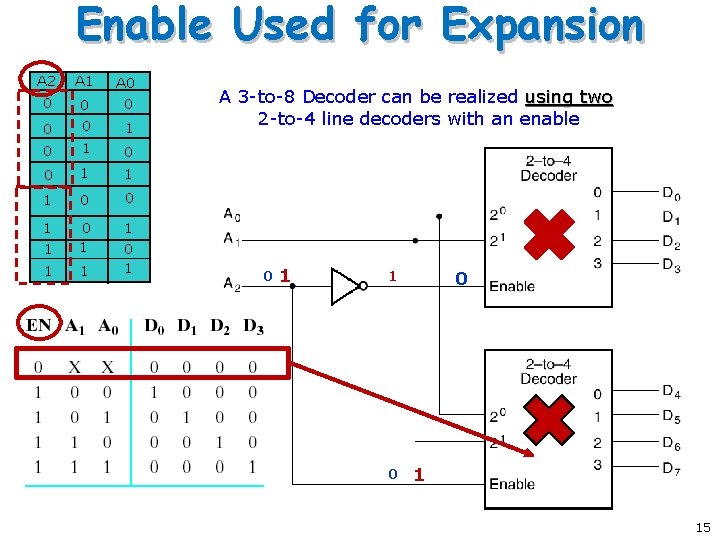

Enable Used for Expansion A 2 A 1 0 0 A 0 0 1 1 1 0 0 1 1 1 1 0 1 A 3 -to-8 Decoder can be realized using two 2 -to-4 line decoders with an enable 0 1 0 1 15

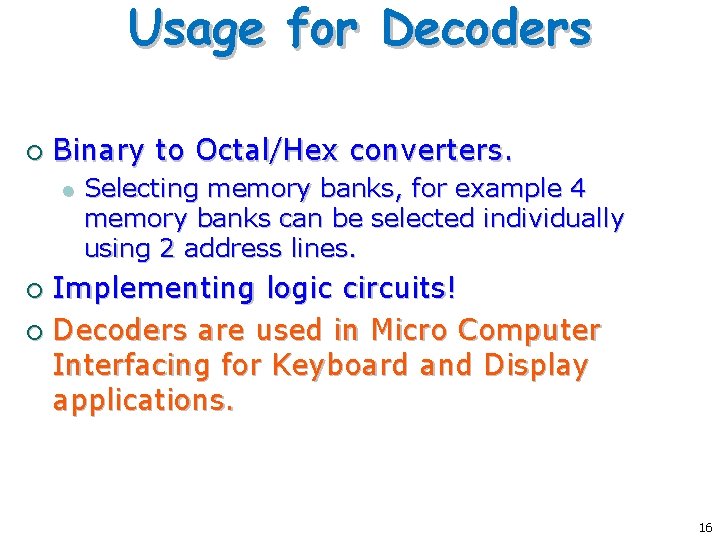

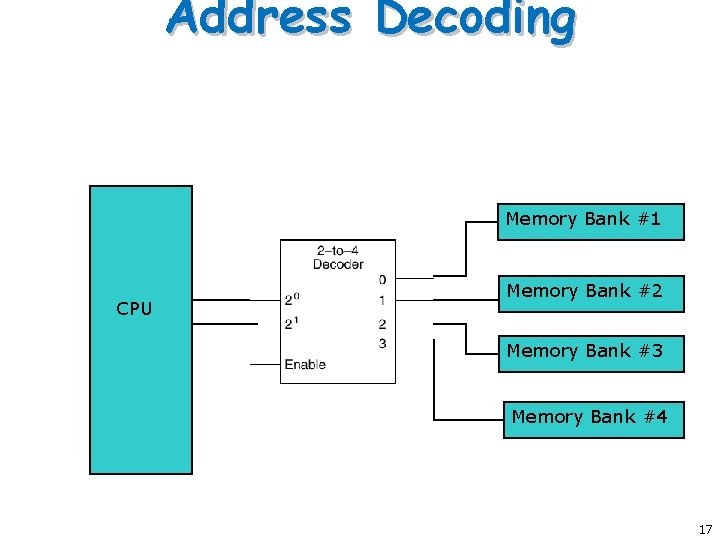

Usage for Decoders ¡ Binary to Octal/Hex converters. l Selecting memory banks, for example 4 memory banks can be selected individually using 2 address lines. Implementing logic circuits! ¡ Decoders are used in Micro Computer Interfacing for Keyboard and Display applications. ¡ 16

Address Decoding Memory Bank #1 CPU Memory Bank #2 Memory Bank #3 Memory Bank #4 17

Decoders: Logic Implementation

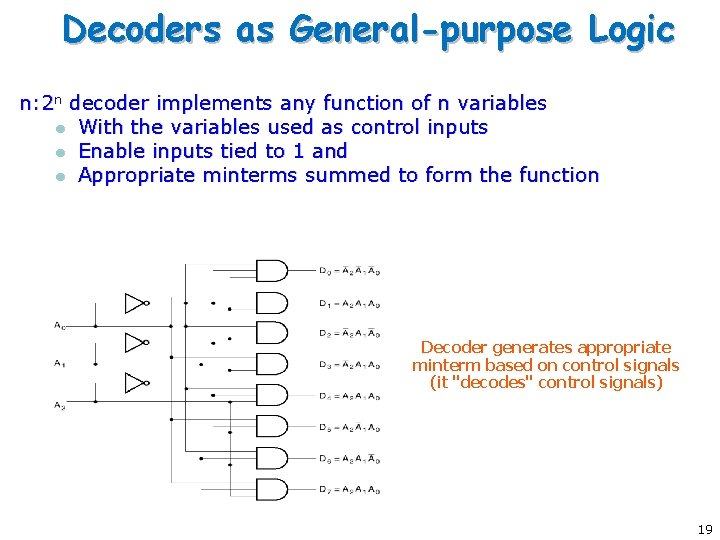

Decoders as General-purpose Logic n: 2 n decoder implements any function of n variables l With the variables used as control inputs l Enable inputs tied to 1 and l Appropriate minterms summed to form the function Decoder generates appropriate minterm based on control signals (it "decodes" control signals) 19

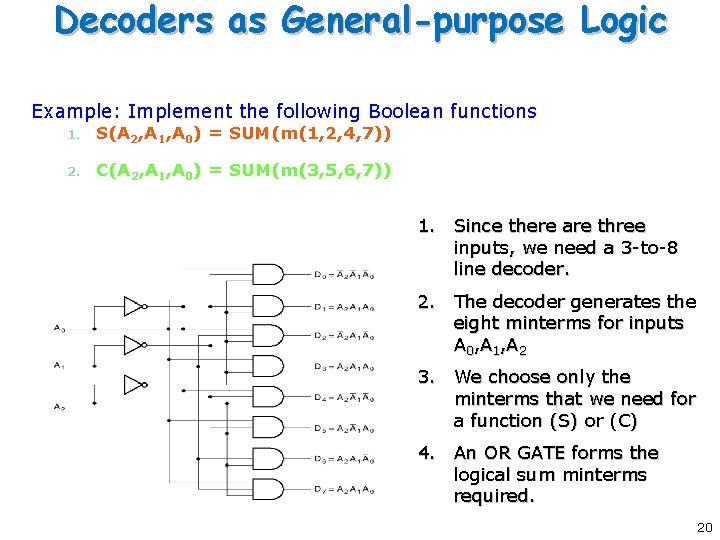

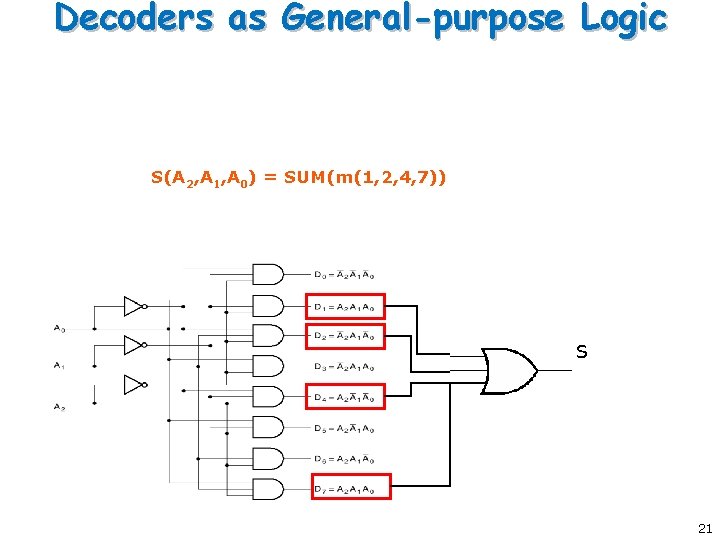

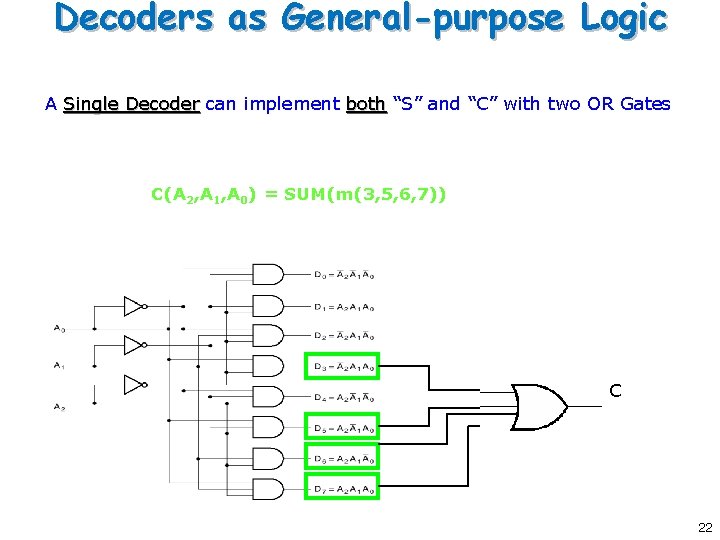

Decoders as General-purpose Logic Example: Implement the following Boolean functions 1. S(A 2, A 1, A 0) = SUM(m(1, 2, 4, 7)) 2. C(A 2, A 1, A 0) = SUM(m(3, 5, 6, 7)) 1. Since there are three inputs, we need a 3 -to-8 line decoder. 2. The decoder generates the eight minterms for inputs A 0, A 1, A 2 3. We choose only the minterms that we need for a function (S) or (C) 4. An OR GATE forms the logical sum minterms required. 20

Decoders as General-purpose Logic S(A 2, A 1, A 0) = SUM(m(1, 2, 4, 7)) S 21

Decoders as General-purpose Logic A Single Decoder can implement both “S” and “C” with two OR Gates C(A 2, A 1, A 0) = SUM(m(3, 5, 6, 7)) C 22

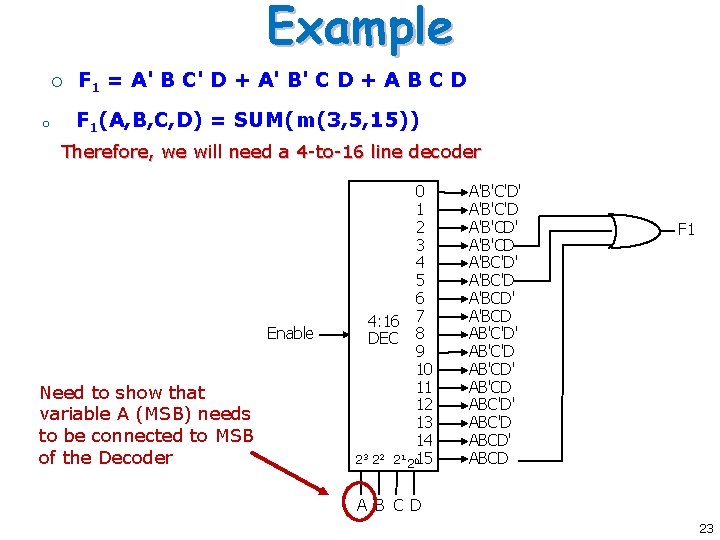

Example ¡ o F 1 = A' B C' D + A' B' C D + A B C D F 1(A, B, C, D) = SUM(m(3, 5, 15)) Therefore, we will need a 4 -to-16 line decoder Enable Need to show that variable A (MSB) needs to be connected to MSB of the Decoder 0 1 2 3 4 5 6 4: 16 7 DEC 8 9 10 11 12 13 14 23 22 21 2015 A'B'C'D' A'B'C'D A'B'CD' A'B'CD A'BC'D' A'BC'D A'BCD' A'BCD AB'C'D' AB'C'D AB'CD' AB'CD ABC'D' ABC'D ABCD' ABCD F 1 A B C D 23

Encoders

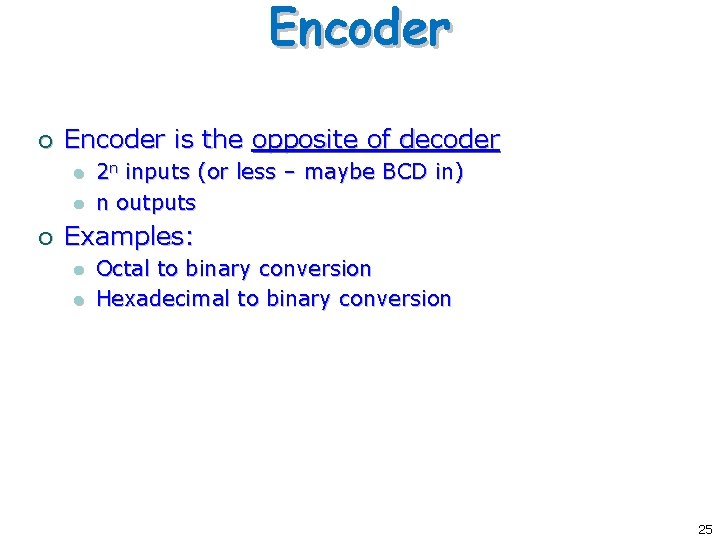

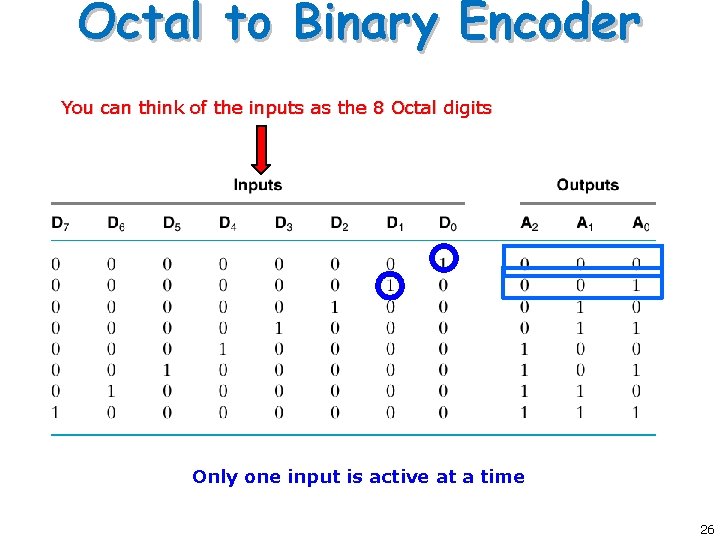

Encoder ¡ Encoder is the opposite of decoder l l ¡ 2 n inputs (or less – maybe BCD in) n outputs Examples: l l Octal to binary conversion Hexadecimal to binary conversion 25

Octal to Binary Encoder You can think of the inputs as the 8 Octal digits Only one input is active at a time 26

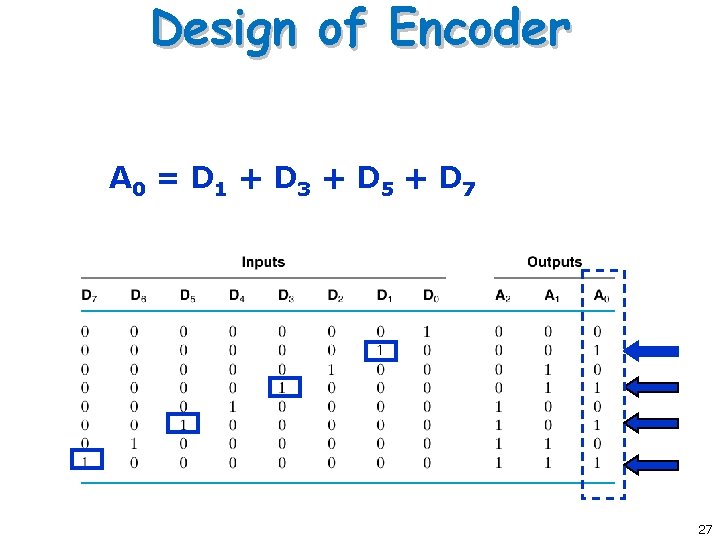

Design of Encoder A 0 = D 1 + D 3 + D 5 + D 7 27

Multiplexors

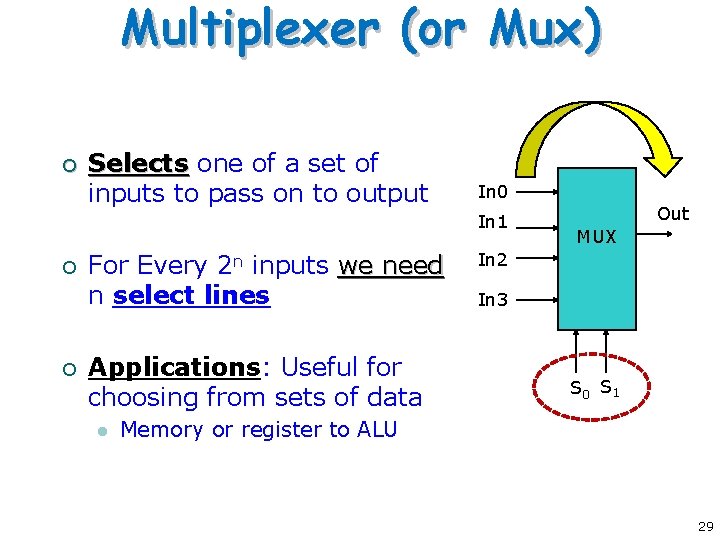

Multiplexer (or Mux) ¡ Selects one of a set of inputs to pass on to output In 0 In 1 ¡ ¡ For Every 2 n inputs we need n select lines Applications: Useful for choosing from sets of data l Out MUX In 2 In 3 S 0 S 1 Memory or register to ALU 29

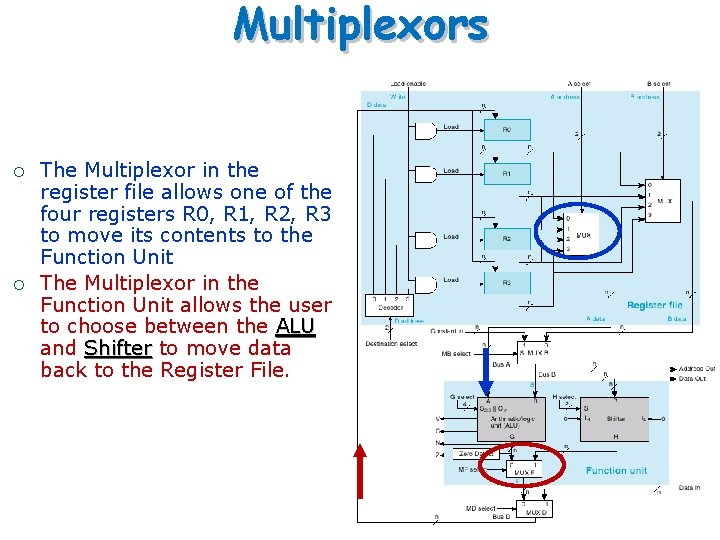

Multiplexors ¡ ¡ The Multiplexor in the register file allows one of the four registers R 0, R 1, R 2, R 3 to move its contents to the Function Unit The Multiplexor in the Function Unit allows the user to choose between the ALU and Shifter to move data back to the Register File.

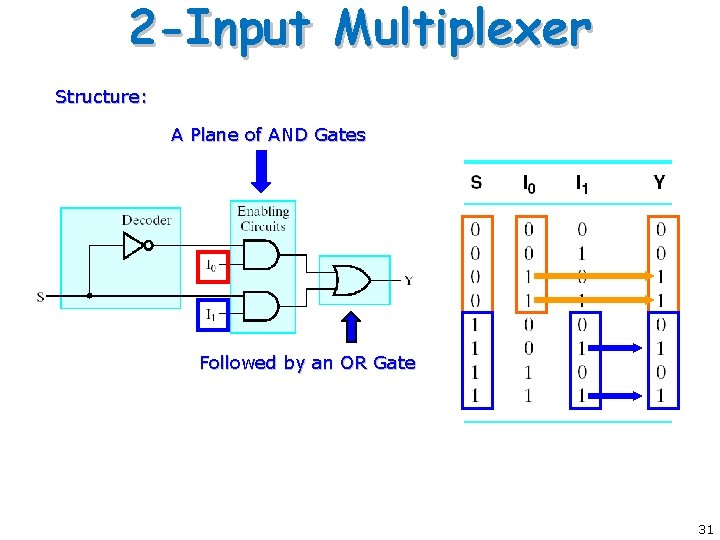

2 -Input Multiplexer Structure: A Plane of AND Gates Followed by an OR Gate 31

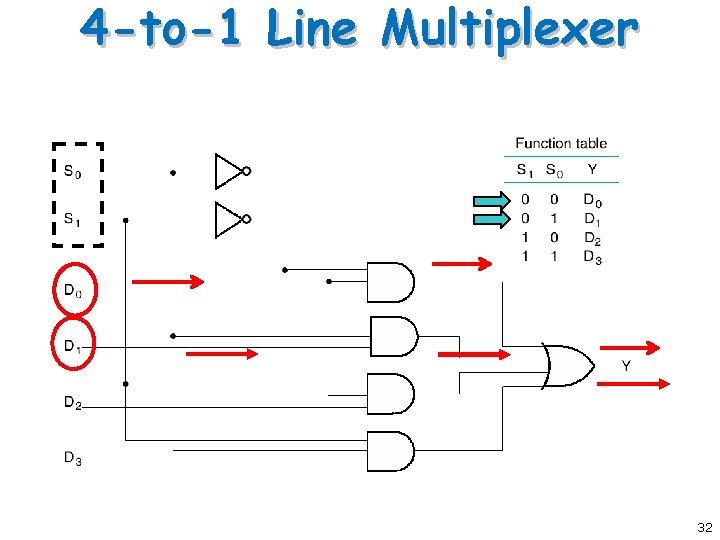

4 -to-1 Line Multiplexer 32

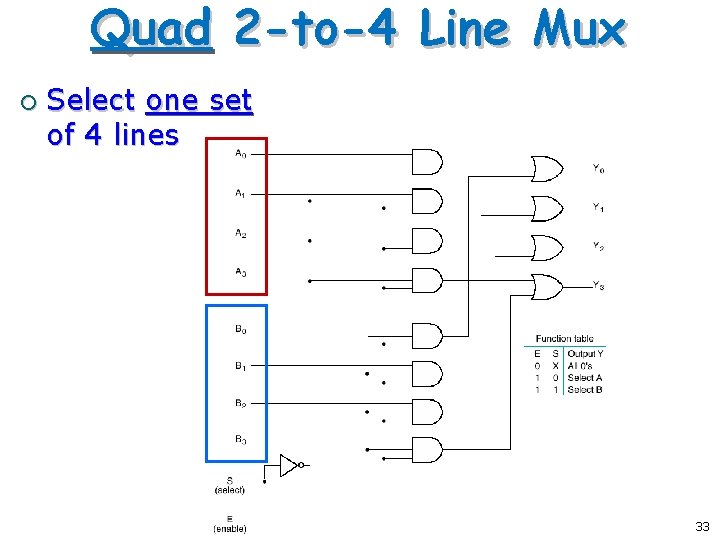

Quad 2 -to-4 Line Mux ¡ Select one set of 4 lines 33

Multiplexors: Logic Implementation

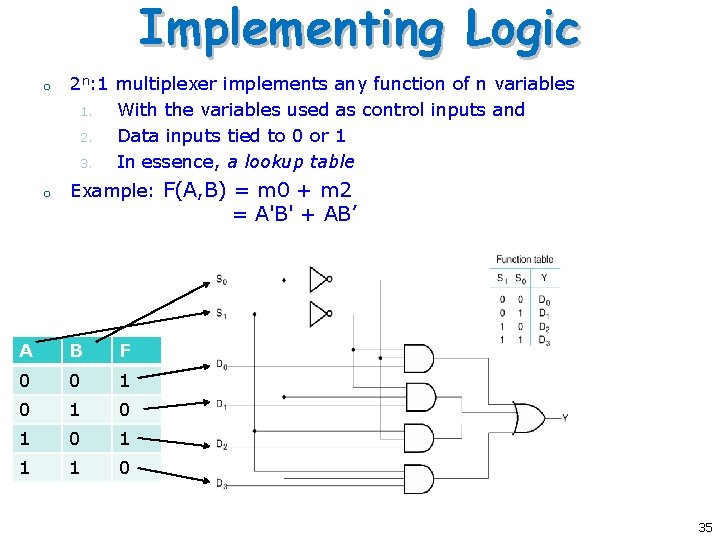

Implementing Logic o o 2 n: 1 multiplexer implements any function of n variables 1. With the variables used as control inputs and 2. Data inputs tied to 0 or 1 3. In essence, a lookup table Example: F(A, B) = m 0 + m 2 = A'B' + AB’ A B F 0 0 1 0 1 1 1 0 35

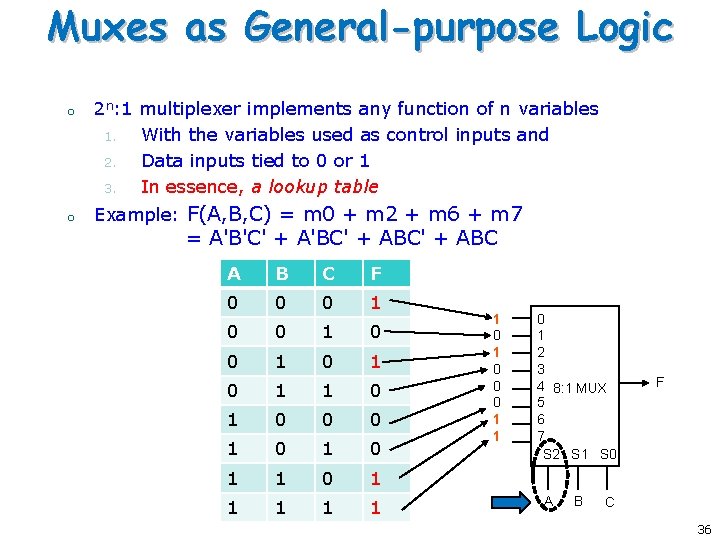

Muxes as General-purpose Logic o o 2 n: 1 multiplexer implements any function of n variables 1. With the variables used as control inputs and 2. Data inputs tied to 0 or 1 3. In essence, a lookup table Example: F(A, B, C) = m 0 + m 2 + m 6 + m 7 = A'B'C' + A'BC' + ABC A B C F 0 0 0 1 0 1 1 0 0 0 1 0 1 1 1 1 0 1 0 0 0 1 1 0 1 2 3 4 8: 1 MUX 5 6 7 S 2 S 1 S 0 A B F C 36

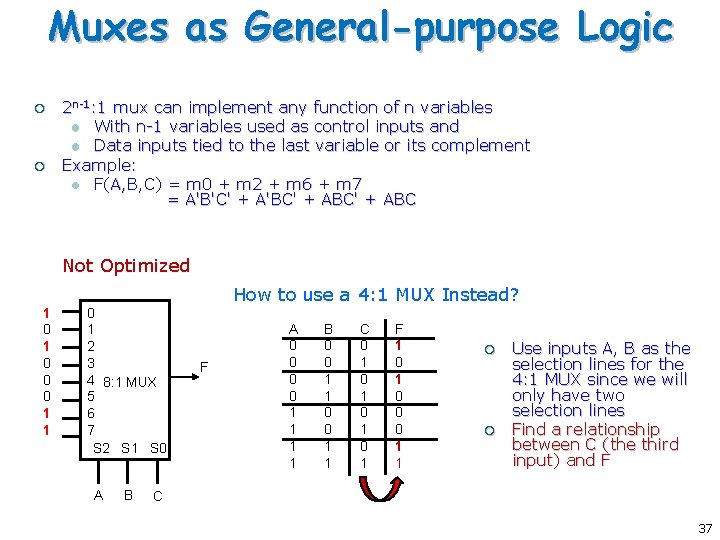

Muxes as General-purpose Logic ¡ ¡ 2 n-1: 1 mux can implement any function of n variables l With n-1 variables used as control inputs and l Data inputs tied to the last variable or its complement Example: l F(A, B, C) = m 0 + m 2 + m 6 + m 7 = A'B'C' + A'BC' + ABC Not Optimized How to use a 4: 1 MUX Instead? 1 0 0 0 1 1 0 1 2 3 4 8: 1 MUX 5 6 7 S 2 S 1 S 0 A B F A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 F 1 0 0 0 1 1 ¡ ¡ Use inputs A, B as the selection lines for the 4: 1 MUX since we will only have two selection lines Find a relationship between C (the third input) and F C 37

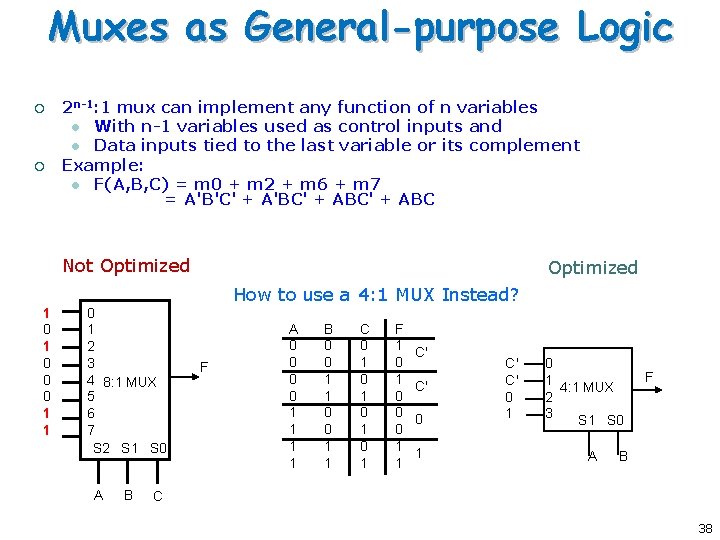

Muxes as General-purpose Logic ¡ ¡ 2 n-1: 1 mux can implement any function of n variables l With n-1 variables used as control inputs and l Data inputs tied to the last variable or its complement Example: l F(A, B, C) = m 0 + m 2 + m 6 + m 7 = A'B'C' + A'BC' + ABC Not Optimized How to use a 4: 1 MUX Instead? 1 0 0 0 1 1 0 1 2 3 4 8: 1 MUX 5 6 7 S 2 S 1 S 0 A B F A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 F 1 0 0 0 1 1 C' C' 0 1 0 1 4: 1 MUX 2 3 S 1 S 0 A F B C 38

Demultiplexors

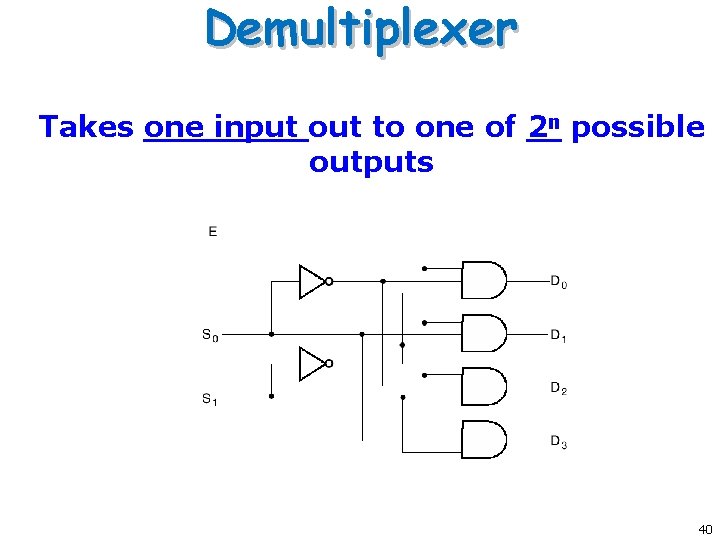

Demultiplexer Takes one input out to one of 2 n possible outputs 40

VHDL Implementations

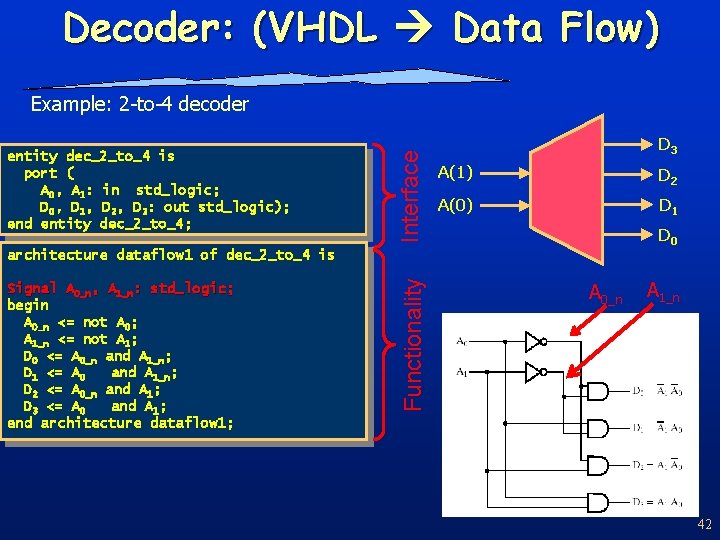

Decoder: (VHDL Data Flow) entity dec_2_to_4 is port ( A 0, A 1: in std_logic; D 0, D 1, D 2, D 3: out std_logic); end entity dec_2_to_4; Interface Example: 2 -to-4 decoder D 3 A(1) D 2 A(0) D 1 D 0 Signal A 0_n, A 1_n: std_logic; begin A 0_n <= not A 0; A 1_n <= not A 1; D 0 <= A 0_n and A 1_n; D 1 <= A 0 and A 1_n; D 2 <= A 0_n and A 1; D 3 <= A 0 and A 1; end architecture dataflow 1; Functionality architecture dataflow 1 of dec_2_to_4 is A 0_n A 1_n 42

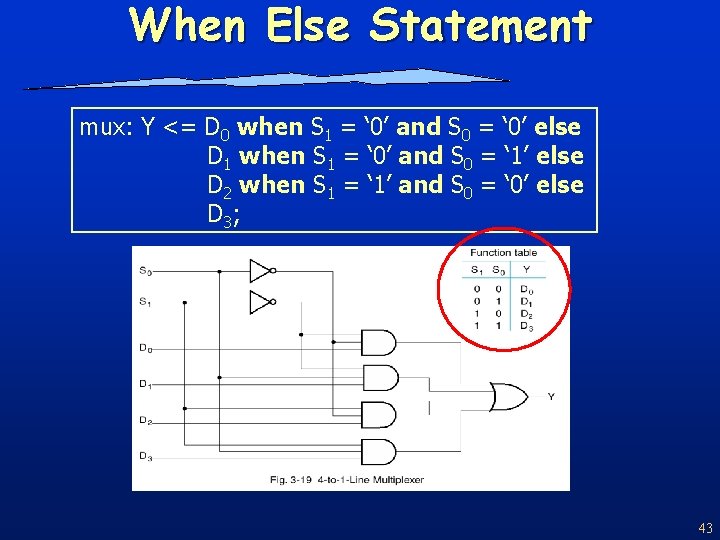

When Else Statement mux: Y <= D 0 when S 1 = ‘ 0’ and S 0 = ‘ 0’ else D 1 when S 1 = ‘ 0’ and S 0 = ‘ 1’ else D 2 when S 1 = ‘ 1’ and S 0 = ‘ 0’ else D 3; 43

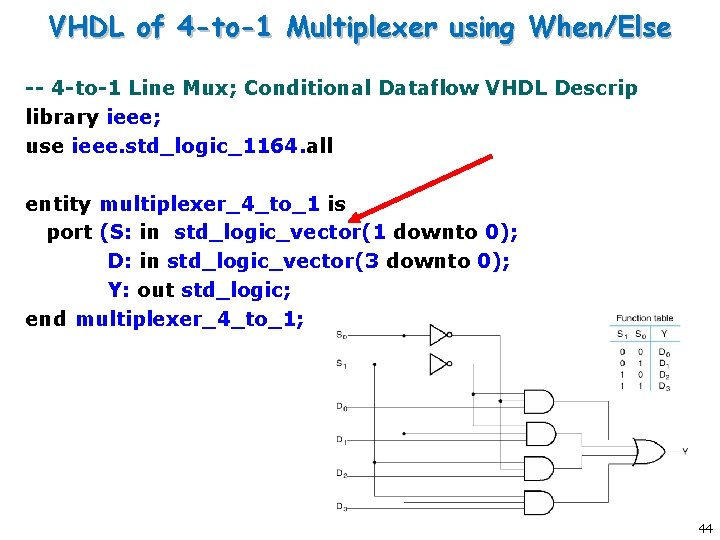

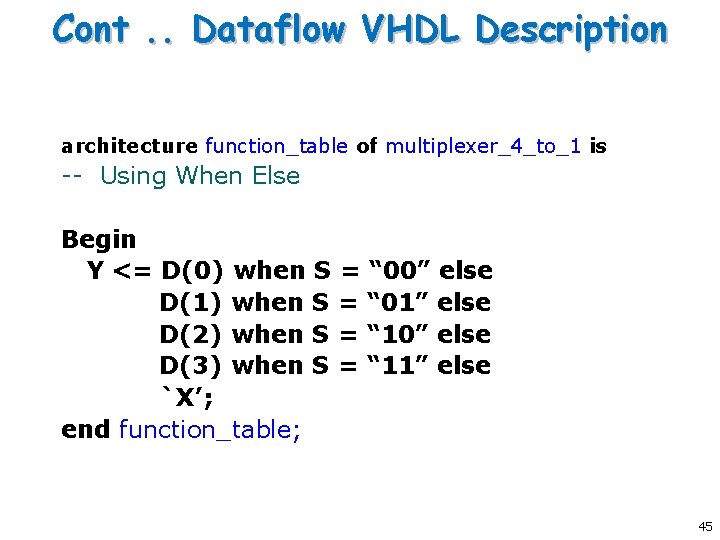

VHDL of 4 -to-1 Multiplexer using When/Else -- 4 -to-1 Line Mux; Conditional Dataflow VHDL Descrip library ieee; use ieee. std_logic_1164. all entity multiplexer_4_to_1 is port (S: in std_logic_vector(1 downto 0); D: in std_logic_vector(3 downto 0); Y: out std_logic; end multiplexer_4_to_1; 44

Cont. . Dataflow VHDL Description architecture function_table of multiplexer_4_to_1 is -- Using When Else Begin Y <= D(0) when S = “ 00” else D(1) when S = “ 01” else D(2) when S = “ 10” else D(3) when S = “ 11” else `X’; end function_table; 45

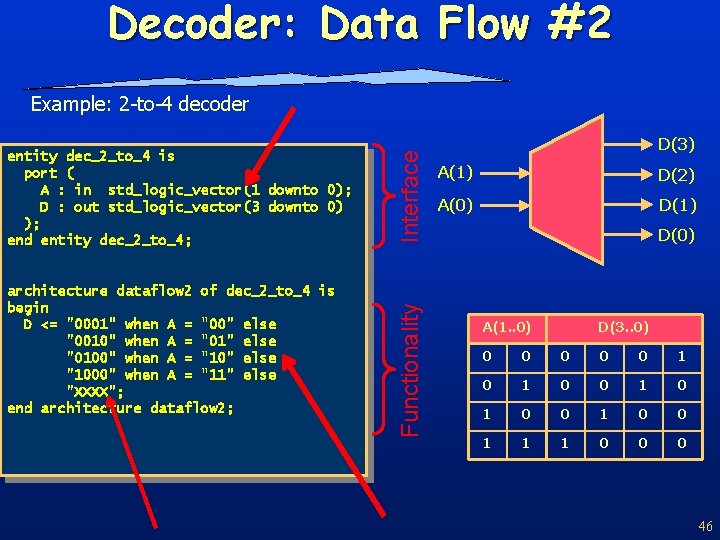

Decoder: Data Flow #2 architecture dataflow 2 of dec_2_to_4 is begin D <= "0001" when A = "00" else "0010" when A = "01" else "0100" when A = "10" else "1000" when A = "11" else "XXXX"; end architecture dataflow 2; Functionality entity dec_2_to_4 is port ( A : in std_logic_vector(1 downto 0); D : out std_logic_vector(3 downto 0) ); end entity dec_2_to_4; Interface Example: 2 -to-4 decoder D(3) A(1) D(2) A(0) D(1) D(0) A(1. . 0) D(3. . 0) 0 0 0 1 0 1 0 0 1 1 1 0 0 0 46

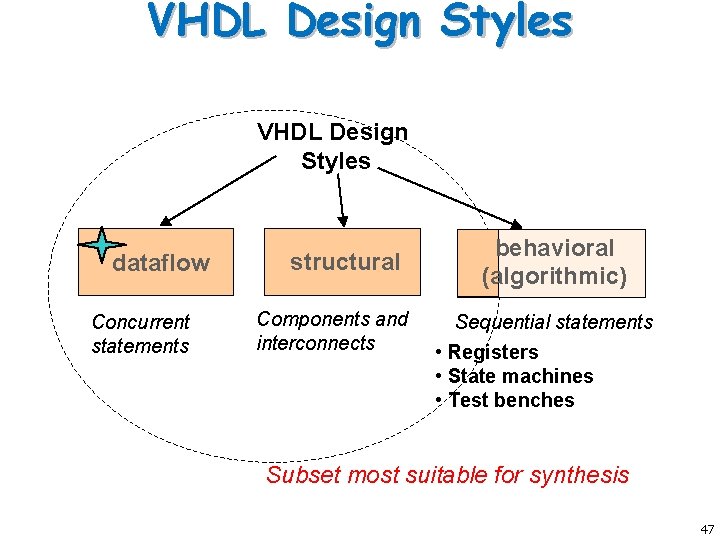

VHDL Design Styles dataflow Concurrent statements structural Components and interconnects behavioral (algorithmic) Sequential statements • Registers • State machines • Test benches Subset most suitable for synthesis 47

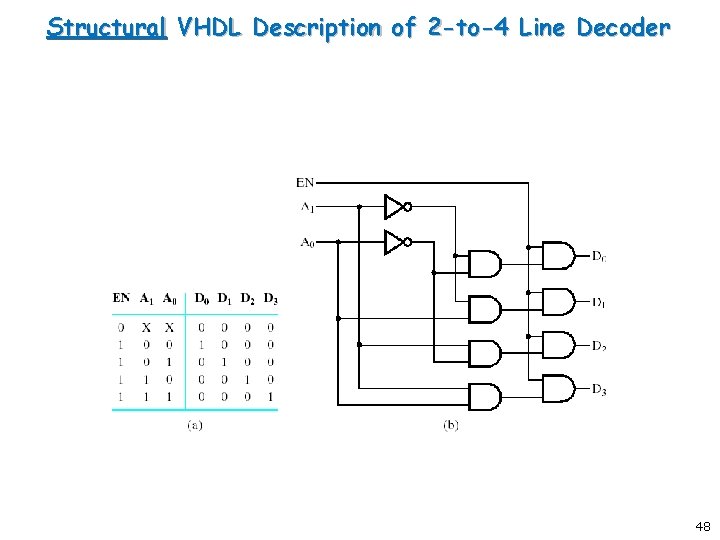

Structural VHDL Description of 2 -to-4 Line Decoder 48

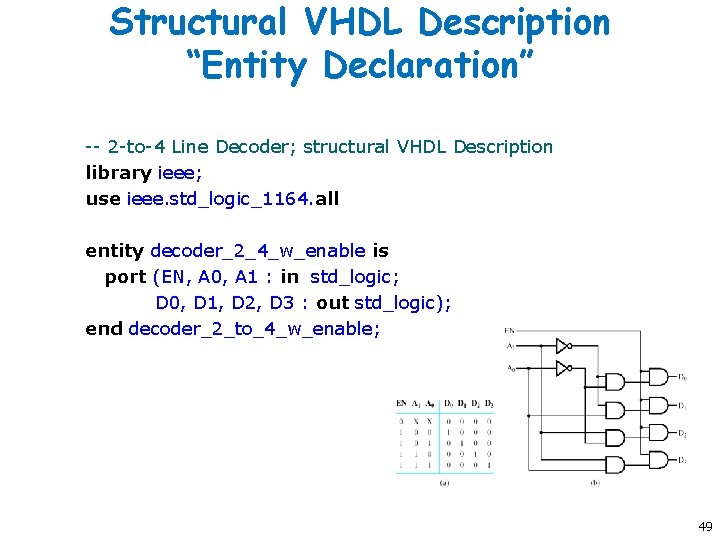

Structural VHDL Description “Entity Declaration” -- 2 -to-4 Line Decoder; structural VHDL Description library ieee; use ieee. std_logic_1164. all entity decoder_2_4_w_enable is port (EN, A 0, A 1 : in std_logic; D 0, D 1, D 2, D 3 : out std_logic); end decoder_2_to_4_w_enable; 49

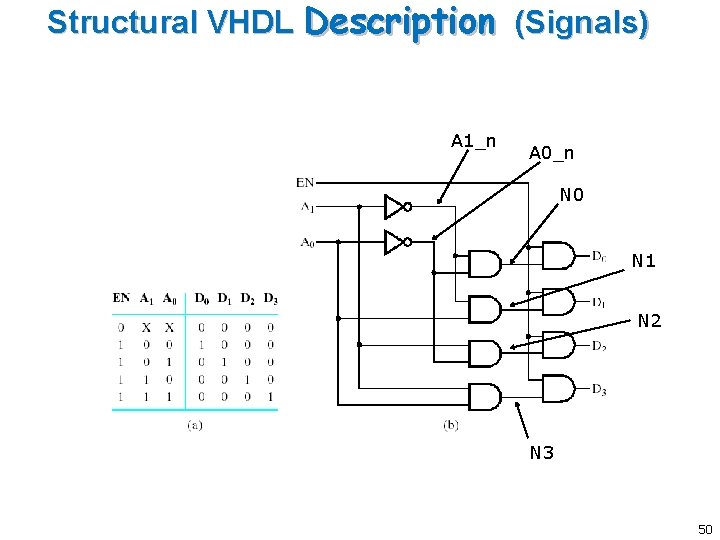

Structural VHDL Description (Signals) A 1_n A 0_n N 0 N 1 N 2 N 3 50

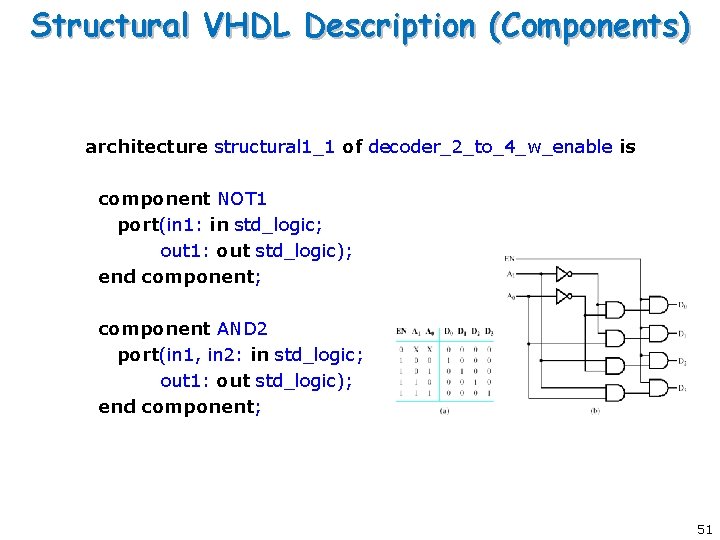

Structural VHDL Description (Components) architecture structural 1_1 of decoder_2_to_4_w_enable is component NOT 1 port(in 1: in std_logic; out 1: out std_logic); end component; component AND 2 port(in 1, in 2: in std_logic; out 1: out std_logic); end component; 51

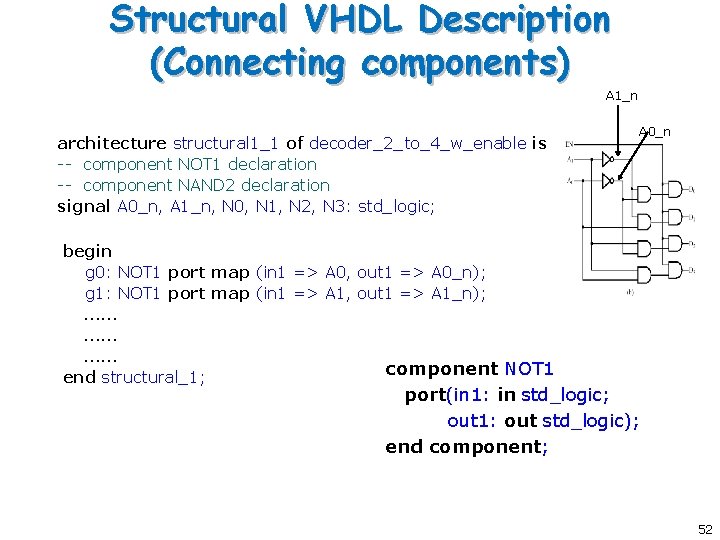

Structural VHDL Description (Connecting components) A 1_n architecture structural 1_1 of decoder_2_to_4_w_enable is -- component NOT 1 declaration -- component NAND 2 declaration signal A 0_n, A 1_n, N 0, N 1, N 2, N 3: std_logic; A 0_n begin g 0: NOT 1 port map (in 1 => A 0, out 1 => A 0_n); g 1: NOT 1 port map (in 1 => A 1, out 1 => A 1_n); …… …… …… component NOT 1 end structural_1; port(in 1: in std_logic; out 1: out std_logic); end component; 52

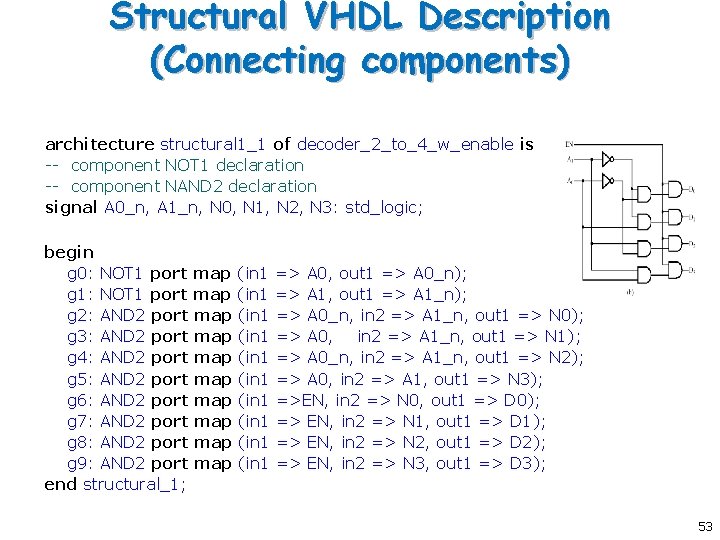

Structural VHDL Description (Connecting components) architecture structural 1_1 of decoder_2_to_4_w_enable is -- component NOT 1 declaration -- component NAND 2 declaration signal A 0_n, A 1_n, N 0, N 1, N 2, N 3: std_logic; begin g 0: NOT 1 port map g 1: NOT 1 port map g 2: AND 2 port map g 3: AND 2 port map g 4: AND 2 port map g 5: AND 2 port map g 6: AND 2 port map g 7: AND 2 port map g 8: AND 2 port map g 9: AND 2 port map end structural_1; (in 1 (in 1 (in 1 => A 0, out 1 => A 0_n); => A 1, out 1 => A 1_n); => A 0_n, in 2 => A 1_n, out 1 => N 0); => A 0, in 2 => A 1_n, out 1 => N 1); => A 0_n, in 2 => A 1_n, out 1 => N 2); => A 0, in 2 => A 1, out 1 => N 3); =>EN, in 2 => N 0, out 1 => D 0); => EN, in 2 => N 1, out 1 => D 1); => EN, in 2 => N 2, out 1 => D 2); => EN, in 2 => N 3, out 1 => D 3); 53

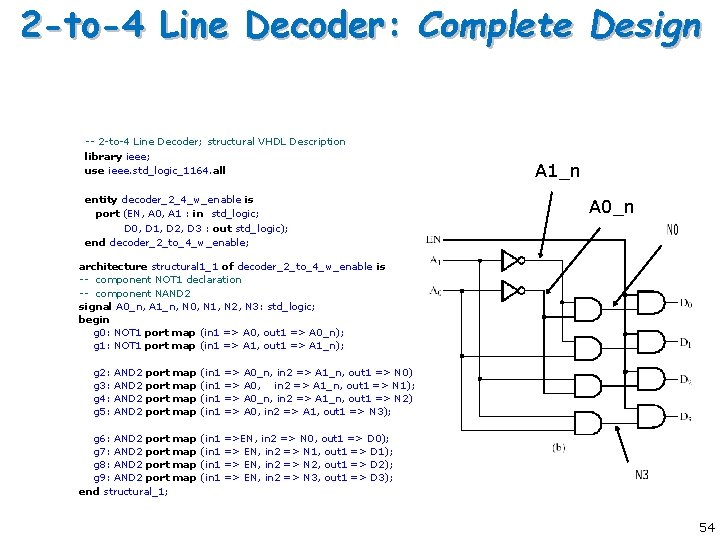

2 -to-4 Line Decoder: Complete Design -- 2 -to-4 Line Decoder; structural VHDL Description library ieee; use ieee. std_logic_1164. all entity decoder_2_4_w_enable is port (EN, A 0, A 1 : in std_logic; D 0, D 1, D 2, D 3 : out std_logic); end decoder_2_to_4_w_enable; A 1_n A 0_n architecture structural 1_1 of decoder_2_to_4_w_enable is -- component NOT 1 declaration -- component NAND 2 signal A 0_n, A 1_n, N 0, N 1, N 2, N 3: std_logic; begin g 0: NOT 1 port map (in 1 => A 0, out 1 => A 0_n); g 1: NOT 1 port map (in 1 => A 1, out 1 => A 1_n); g 2: g 3: g 4: g 5: AND 2 port map map (in 1 => => A 0_n, in 2 => A 1_n, out 1 => N 0); A 0, in 2 => A 1_n, out 1 => N 1); A 0_n, in 2 => A 1_n, out 1 => N 2); A 0, in 2 => A 1, out 1 => N 3); g 6: AND 2 port g 7: AND 2 port g 8: AND 2 port g 9: AND 2 port end structural_1; map map (in 1 =>EN, in 2 => N 0, out 1 => D 0); => EN, in 2 => N 1, out 1 => D 1); => EN, in 2 => N 2, out 1 => D 2); => EN, in 2 => N 3, out 1 => D 3); 54

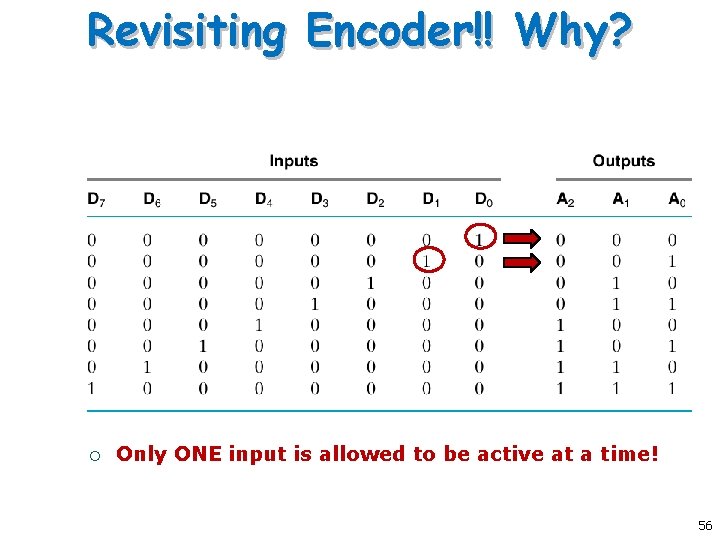

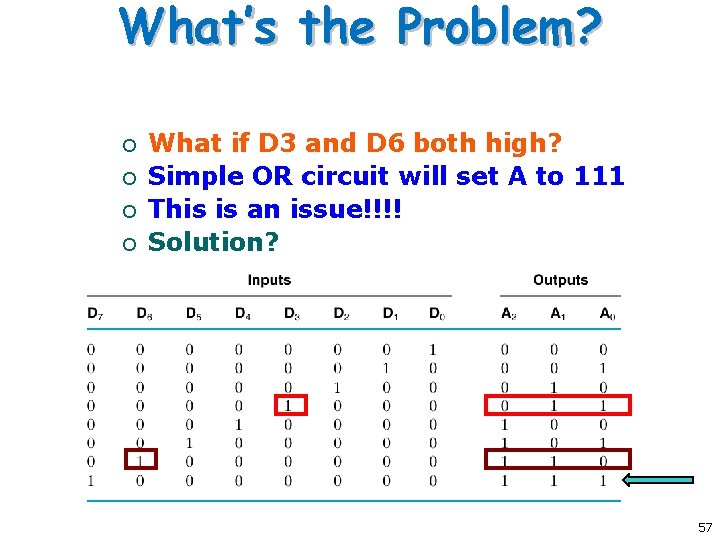

Revisiting Encoder!! Why? ¡ Only ONE input is allowed to be active at a time! 56

What’s the Problem? ¡ ¡ What if D 3 and D 6 both high? Simple OR circuit will set A to 111 This is an issue!!!! Solution? 57

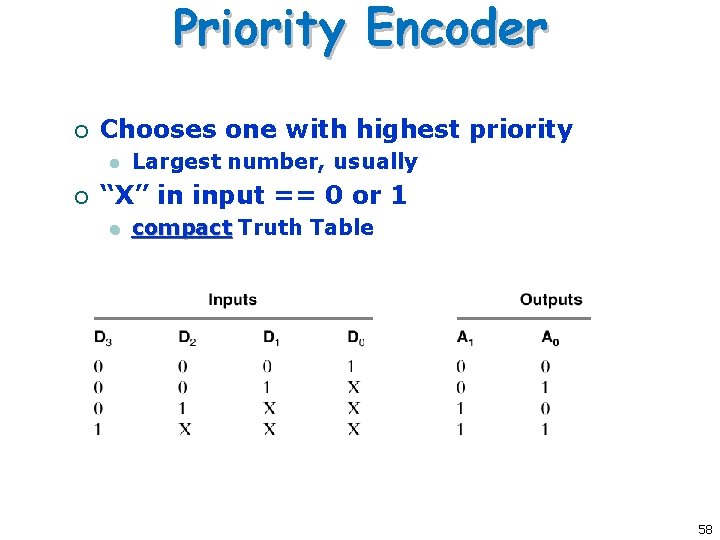

Priority Encoder ¡ Chooses one with highest priority l ¡ Largest number, usually “X” in input == 0 or 1 l compact Truth Table 58

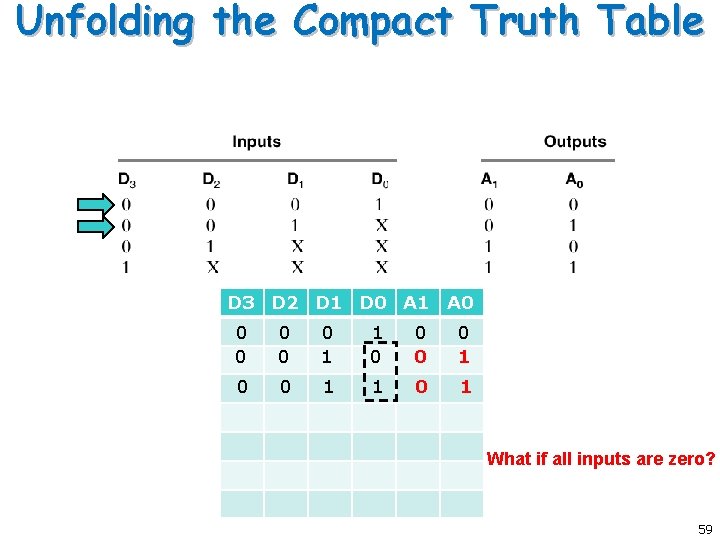

Unfolding the Compact Truth Table D 3 D 2 D 1 D 0 A 1 A 0 0 0 1 1 0 0 1 1 0 1 What if all inputs are zero? 59

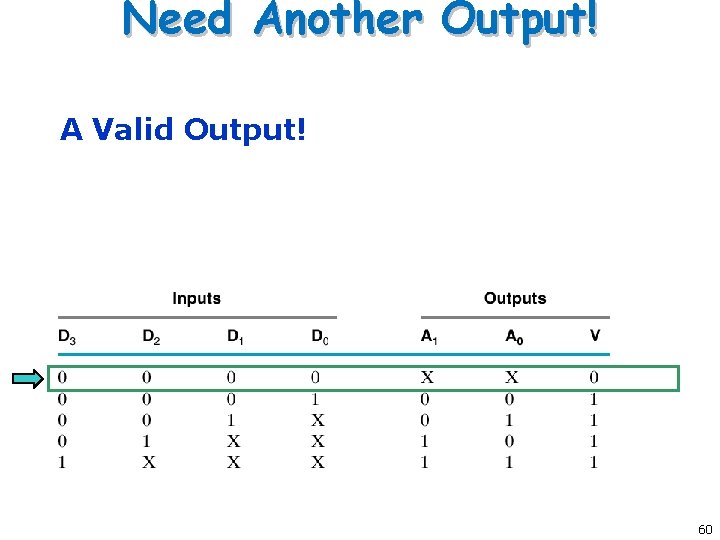

Need Another Output! A Valid Output! 60

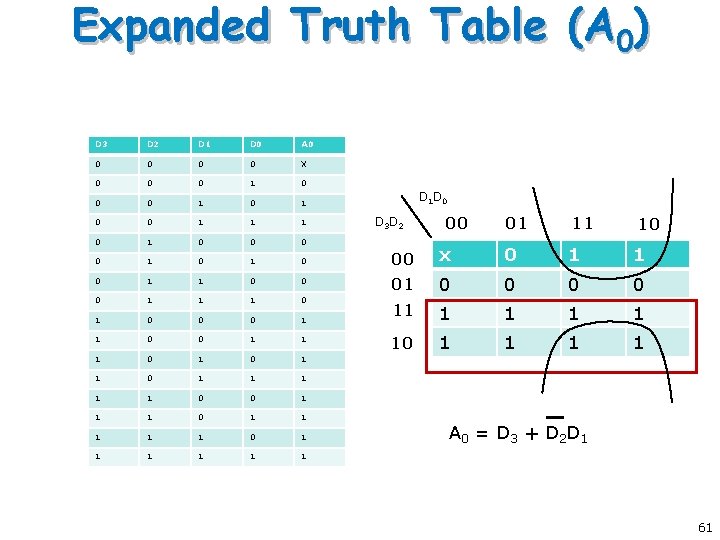

Expanded Truth Table (A 0) D 3 D 2 D 1 D 0 A 0 0 0 X 0 0 0 1 0 1 0 0 1 1 1 0 0 0 0 1 0 00 0 1 1 0 0 0 1 1 1 0 1 1 1 0 0 1 1 1 1 1 0 1 1 1 D 1 D 0 01 11 10 x 0 1 1 01 0 0 11 1 1 10 1 1 D 3 D 2 00 A 0 = D 3 + D 2 D 1 61

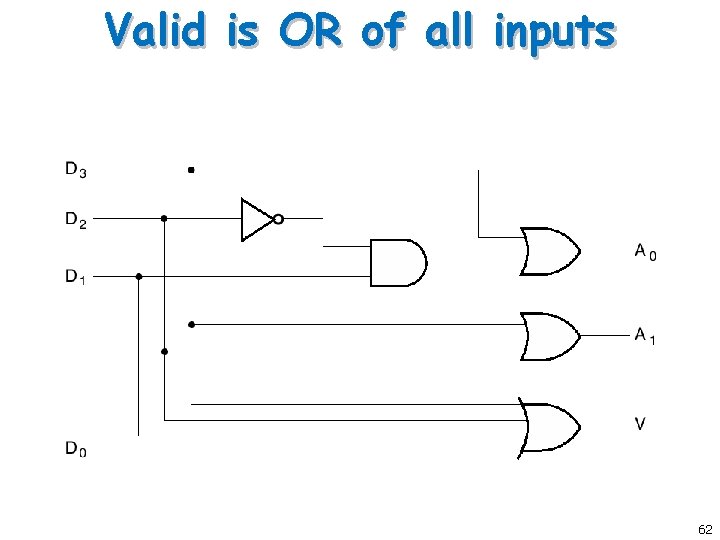

Valid is OR of all inputs 62

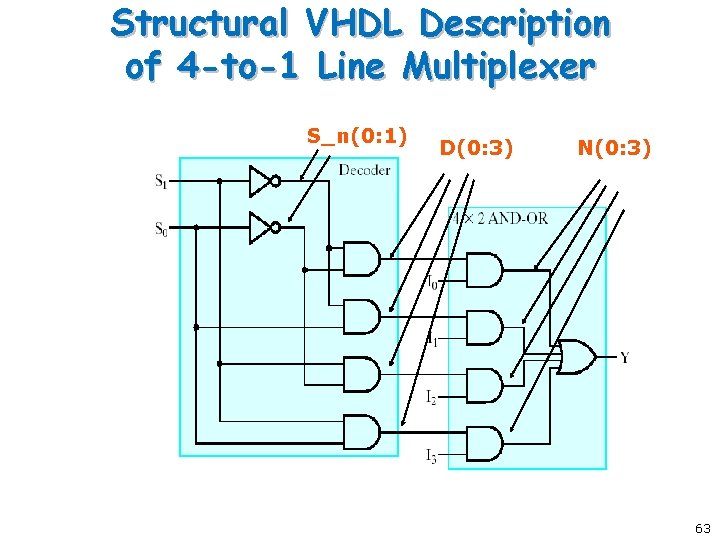

Structural VHDL Description of 4 -to-1 Line Multiplexer S_n(0: 1) D(0: 3) N(0: 3) 63

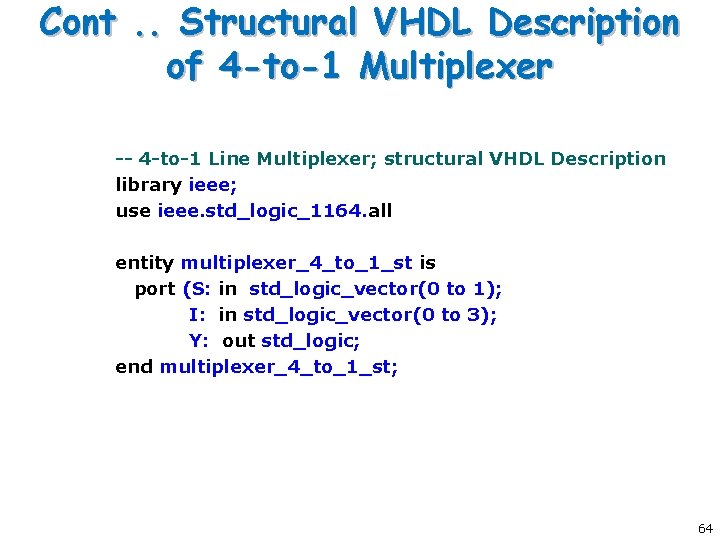

Cont. . Structural VHDL Description of 4 -to-1 Multiplexer -- 4 -to-1 Line Multiplexer; structural VHDL Description library ieee; use ieee. std_logic_1164. all entity multiplexer_4_to_1_st is port (S: in std_logic_vector(0 to 1); I: in std_logic_vector(0 to 3); Y: out std_logic; end multiplexer_4_to_1_st; 64

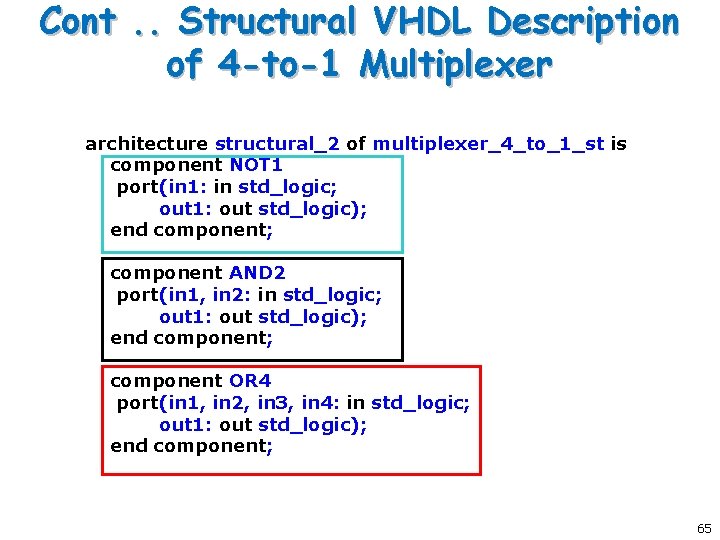

Cont. . Structural VHDL Description of 4 -to-1 Multiplexer architecture structural_2 of multiplexer_4_to_1_st is component NOT 1 port(in 1: in std_logic; out 1: out std_logic); end component; component AND 2 port(in 1, in 2: in std_logic; out 1: out std_logic); end component; component OR 4 port(in 1, in 2, in 3, in 4: in std_logic; out 1: out std_logic); end component; 65

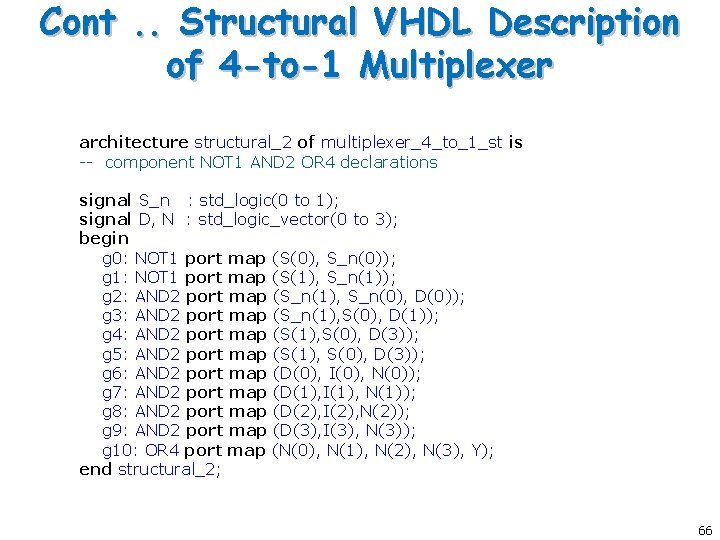

Cont. . Structural VHDL Description of 4 -to-1 Multiplexer architecture structural_2 of multiplexer_4_to_1_st is -- component NOT 1 AND 2 OR 4 declarations signal S_n : std_logic(0 to 1); signal D, N : std_logic_vector(0 to 3); begin g 0: NOT 1 port map (S(0), S_n(0)); g 1: NOT 1 port map (S(1), S_n(1)); g 2: AND 2 port map (S_n(1), S_n(0), D(0)); g 3: AND 2 port map (S_n(1), S(0), D(1)); g 4: AND 2 port map (S(1), S(0), D(3)); g 5: AND 2 port map (S(1), S(0), D(3)); g 6: AND 2 port map (D(0), I(0), N(0)); g 7: AND 2 port map (D(1), I(1), N(1)); g 8: AND 2 port map (D(2), I(2), N(2)); g 9: AND 2 port map (D(3), I(3), N(3)); g 10: OR 4 port map (N(0), N(1), N(2), N(3), Y); end structural_2; 66

- Slides: 66