TRIPENT David Yip Charles Moore Koushik Subramanian Chris

TRIPENT David Yip, Charles Moore, Koushik Subramanian, Chris Meyer, Eric Knutson

Naming Scheme Tri – Latin for three n Pent – Greek for five n There are three five bit sections for instructions, hence Tri. Pent n

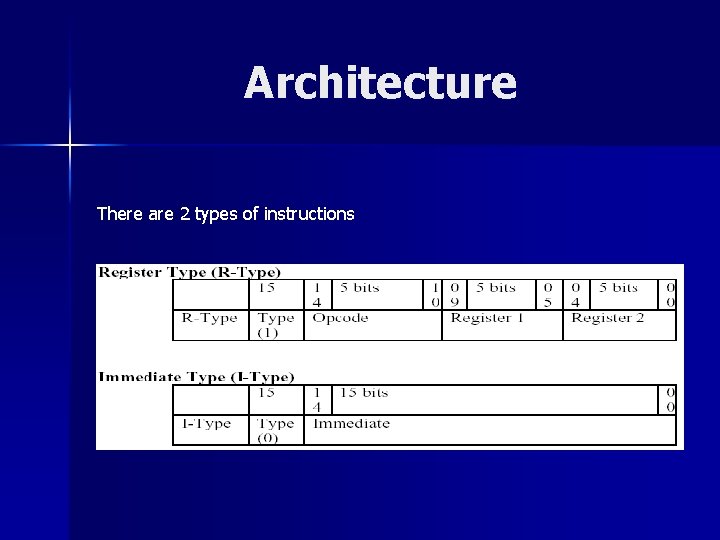

Architecture There are 2 types of instructions

I-Type n n - If the I-Type instruction holds a memory address, the least significant bit is omitted (all addresses are word-aligned, and thus the last bit will be 0). - If the I-Type instruction holds any other immediate, the most significant bit is omitted, assembler uses of the LON instruction (sets the most significant bit in $IR)

R-Type n Opcodes are only defined for R-Type instructions, as only one instruction, lir, deals directly with immediate values.

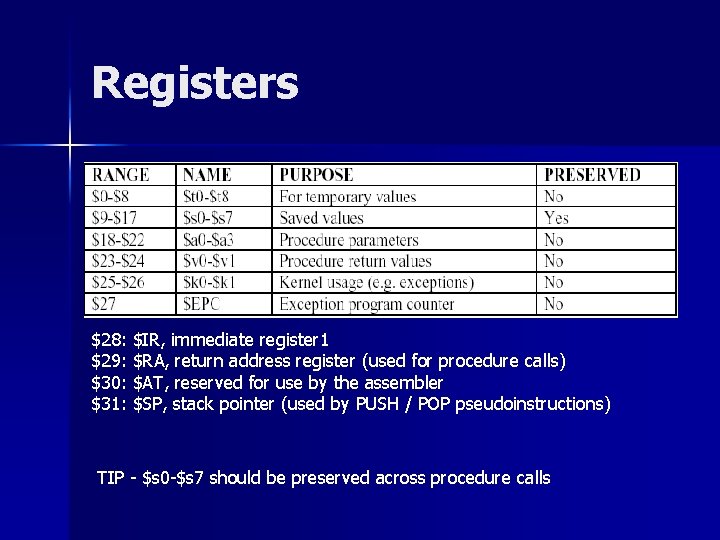

Registers $28: $29: $30: $31: $IR, immediate register 1 $RA, return address register (used for procedure calls) $AT, reserved for use by the assembler $SP, stack pointer (used by PUSH / POP pseudoinstructions) TIP - $s 0 -$s 7 should be preserved across procedure calls

I/O ports (5) 16 -bit input ports n (1) 16 -bit output port n

Interrupt Handling Vectored interrupt model with 8 interrupt service lines. n Addresses of interrupt handlers are memory-mapped at fixed locations. n Memory mapping is accomplished through use of the SW (store word) instruction. n

Arithmetic ADD – $RD, $RS R-Type n ADD – $RD, IMM Psuedo n SUB – $RD, $RS R-Type n SUB – $RD, IMM Psuedo n

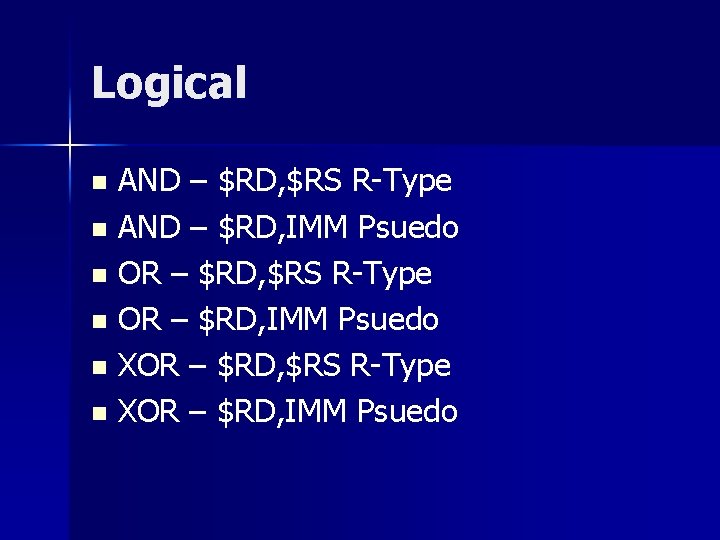

Logical AND – $RD, $RS R-Type n AND – $RD, IMM Psuedo n OR – $RD, $RS R-Type n OR – $RD, IMM Psuedo n XOR – $RD, $RS R-Type n XOR – $RD, IMM Psuedo n

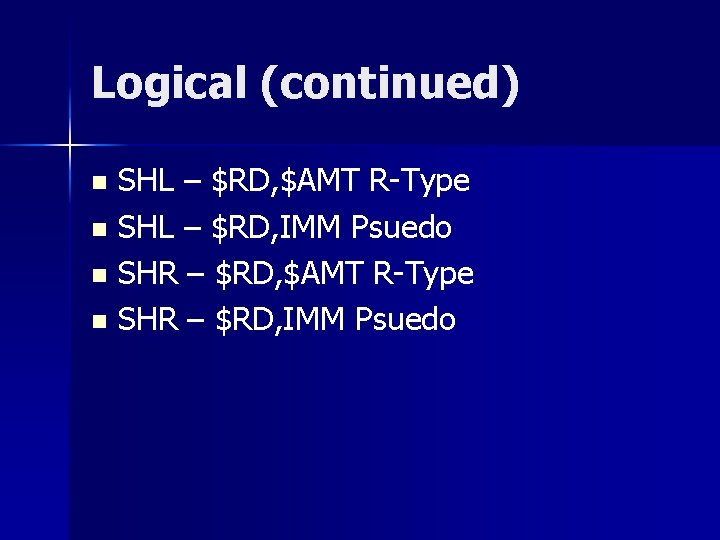

Logical (continued) SHL – $RD, $AMT R-Type n SHL – $RD, IMM Psuedo n SHR – $RD, $AMT R-Type n SHR – $RD, IMM Psuedo n

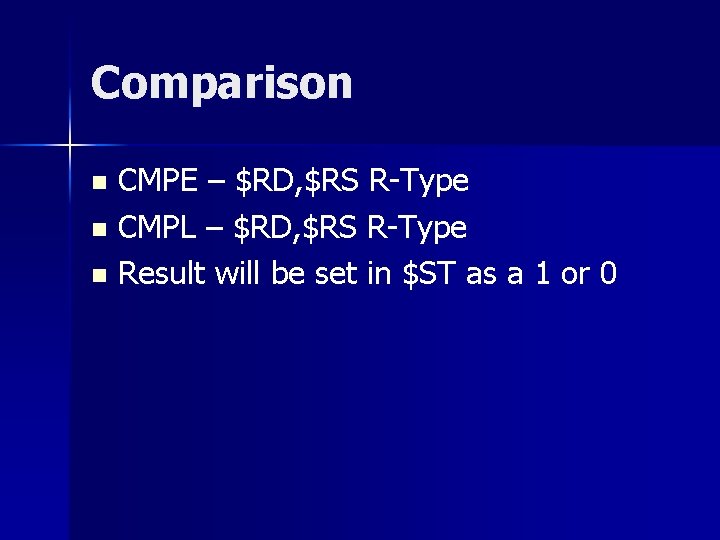

Comparison CMPE – $RD, $RS R-Type n CMPL – $RD, $RS R-Type n Result will be set in $ST as a 1 or 0 n

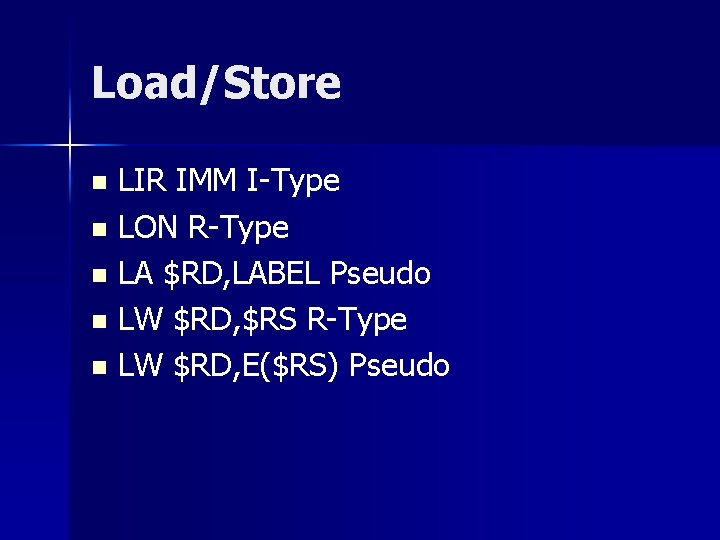

Load/Store LIR IMM I-Type n LON R-Type n LA $RD, LABEL Pseudo n LW $RD, $RS R-Type n LW $RD, E($RS) Pseudo n

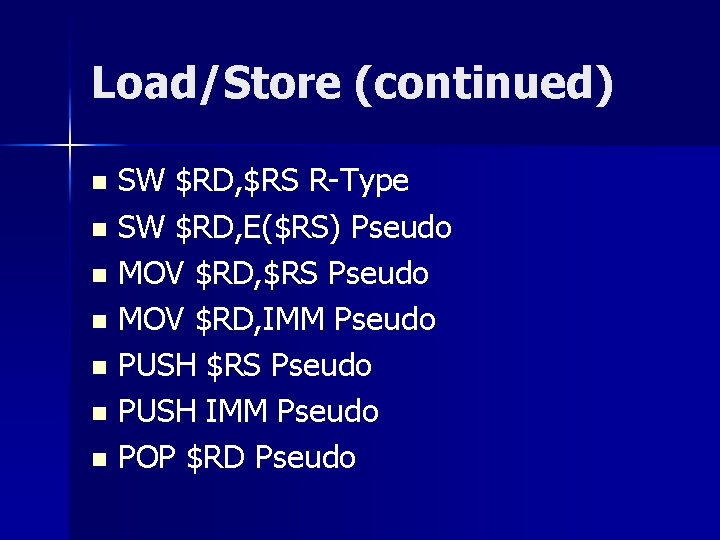

Load/Store (continued) SW $RD, $RS R-Type n SW $RD, E($RS) Pseudo n MOV $RD, $RS Pseudo n MOV $RD, IMM Pseudo n PUSH $RS Pseudo n PUSH IMM Pseudo n POP $RD Pseudo n

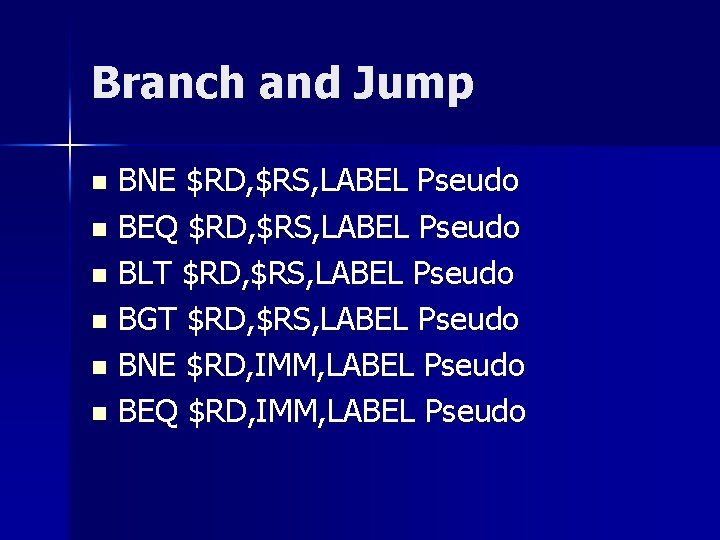

Branch and Jump BNE $RD, $RS, LABEL Pseudo n BEQ $RD, $RS, LABEL Pseudo n BLT $RD, $RS, LABEL Pseudo n BGT $RD, $RS, LABEL Pseudo n BNE $RD, IMM, LABEL Pseudo n BEQ $RD, IMM, LABEL Pseudo n

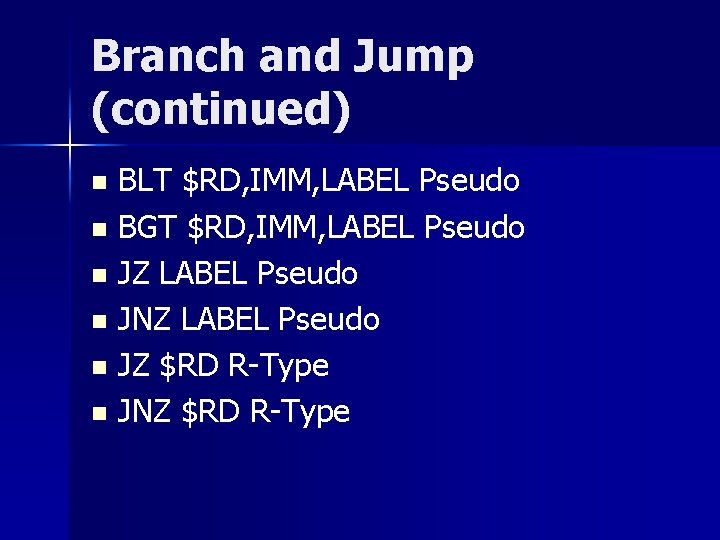

Branch and Jump (continued) BLT $RD, IMM, LABEL Pseudo n BGT $RD, IMM, LABEL Pseudo n JZ LABEL Pseudo n JNZ LABEL Pseudo n JZ $RD R-Type n JNZ $RD R-Type n

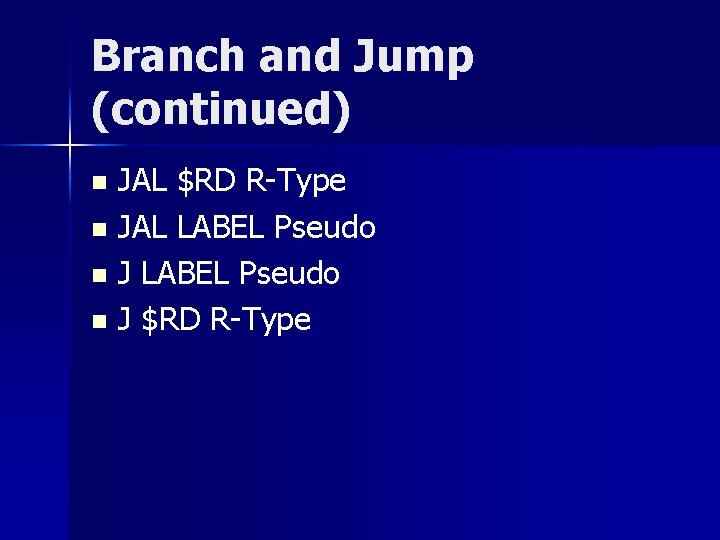

Branch and Jump (continued) JAL $RD R-Type n JAL LABEL Pseudo n J $RD R-Type n

Input/Output INP $RD, Port Pseudo n INP $RD, $RP Pseudo n OUTP PORT, $RS Pseudo n OUTP $RP, $RS Pseudo n

Statistics Gate Count – 14, 405 n Minimum period – 21. 791 ns n Max Frequency – 45. 891 mhz n Number of Cycles – 644813 (cycles to find first relative prime for 5040 including time to setup input) n

Recursive n Implemented our greatest common denominator algorithm using a recursive procedure. Thus proving that our processor can handle recursive calls.

Direct Addressing Up to 216 bits of memory can be directly addressed n Eliminates need for superfluous shifting since the entire address can be represented n

Status Register n The Status Register is a ‘scratch’ register that is holds pieces of state/status information. It contains 3 1 -bit registers: comparison result register, pending interrupt register, interrupt enable register; as well as 1 3 -bit register to hold a number (0 -7) that specifies the current interrupt line waiting to be serviced.

Barrel Shifter n Contains 32 1 -bit shifters that run in series with each shifter output going into a 32 -bit multiplexer. Output is then obtained depending on how many shifts needed.

- Slides: 23