SUPPLEMENTARY CHAPTER 2 Instruction Addressing Modes The Architecture

- Slides: 38

SUPPLEMENTARY CHAPTER 2 Instruction Addressing Modes § The Architecture of Computer Hardware and Systems Software: An Information Technology Approach § 3 rd Edition, Irv Englander § John Wiley and Sons 2003 § Linda Senne, Bentley College § Wilson Wong, Bentley College

Little Man Computer § Direct, absolute addressing § Direct: data is reached directly from the address in the instruction § Absolute: address in the instruction field is the actual memory location being addressed Supplementary Chapter 2 Instruction Addressing Modes 2

Additional Addressing Modes § Programmer-accessible registers § Provide faster execution with register-based instructions § Alternatives to absolute addressing § Allow larger range of addressable memory § While using a reasonable number of bits for the address field § Alternatives to direct addressing § Facilitate writing certain types of programs § Example: loops that use index to address different entries in a table or array Supplementary Chapter 2 Instruction Addressing Modes 3

Register Addressing § Does not require a memory access § Faster execution § Implemented directly as part of the CPU § RISC machine instruction set: made up almost entirely of register operation instructions Supplementary Chapter 2 Instruction Addressing Modes 4

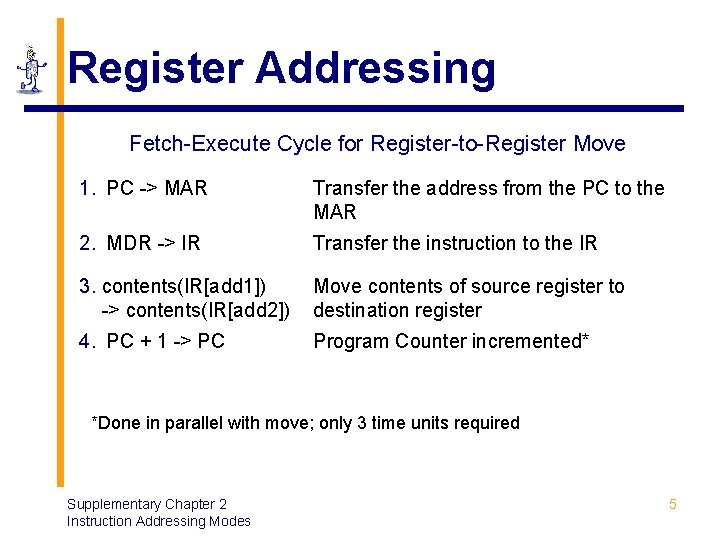

Register Addressing Fetch-Execute Cycle for Register-to-Register Move 1. PC -> MAR Transfer the address from the PC to the MAR 2. MDR -> IR Transfer the instruction to the IR 3. contents(IR[add 1]) -> contents(IR[add 2]) Move contents of source register to destination register 4. PC + 1 -> PC Program Counter incremented* *Done in parallel with move; only 3 time units required Supplementary Chapter 2 Instruction Addressing Modes 5

Additional Addressing Modes § Programmer-accessible registers § Provide faster execution with register-based instructions § Alternative to absolute addressing § Allow larger range of addressable memory § While using a reasonable number of bits for the address field § Alternative to direct addressing § Facilitate writing certain types of programs § Example: loops that use index to address different entries in a table or array Supplementary Chapter 2 Instruction Addressing Modes 6

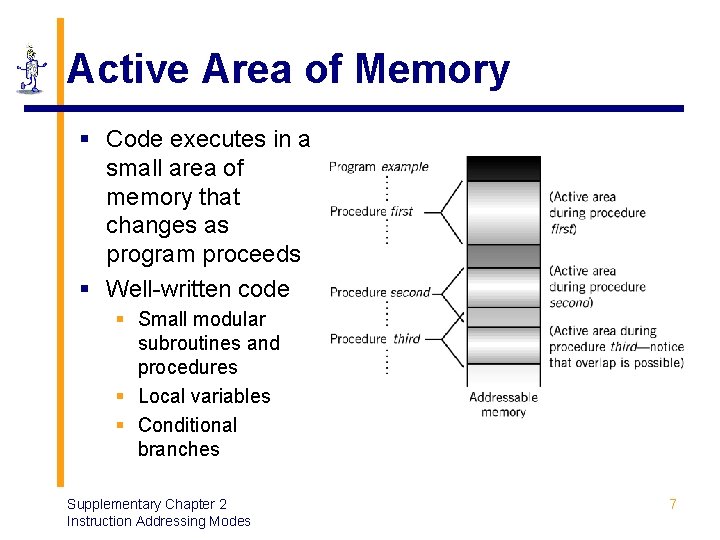

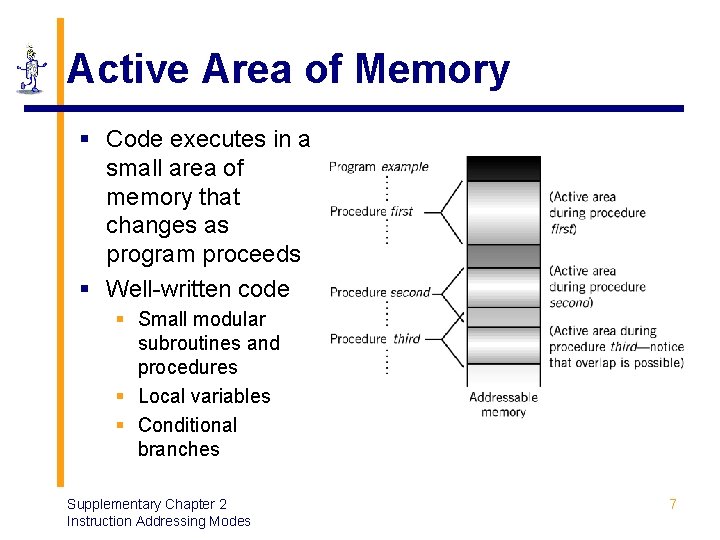

Active Area of Memory § Code executes in a small area of memory that changes as program proceeds § Well-written code Fig S 2. 2 § Small modular subroutines and procedures § Local variables § Conditional branches Supplementary Chapter 2 Instruction Addressing Modes 7

2 Alternatives to Absolute Addressing § Base register addressing § Relative addressing § Both provide starting address and an offset or displacement from the starting point Starting address in register or program counter p Offset: address in the instruction p § Programming advantage: relocatability Supplementary Chapter 2 Instruction Addressing Modes 8

Base Register Addressing § Base register set to initial address § Hardware design: special, separate register or general-purpose registers § Generally large to provide large memory space, frequently gigabytes § Final address: contents of instruction address field added to the base address Supplementary Chapter 2 Instruction Addressing Modes 9

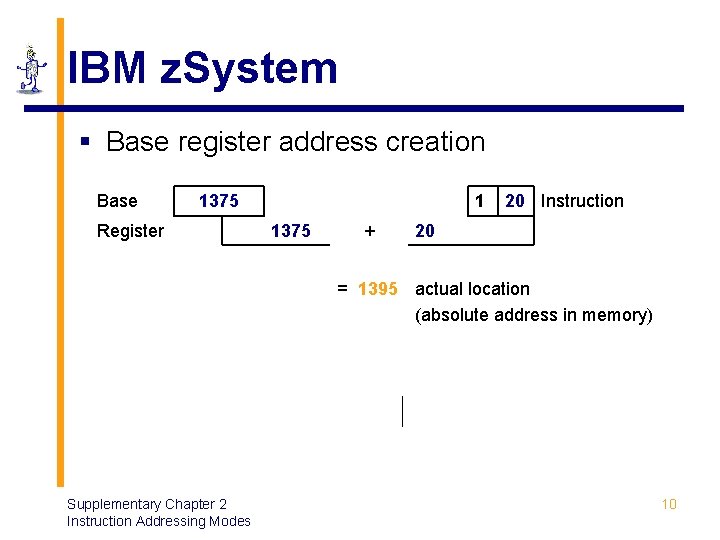

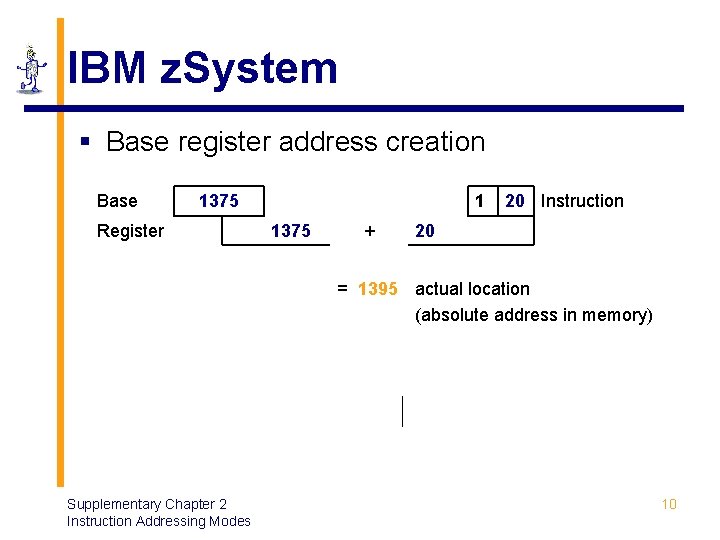

IBM z. System § Base register address creation Base 1375 Register 1 1375 + 20 Instruction 20 = 1395 actual location (absolute address in memory) Supplementary Chapter 2 Instruction Addressing Modes 10

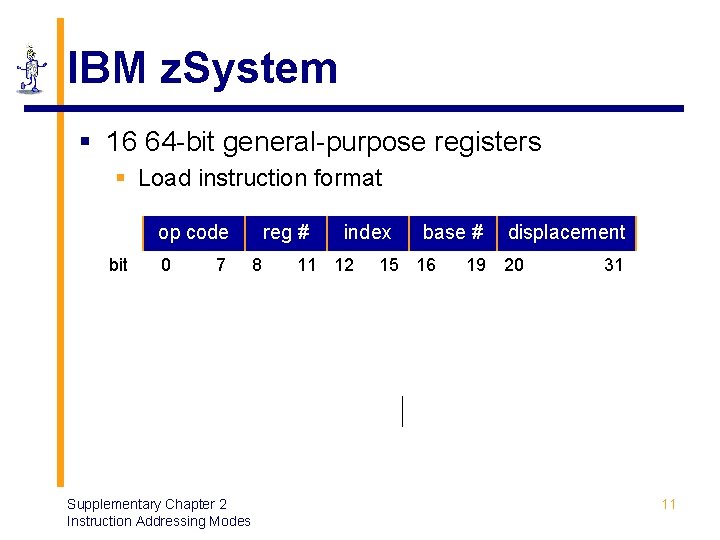

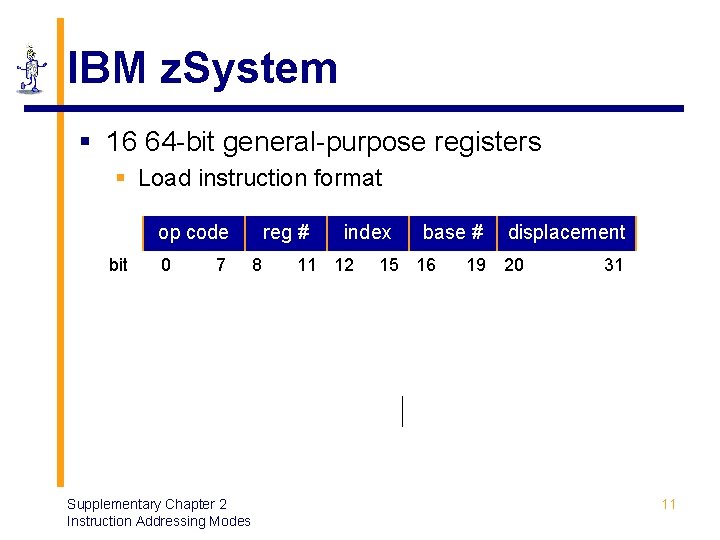

IBM z. System § 16 64 -bit general-purpose registers § Load instruction format op code bit 0 7 Supplementary Chapter 2 Instruction Addressing Modes reg # 8 index 11 12 base # 15 16 19 displacement 20 31 11

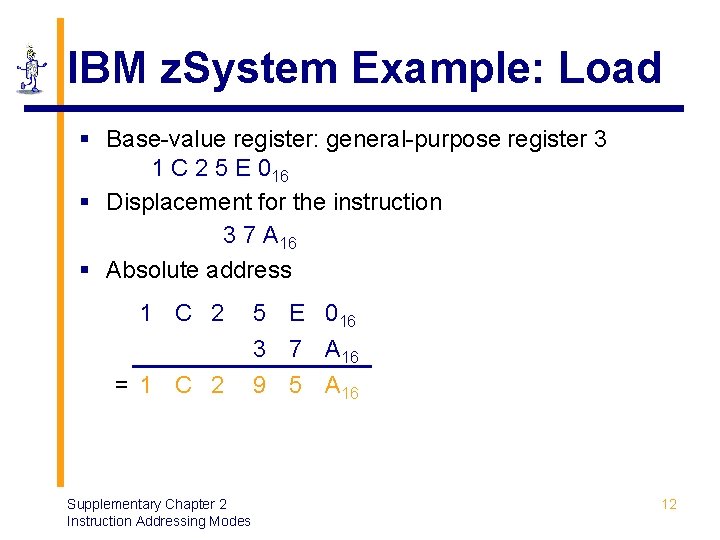

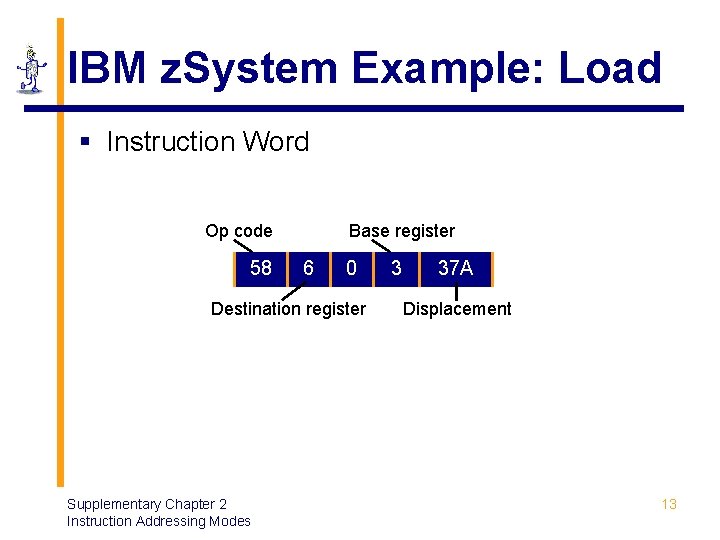

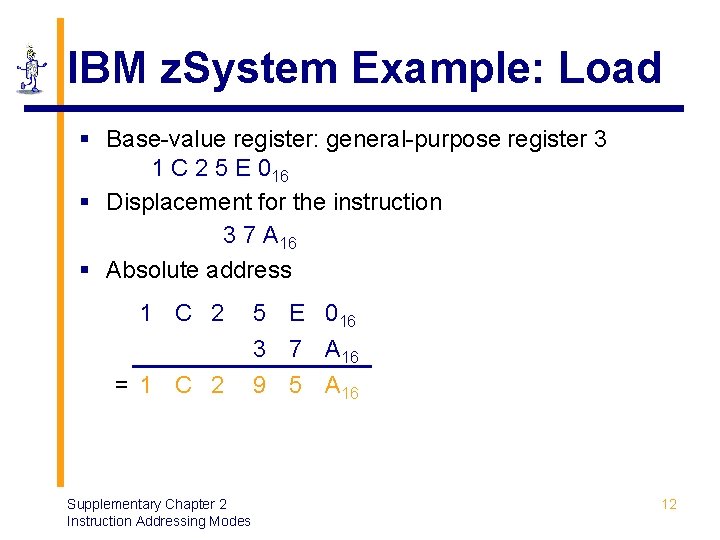

IBM z. System Example: Load § Base-value register: general-purpose register 3 1 C 2 5 E 016 § Displacement for the instruction 3 7 A 16 § Absolute address 1 C 2 5 E 016 3 7 A 16 = 1 C 2 9 5 A 16 Supplementary Chapter 2 Instruction Addressing Modes 12

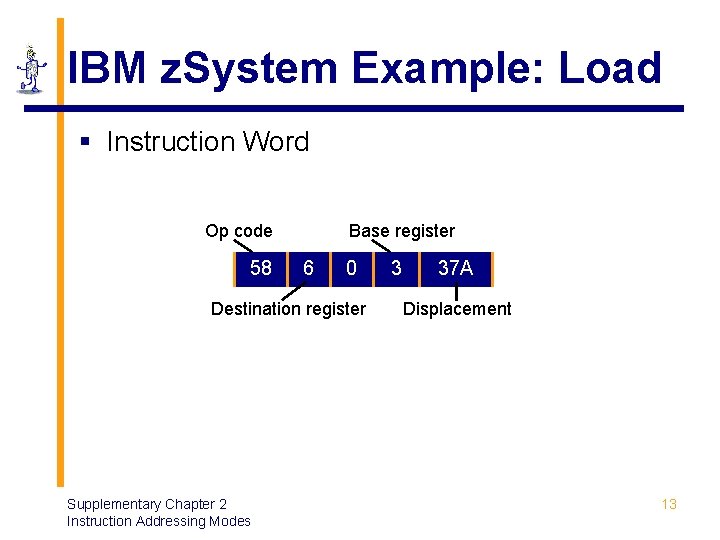

IBM z. System Example: Load § Instruction Word Op code 58 Base register 6 0 Destination register Supplementary Chapter 2 Instruction Addressing Modes 3 37 A Displacement 13

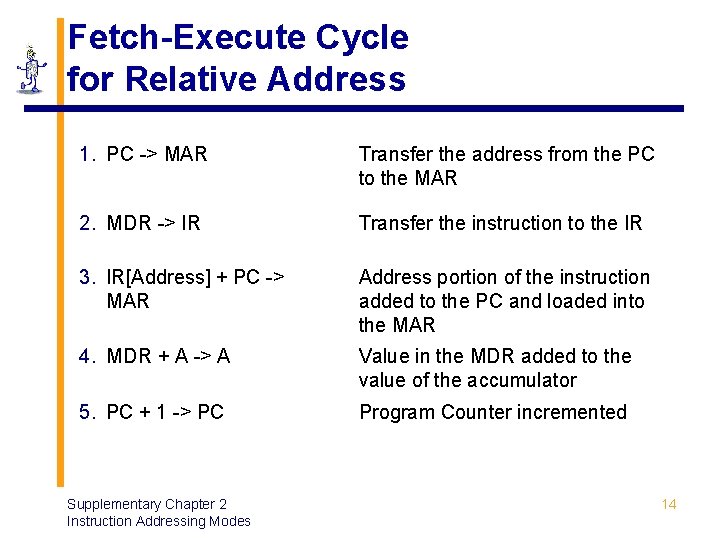

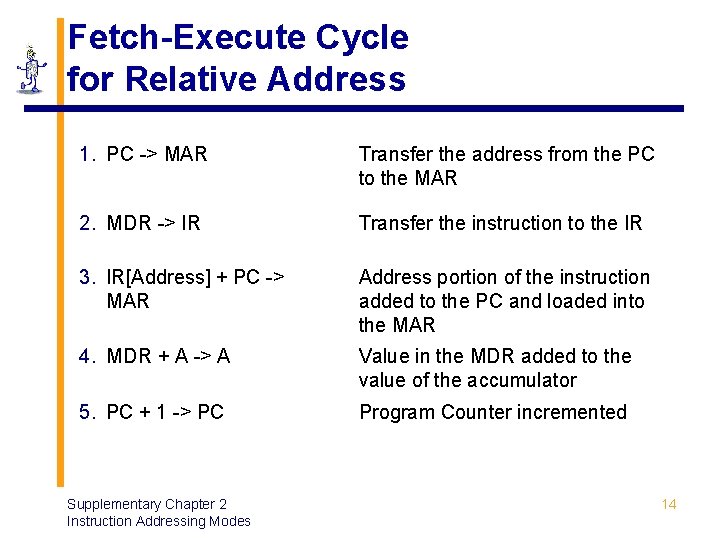

Fetch-Execute Cycle for Relative Address 1. PC -> MAR Transfer the address from the PC to the MAR 2. MDR -> IR Transfer the instruction to the IR 3. IR[Address] + PC -> MAR Address portion of the instruction added to the PC and loaded into the MAR 4. MDR + A -> A Value in the MDR added to the value of the accumulator 5. PC + 1 -> PC Program Counter incremented Supplementary Chapter 2 Instruction Addressing Modes 14

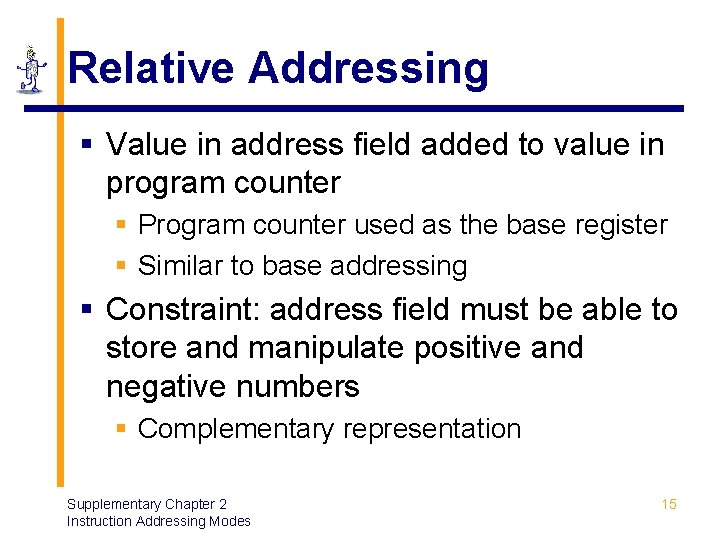

Relative Addressing § Value in address field added to value in program counter § Program counter used as the base register § Similar to base addressing § Constraint: address field must be able to store and manipulate positive and negative numbers § Complementary representation Supplementary Chapter 2 Instruction Addressing Modes 15

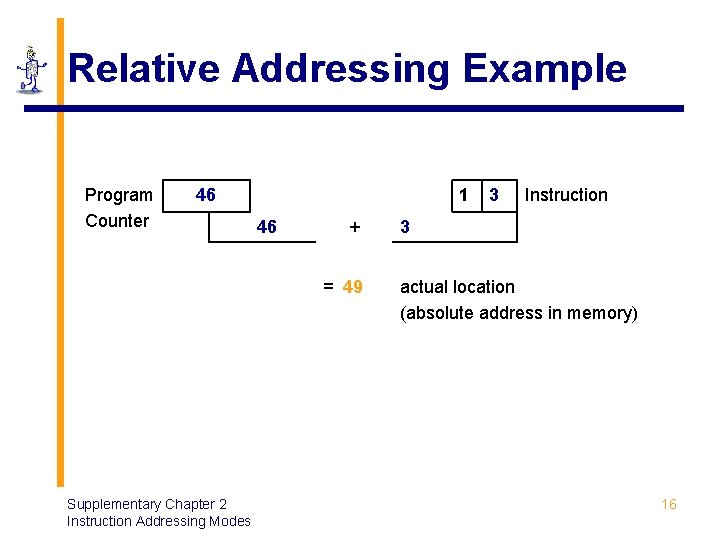

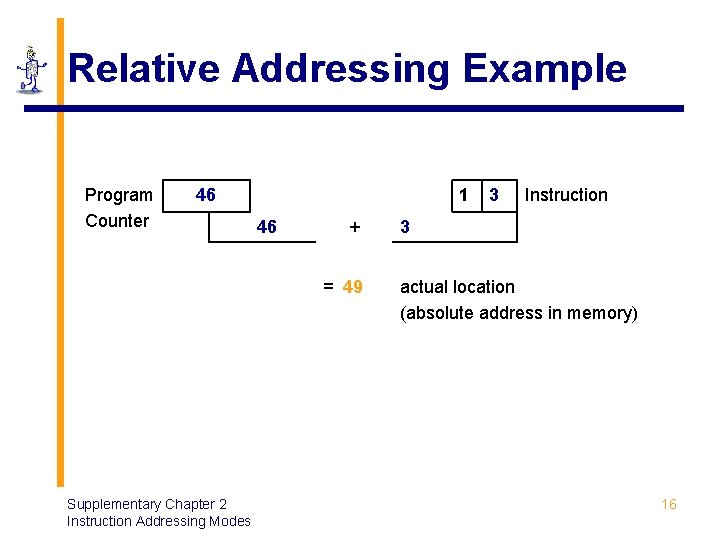

Relative Addressing Example Program Counter 46 1 46 + = 49 Supplementary Chapter 2 Instruction Addressing Modes 3 Instruction 3 actual location (absolute address in memory) 16

Direct Addressing § Separates data into location different from location of instructions § Benefits to programmer § Data can be changed without affecting the instruction itself § Data is available to different instructions Supplementary Chapter 2 Instruction Addressing Modes 17

Additional Addressing Modes § Programmer-accessible registers § Provide faster execution with register-based instructions § Alternative to absolute addressing § Allow larger range of addressable memory § While using a reasonable number of bits for the address field § Alternative to direct addressing § Facilitate writing certain types of programs § Example: loops that use index to address different entries in a table or array Supplementary Chapter 2 Instruction Addressing Modes 18

Alternatives to Direct Addressing § § Immediate addressing Indirect addressing Register Indirect addressing Indexed addressing Supplementary Chapter 2 Instruction Addressing Modes 19

Immediate Addressing § Store data with the instruction itself § Example: p Data is a constant § Constraint: Address field must be able to store and manipulate positive and negative numbers p Complementary representation p § Advantage: Additional memory access not required p Faster execution p Supplementary Chapter 2 Instruction Addressing Modes 20

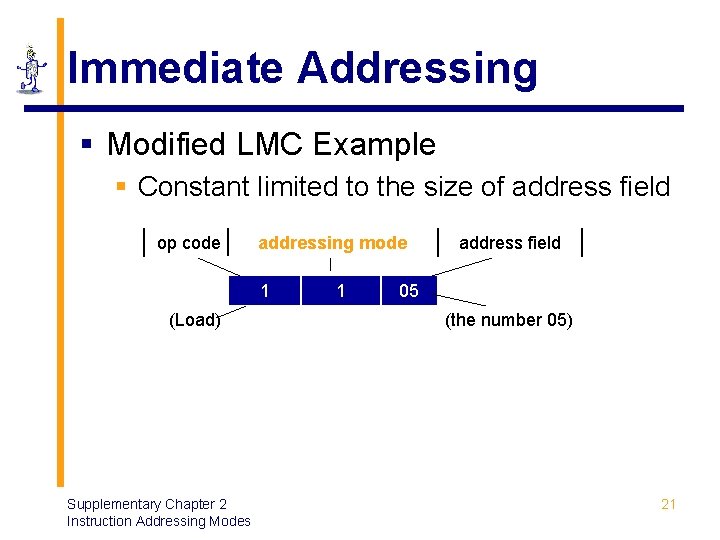

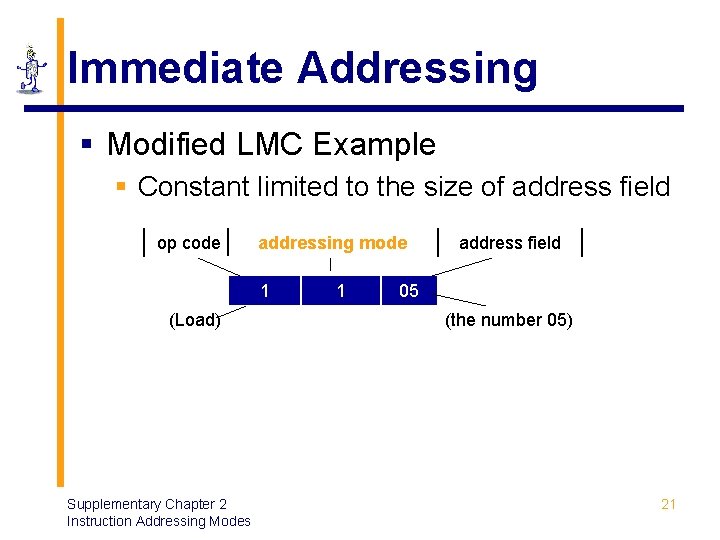

Immediate Addressing § Modified LMC Example § Constant limited to the size of address field op code addressing mode 1 (Load) Supplementary Chapter 2 Instruction Addressing Modes 1 address field 05 (the number 05) 21

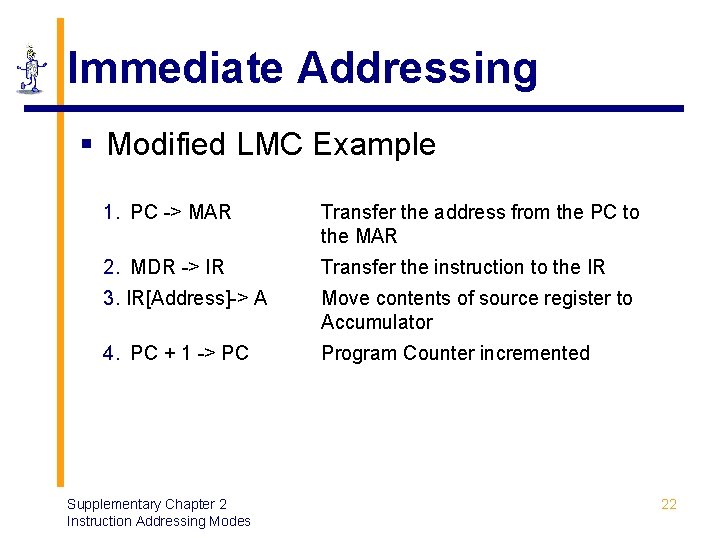

Immediate Addressing § Modified LMC Example 1. PC -> MAR Transfer the address from the PC to the MAR 2. MDR -> IR Transfer the instruction to the IR 3. IR[Address]-> A Move contents of source register to Accumulator 4. PC + 1 -> PC Program Counter incremented Supplementary Chapter 2 Instruction Addressing Modes 22

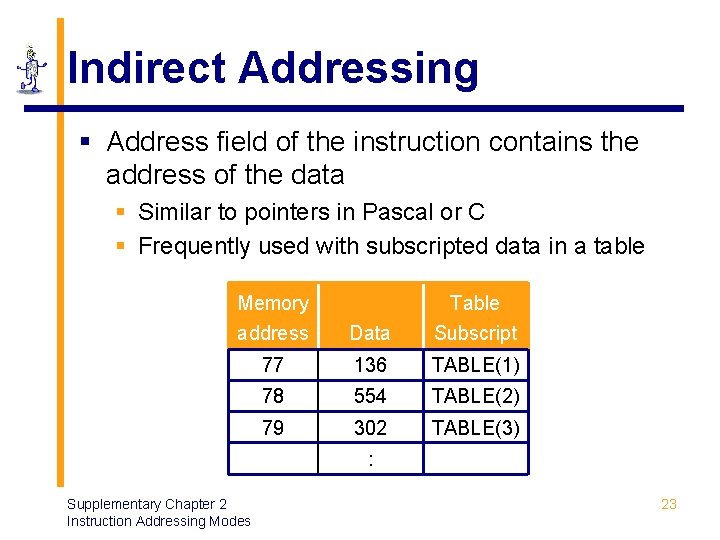

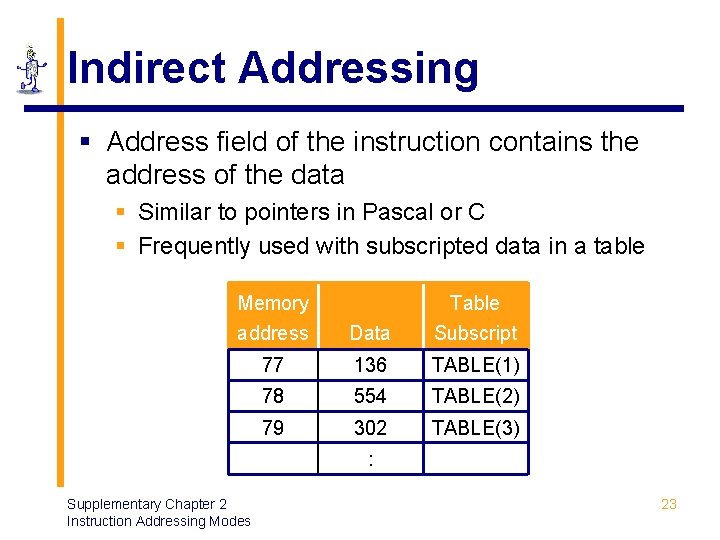

Indirect Addressing § Address field of the instruction contains the address of the data § Similar to pointers in Pascal or C § Frequently used with subscripted data in a table Memory address Data Table Subscript 77 136 TABLE(1) 78 554 TABLE(2) 79 302 TABLE(3) : Supplementary Chapter 2 Instruction Addressing Modes 23

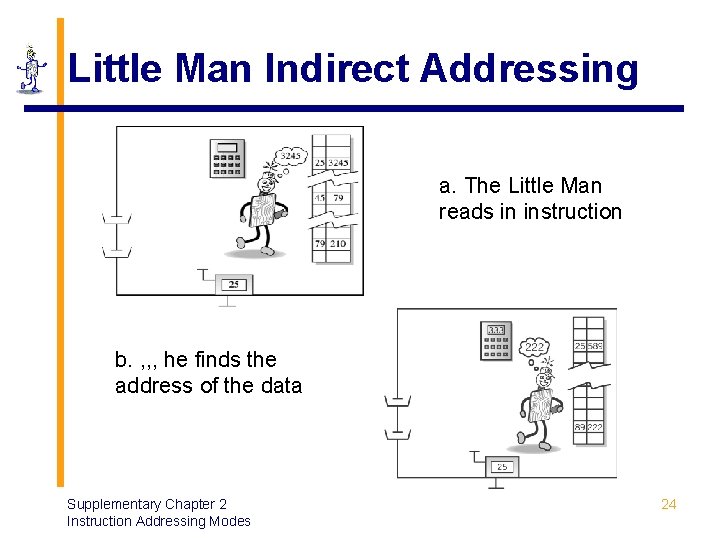

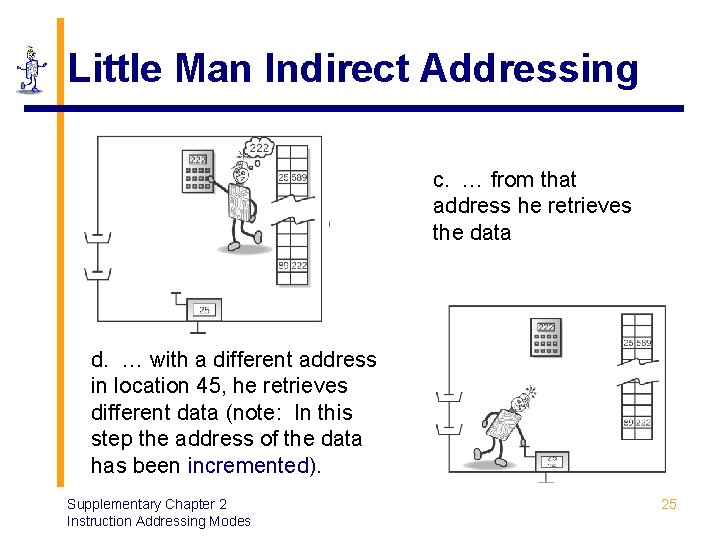

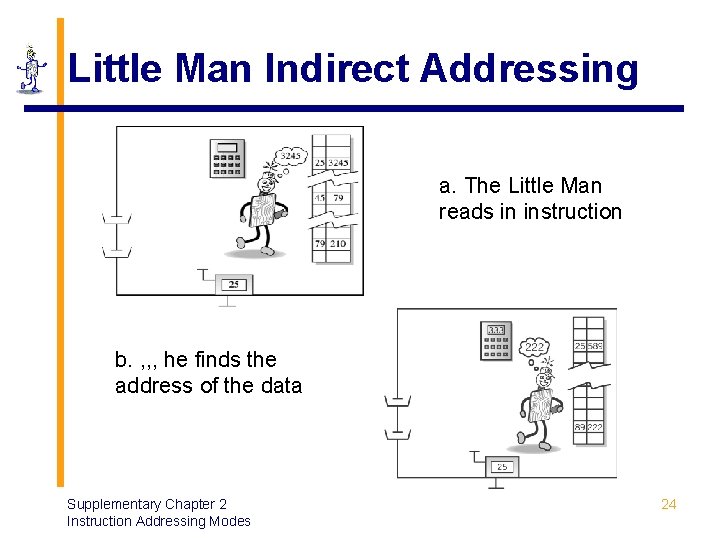

Little Man Indirect Addressing a. The Little Man reads in instruction b. , , , he finds the address of the data Supplementary Chapter 2 Instruction Addressing Modes 24

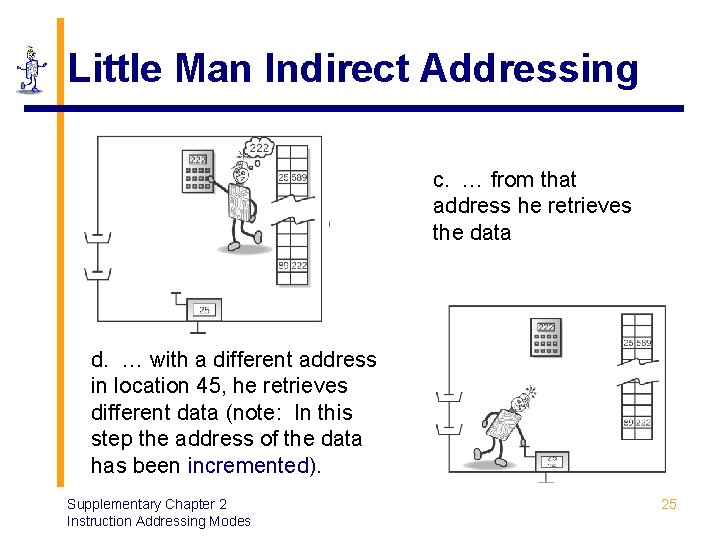

Little Man Indirect Addressing c. … from that address he retrieves the data d. … with a different address in location 45, he retrieves different data (note: In this step the address of the data has been incremented). Supplementary Chapter 2 Instruction Addressing Modes 25

Incrementing § Treat the instruction as data § Modify the address field § Pure code: does not modify itself during execution § Incrementing does not modify the instruction § Address stored in a separate data region § Advantage: program can be stored in ROM Supplementary Chapter 2 Instruction Addressing Modes 26

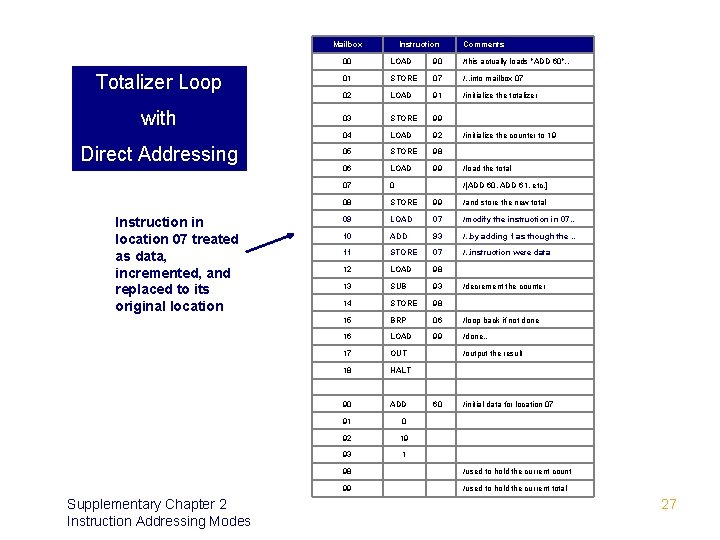

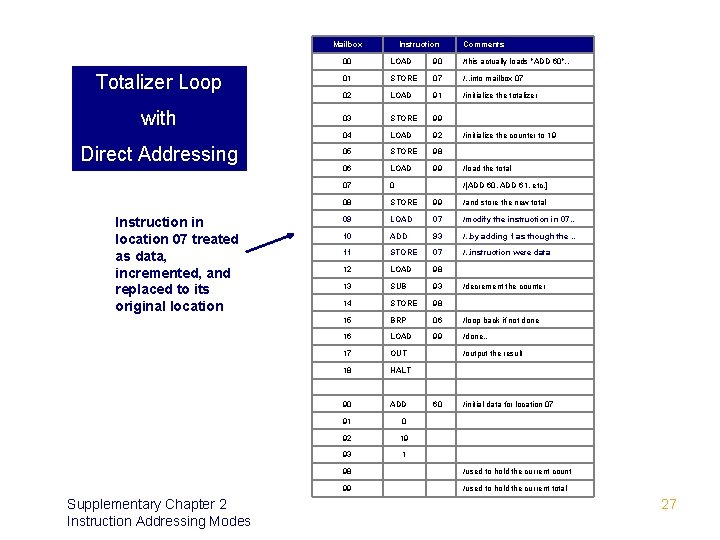

Mailbox Instruction Comments 00 LOAD 90 /this actually loads "ADD 60". . Totalizer Loop 01 STORE 07 /. . into mailbox 07 02 LOAD 91 /initialize the totalizer with 03 STORE 99 04 LOAD 92 05 STORE 98 06 LOAD 99 07 0 08 STORE 99 /and store the new total 09 LOAD 07 /modify the instruction in 07. . 10 ADD 93 /. . by adding 1 as though the. . 11 STORE 07 /. . instruction were data 12 LOAD 98 13 SUB 93 14 STORE 98 15 BRP 06 /loop back if not done 16 LOAD 99 /done. . 17 OUT 18 HALT 90 ADD 91 0 92 19 93 1 Direct Addressing Instruction in location 07 treated as data, incremented, and replaced to its original location Supplementary Chapter 2 Instruction Addressing Modes /initialize the counter to 19 /load the total /[ADD 60, ADD 61, etc. ] /decrement the counter /output the result 60 /initial data for location 07 98 /used to hold the current count 99 /used to hold the current total 27

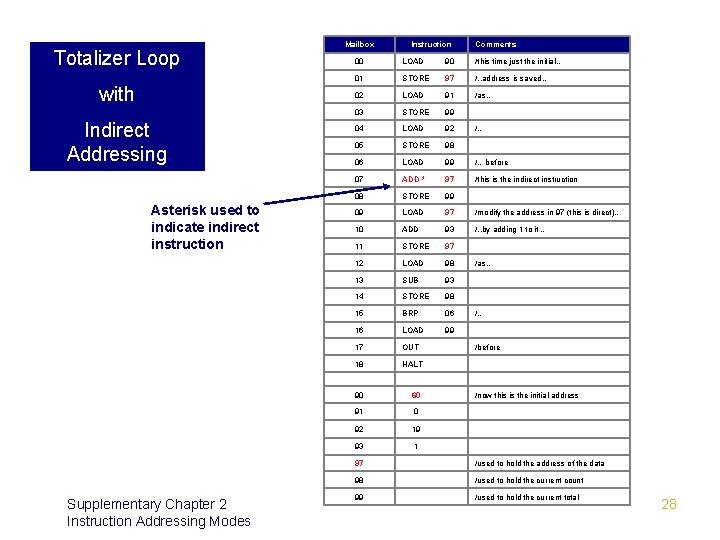

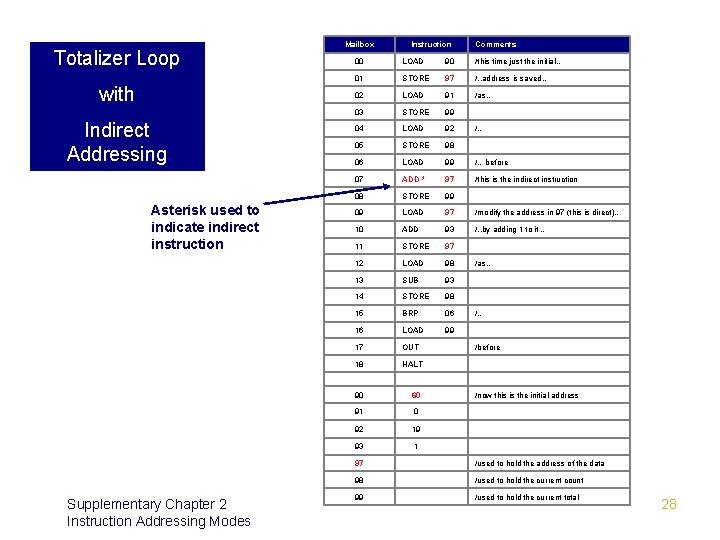

Totalizer Loop with Indirect Addressing Asterisk used to indicate indirect instruction Supplementary Chapter 2 Instruction Addressing Modes Mailbox Instruction Comments 00 LOAD 90 /this time just the initial. . 01 STORE 97 /. . address is saved. . 02 LOAD 91 /as. . 03 STORE 99 04 LOAD 92 05 STORE 98 06 LOAD 99 /…before 07 ADD * 97 /this is the indirect instruction 08 STORE 99 09 LOAD 97 /modify the address in 97 (this is direct). . 10 ADD 93 /. . by adding 1 to it … 11 STORE 97 12 LOAD 98 13 SUB 93 14 STORE 98 15 BRP 06 16 LOAD 99 17 OUT 18 HALT 90 60 91 0 92 19 93 1 /… /as… /… /before /now this is the initial address 97 /used to hold the address of the data 98 /used to hold the current count 99 /used to hold the current total 28

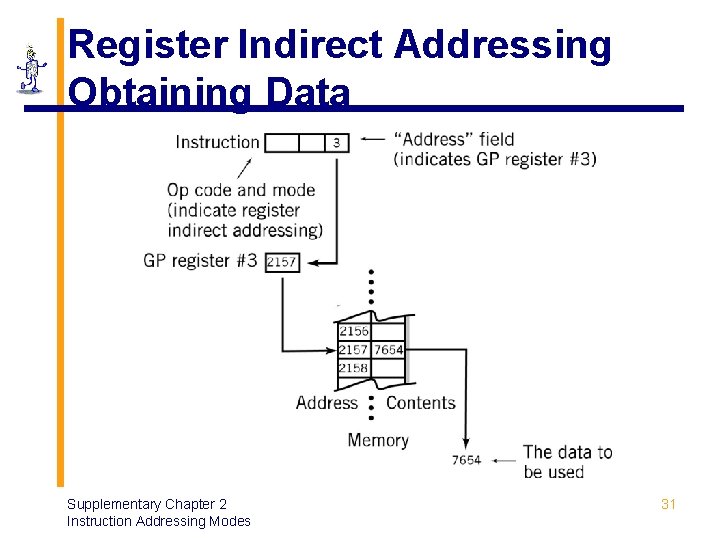

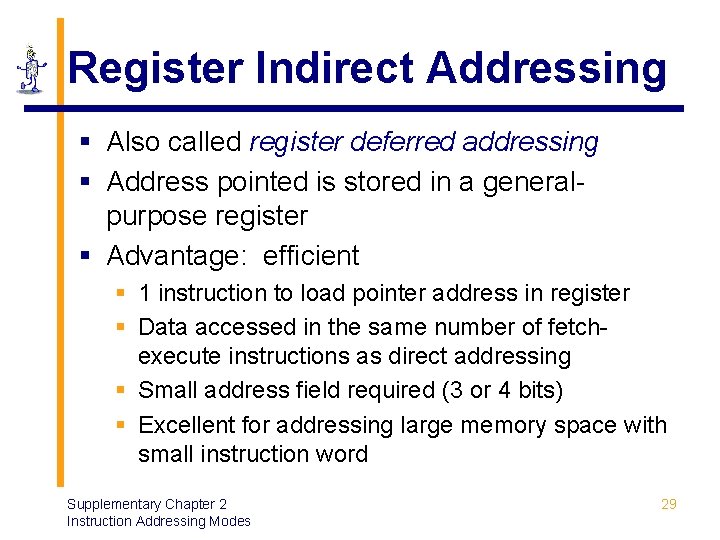

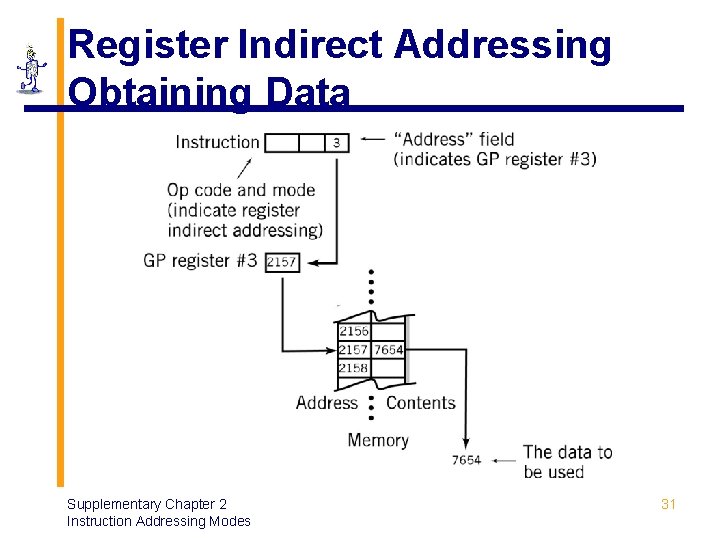

Register Indirect Addressing § Also called register deferred addressing § Address pointed is stored in a generalpurpose register § Advantage: efficient § 1 instruction to load pointer address in register § Data accessed in the same number of fetchexecute instructions as direct addressing § Small address field required (3 or 4 bits) § Excellent for addressing large memory space with small instruction word Supplementary Chapter 2 Instruction Addressing Modes 29

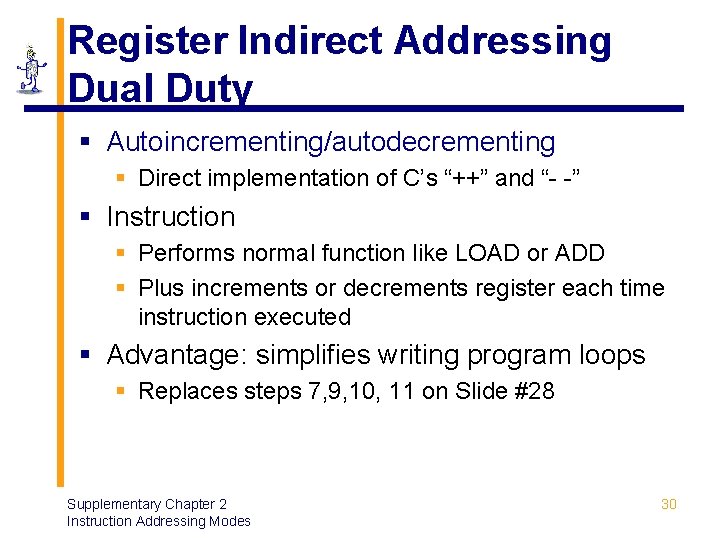

Register Indirect Addressing Dual Duty § Autoincrementing/autodecrementing § Direct implementation of C’s “++” and “- -” § Instruction § Performs normal function like LOAD or ADD § Plus increments or decrements register each time instruction executed § Advantage: simplifies writing program loops § Replaces steps 7, 9, 10, 11 on Slide #28 Supplementary Chapter 2 Instruction Addressing Modes 30

Register Indirect Addressing Obtaining Data Supplementary Chapter 2 Instruction Addressing Modes 31

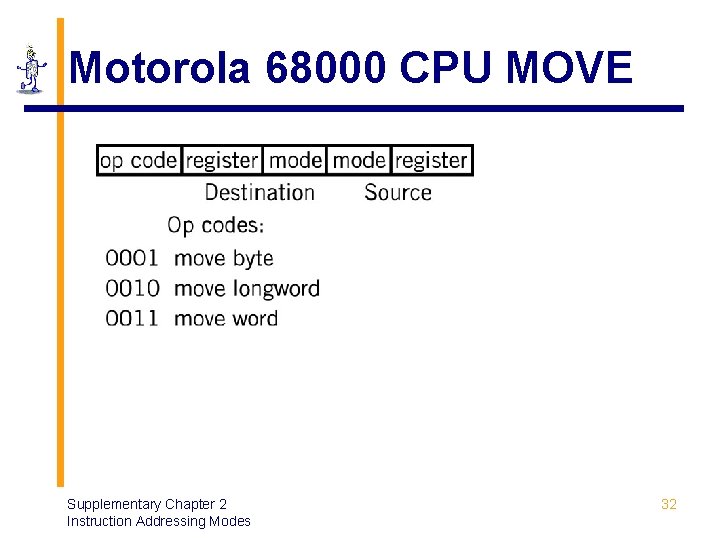

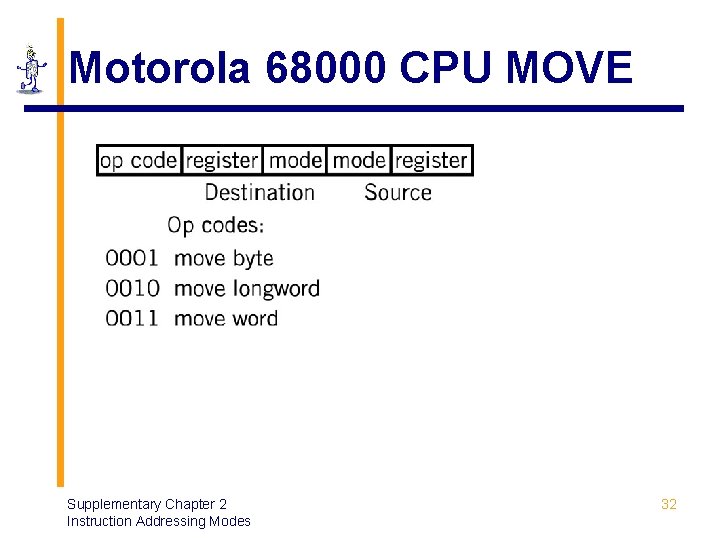

Motorola 68000 CPU MOVE Supplementary Chapter 2 Instruction Addressing Modes 32

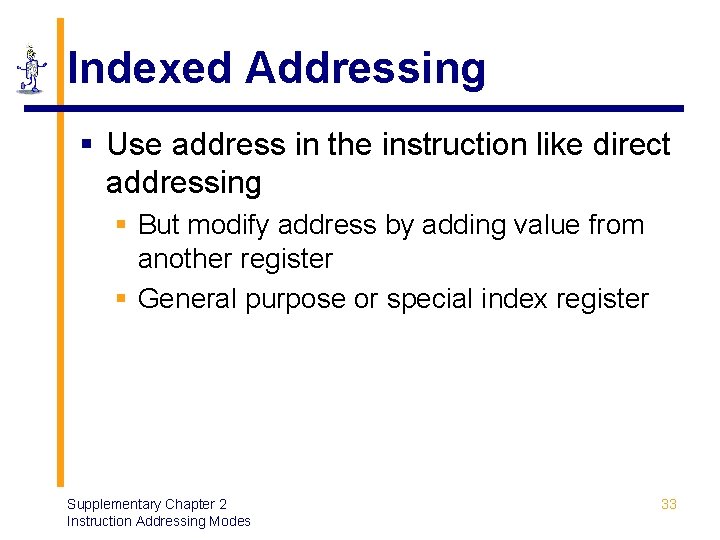

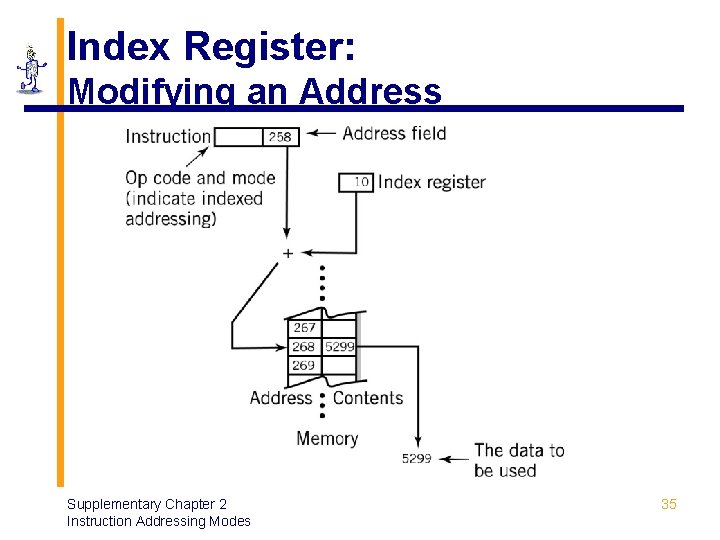

Indexed Addressing § Use address in the instruction like direct addressing § But modify address by adding value from another register § General purpose or special index register Supplementary Chapter 2 Instruction Addressing Modes 33

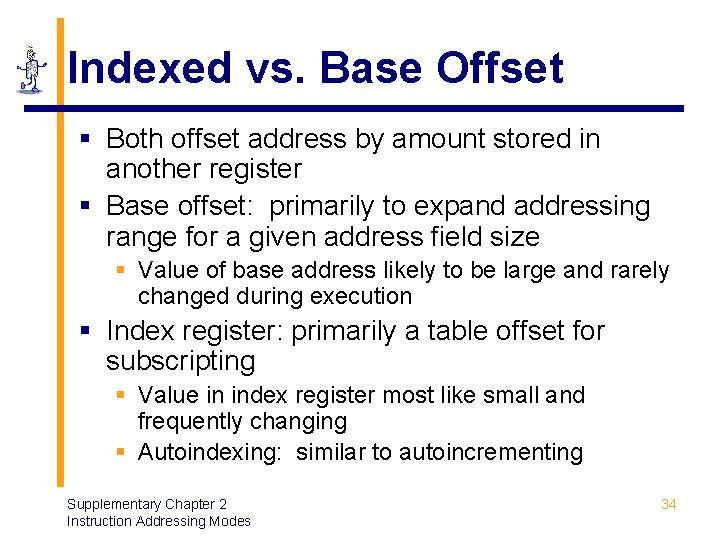

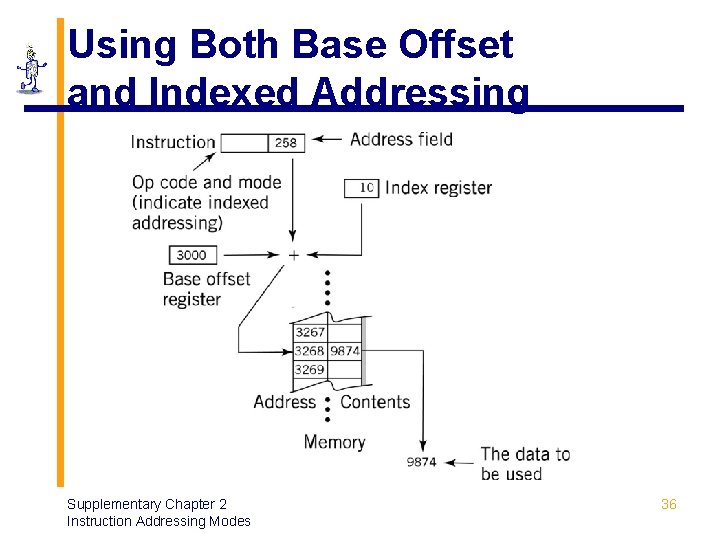

Indexed vs. Base Offset § Both offset address by amount stored in another register § Base offset: primarily to expand addressing range for a given address field size § Value of base address likely to be large and rarely changed during execution § Index register: primarily a table offset for subscripting § Value in index register most like small and frequently changing § Autoindexing: similar to autoincrementing Supplementary Chapter 2 Instruction Addressing Modes 34

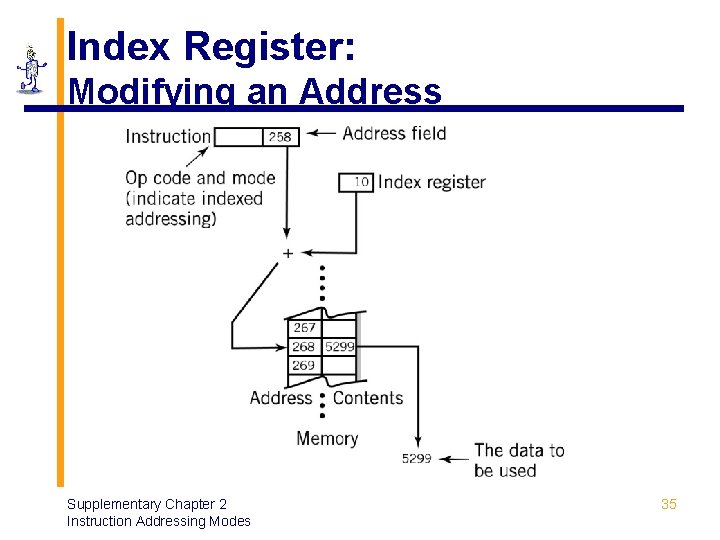

Index Register: Modifying an Address Supplementary Chapter 2 Instruction Addressing Modes 35

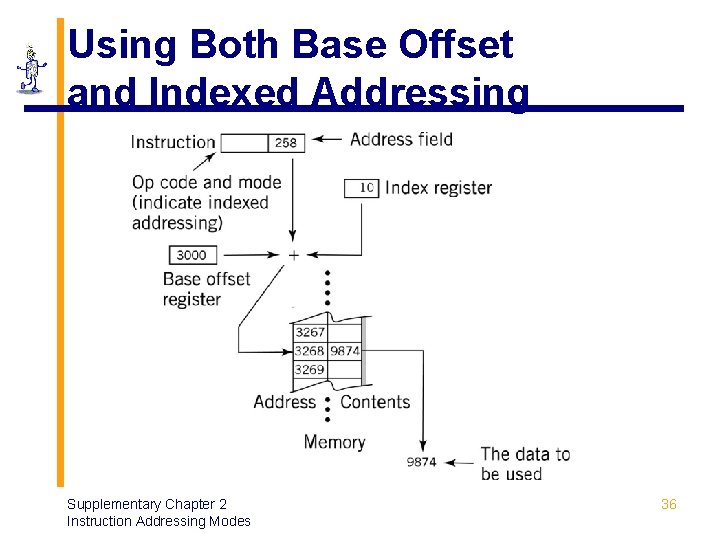

Using Both Base Offset and Indexed Addressing Supplementary Chapter 2 Instruction Addressing Modes 36

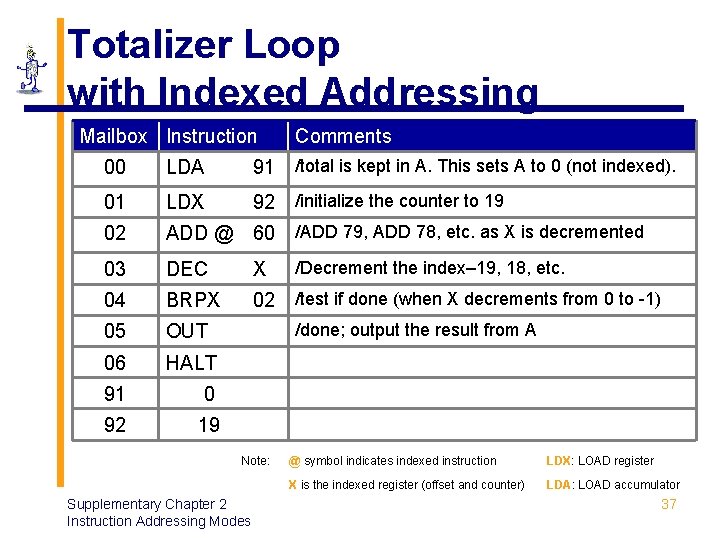

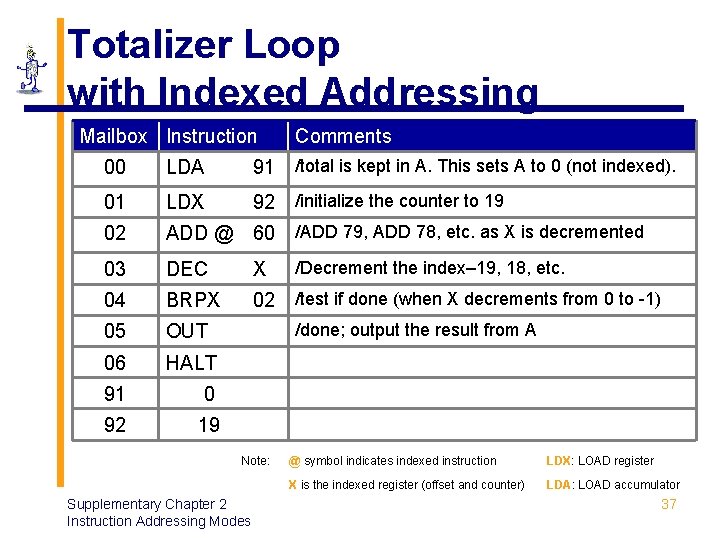

Totalizer Loop with Indexed Addressing Mailbox Instruction Comments 00 LDA 91 /total is kept in A. This sets A to 0 (not indexed). 01 LDX 92 /initialize the counter to 19 02 ADD @ 60 /ADD 79, ADD 78, etc. as X is decremented 03 DEC X 04 BRPX 02 /test if done (when X decrements from 0 to -1) 05 OUT 06 HALT 91 0 92 19 /Decrement the index– 19, 18, etc. /done; output the result from A Note: Supplementary Chapter 2 Instruction Addressing Modes @ symbol indicates indexed instruction LDX: LOAD register X is the indexed register (offset and counter) LDA: LOAD accumulator 37

Copyright 2003 John Wiley & Sons All rights reserved. Reproduction or translation of this work beyond that permitted in Section 117 of the 1976 United States Copyright Act without express permission of the copyright owner is unlawful. Request for further information should be addressed to the permissions Department, John Wiley & Songs, Inc. The purchaser may make back-up copies for his/her own use only and not for distribution or resale. The Publisher assumes no responsibility for errors, omissions, or damages caused by the use of these programs or from the use of the information contained herein. Supplementary Chapter 2 Instruction Addressing Modes 38