Accessing Atmega 32 SRAM data memory Addressing Modes

- Slides: 17

Accessing Atmega 32 SRAM data memory Addressing Modes Load and Store Instructions CS-280 Dr. Mark L. Hornick 1

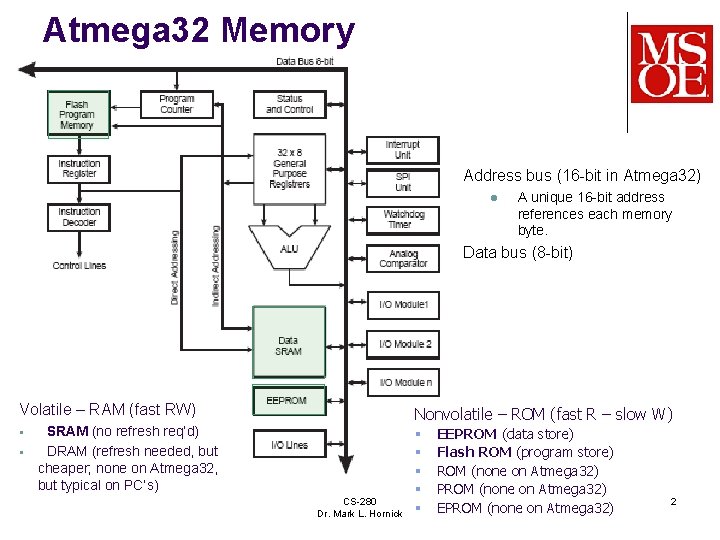

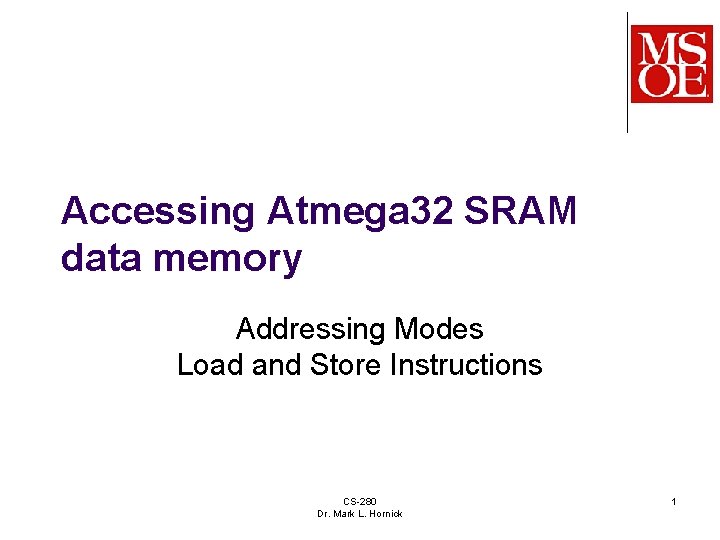

Atmega 32 Memory Address bus (16 -bit in Atmega 32) l A unique 16 -bit address references each memory byte. Data bus (8 -bit) Volatile – RAM (fast RW) § § Nonvolatile – ROM (fast R – slow W) SRAM (no refresh req’d) DRAM (refresh needed, but cheaper; none on Atmega 32, but typical on PC’s) CS-280 Dr. Mark L. Hornick § § § EEPROM (data store) Flash ROM (program store) ROM (none on Atmega 32) PROM (none on Atmega 32) EPROM (none on Atmega 32) 2

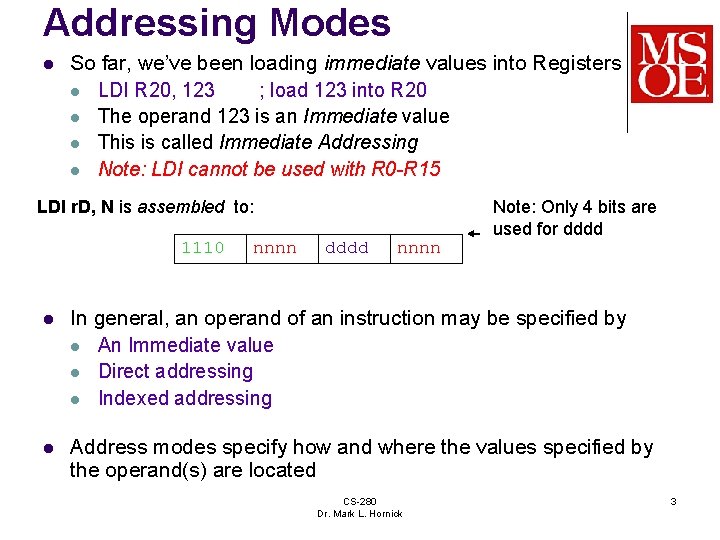

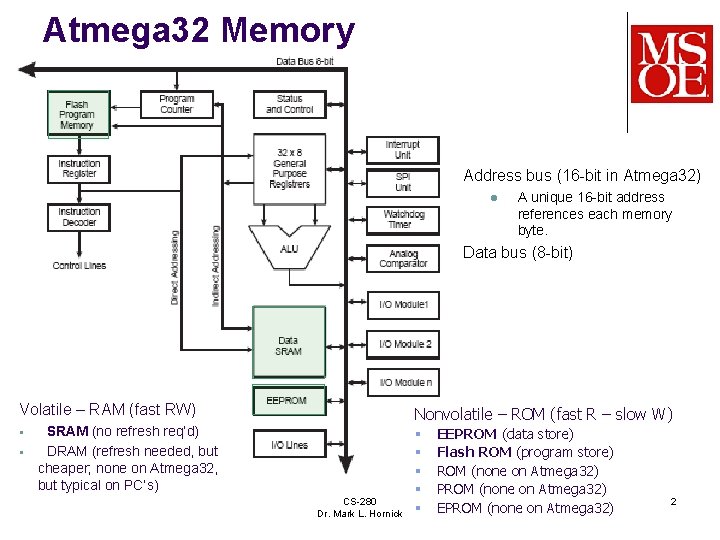

Addressing Modes l So far, we’ve been loading immediate values into Registers l LDI R 20, 123 ; load 123 into R 20 l The operand 123 is an Immediate value l This is called Immediate Addressing l Note: LDI cannot be used with R 0 -R 15 Note: Only 4 bits are used for dddd LDI r. D, N is assembled to: 1110 nnnn dddd nnnn l In general, an operand of an instruction may be specified by l An Immediate value l Direct addressing l Indexed addressing l Address modes specify how and where the values specified by the operand(s) are located CS-280 Dr. Mark L. Hornick 3

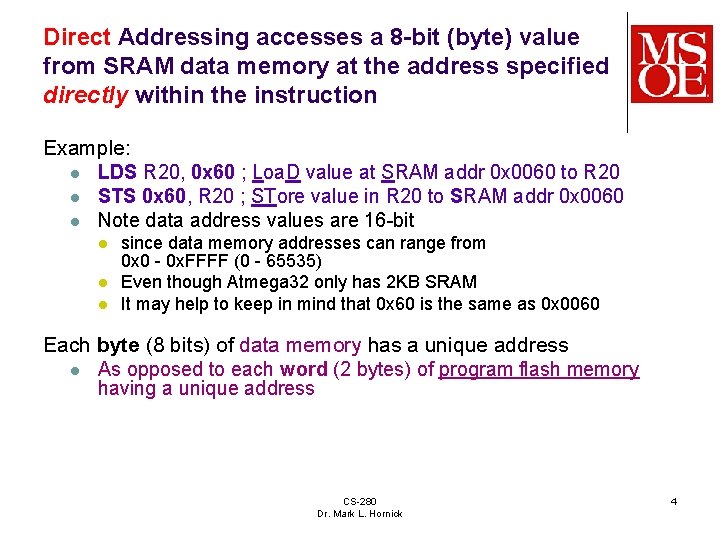

Direct Addressing accesses a 8 -bit (byte) value from SRAM data memory at the address specified directly within the instruction Example: l LDS R 20, 0 x 60 ; Loa. D value at SRAM addr 0 x 0060 to R 20 l STS 0 x 60, R 20 ; STore value in R 20 to SRAM addr 0 x 0060 l Note data address values are 16 -bit l l l since data memory addresses can range from 0 x 0 - 0 x. FFFF (0 - 65535) Even though Atmega 32 only has 2 KB SRAM It may help to keep in mind that 0 x 60 is the same as 0 x 0060 Each byte (8 bits) of data memory has a unique address l As opposed to each word (2 bytes) of program flash memory having a unique address CS-280 Dr. Mark L. Hornick 4

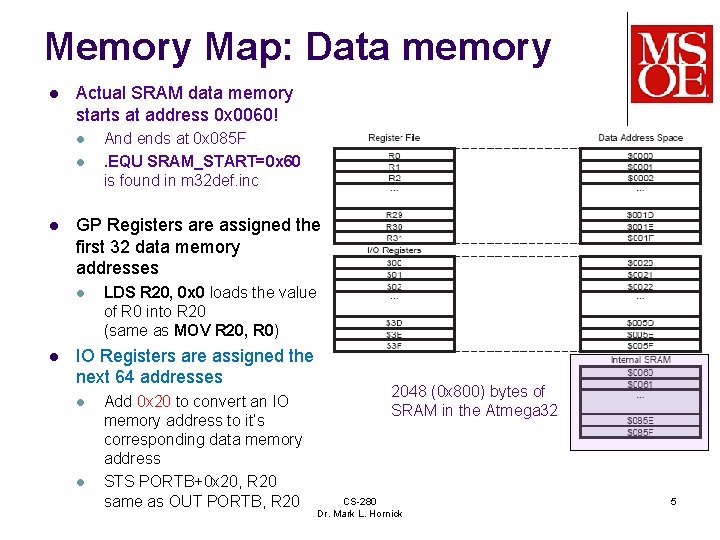

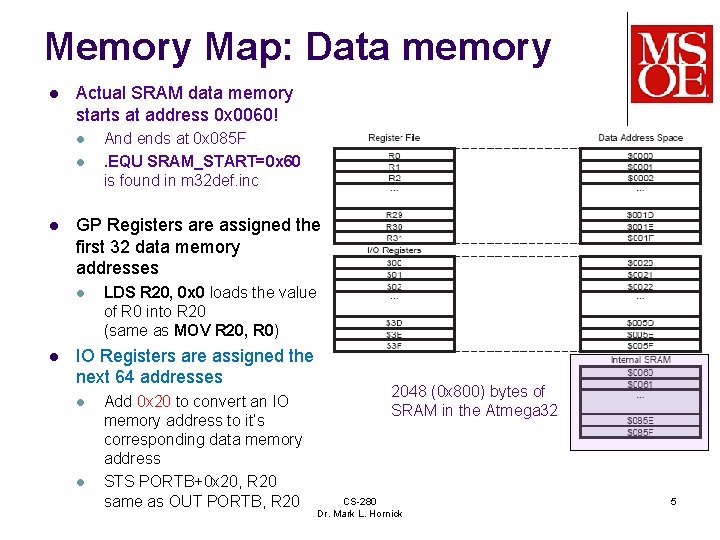

Memory Map: Data memory l Actual SRAM data memory starts at address 0 x 0060! l l l GP Registers are assigned the first 32 data memory addresses l l And ends at 0 x 085 F. EQU SRAM_START=0 x 60 is found in m 32 def. inc LDS R 20, 0 x 0 loads the value of R 0 into R 20 (same as MOV R 20, R 0) IO Registers are assigned the next 64 addresses l l Add 0 x 20 to convert an IO memory address to it’s corresponding data memory address STS PORTB+0 x 20, R 20 same as OUT PORTB, R 20 2048 (0 x 800) bytes of SRAM in the Atmega 32 CS-280 Dr. Mark L. Hornick 5

Referring to raw memory addresses is not ideal l l We can explicitly define constant symbols to refer to addresses using the. EQU directive Example: l l l . EQU x 1=0 x 0060 ; define a symbol “x 1” LDS R 20, x 1 ; data load addr is referred to by x 1 STS x 1, R 20 ; data store addr is x 1 CS-280 Dr. Mark L. Hornick 6

An even better way to specify addresses is to use labels l l l We defined labels to identify addresses in program memory to be used as jump/branch targets loop: RJMP loop The address assigned to a label is determined automatically by the Assembler Similarly, we can define labels to identify addresses in data memory to be used as load/store targets CS-280 Dr. Mark L. Hornick 7

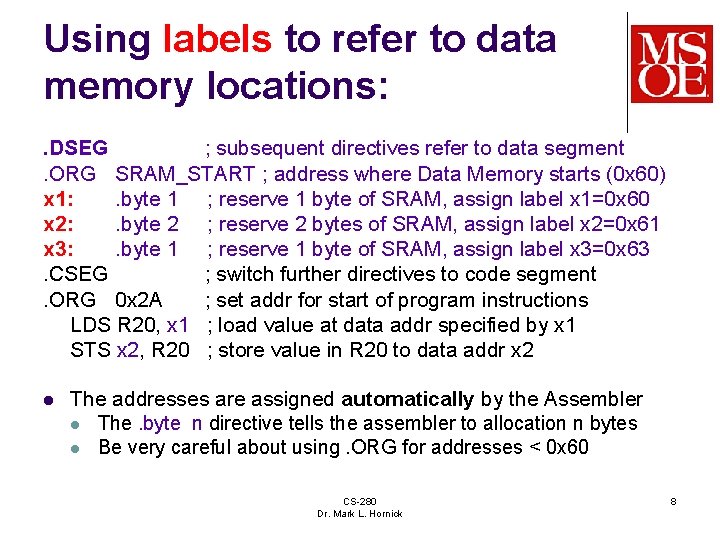

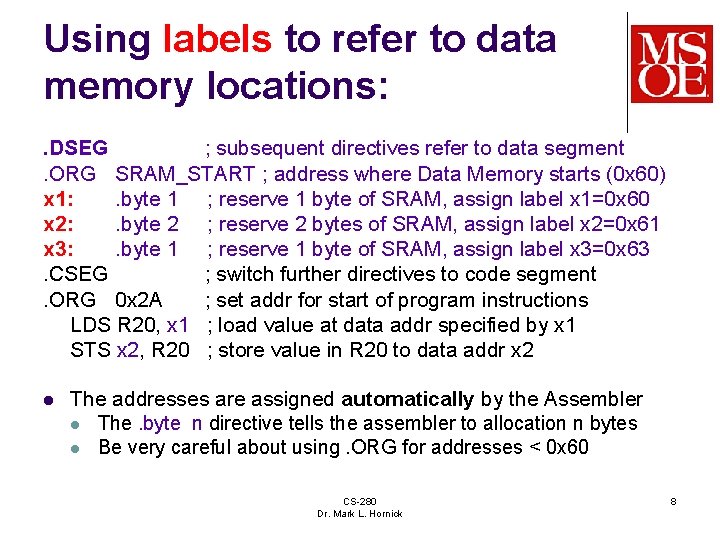

Using labels to refer to data memory locations: . DSEG ; subsequent directives refer to data segment. ORG SRAM_START ; address where Data Memory starts (0 x 60) x 1: . byte 1 ; reserve 1 byte of SRAM, assign label x 1=0 x 60 x 2: . byte 2 ; reserve 2 bytes of SRAM, assign label x 2=0 x 61 x 3: . byte 1 ; reserve 1 byte of SRAM, assign label x 3=0 x 63. CSEG ; switch further directives to code segment. ORG 0 x 2 A ; set addr for start of program instructions LDS R 20, x 1 ; load value at data addr specified by x 1 STS x 2, R 20 ; store value in R 20 to data addr x 2 l The addresses are assigned automatically by the Assembler l The. byte n directive tells the assembler to allocation n bytes l Be very careful about using. ORG for addresses < 0 x 60 CS-280 Dr. Mark L. Hornick 8

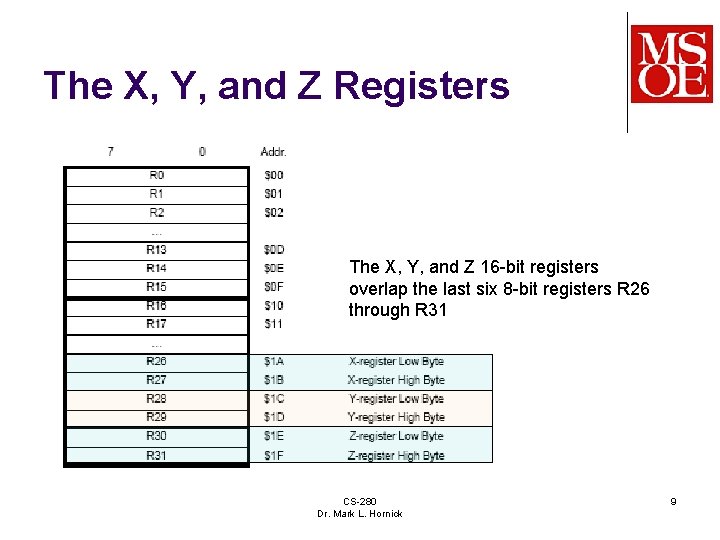

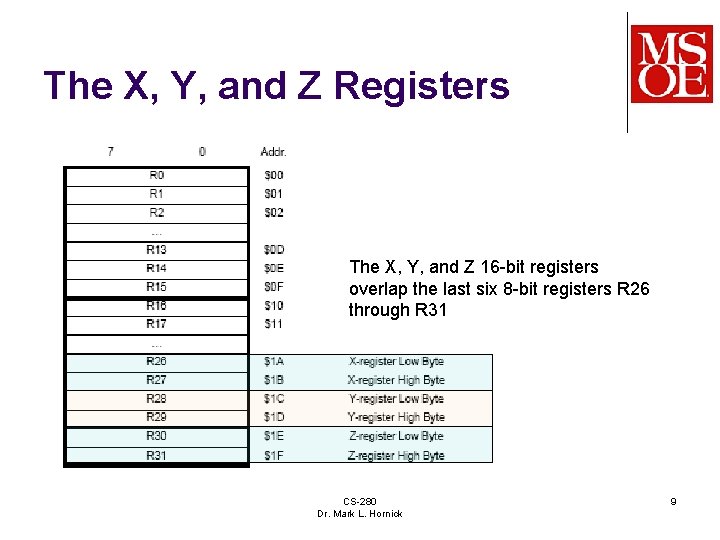

The X, Y, and Z Registers The X, Y, and Z 16 -bit registers overlap the last six 8 -bit registers R 26 through R 31 CS-280 Dr. Mark L. Hornick 9

Indirect Addressing l Accesses a 8 -bit (byte) value from SRAM data memory at the address specified indirectly via the 16 -bit X, Y, or Z index-registers l Example: l l l LD R 20, X ; load value at data addr held in X to R 20 ST Y, R 20 ; store value in R 20 to data addr held in Y Note X, Y, Z hold data address values that are 16 -bits CS-280 Dr. Mark L. Hornick 10

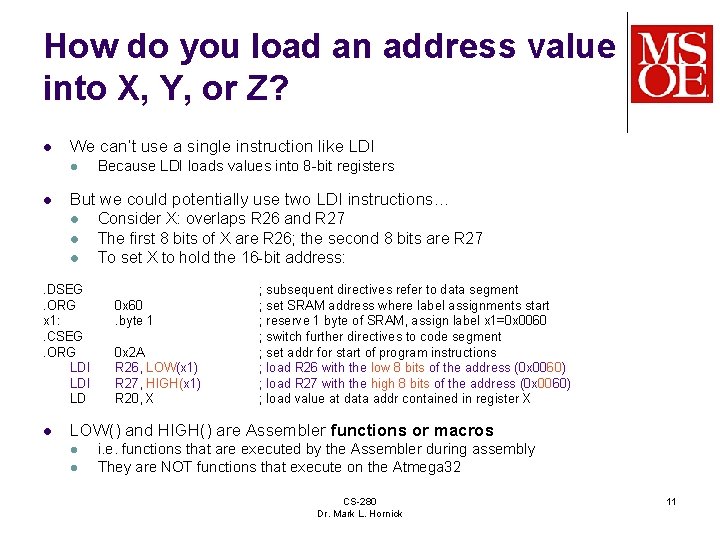

How do you load an address value into X, Y, or Z? l We can’t use a single instruction like LDI l l But we could potentially use two LDI instructions… l l l . DSEG. ORG x 1: . CSEG. ORG LDI LD l Because LDI loads values into 8 -bit registers Consider X: overlaps R 26 and R 27 The first 8 bits of X are R 26; the second 8 bits are R 27 To set X to hold the 16 -bit address: 0 x 60. byte 1 0 x 2 A R 26, LOW(x 1) R 27, HIGH(x 1) R 20, X ; subsequent directives refer to data segment ; set SRAM address where label assignments start ; reserve 1 byte of SRAM, assign label x 1=0 x 0060 ; switch further directives to code segment ; set addr for start of program instructions ; load R 26 with the low 8 bits of the address (0 x 0060) ; load R 27 with the high 8 bits of the address (0 x 0060) ; load value at data addr contained in register X LOW() and HIGH() are Assembler functions or macros l l i. e. functions that are executed by the Assembler during assembly They are NOT functions that execute on the Atmega 32 CS-280 Dr. Mark L. Hornick 11

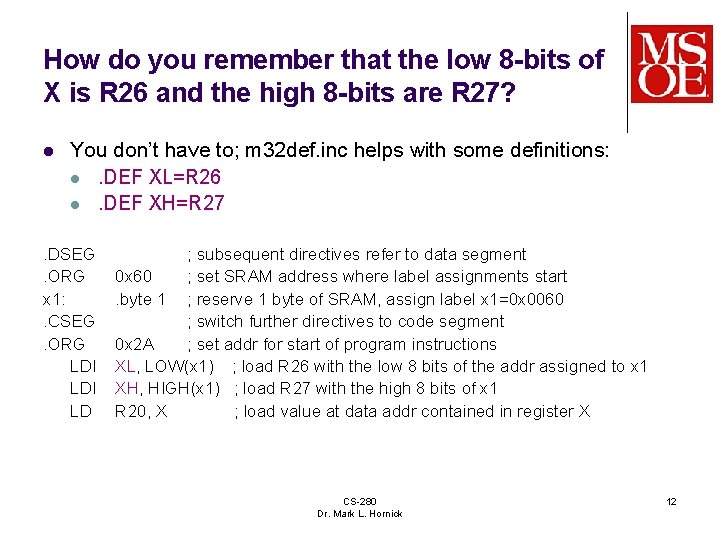

How do you remember that the low 8 -bits of X is R 26 and the high 8 -bits are R 27? l You don’t have to; m 32 def. inc helps with some definitions: l. DEF XL=R 26 l. DEF XH=R 27 . DSEG. ORG x 1: . CSEG. ORG LDI LD ; subsequent directives refer to data segment 0 x 60 ; set SRAM address where label assignments start. byte 1 ; reserve 1 byte of SRAM, assign label x 1=0 x 0060 ; switch further directives to code segment 0 x 2 A ; set addr for start of program instructions XL, LOW(x 1) ; load R 26 with the low 8 bits of the addr assigned to x 1 XH, HIGH(x 1) ; load R 27 with the high 8 bits of x 1 R 20, X ; load value at data addr contained in register X CS-280 Dr. Mark L. Hornick 12

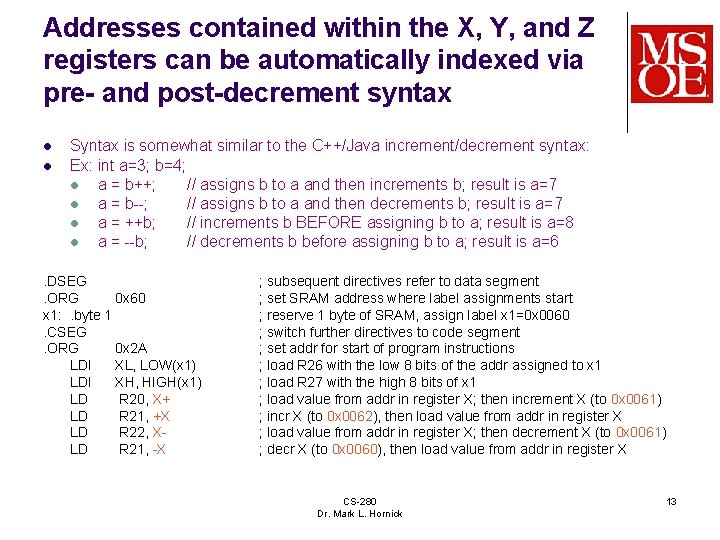

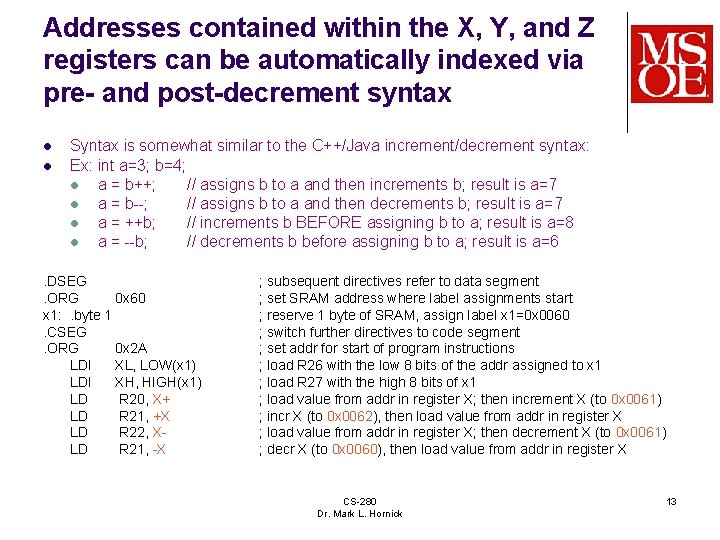

Addresses contained within the X, Y, and Z registers can be automatically indexed via pre- and post-decrement syntax l l Syntax is somewhat similar to the C++/Java increment/decrement syntax: Ex: int a=3; b=4; l a = b++; // assigns b to a and then increments b; result is a=7 l a = b--; // assigns b to a and then decrements b; result is a=7 l a = ++b; // increments b BEFORE assigning b to a; result is a=8 l a = --b; // decrements b before assigning b to a; result is a=6 . DSEG. ORG 0 x 60 x 1: . byte 1. CSEG. ORG 0 x 2 A LDI XL, LOW(x 1) LDI XH, HIGH(x 1) LD R 20, X+ LD R 21, +X LD R 22, XLD R 21, -X ; subsequent directives refer to data segment ; set SRAM address where label assignments start ; reserve 1 byte of SRAM, assign label x 1=0 x 0060 ; switch further directives to code segment ; set addr for start of program instructions ; load R 26 with the low 8 bits of the addr assigned to x 1 ; load R 27 with the high 8 bits of x 1 ; load value from addr in register X; then increment X (to 0 x 0061) ; incr X (to 0 x 0062), then load value from addr in register X ; load value from addr in register X; then decrement X (to 0 x 0061) ; decr X (to 0 x 0060), then load value from addr in register X CS-280 Dr. Mark L. Hornick 13

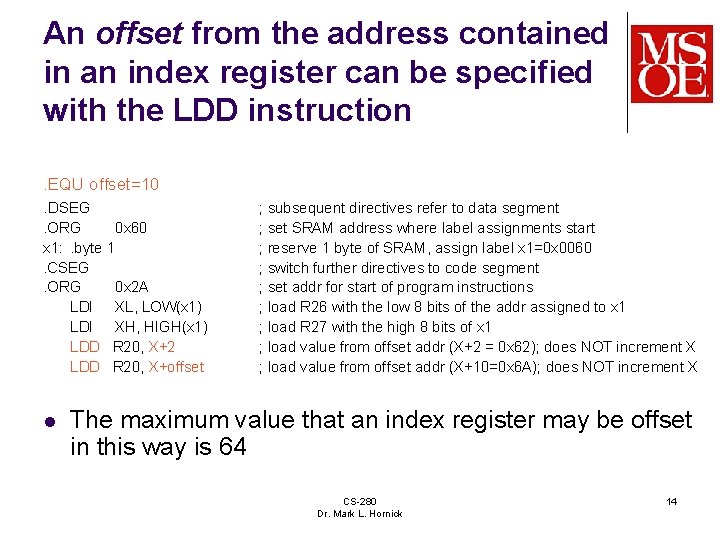

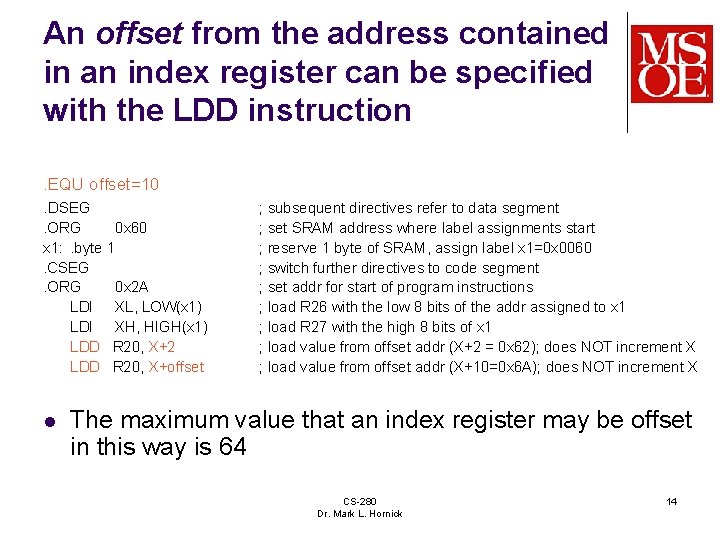

An offset from the address contained in an index register can be specified with the LDD instruction. EQU offset=10. DSEG. ORG 0 x 60 x 1: . byte 1. CSEG. ORG 0 x 2 A LDI XL, LOW(x 1) LDI XH, HIGH(x 1) LDD R 20, X+2 LDD R 20, X+offset l ; subsequent directives refer to data segment ; set SRAM address where label assignments start ; reserve 1 byte of SRAM, assign label x 1=0 x 0060 ; switch further directives to code segment ; set addr for start of program instructions ; load R 26 with the low 8 bits of the addr assigned to x 1 ; load R 27 with the high 8 bits of x 1 ; load value from offset addr (X+2 = 0 x 62); does NOT increment X ; load value from offset addr (X+10=0 x 6 A); does NOT increment X The maximum value that an index register may be offset in this way is 64 CS-280 Dr. Mark L. Hornick 14

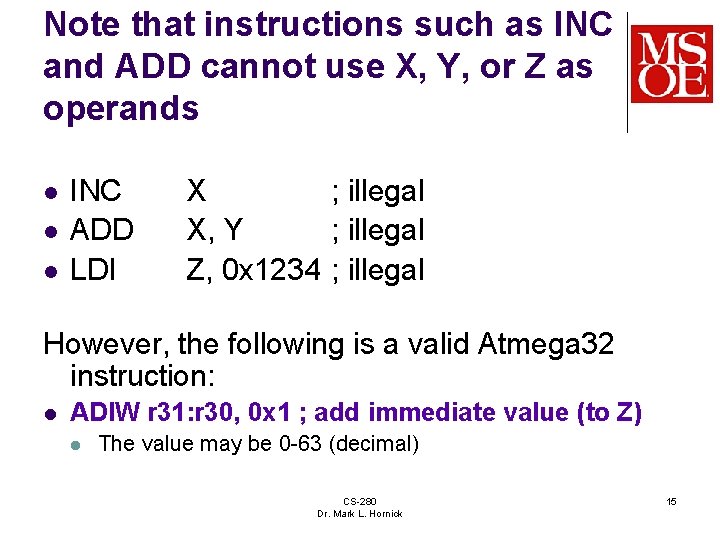

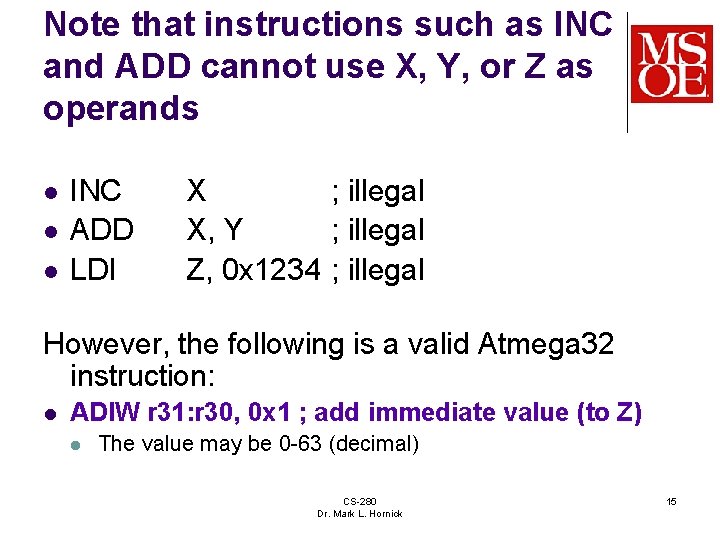

Note that instructions such as INC and ADD cannot use X, Y, or Z as operands l l l INC ADD LDI X ; illegal X, Y ; illegal Z, 0 x 1234 ; illegal However, the following is a valid Atmega 32 instruction: l ADIW r 31: r 30, 0 x 1 ; add immediate value (to Z) l The value may be 0 -63 (decimal) CS-280 Dr. Mark L. Hornick 15

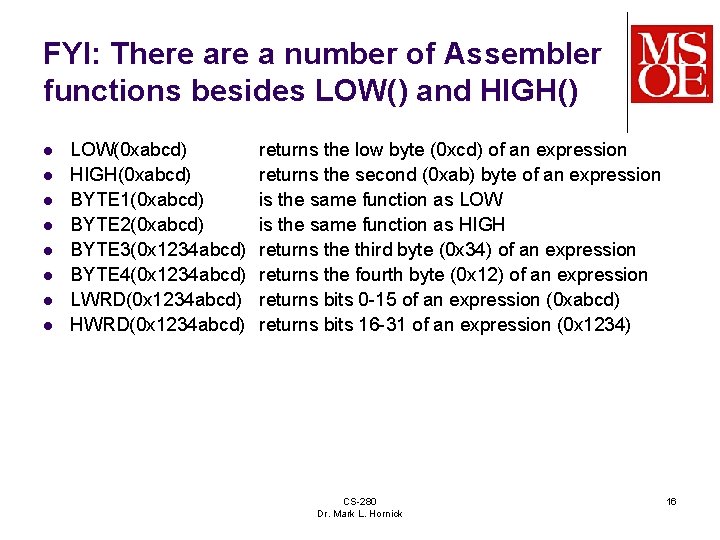

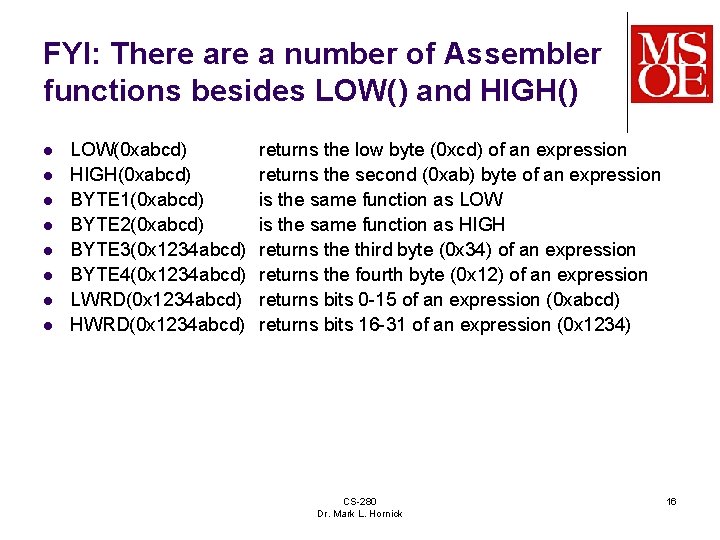

FYI: There a number of Assembler functions besides LOW() and HIGH() l l l l LOW(0 xabcd) HIGH(0 xabcd) BYTE 1(0 xabcd) BYTE 2(0 xabcd) BYTE 3(0 x 1234 abcd) BYTE 4(0 x 1234 abcd) LWRD(0 x 1234 abcd) HWRD(0 x 1234 abcd) returns the low byte (0 xcd) of an expression returns the second (0 xab) byte of an expression is the same function as LOW is the same function as HIGH returns the third byte (0 x 34) of an expression returns the fourth byte (0 x 12) of an expression returns bits 0 -15 of an expression (0 xabcd) returns bits 16 -31 of an expression (0 x 1234) CS-280 Dr. Mark L. Hornick 16

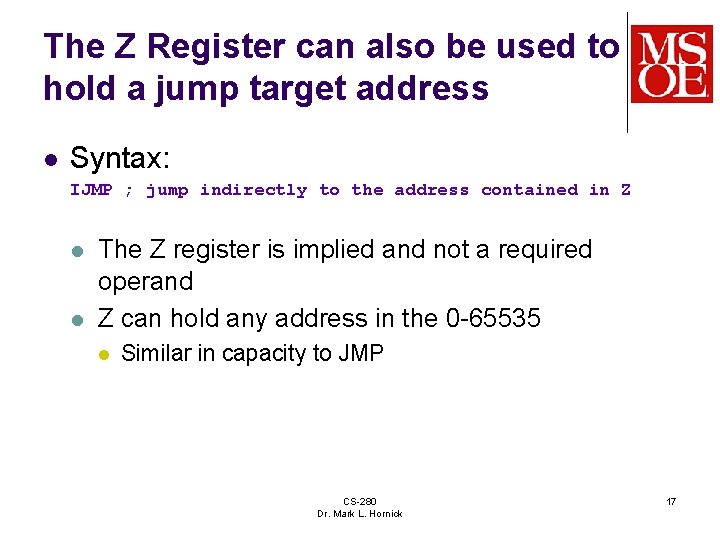

The Z Register can also be used to hold a jump target address l Syntax: IJMP ; jump indirectly to the address contained in Z l l The Z register is implied and not a required operand Z can hold any address in the 0 -65535 l Similar in capacity to JMP CS-280 Dr. Mark L. Hornick 17