SPARC Registers General purpose registers 32 immediately visible

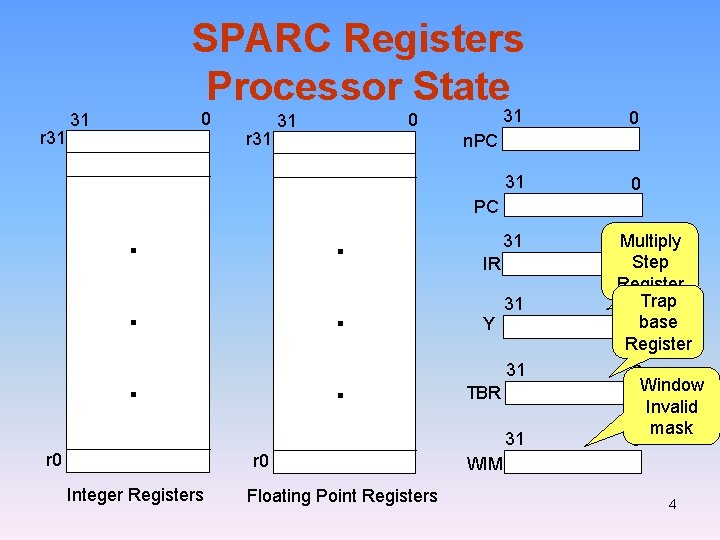

SPARC Registers • General purpose registers: 32 immediately visible integer registers and 32 floating point registers • The Processor Status Register, PSR contains the flags or condition codes • Program Counters, PC and n. PC hold the current and next instruction address • Special purpose registers: WIM, TBR and multiply step register Y. 1

CS 501 Advanced Computer Architecture Lecture 11 Dr. Noor Muhammad Sheikh 2

Review 3

SPARC Registers Processor State r 31 0 31 r 31 . . . 0 31 31 0 n. PC . . . PC 31 IR Y 31 31 TBR 31 r 0 Integer Registers Floating Point Registers Multiply 0 Step Register 0 Trap base Register 0 Window Invalid mask 0 WIM 4

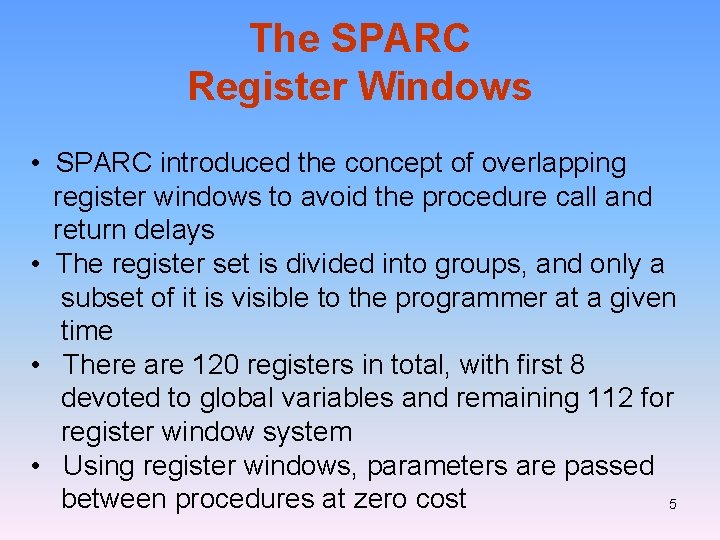

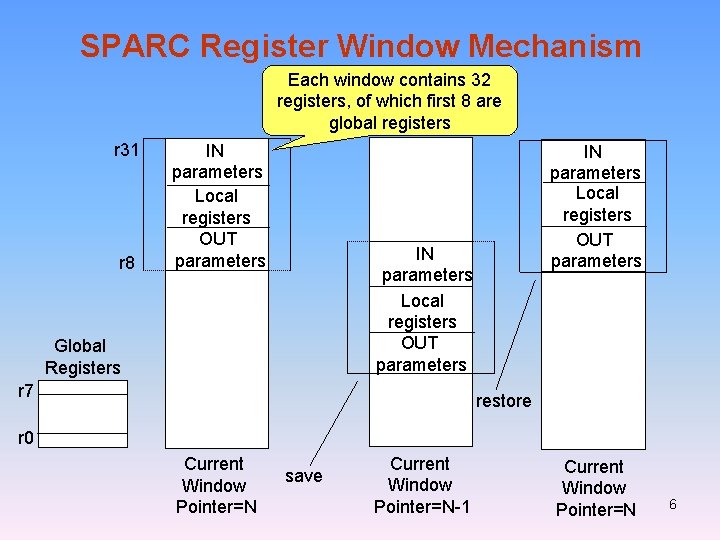

The SPARC Register Windows • SPARC introduced the concept of overlapping register windows to avoid the procedure call and return delays • The register set is divided into groups, and only a subset of it is visible to the programmer at a given time • There are 120 registers in total, with first 8 devoted to global variables and remaining 112 for register window system • Using register windows, parameters are passed between procedures at zero cost 5

SPARC Register Window Mechanism Each window contains 32 registers, of which first 8 are global registers r 31 r 8 IN parameters Local registers OUT parameters Global Registers r 7 restore r 0 Current Window Pointer=N save Current Window Pointer=N-1 Current Window Pointer=N 6

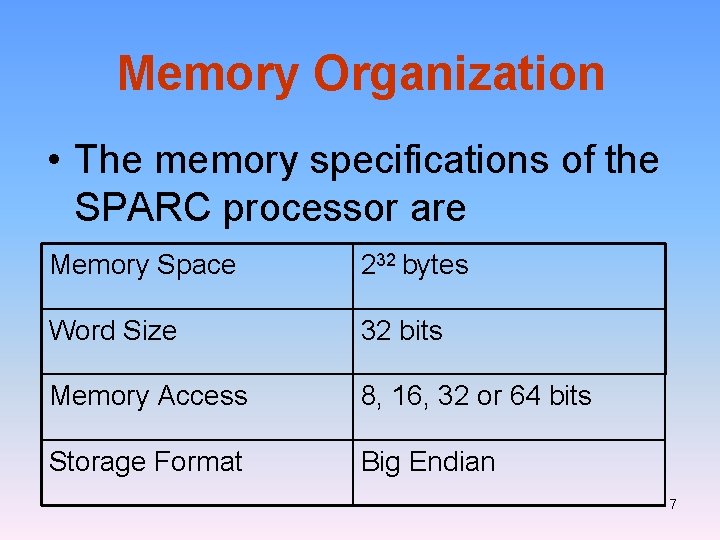

Memory Organization • The memory specifications of the SPARC processor are Memory Space 232 bytes Word Size 32 bits Memory Access 8, 16, 32 or 64 bits Storage Format Big Endian 7

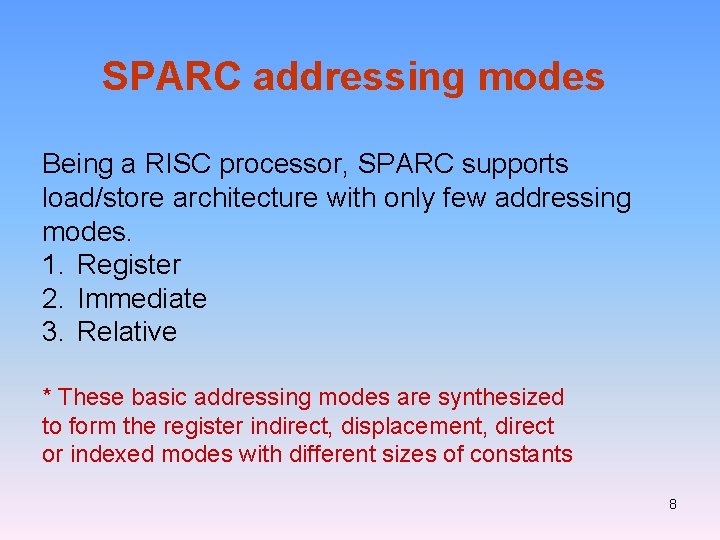

SPARC addressing modes Being a RISC processor, SPARC supports load/store architecture with only few addressing modes. 1. Register 2. Immediate 3. Relative * These basic addressing modes are synthesized to form the register indirect, displacement, direct or indexed modes with different sizes of constants 8

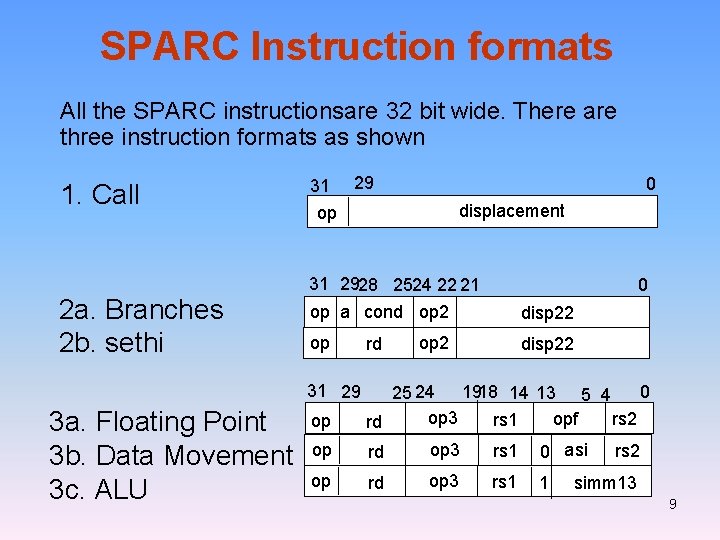

SPARC Instruction formats All the SPARC instructionsare 32 bit wide. There are three instruction formats as shown 1. Call 2 a. Branches 2 b. sethi 3 a. Floating Point 3 b. Data Movement 3 c. ALU 31 29 op 0 displacement 31 2928 2524 22 21 0 op a cond op 2 disp 22 op rd 31 29 op 1918 14 13 5 4 0 25 24 op 3 opf rs 2 rs 1 rd op 3 rs 1 0 asi op rd op 3 rs 1 1 rs 2 simm 13 9

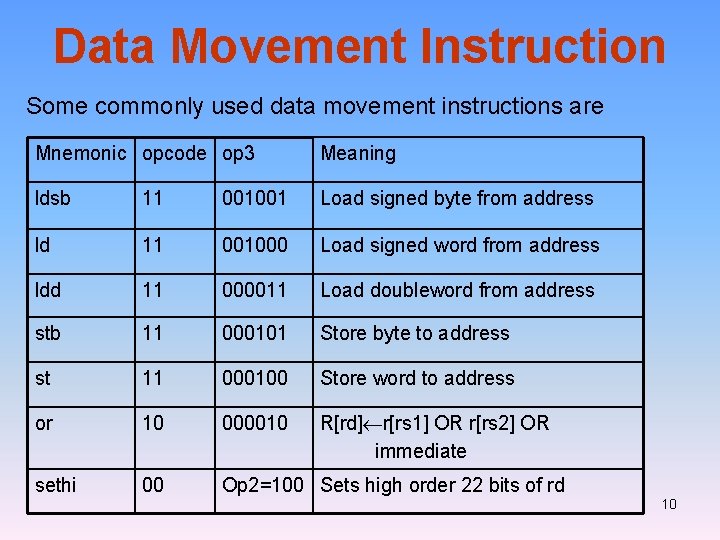

Data Movement Instruction Some commonly used data movement instructions are Mnemonic opcode op 3 Meaning ldsb 11 001001 Load signed byte from address ld 11 001000 Load signed word from address ldd 11 000011 Load doubleword from address stb 11 000101 Store byte to address st 11 000100 Store word to address or 10 000010 R[rd] r[rs 1] OR r[rs 2] OR immediate sethi 00 Op 2=100 Sets high order 22 bits of rd 10

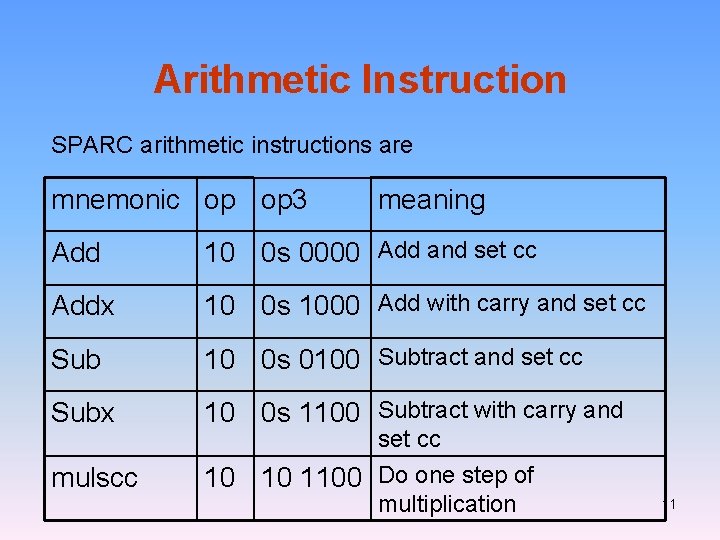

Arithmetic Instruction SPARC arithmetic instructions are mnemonic op op 3 meaning Add 10 0 s 0000 Add and set cc Addx 10 0 s 1000 Add with carry and set cc Sub 10 0 s 0100 Subtract and set cc Subx 10 0 s 1100 Subtract with carry and mulscc 10 set cc 10 1100 Do one step of multiplication 11

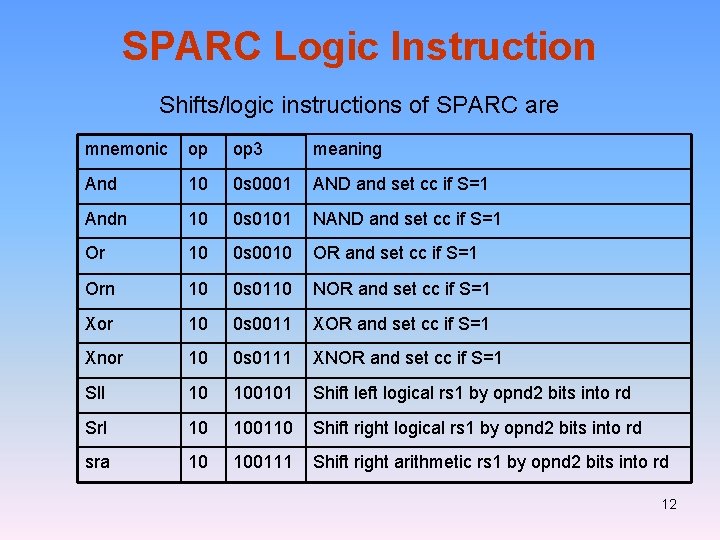

SPARC Logic Instruction Shifts/logic instructions of SPARC are mnemonic op op 3 meaning And 10 0 s 0001 AND and set cc if S=1 Andn 10 0 s 0101 NAND and set cc if S=1 Or 10 0 s 0010 OR and set cc if S=1 Orn 10 0 s 0110 NOR and set cc if S=1 Xor 10 0 s 0011 XOR and set cc if S=1 Xnor 10 0 s 0111 XNOR and set cc if S=1 Sll 10 100101 Shift left logical rs 1 by opnd 2 bits into rd Srl 10 100110 Shift right logical rs 1 by opnd 2 bits into rd sra 10 100111 Shift right arithmetic rs 1 by opnd 2 bits into rd 12

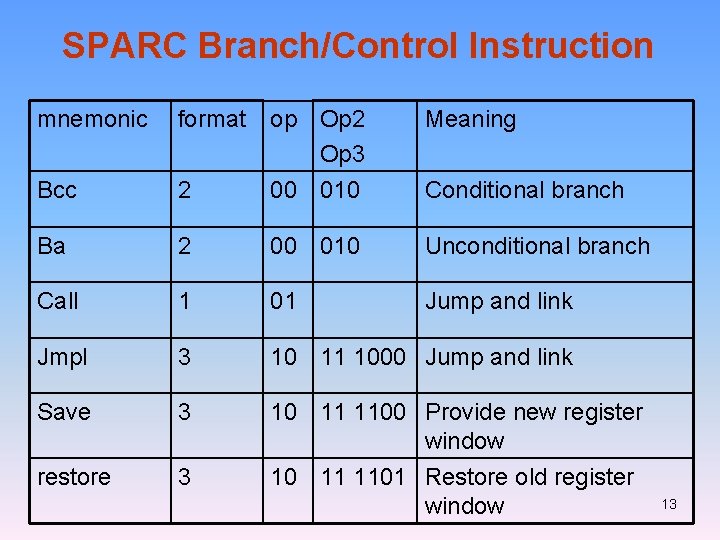

SPARC Branch/Control Instruction mnemonic format Meaning 2 op Op 2 Op 3 00 010 Bcc Ba 2 00 010 Unconditional branch Call 1 01 Jump and link Jmpl 3 10 11 1000 Jump and link Save 3 restore 3 10 11 1100 Provide new register window 10 11 1101 Restore old register window Conditional branch 13

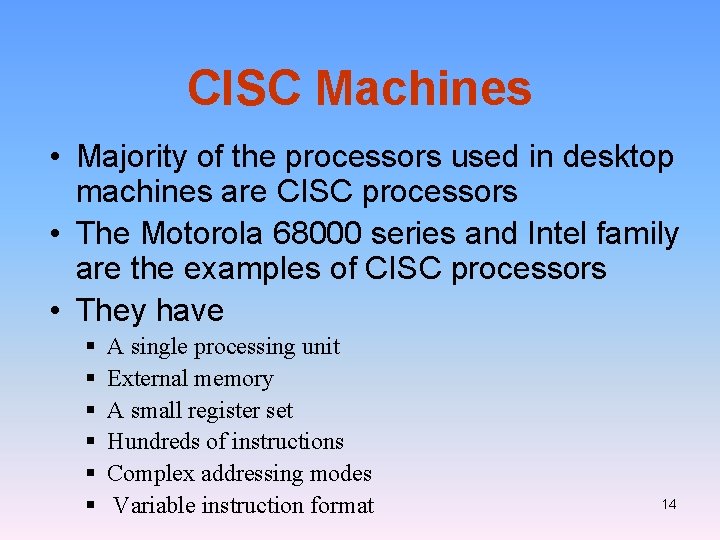

CISC Machines • Majority of the processors used in desktop machines are CISC processors • The Motorola 68000 series and Intel family are the examples of CISC processors • They have § § § A single processing unit External memory A small register set Hundreds of instructions Complex addressing modes Variable instruction format 14

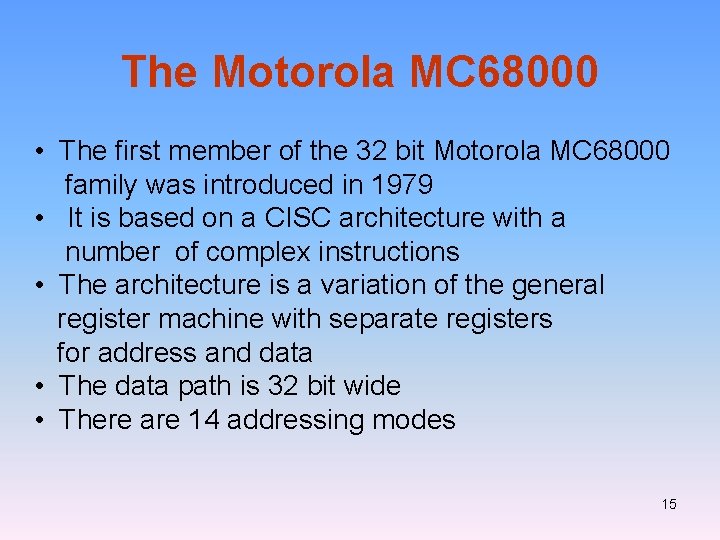

The Motorola MC 68000 • The first member of the 32 bit Motorola MC 68000 family was introduced in 1979 • It is based on a CISC architecture with a number of complex instructions • The architecture is a variation of the general register machine with separate registers for address and data • The data path is 32 bit wide • There are 14 addressing modes 15

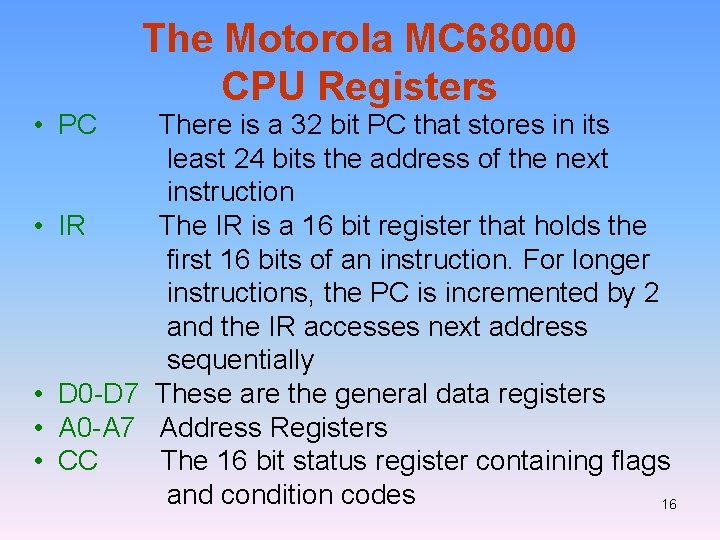

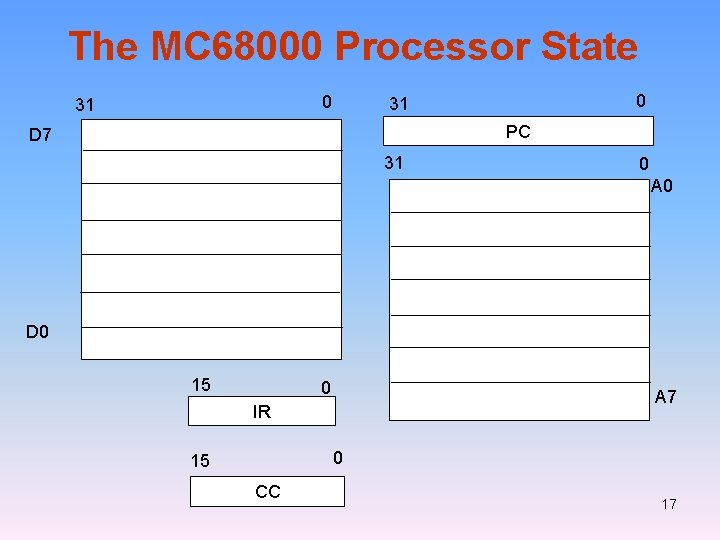

• PC The Motorola MC 68000 CPU Registers There is a 32 bit PC that stores in its least 24 bits the address of the next instruction • IR The IR is a 16 bit register that holds the first 16 bits of an instruction. For longer instructions, the PC is incremented by 2 and the IR accesses next address sequentially • D 0 -D 7 These are the general data registers • A 0 -A 7 Address Registers • CC The 16 bit status register containing flags and condition codes 16

The MC 68000 Processor State 0 31 PC D 7 31 0 A 0 D 0 15 0 A 7 IR 0 15 CC 17

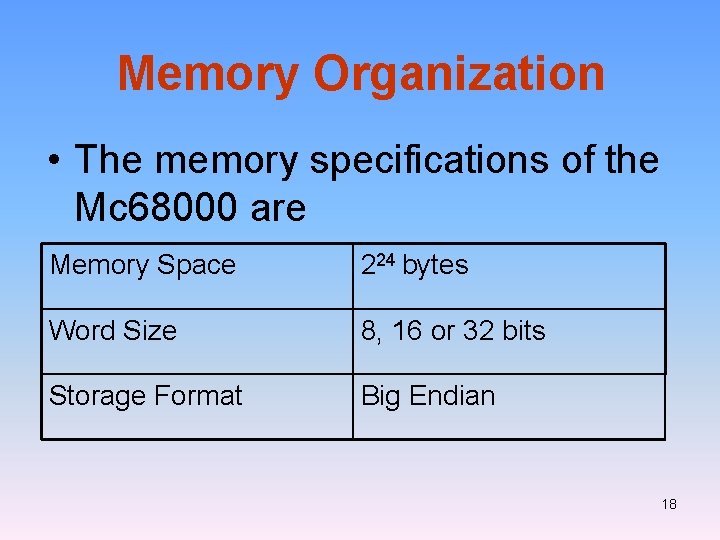

Memory Organization • The memory specifications of the Mc 68000 are Memory Space 224 bytes Word Size 8, 16 or 32 bits Storage Format Big Endian 18

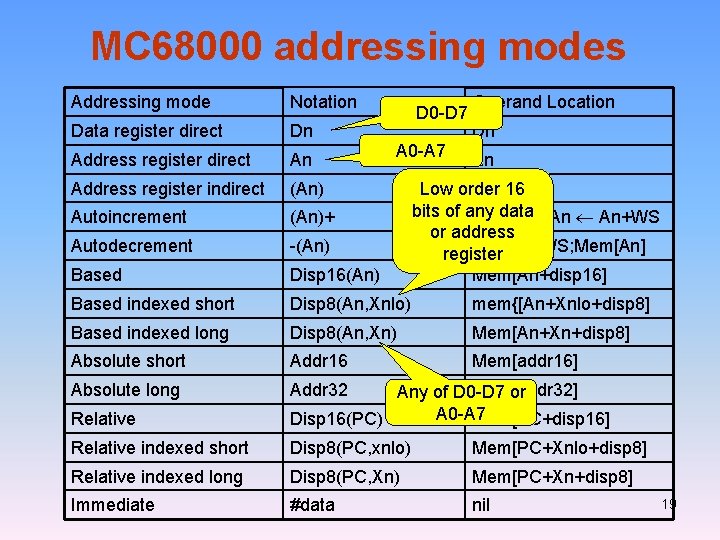

MC 68000 addressing modes Addressing mode Notation Data register direct Dn Address register direct An Address register indirect (An) Autoincrement (An)+ Autodecrement -(An) Based Disp 16(An) Based indexed short Disp 8(An, Xnlo) mem{[An+Xnlo+disp 8] Based indexed long Disp 8(An, Xn) Mem[An+Xn+disp 8] Absolute short Addr 16 Mem[addr 16] Absolute long Addr 32 D 0 -D 7 A 0 -A 7 Operand Location Dn An Mem[An] Low order 16 bits of any data Mem[An]; An An+WS or address An An-WS; Mem[An] register Mem[An+disp 16] Relative Mem[addr 32] Any of D 0 -D 7 or A 0 -A 7 Disp 16(PC) Mem[PC+disp 16] Relative indexed short Disp 8(PC, xnlo) Mem[PC+Xnlo+disp 8] Relative indexed long Disp 8(PC, Xn) Mem[PC+Xn+disp 8] Immediate #data nil 19

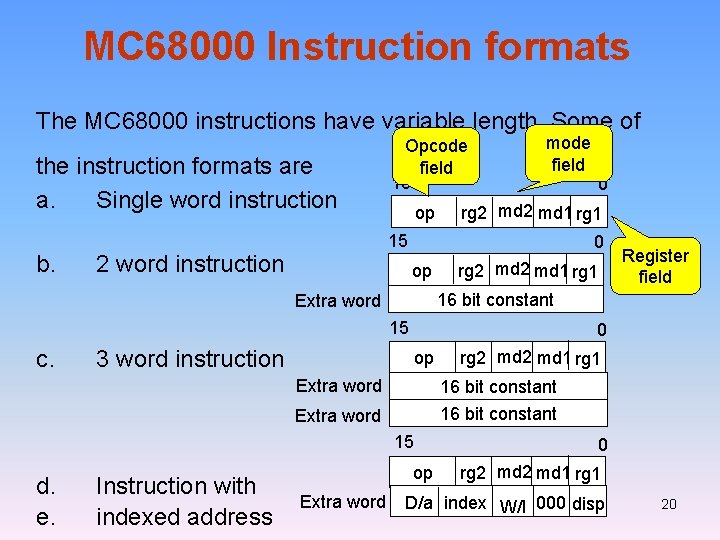

MC 68000 Instruction formats The MC 68000 instructions have variable length. Some of the instruction formats are a. Single word instruction b. Opcode field 15 op mode field rg 2 md 1 rg 1 15 2 word instruction 0 op rg 2 md 1 rg 1 15 3 word instruction 0 op Instruction with indexed address rg 2 md 1 rg 1 Extra word 16 bit constant 15 d. e. op Extra word Register field 16 bit constant Extra word c. 0 0 rg 2 md 1 rg 1 D/a index W/l 000 disp 20

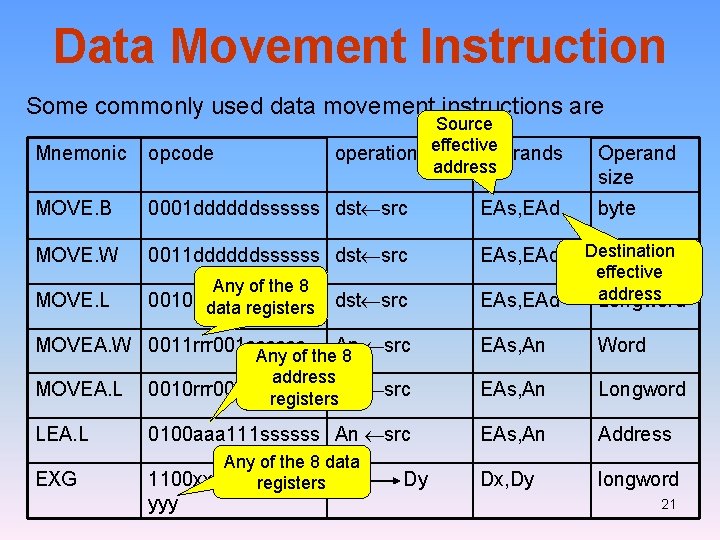

Data Movement Instruction Some commonly used data movement instructions are Source operation effective operands address Mnemonic opcode MOVE. B 0001 ddddddssssss dst src EAs, EAd MOVE. W 0011 ddddddssssss dst src EAs, EAd MOVE. L 0010 ddddddssssss data registers dst src Any of the 8 MOVEA. W 0011 rrr 001 ssssss An src EAs, EAd Operand size byte Destination Word effective address Longword EAs, An Word EAs, An Longword MOVEA. L Any of the 8 address 0010 rrr 001 ssssss registers. An src LEA. L 0100 aaa 111 ssssss An src EAs, An Address EXG Any of the 8 data 1100 xxx 1 mmmmm registers Dx Dx, Dy longword yyy Dy 21

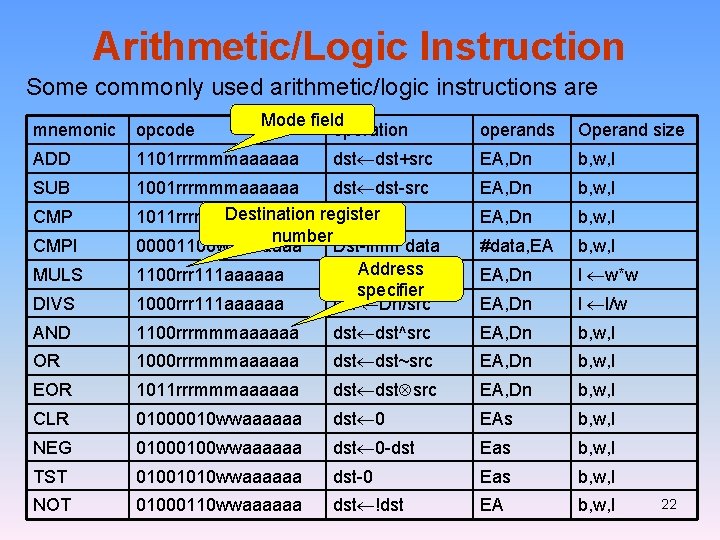

Arithmetic/Logic Instruction Some commonly used arithmetic/logic instructions are Mode field operation mnemonic opcode operands Operand size ADD 1101 rrrmmmaaaaaa EA, Dn b, w, l SUB EA, Dn b, w, l #data, EA b, w, l EA, Dn l w*w DIVS 1001 rrrmmmaaaaaa dst-src Destination register 1011 rrrmmmaaaaaa Dst-src number 00001100 wwaaaaaa Dst-imm data 1100 rrr 111 aaaaaa Dn Address Dn*src specifier 1000 rrr 111 aaaaaa Dn Dn/src EA, Dn l l/w AND 1100 rrrmmmaaaaaa dst^src EA, Dn b, w, l OR 1000 rrrmmmaaaaaa dst~src EA, Dn b, w, l EOR 1011 rrrmmmaaaaaa dst src EA, Dn b, w, l CLR 01000010 wwaaaaaa dst 0 EAs b, w, l NEG 0100 wwaaaaaa dst 0 -dst Eas b, w, l TST 01001010 wwaaaaaa dst-0 Eas b, w, l NOT 01000110 wwaaaaaa dst !dst EA b, w, l CMPI MULS dst+src 22

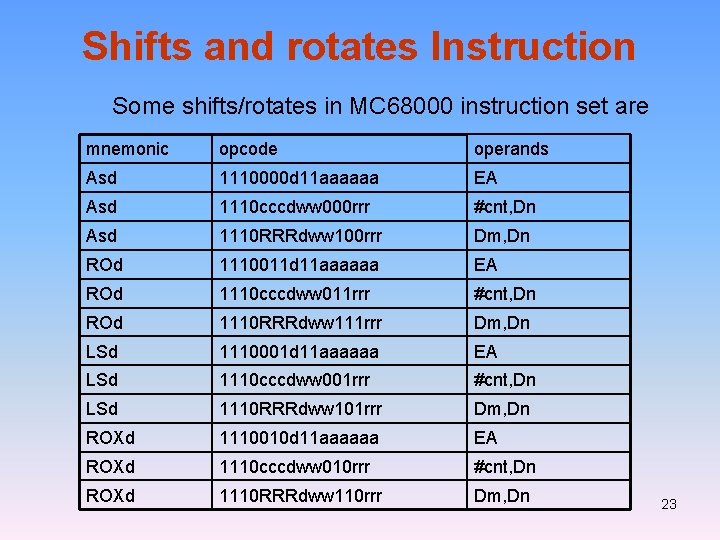

Shifts and rotates Instruction Some shifts/rotates in MC 68000 instruction set are mnemonic opcode operands Asd 1110000 d 11 aaaaaa EA Asd 1110 cccdww 000 rrr #cnt, Dn Asd 1110 RRRdww 100 rrr Dm, Dn ROd 1110011 d 11 aaaaaa EA ROd 1110 cccdww 011 rrr #cnt, Dn ROd 1110 RRRdww 111 rrr Dm, Dn LSd 1110001 d 11 aaaaaa EA LSd 1110 cccdww 001 rrr #cnt, Dn LSd 1110 RRRdww 101 rrr Dm, Dn ROXd 1110010 d 11 aaaaaa EA ROXd 1110 cccdww 010 rrr #cnt, Dn ROXd 1110 RRRdww 110 rrr Dm, Dn 23

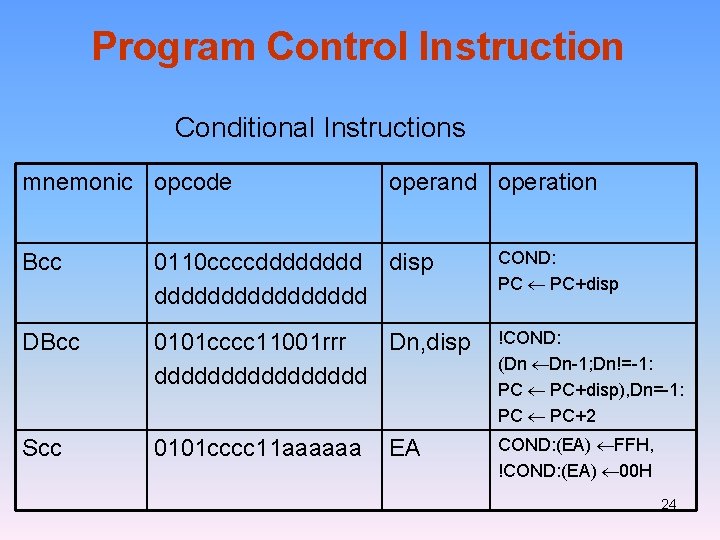

Program Control Instruction Conditional Instructions mnemonic opcode operand operation Bcc 0110 ccccdddd disp dddddddd COND: PC PC+disp DBcc 0101 cccc 11001 rrr Dn, disp dddddddd !COND: (Dn Dn-1; Dn!=-1: PC PC+disp), Dn=-1: PC PC+2 Scc 0101 cccc 11 aaaaaa COND: (EA) FFH, !COND: (EA) 00 H EA 24

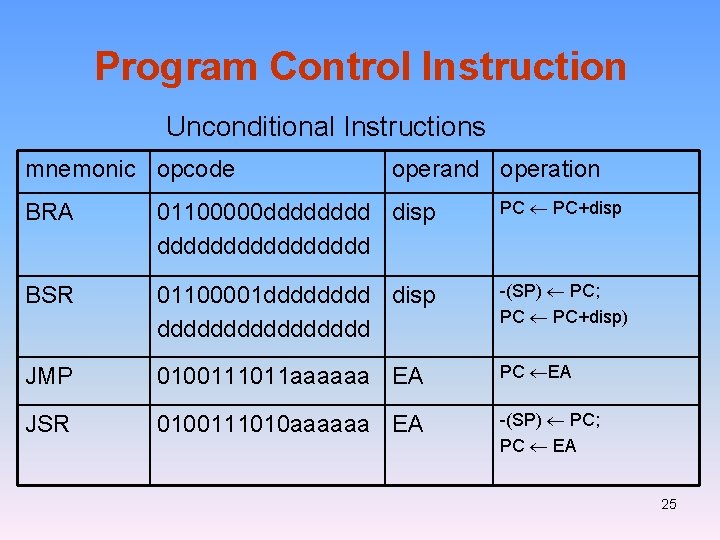

Program Control Instruction Unconditional Instructions mnemonic opcode operand operation BRA 01100000 dddd disp dddddddd PC PC+disp BSR 01100001 dddd disp dddddddd -(SP) PC; PC PC+disp) JMP 0100111011 aaaaaa EA PC EA JSR 0100111010 aaaaaa EA -(SP) PC; PC EA 25

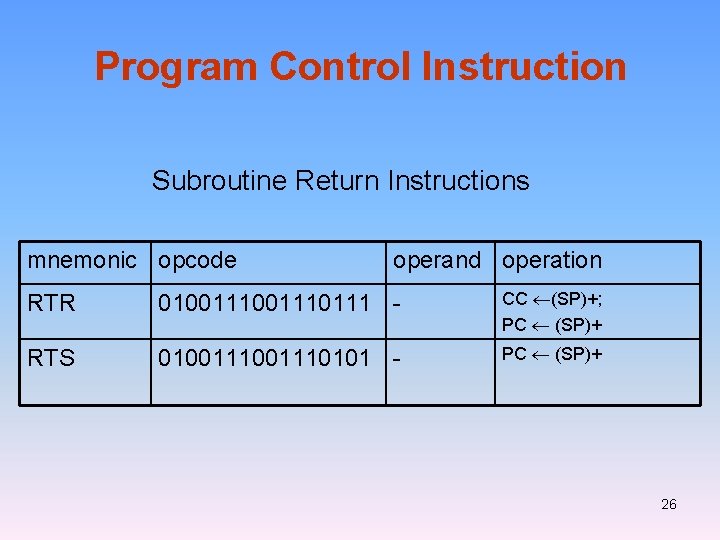

Program Control Instruction Subroutine Return Instructions mnemonic opcode operand operation RTR 01001110111 - CC (SP)+; PC (SP)+ RTS 01001110101 - PC (SP)+ 26

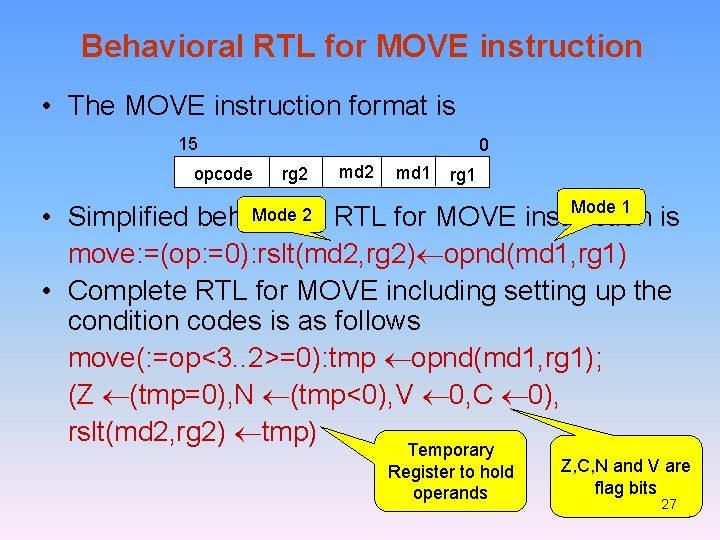

Behavioral RTL for MOVE instruction • The MOVE instruction format is 15 opcode 0 rg 2 md 1 rg 1 Mode 2 RTL for MOVE instruction • Simplified behavioral is move: =(op: =0): rslt(md 2, rg 2) opnd(md 1, rg 1) • Complete RTL for MOVE including setting up the condition codes is as follows move(: =op<3. . 2>=0): tmp opnd(md 1, rg 1); (Z (tmp=0), N (tmp<0), V 0, C 0), rslt(md 2, rg 2) tmp) Temporary Register to hold operands Z, C, N and V are flag bits 27

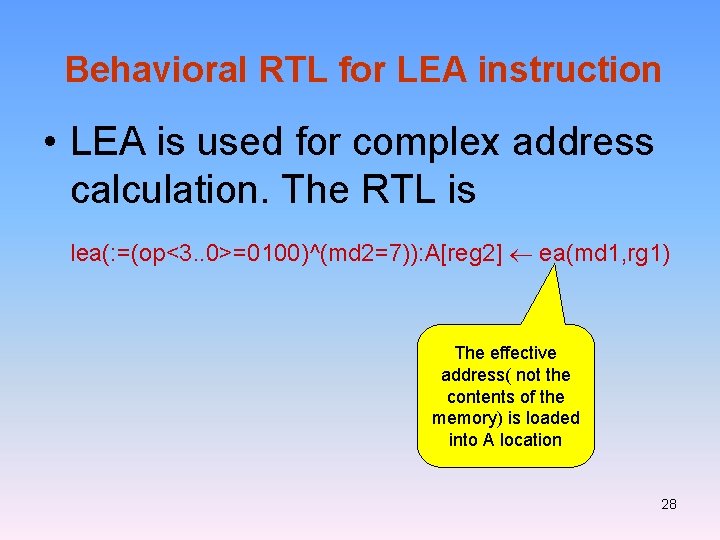

Behavioral RTL for LEA instruction • LEA is used for complex address calculation. The RTL is lea(: =(op<3. . 0>=0100)^(md 2=7)): A[reg 2] ea(md 1, rg 1) The effective address( not the contents of the memory) is loaded into A location 28

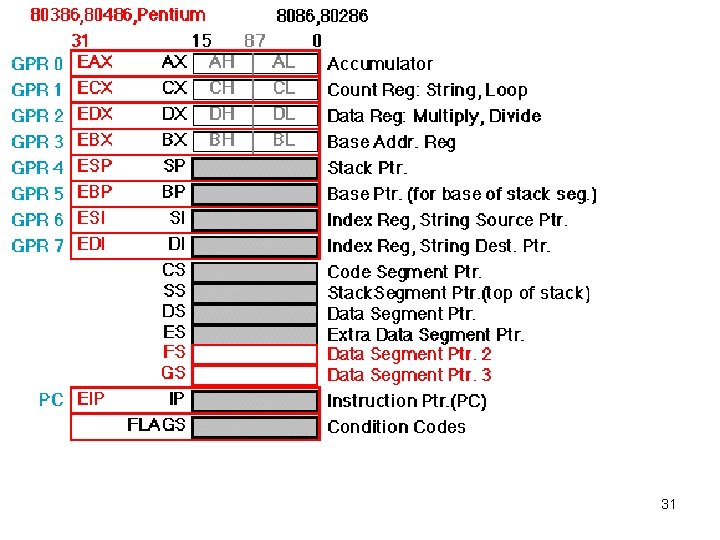

Registers • Data Registers 1. 2. 3. 4. • Accumulators( Ax, EAx) Base Index ( Bx, EBx) Count ( Cx, ECx) Data ( Dx, EDx) Control Registers 1. Instruction pointer( IP, EIP), 2. FLAGS, EFLAGS 29

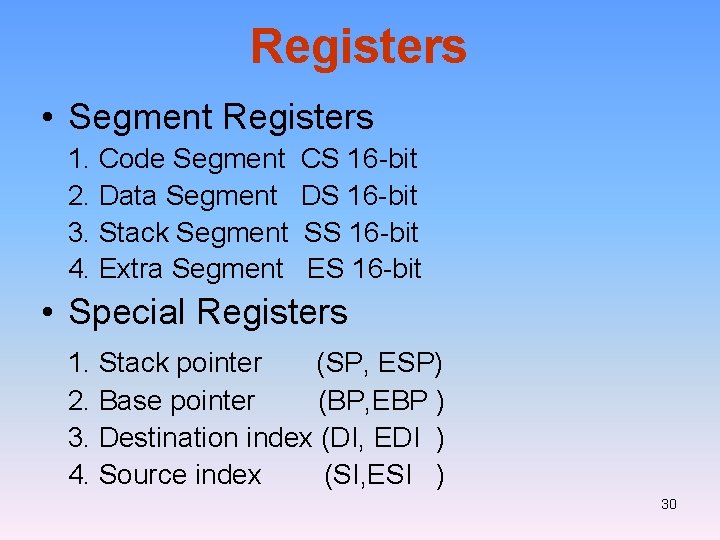

Registers • Segment Registers 1. Code Segment 2. Data Segment 3. Stack Segment 4. Extra Segment CS 16 -bit DS 16 -bit SS 16 -bit ES 16 -bit • Special Registers 1. Stack pointer (SP, ESP) 2. Base pointer (BP, EBP ) 3. Destination index (DI, EDI ) 4. Source index (SI, ESI ) 30

31

Memory Organization • Memory Size: 1 M in 8086 to 4 G in pentium • Soft alignment constraints imply aligned or unaligned storage of words • Little Endian organization 32

Addressing modes Seven addressing modes 1. 2. 3. 4. 5. 6. 7. Register Immediate Direct Register indirect Base plus index Register relative Base relative plus index 33

Instruction Format • Variable length instructions (1 to 17 bytes long) Address displacement Prefix opcode specifier immediate • Two operand machine: One operand must act as both source and destination 34

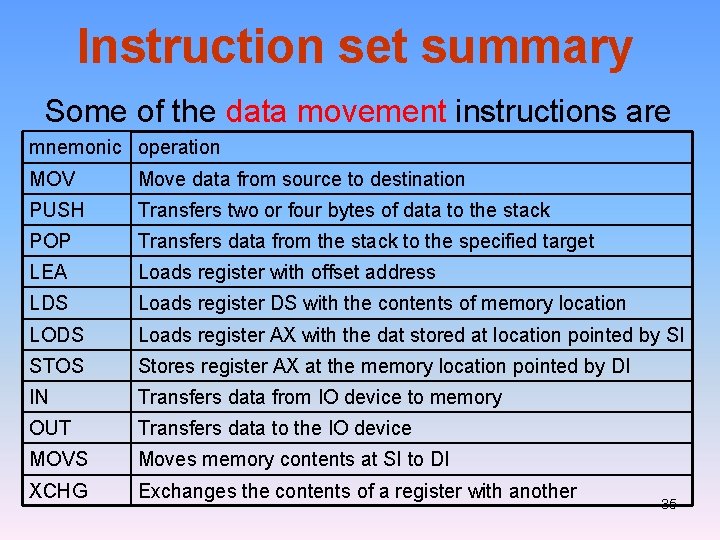

Instruction set summary Some of the data movement instructions are mnemonic operation MOV Move data from source to destination PUSH Transfers two or four bytes of data to the stack POP Transfers data from the stack to the specified target LEA Loads register with offset address LDS Loads register DS with the contents of memory location LODS Loads register AX with the dat stored at location pointed by SI STOS Stores register AX at the memory location pointed by DI IN Transfers data from IO device to memory OUT Transfers data to the IO device MOVS Moves memory contents at SI to DI XCHG Exchanges the contents of a register with another 35

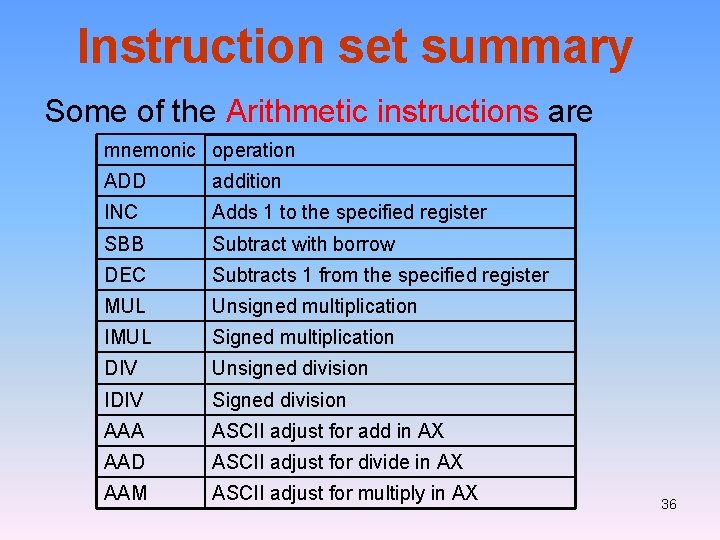

Instruction set summary Some of the Arithmetic instructions are mnemonic operation ADD addition INC Adds 1 to the specified register SBB Subtract with borrow DEC Subtracts 1 from the specified register MUL Unsigned multiplication IMUL Signed multiplication DIV Unsigned division IDIV Signed division AAA ASCII adjust for add in AX AAD ASCII adjust for divide in AX AAM ASCII adjust for multiply in AX 36

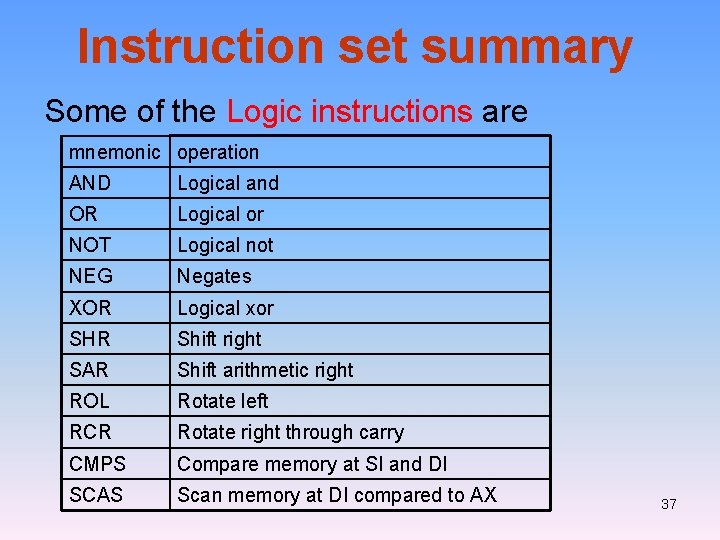

Instruction set summary Some of the Logic instructions are mnemonic operation AND Logical and OR Logical or NOT Logical not NEG Negates XOR Logical xor SHR Shift right SAR Shift arithmetic right ROL Rotate left RCR Rotate right through carry CMPS Compare memory at SI and DI SCAS Scan memory at DI compared to AX 37

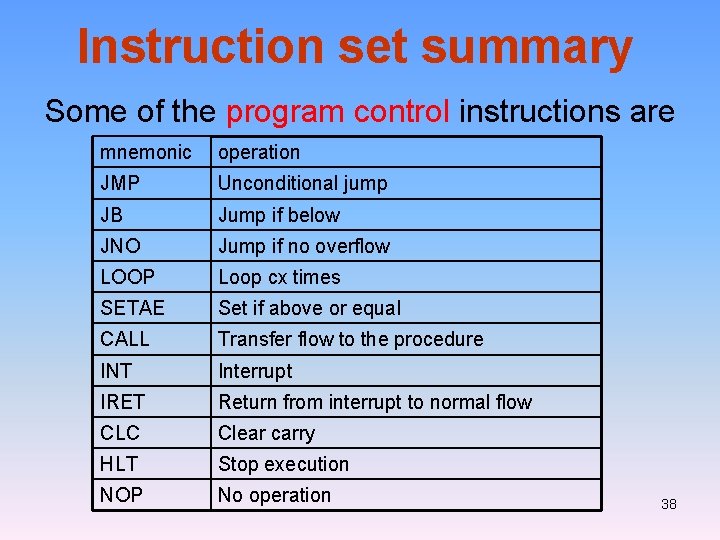

Instruction set summary Some of the program control instructions are mnemonic operation JMP Unconditional jump JB Jump if below JNO Jump if no overflow LOOP Loop cx times SETAE Set if above or equal CALL Transfer flow to the procedure INT Interrupt IRET Return from interrupt to normal flow CLC Clear carry HLT Stop execution NOP No operation 38

- Slides: 38