Mikroraunarski sistemi za rad u realnom vremenu ARM

![Literatura [1] Carol Atack i Alex van Someren, 'The ARM RISC Chip: A Programmers' Literatura [1] Carol Atack i Alex van Someren, 'The ARM RISC Chip: A Programmers'](https://slidetodoc.com/presentation_image_h2/ae170a42e33f8f354110761a5a3312a6/image-34.jpg)

- Slides: 35

Mikroračunarski sistemi za rad u realnom vremenu „ARM mikrokontroleri“ Predavač: Dr Predrag Teodorović

Istorija kompanije ARM – „Acorn RISC Machine“, su procesorska jezgra koja potiču od britanske kompanije Acorn, osnovane 1978 Acorn je prodavao svoje BBC Micro platforme bazirane na 8 -bitnom 6052 procesoru i stekao na taj način veliki udeo u britanskoj kompjuterskoj industriji Napredak na tržištu je tražio nove 16 -bitne i 32 -bitne procesore i ljudi iz Acorna su testiraju trenutno dostupne čipove za svoju novu platformu

Pošto nijedan ne zadovoljava njihova očekivanja, rešavaju da dizajniraju svoj procesor Glavna ideja je bila da se zadrže mnoge osnove 6052 procesora, ali u 32 -bitnom RISC okruženju, integrisanog u malom čipu jeftine izrade i lakog testiranja Aprila 1985. svetlost dana je ugledao prvi ARM procesor, odnosno ARM 1. Imao je manje od 25 000 tranzistora, ali je ispunjavao sve uslove koje su dizajneri zacrtali Prvi komercijalni ARM procesor je ipak bio ARM 2, 1986. godine, jer su dizajneri smatrali da se set instrukcija ARM 1 procesora može poboljšati (dodate su Muliply i Multiply and Accumulate instrukcije)

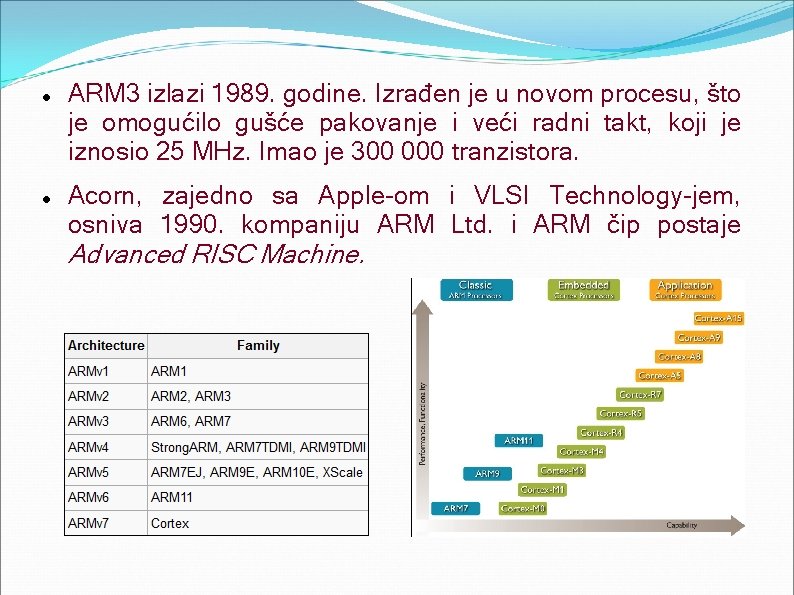

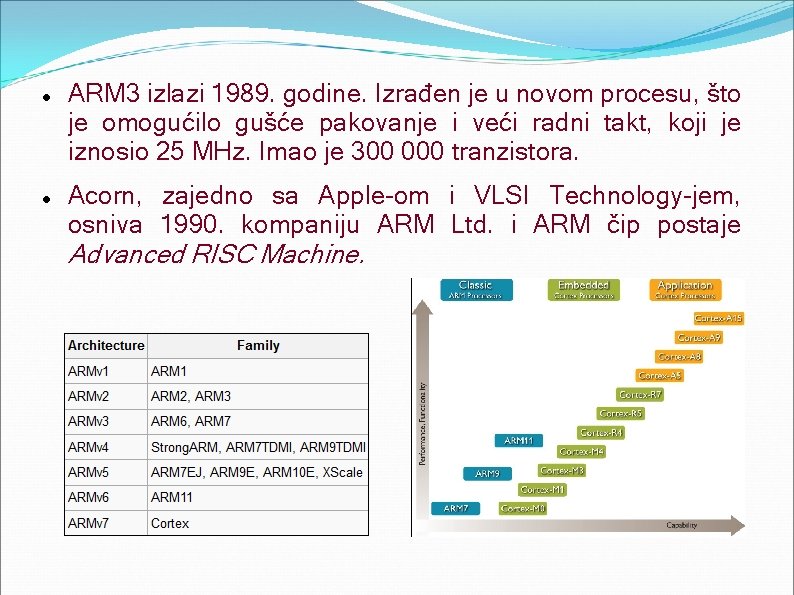

ARM 3 izlazi 1989. godine. Izrađen je u novom procesu, što je omogućilo gušće pakovanje i veći radni takt, koji je iznosio 25 MHz. Imao je 300 000 tranzistora. Acorn, zajedno sa Apple-om i VLSI Technology-jem, osniva 1990. kompaniju ARM Ltd. i ARM čip postaje Advanced RISC Machine.

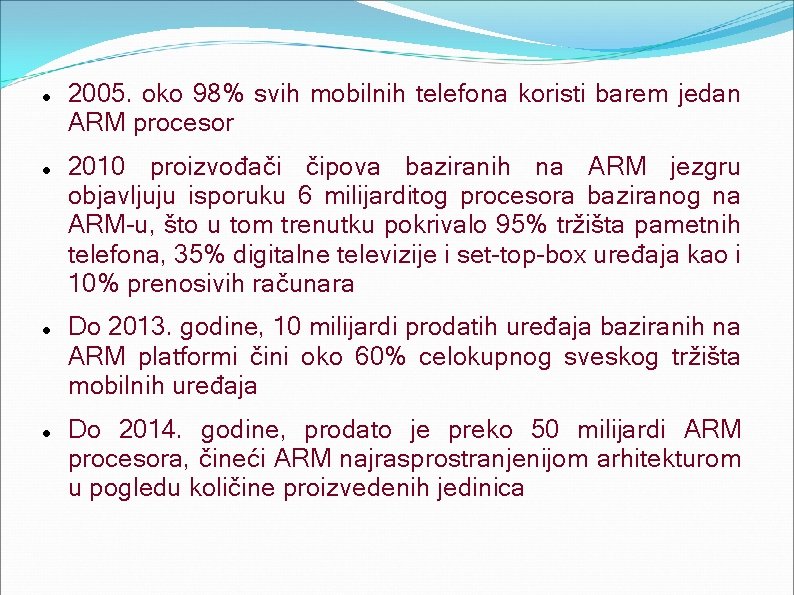

2005. oko 98% svih mobilnih telefona koristi barem jedan ARM procesor 2010 proizvođači čipova baziranih na ARM jezgru objavljuju isporuku 6 milijarditog procesora baziranog na ARM-u, što u tom trenutku pokrivalo 95% tržišta pametnih telefona, 35% digitalne televizije i set-top-box uređaja kao i 10% prenosivih računara Do 2013. godine, 10 milijardi prodatih uređaja baziranih na ARM platformi čini oko 60% celokupnog sveskog tržišta mobilnih uređaja Do 2014. godine, prodato je preko 50 milijardi ARM procesora, čineći ARM najrasprostranjenijom arhitekturom u pogledu količine proizvedenih jedinica

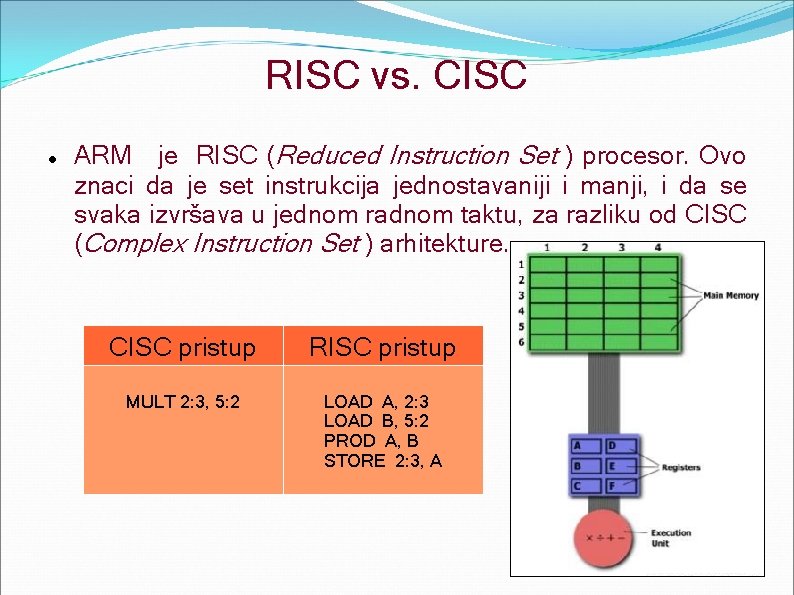

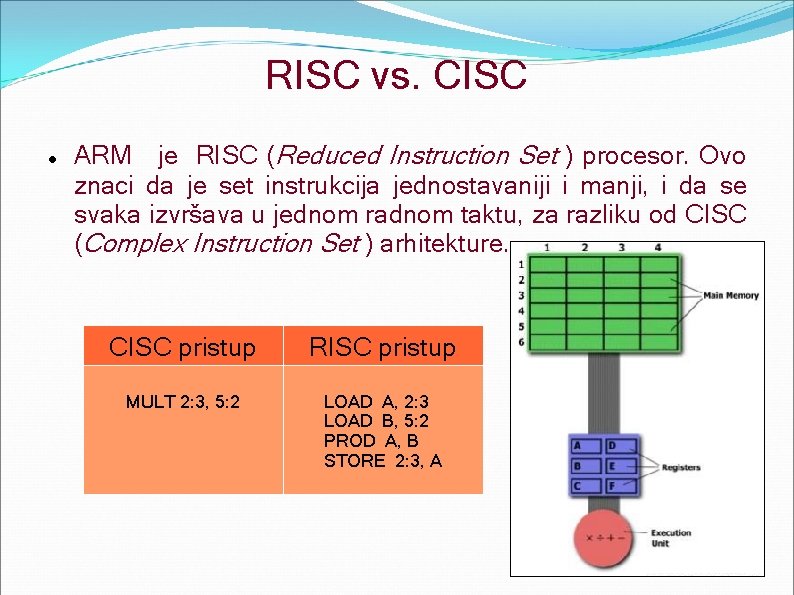

RISC vs. CISC ARM je RISC (Reduced Instruction Set ) procesor. Ovo znaci da je set instrukcija jednostavaniji i manji, i da se svaka izvršava u jednom radnom taktu, za razliku od CISC (Complex Instruction Set ) arhitekture. CISC pristup RISC pristup MULT 2: 3, 5: 2 LOAD A, 2: 3 LOAD B, 5: 2 PROD A, B STORE 2: 3, A

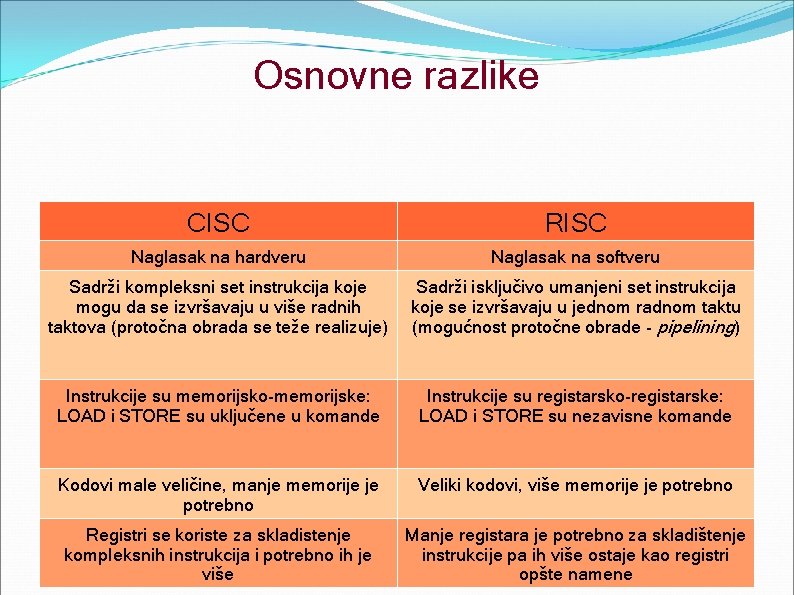

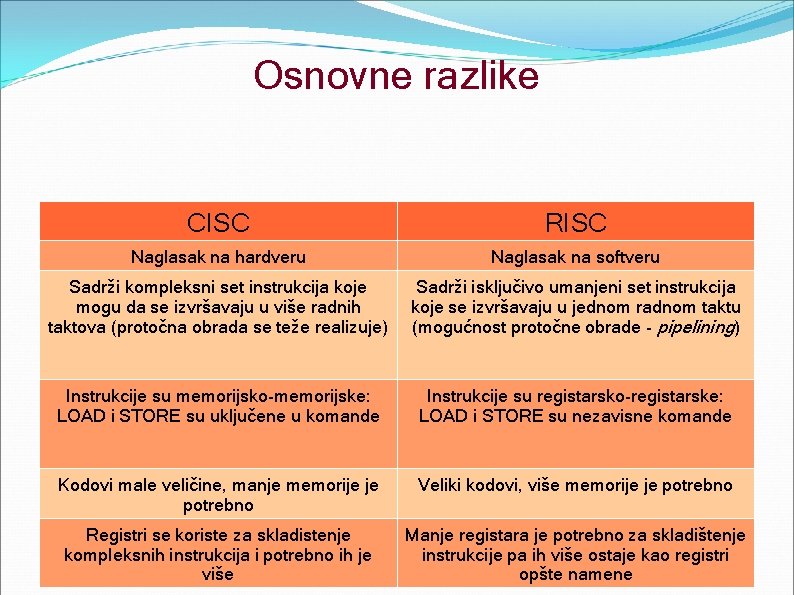

Osnovne razlike CISC RISC Naglasak na hardveru Naglasak na softveru Sadrži kompleksni set instrukcija koje mogu da se izvršavaju u više radnih taktova (protočna obrada se teže realizuje) Sadrži isključivo umanjeni set instrukcija koje se izvršavaju u jednom radnom taktu (mogućnost protočne obrade - pipelining) Instrukcije su memorijsko-memorijske: LOAD i STORE su uključene u komande Instrukcije su registarsko-registarske: LOAD i STORE su nezavisne komande Kodovi male veličine, manje memorije je potrebno Veliki kodovi, više memorije je potrebno Registri se koriste za skladistenje kompleksnih instrukcija i potrebno ih je više Manje registara je potrebno za skladištenje instrukcije pa ih više ostaje kao registri opšte namene

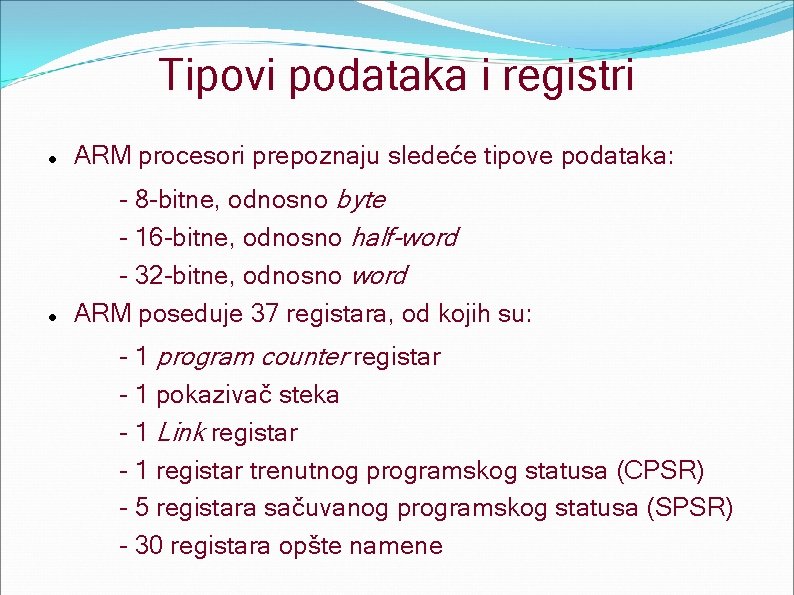

Tipovi podataka i registri ARM procesori prepoznaju sledeće tipove podataka: - 8 -bitne, odnosno byte - 16 -bitne, odnosno half-word - 32 -bitne, odnosno word ARM poseduje 37 registara, od kojih su: - 1 program counter registar - 1 pokazivač steka - 1 Link registar - 1 registar trenutnog programskog statusa (CPSR) - 5 registara sačuvanog programskog statusa (SPSR) - 30 registara opšte namene

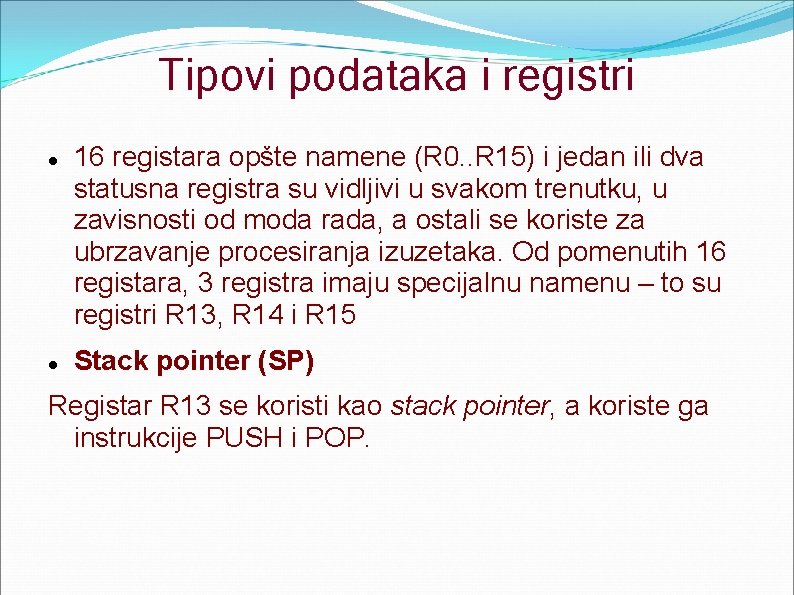

Tipovi podataka i registri 16 registara opšte namene (R 0. . R 15) i jedan ili dva statusna registra su vidljivi u svakom trenutku, u zavisnosti od moda rada, a ostali se koriste za ubrzavanje procesiranja izuzetaka. Od pomenutih 16 registara, 3 registra imaju specijalnu namenu – to su registri R 13, R 14 i R 15 Stack pointer (SP) Registar R 13 se koristi kao stack pointer, a koriste ga instrukcije PUSH i POP.

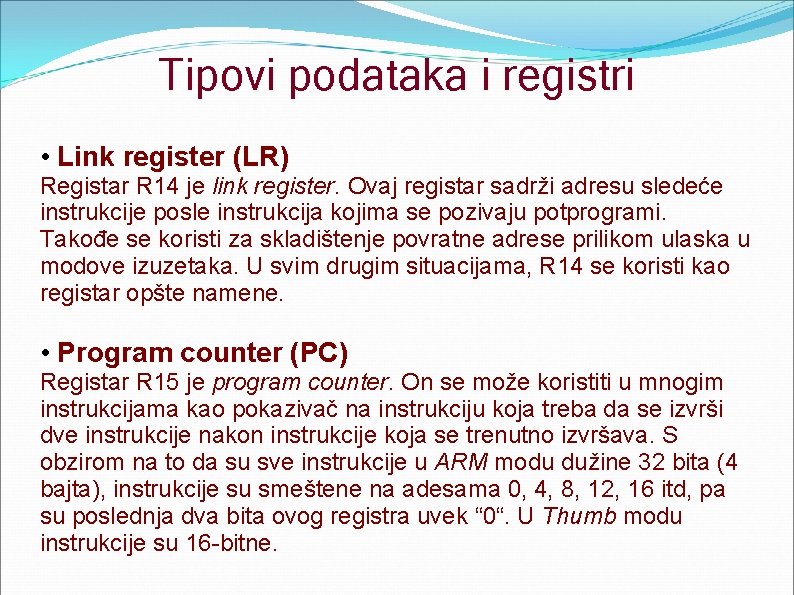

Tipovi podataka i registri • Link register (LR) Registar R 14 je link register. Ovaj registar sadrži adresu sledeće instrukcije posle instrukcija kojima se pozivaju potprogrami. Takođe se koristi za skladištenje povratne adrese prilikom ulaska u modove izuzetaka. U svim drugim situacijama, R 14 se koristi kao registar opšte namene. • Program counter (PC) Registar R 15 je program counter. On se može koristiti u mnogim instrukcijama kao pokazivač na instrukciju koja treba da se izvrši dve instrukcije nakon instrukcije koja se trenutno izvršava. S obzirom na to da su sve instrukcije u ARM modu dužine 32 bita (4 bajta), instrukcije su smeštene na adesama 0, 4, 8, 12, 16 itd, pa su poslednja dva bita ovog registra uvek “ 0“. U Thumb modu instrukcije su 16 -bitne.

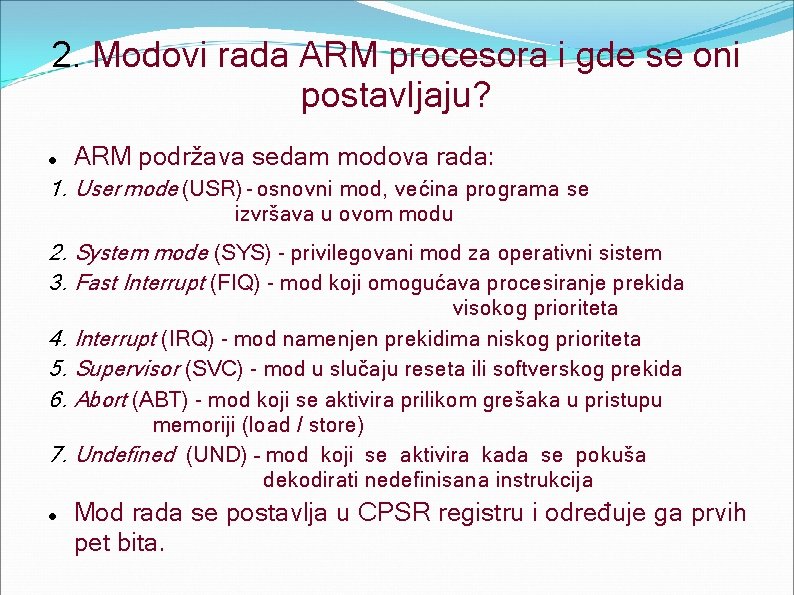

Modovi rada ARM podržava sedam modova rada: 1. User mode (USR) - osnovni mod, većina programa se izvršava u ovom modu 2. System mode (SYS) - privilegovani mod za operativni sistem 3. Fast Interrupt (FIQ) - mod koji omogućava procesiranje prekida 4. 5. 6. 7. visokog prioriteta Interrupt (IRQ) - mod namenjen prekidima niskog prioriteta Supervisor (SVC) - mod u slučaju reseta ili softverskog prekida Abort (ABT) - mod koji se aktivira prilikom grešaka u pristupu memoriji (load / store) Undefined (UND) – mod koji se aktivira kada se pokuša dekodirati nedefinisana instrukcija

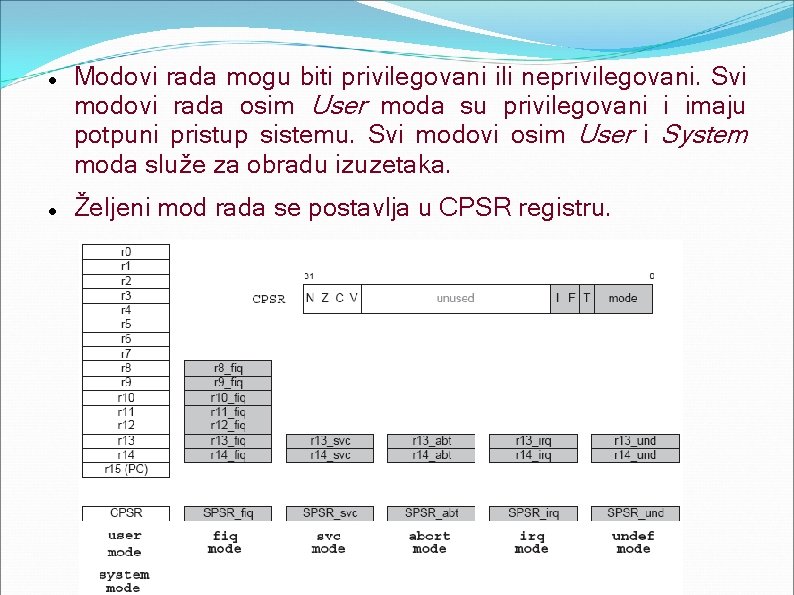

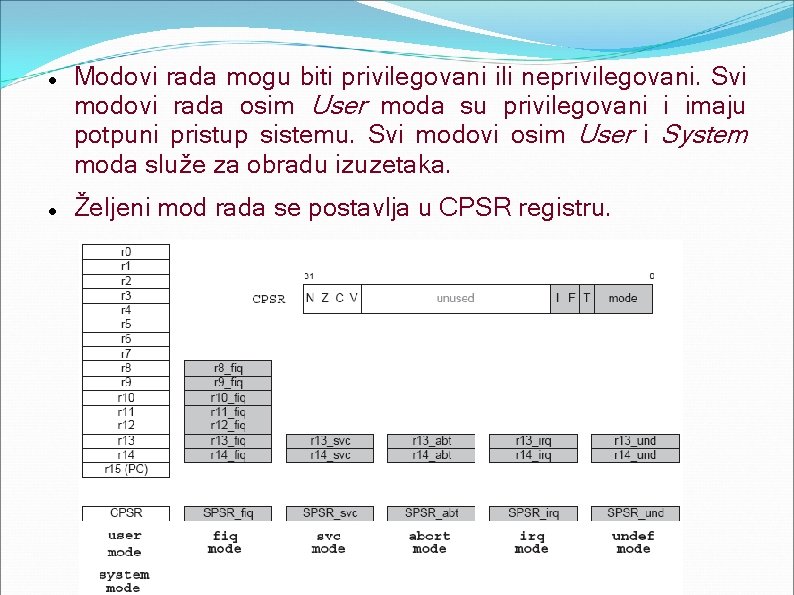

Modovi rada mogu biti privilegovani ili neprivilegovani. Svi modovi rada osim User moda su privilegovani i imaju potpuni pristup sistemu. Svi modovi osim User i System moda služe za obradu izuzetaka. Željeni mod rada se postavlja u CPSR registru.

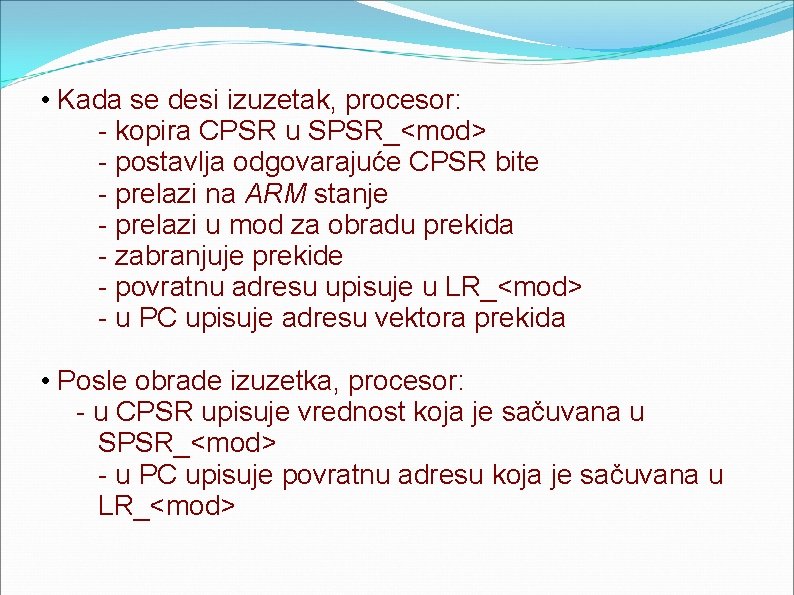

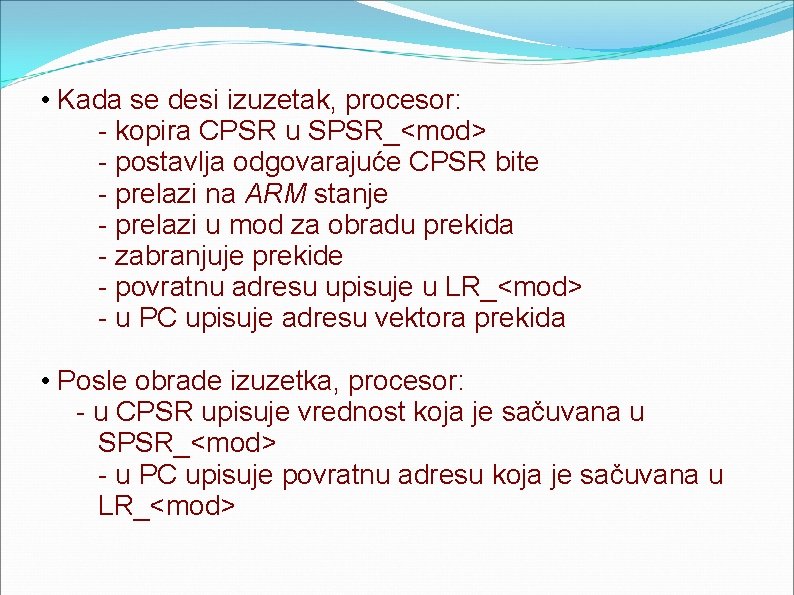

• Kada se desi izuzetak, procesor: - kopira CPSR u SPSR_<mod> - postavlja odgovarajuće CPSR bite - prelazi na ARM stanje - prelazi u mod za obradu prekida - zabranjuje prekide - povratnu adresu upisuje u LR_<mod> - u PC upisuje adresu vektora prekida • Posle obrade izuzetka, procesor: - u CPSR upisuje vrednost koja je sačuvana u SPSR_<mod> - u PC upisuje povratnu adresu koja je sačuvana u LR_<mod>

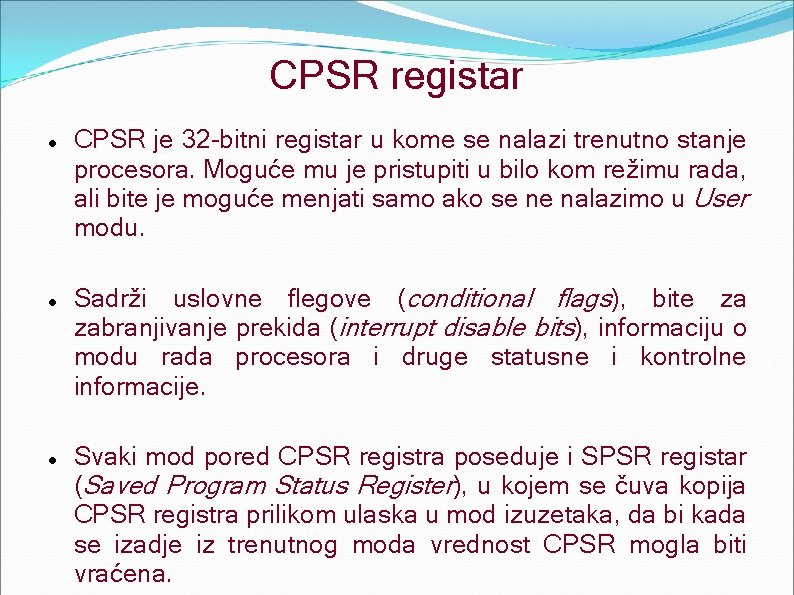

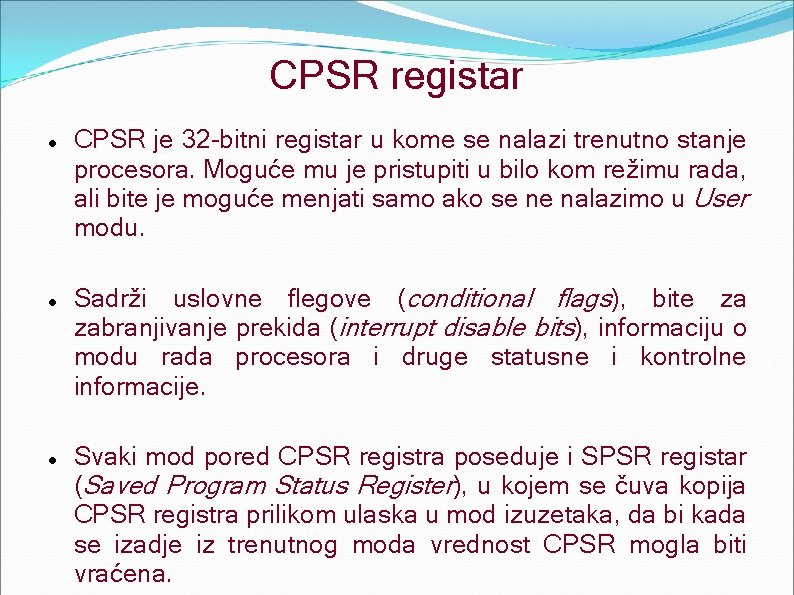

CPSR registar CPSR je 32 -bitni registar u kome se nalazi trenutno stanje procesora. Moguće mu je pristupiti u bilo kom režimu rada, ali bite je moguće menjati samo ako se ne nalazimo u User modu. Sadrži uslovne flegove (conditional flags), bite za zabranjivanje prekida (interrupt disable bits), informaciju o modu rada procesora i druge statusne i kontrolne informacije. Svaki mod pored CPSR registra poseduje i SPSR registar (Saved Program Status Register), u kojem se čuva kopija CPSR registra prilikom ulaska u mod izuzetaka, da bi kada se izadje iz trenutnog moda vrednost CPSR mogla biti vraćena.

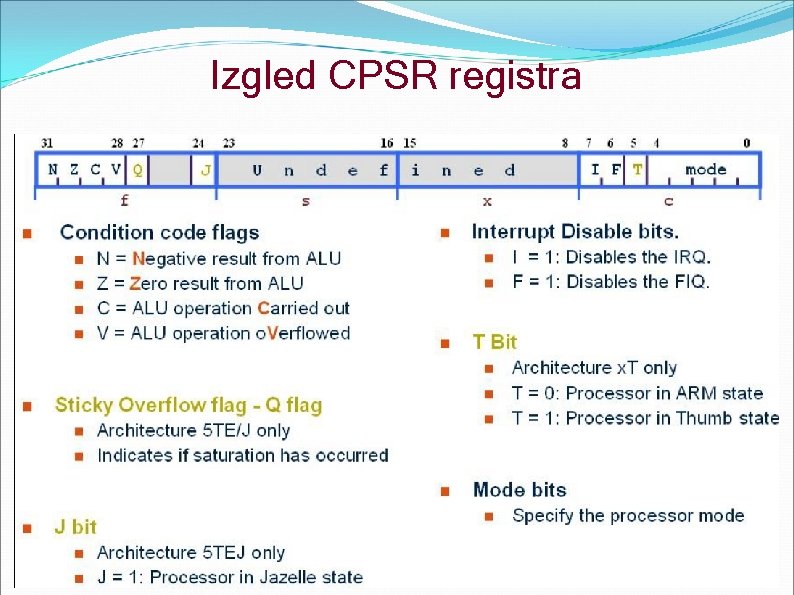

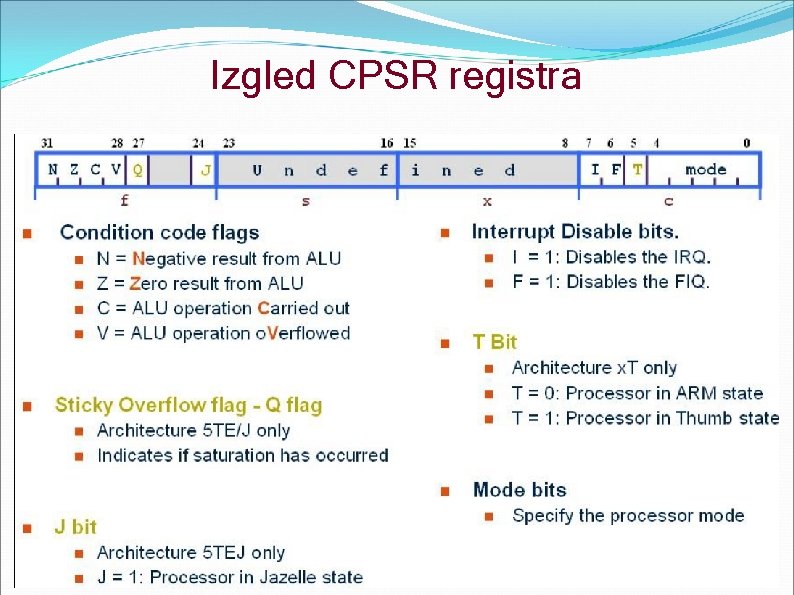

Izgled CPSR registra

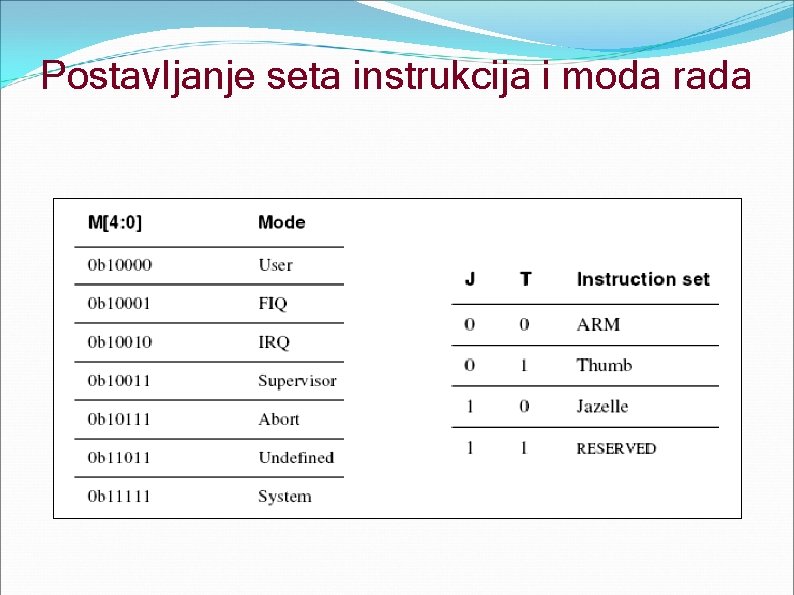

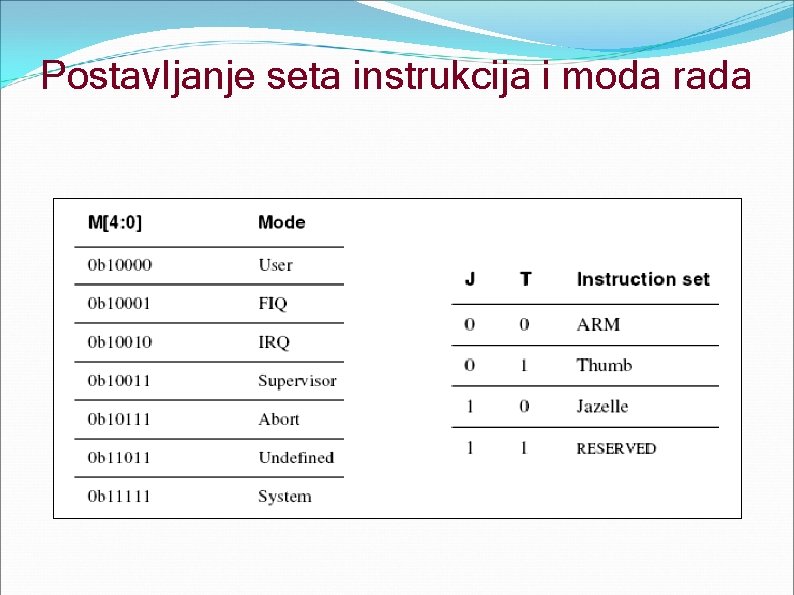

Postavljanje seta instrukcija i moda rada

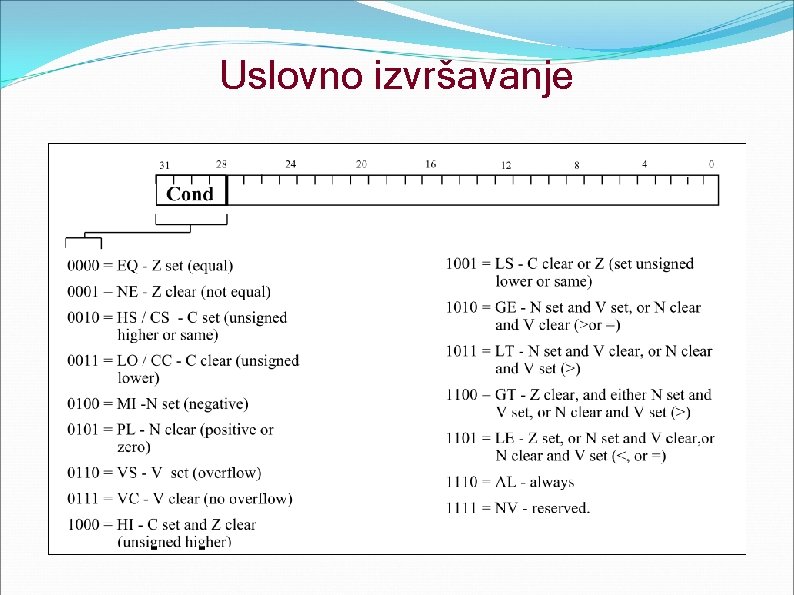

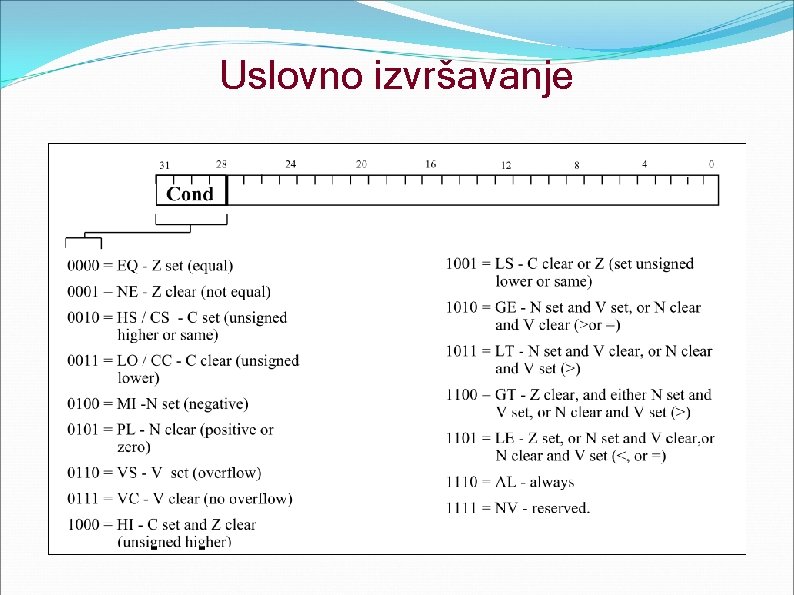

Set instrukcija ARM procesora Većina ARM procesora podržava dva seta instrukcija: a) 32 -bitni ARM set instrukcija b) 16 -bitni Thumb set instrukcija Osim ova dva, kod nekih novijih ARM procesora, Jazelle omogućava HW izvršavanje Java bytecode-a ARM set instrukcija je osnovni set instrukcija procesora i koristi se u aplikacijama koje zahtevaju visoke performanse, ili za rukovanje hardverskim izuzecima poput prekida i startovanje procesora. Ove komande su raspoređene kao 4 bajta. ARM instrukcije takođe omogućavaju uslovno izvršavanje, u zavisnosti od vrednosti N, Z, C i V bita CPSR registra. Ova osobina povećava gustinu koda i poboljšava performanse.

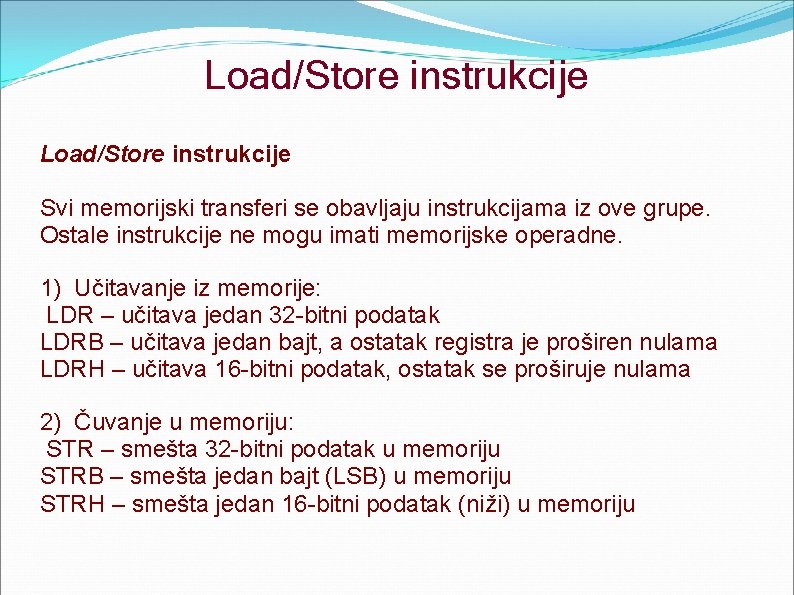

Load/Store instrukcije Svi memorijski transferi se obavljaju instrukcijama iz ove grupe. Ostale instrukcije ne mogu imati memorijske operadne. 1) Učitavanje iz memorije: LDR – učitava jedan 32 -bitni podatak LDRB – učitava jedan bajt, a ostatak registra je proširen nulama LDRH – učitava 16 -bitni podatak, ostatak se proširuje nulama 2) Čuvanje u memoriju: STR – smešta 32 -bitni podatak u memoriju STRB – smešta jedan bajt (LSB) u memoriju STRH – smešta jedan 16 -bitni podatak (niži) u memoriju

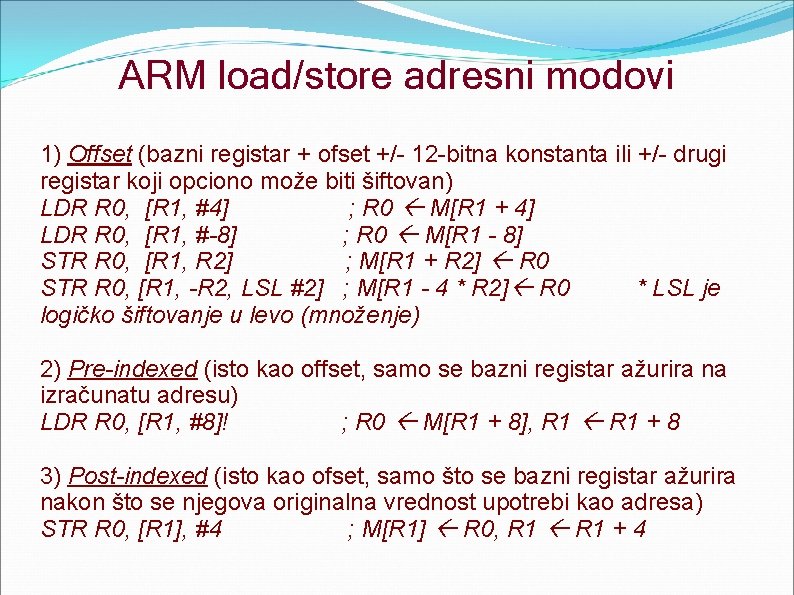

ARM load/store adresni modovi 1) Offset (bazni registar + ofset +/- 12 -bitna konstanta ili +/- drugi registar koji opciono može biti šiftovan) LDR R 0, [R 1, #4] ; R 0 M[R 1 + 4] LDR R 0, [R 1, #-8] ; R 0 M[R 1 - 8] STR R 0, [R 1, R 2] ; M[R 1 + R 2] R 0 STR R 0, [R 1, -R 2, LSL #2] ; M[R 1 - 4 * R 2] R 0 * LSL je logičko šiftovanje u levo (množenje) 2) Pre-indexed (isto kao offset, samo se bazni registar ažurira na izračunatu adresu) LDR R 0, [R 1, #8]! ; R 0 M[R 1 + 8], R 1 + 8 3) Post-indexed (isto kao ofset, samo što se bazni registar ažurira nakon što se njegova originalna vrednost upotrebi kao adresa) STR R 0, [R 1], #4 ; M[R 1] R 0, R 1 + 4

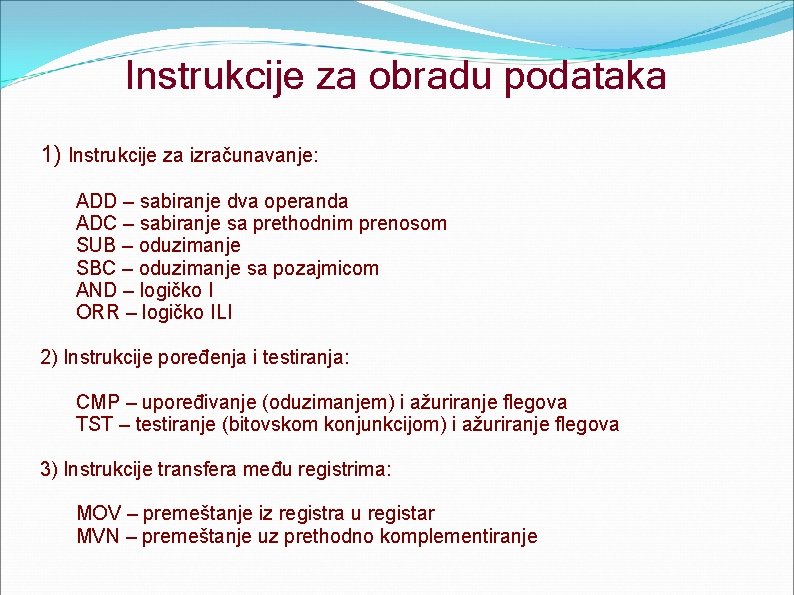

Instrukcije za obradu podataka 1) Instrukcije za izračunavanje: ADD – sabiranje dva operanda ADC – sabiranje sa prethodnim prenosom SUB – oduzimanje SBC – oduzimanje sa pozajmicom AND – logičko I ORR – logičko ILI 2) Instrukcije poređenja i testiranja: CMP – upoređivanje (oduzimanjem) i ažuriranje flegova TST – testiranje (bitovskom konjunkcijom) i ažuriranje flegova 3) Instrukcije transfera među registrima: MOV – premeštanje iz registra u registar MVN – premeštanje uz prethodno komplementiranje

Uslovno izvršavanje

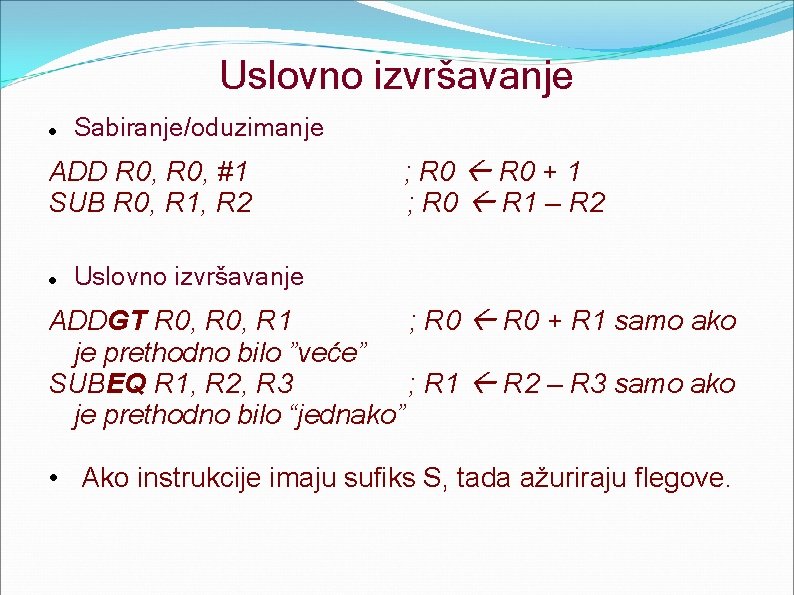

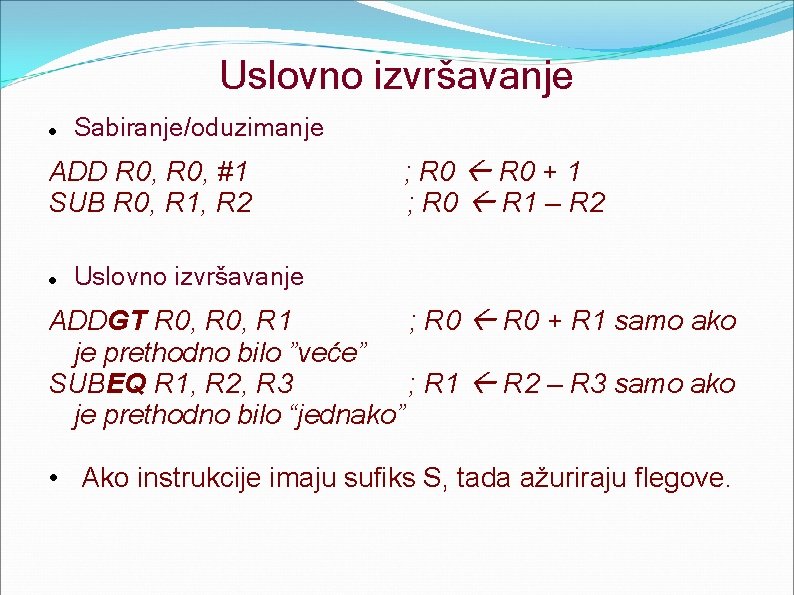

Uslovno izvršavanje Sabiranje/oduzimanje ADD R 0, #1 SUB R 0, R 1, R 2 ; R 0 + 1 ; R 0 R 1 – R 2 Uslovno izvršavanje ADDGT R 0, R 1 ; R 0 + R 1 samo ako je prethodno bilo ”veće” SUBEQ R 1, R 2, R 3 ; R 1 R 2 – R 3 samo ako je prethodno bilo “jednako” • Ako instrukcije imaju sufiks S, tada ažuriraju flegove.

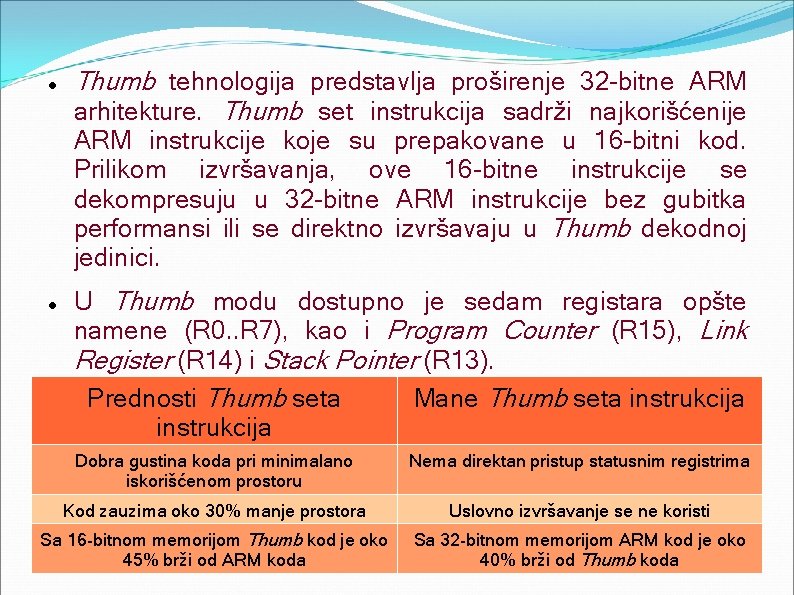

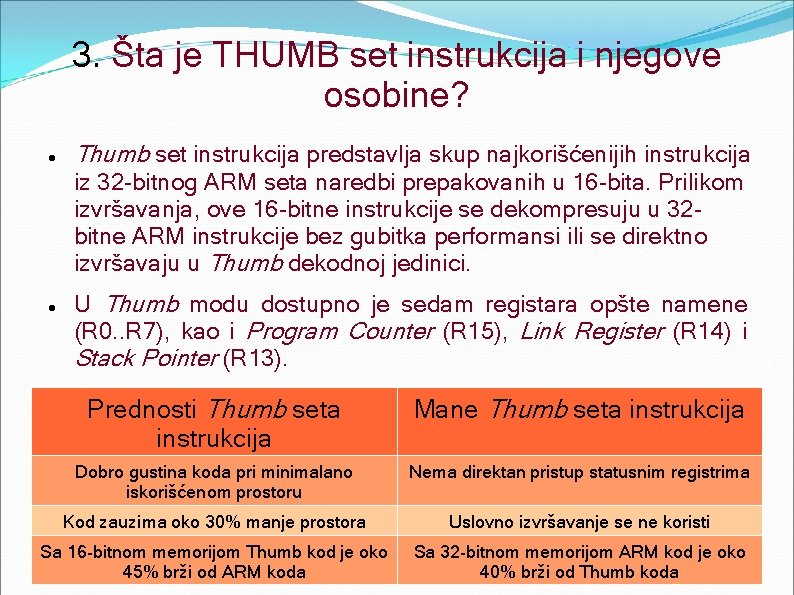

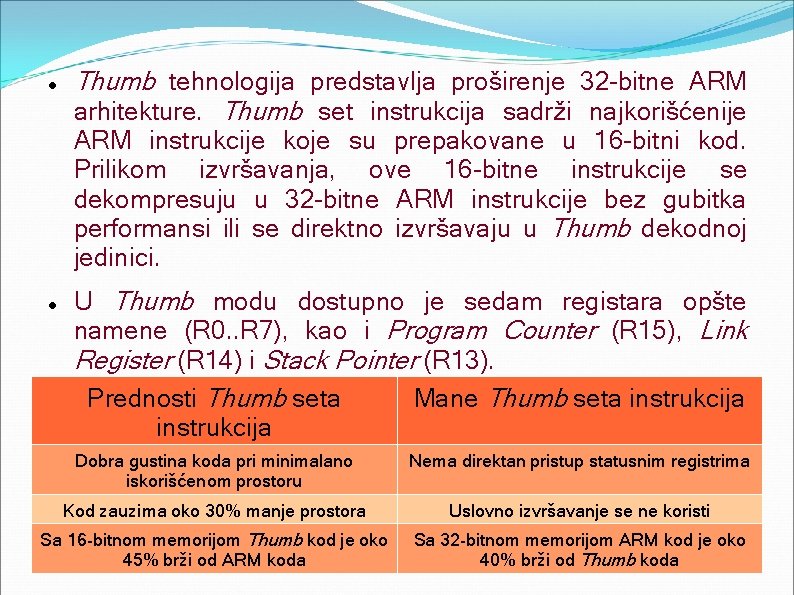

Thumb tehnologija predstavlja proširenje 32 -bitne ARM arhitekture. Thumb set instrukcija sadrži najkorišćenije ARM instrukcije koje su prepakovane u 16 -bitni kod. Prilikom izvršavanja, ove 16 -bitne instrukcije se dekompresuju u 32 -bitne ARM instrukcije bez gubitka performansi ili se direktno izvršavaju u Thumb dekodnoj jedinici. U Thumb modu dostupno je sedam registara opšte namene (R 0. . R 7), kao i Program Counter (R 15), Link Register (R 14) i Stack Pointer (R 13). Prednosti Thumb seta Mane Thumb seta instrukcija Dobra gustina koda pri minimalano iskorišćenom prostoru Nema direktan pristup statusnim registrima Kod zauzima oko 30% manje prostora Uslovno izvršavanje se ne koristi Sa 16 -bitnom memorijom Thumb kod je oko 45% brži od ARM koda Sa 32 -bitnom memorijom ARM kod je oko 40% brži od Thumb koda

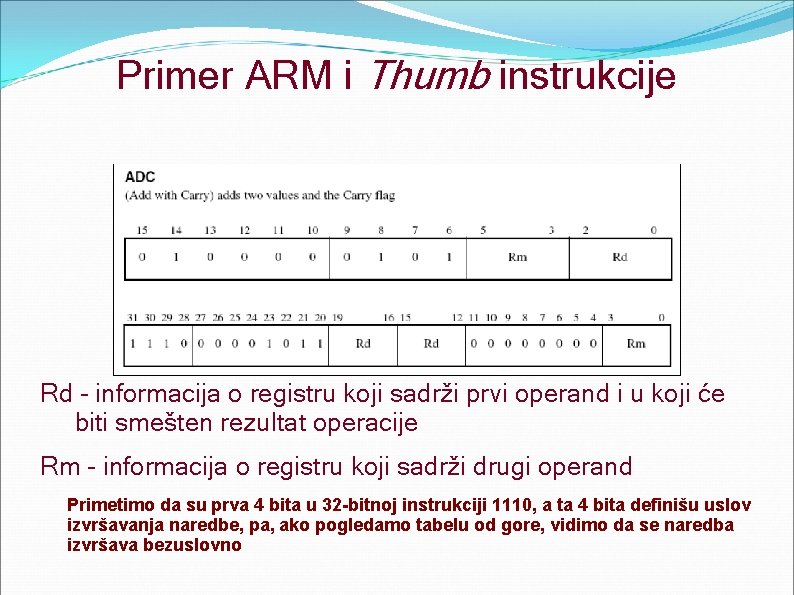

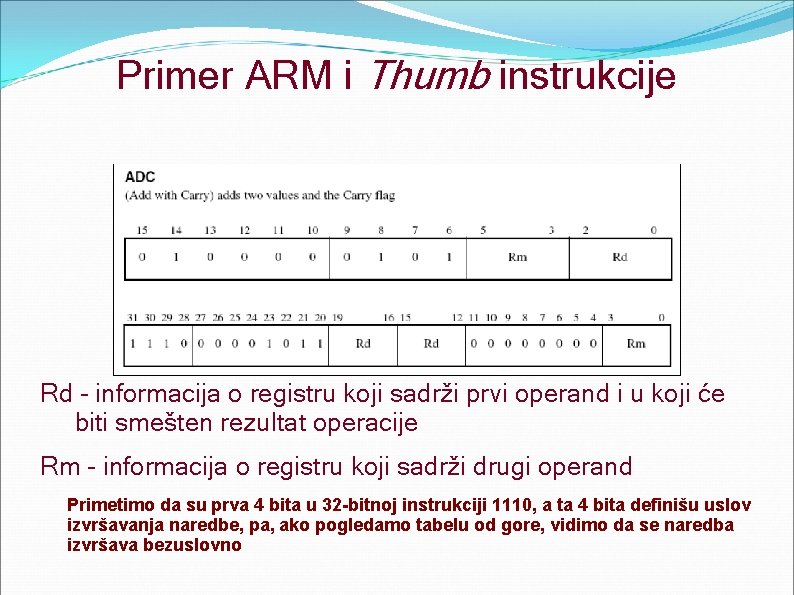

Primer ARM i Thumb instrukcije Rd - informacija o registru koji sadrži prvi operand i u koji će biti smešten rezultat operacije Rm - informacija o registru koji sadrži drugi operand Primetimo da su prva 4 bita u 32 -bitnoj instrukciji 1110, a ta 4 bita definišu uslov izvršavanja naredbe, pa, ako pogledamo tabelu od gore, vidimo da se naredba izvršava bezuslovno

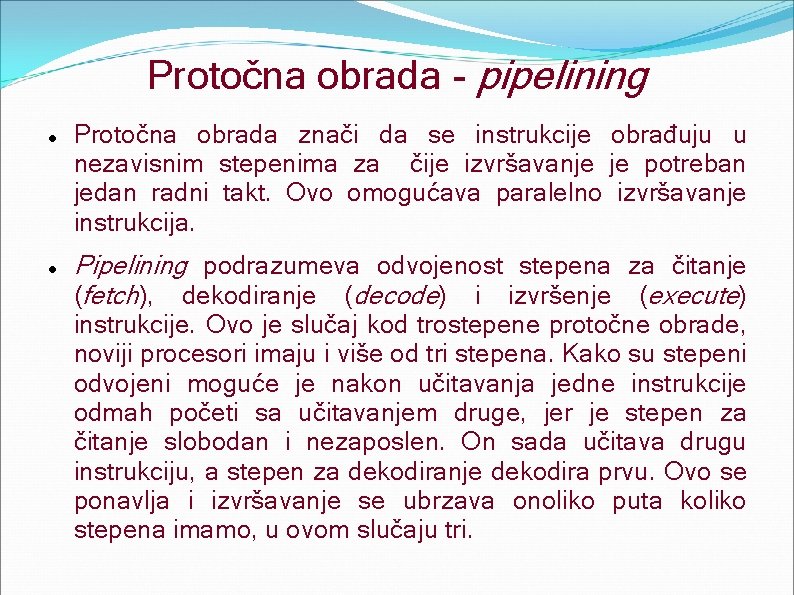

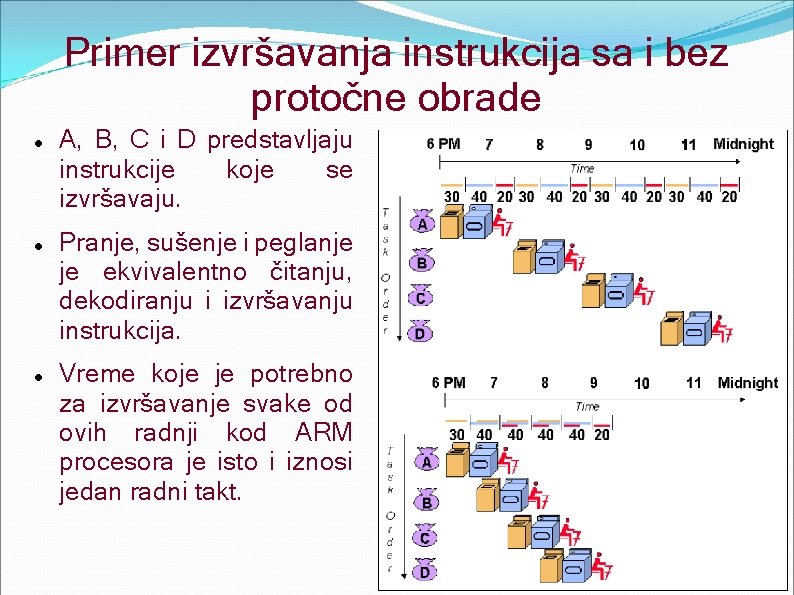

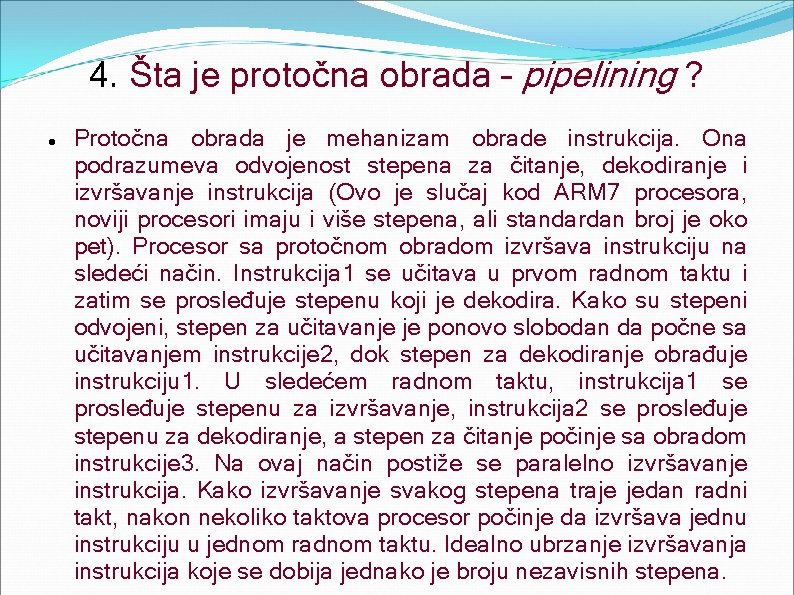

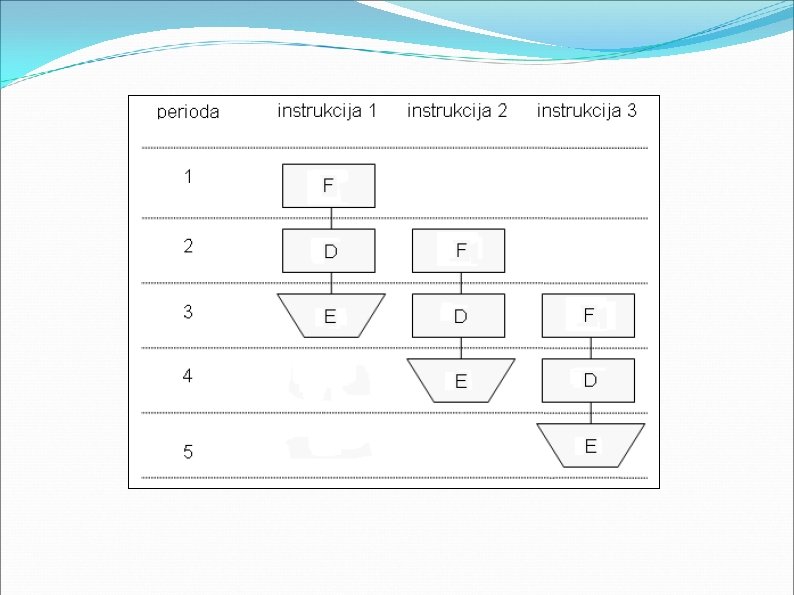

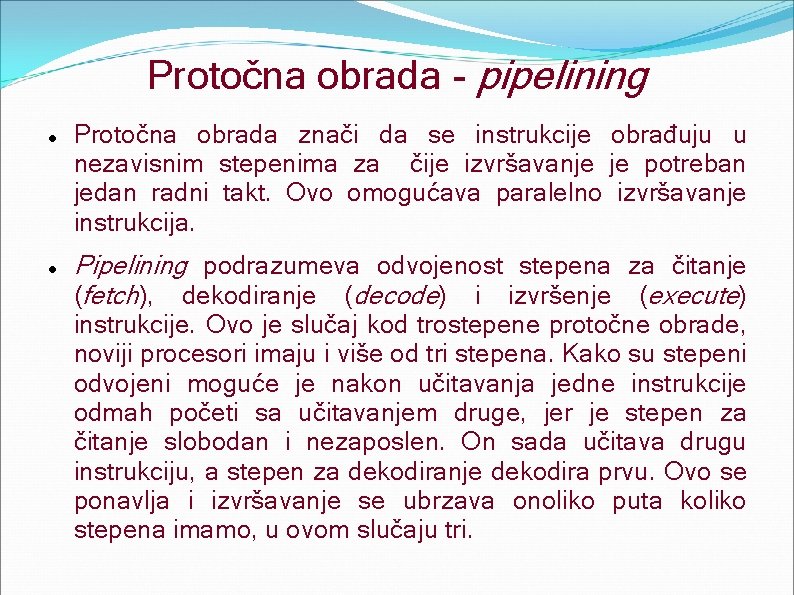

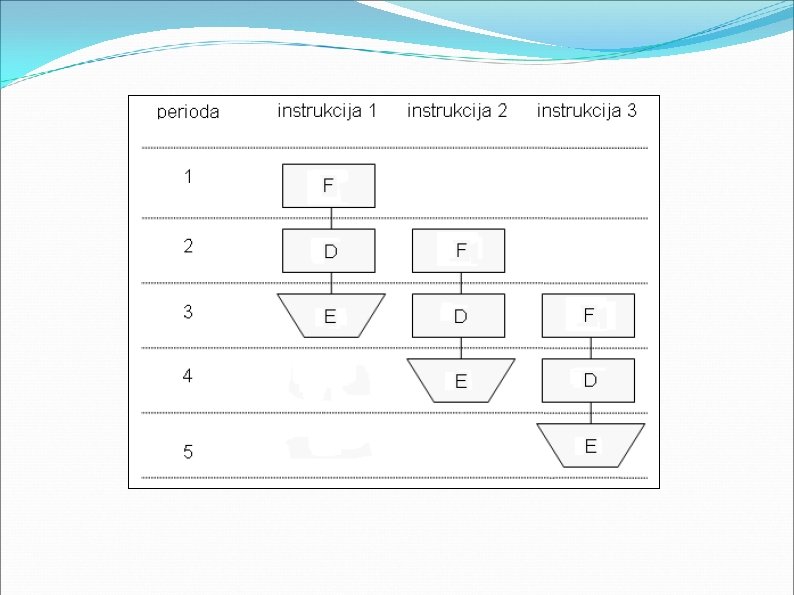

Protočna obrada - pipelining Protočna obrada znači da se instrukcije obrađuju u nezavisnim stepenima za čije izvršavanje je potreban jedan radni takt. Ovo omogućava paralelno izvršavanje instrukcija. Pipelining podrazumeva odvojenost stepena za čitanje (fetch), dekodiranje (decode) i izvršenje (execute) instrukcije. Ovo je slučaj kod trostepene protočne obrade, noviji procesori imaju i više od tri stepena. Kako su stepeni odvojeni moguće je nakon učitavanja jedne instrukcije odmah početi sa učitavanjem druge, jer je stepen za čitanje slobodan i nezaposlen. On sada učitava drugu instrukciju, a stepen za dekodiranje dekodira prvu. Ovo se ponavlja i izvršavanje se ubrzava onoliko puta koliko stepena imamo, u ovom slučaju tri.

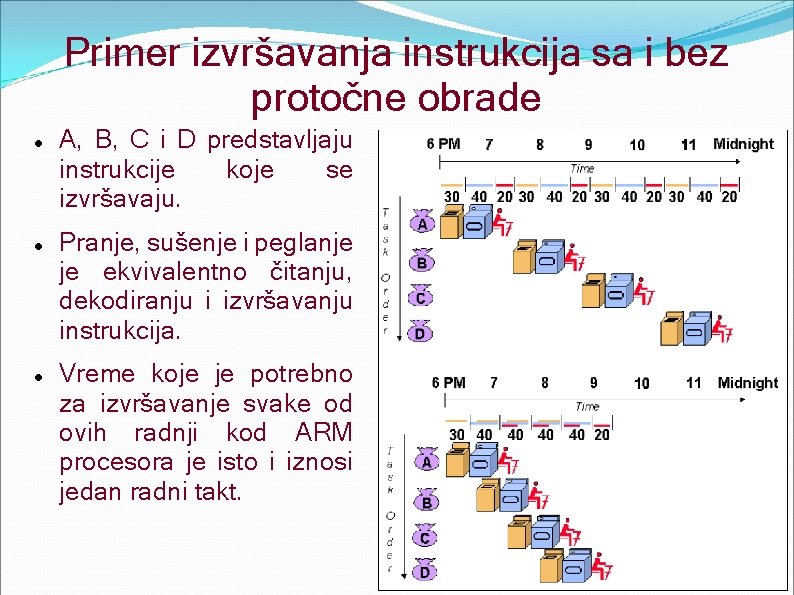

Primer izvršavanja instrukcija sa i bez protočne obrade A, B, C i D predstavljaju instrukcije koje se izvršavaju. Pranje, sušenje i peglanje je ekvivalentno čitanju, dekodiranju i izvršavanju instrukcija. Vreme koje je potrebno za izvršavanje svake od ovih radnji kod ARM procesora je isto i iznosi jedan radni takt.

Sažetak 1. Razlika izmedju CISC i RISC arhitekture? 2. Modovi rada ARM procesora i gde se oni postavljaju? 3. Šta je Thumb osobine? set instrukcija i njegove 4. Šta je protočna obrada - pipelining?

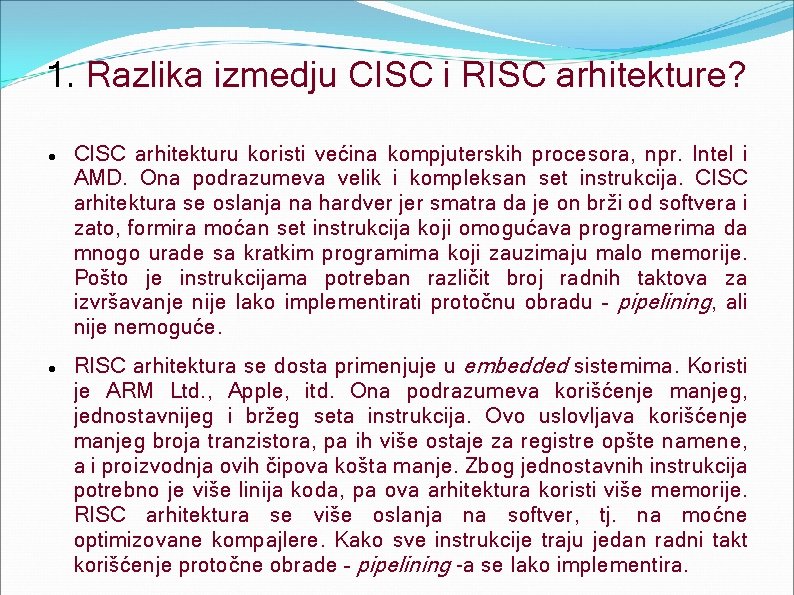

1. Razlika izmedju CISC i RISC arhitekture? CISC arhitekturu koristi većina kompjuterskih procesora, npr. Intel i AMD. Ona podrazumeva velik i kompleksan set instrukcija. CISC arhitektura se oslanja na hardver jer smatra da je on brži od softvera i zato, formira moćan set instrukcija koji omogućava programerima da mnogo urade sa kratkim programima koji zauzimaju malo memorije. Pošto je instrukcijama potreban različit broj radnih taktova za izvršavanje nije lako implementirati protočnu obradu – pipelining, ali nije nemoguće. RISC arhitektura se dosta primenjuje u embedded sistemima. Koristi je ARM Ltd. , Apple, itd. Ona podrazumeva korišćenje manjeg, jednostavnijeg i bržeg seta instrukcija. Ovo uslovljava korišćenje manjeg broja tranzistora, pa ih više ostaje za registre opšte namene, a i proizvodnja ovih čipova košta manje. Zbog jednostavnih instrukcija potrebno je više linija koda, pa ova arhitektura koristi više memorije. RISC arhitektura se više oslanja na softver, tj. na moćne optimizovane kompajlere. Kako sve instrukcije traju jedan radni takt korišćenje protočne obrade – pipelining -a se lako implementira.

CISC RISC Naglasak na hardveru Naglasak na softveru Sadrži kompleksni set instrukcija koje mogu da se izvršavaju u više radnih taktova (protočna obrada se teže realizuje) Sadrži isključivo umanjeni set instrukcija koje se izvršavaju u jednom radnom taktu (mogućnost protočne obrade - pipelining) Instrukcije su memorijsko-memorijske: LOAD i STORE su uključene u komande Instrukcije su registarsko-registarske: LOAD i STORE su nezavisne komande Kodovi male veličine, manje memorije je potrebno Veliki kodovi, više memorije je potrebno Tranzistori se koriste za skladistenje kompleksnih instrukcija i potrebno ih je više Manje tranzistora je potrebno za skladištenje instrukcije pa ih više ostaje kao registri opšte namene

2. Modovi rada ARM procesora i gde se oni postavljaju? ARM podržava sedam modova rada: 1. User mode (USR) - osnovni mod, većina programa se izvršava u ovom modu 2. System mode (SYS) - privilegovani mod za operativni sistem 3. Fast Interrupt (FIQ) - mod koji omogućava procesiranje prekida 4. 5. 6. 7. visokog prioriteta Interrupt (IRQ) - mod namenjen prekidima niskog prioriteta Supervisor (SVC) - mod u slučaju reseta ili softverskog prekida Abort (ABT) - mod koji se aktivira prilikom grešaka u pristupu memoriji (load / store) Undefined (UND) – mod koji se aktivira kada se pokuša dekodirati nedefinisana instrukcija Mod rada se postavlja u CPSR registru i određuje ga prvih pet bita.

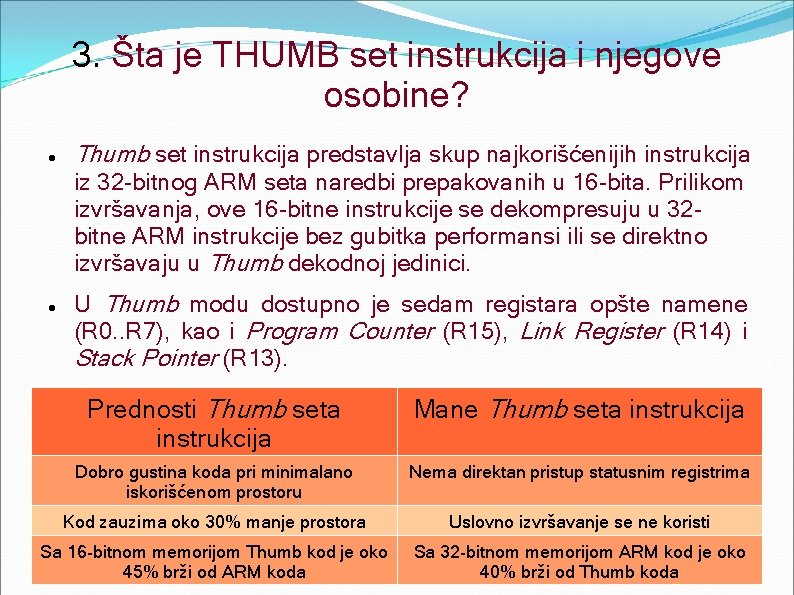

3. Šta je THUMB set instrukcija i njegove osobine? Thumb set instrukcija predstavlja skup najkorišćenijih instrukcija iz 32 -bitnog ARM seta naredbi prepakovanih u 16 -bita. Prilikom izvršavanja, ove 16 -bitne instrukcije se dekompresuju u 32 bitne ARM instrukcije bez gubitka performansi ili se direktno izvršavaju u Thumb dekodnoj jedinici. U Thumb modu dostupno je sedam registara opšte namene (R 0. . R 7), kao i Program Counter (R 15), Link Register (R 14) i Stack Pointer (R 13). Prednosti Thumb seta instrukcija Mane Thumb seta instrukcija Dobro gustina koda pri minimalano iskorišćenom prostoru Nema direktan pristup statusnim registrima Kod zauzima oko 30% manje prostora Uslovno izvršavanje se ne koristi Sa 16 -bitnom memorijom Thumb kod je oko 45% brži od ARM koda Sa 32 -bitnom memorijom ARM kod je oko 40% brži od Thumb koda

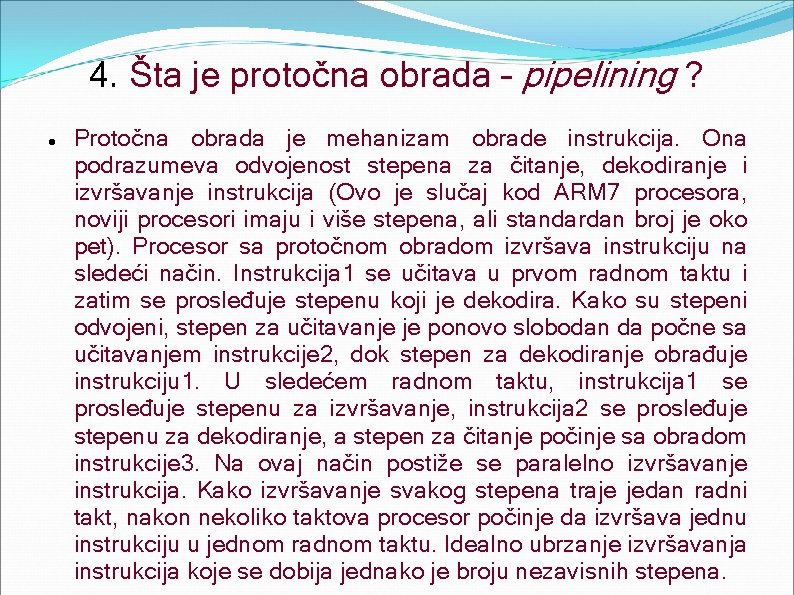

4. Šta je protočna obrada – pipelining ? Protočna obrada je mehanizam obrade instrukcija. Ona podrazumeva odvojenost stepena za čitanje, dekodiranje i izvršavanje instrukcija (Ovo je slučaj kod ARM 7 procesora, noviji procesori imaju i više stepena, ali standardan broj je oko pet). Procesor sa protočnom obradom izvršava instrukciju na sledeći način. Instrukcija 1 se učitava u prvom radnom taktu i zatim se prosleđuje stepenu koji je dekodira. Kako su stepeni odvojeni, stepen za učitavanje je ponovo slobodan da počne sa učitavanjem instrukcije 2, dok stepen za dekodiranje obrađuje instrukciju 1. U sledećem radnom taktu, instrukcija 1 se prosleđuje stepenu za izvršavanje, instrukcija 2 se prosleđuje stepenu za dekodiranje, a stepen za čitanje počinje sa obradom instrukcije 3. Na ovaj način postiže se paralelno izvršavanje instrukcija. Kako izvršavanje svakog stepena traje jedan radni takt, nakon nekoliko taktova procesor počinje da izvršava jednu instrukciju u jednom radnom taktu. Idealno ubrzanje izvršavanja instrukcija koje se dobija jednako je broju nezavisnih stepena.

![Literatura 1 Carol Atack i Alex van Someren The ARM RISC Chip A Programmers Literatura [1] Carol Atack i Alex van Someren, 'The ARM RISC Chip: A Programmers'](https://slidetodoc.com/presentation_image_h2/ae170a42e33f8f354110761a5a3312a6/image-34.jpg)

Literatura [1] Carol Atack i Alex van Someren, 'The ARM RISC Chip: A Programmers' Guide', Boston: Addison Wesley, 1993. [2] Veljko Malbaša i Predrag Teodorović – 'Mikroračunarski sistemi za rad u realnom vremenu', Novi Sad: FTN, 2010. [3] http: //en. wikipedia. org/wiki/ARM_architecture - Dokumentacija o arhitekturi ARM procesora [4] http: //www-cs-faculty. stanford. edu/risccisc/ - Poređenje CISC i RISC arhitekture [5] http: //www-cs-faculty. stanford. edu/pipelining/ - Analiza pipelining-a

Hvala na pažnji