Principle of Microcomputer Based on ARM Technology 15

Principle of Microcomputer Based on ARM Technology (15) 主讲人:陈桂友

CONTENTS • Objectives • Assembly Basics • Moving Data • Data Processing Instructions • Branch and Control Instructions • Miscellaneous Instructions 2 /17

★Objectives: Ø Grasp Branch and Control Instructions, including syntax and usage. 3 /17

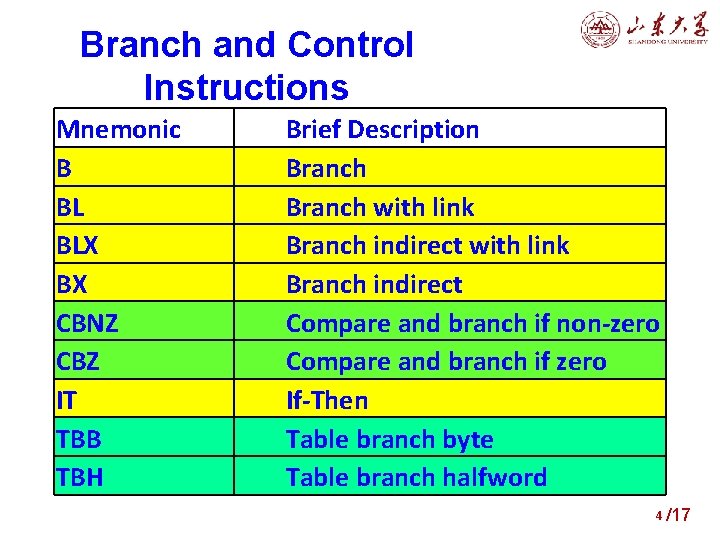

Branch and Control Instructions Mnemonic B BL BLX BX CBNZ CBZ IT TBB TBH Brief Description Branch with link Branch indirect Compare and branch if non-zero Compare and branch if zero If-Then Table branch byte Table branch halfword 4 /17

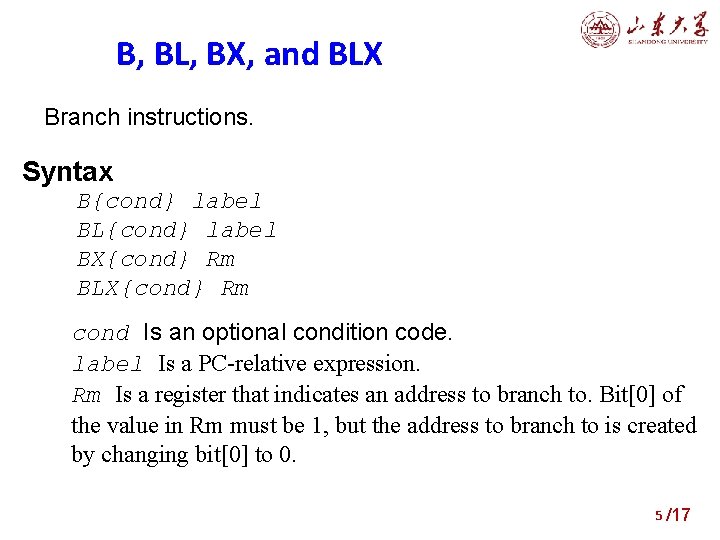

B, BL, BX, and BLX Branch instructions. Syntax B{cond} label BL{cond} label BX{cond} Rm BLX{cond} Rm cond Is an optional condition code. label Is a PC-relative expression. Rm Is a register that indicates an address to branch to. Bit[0] of the value in Rm must be 1, but the address to branch to is created by changing bit[0] to 0. 5 /17

B, BL, BX, and BLX Branch instructions. Examples B loop. A ; Branch to loop. A. BLE ng ; Conditionally branch to label ng. B. W target ; Branch to target within 16 MB range. BEQ target ; Conditionally branch to target. BEQ. W target ; Conditionally branch to target within 1 MB. BL fun. C ; Branch with link (Call) to function fun. C, return address stored in LR. BX LR ; Return from function call. BXNE R 0 ; Conditionally branch to address stored in R 0. BLX R 0 ; Branch with link and exchange (Call) to a address stored in R 0. 6 /17

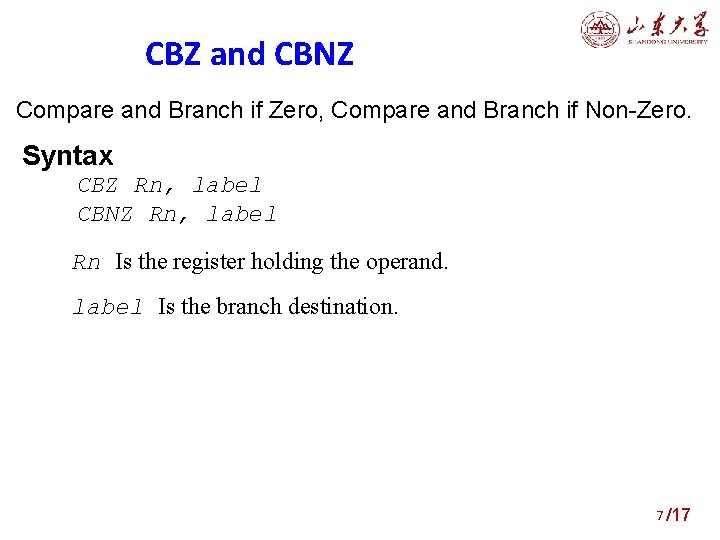

CBZ and CBNZ Compare and Branch if Zero, Compare and Branch if Non-Zero. Syntax CBZ Rn, label CBNZ Rn, label Rn Is the register holding the operand. label Is the branch destination. 7 /17

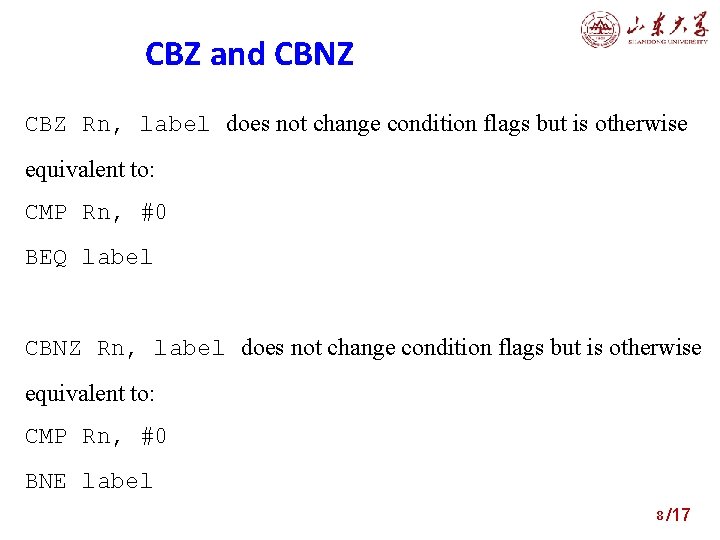

CBZ and CBNZ CBZ Rn, label does not change condition flags but is otherwise equivalent to: CMP Rn, #0 BEQ label CBNZ Rn, label does not change condition flags but is otherwise equivalent to: CMP Rn, #0 BNE label 8 /17

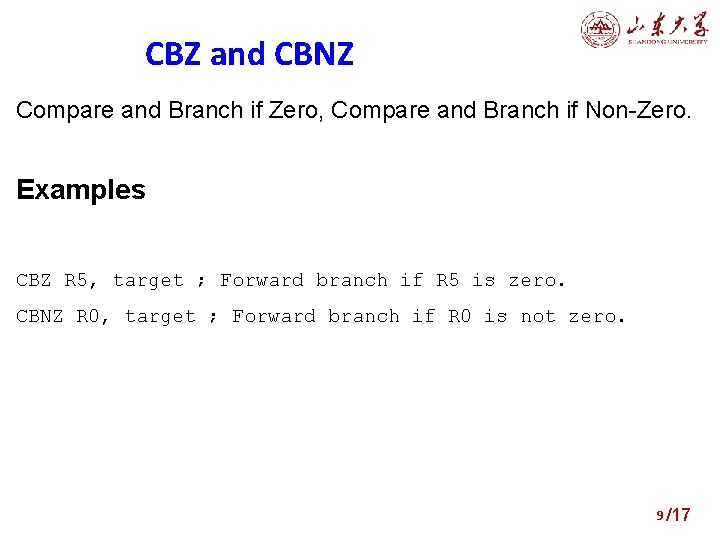

CBZ and CBNZ Compare and Branch if Zero, Compare and Branch if Non-Zero. Examples CBZ R 5, target ; Forward branch if R 5 is zero. CBNZ R 0, target ; Forward branch if R 0 is not zero. 9 /17

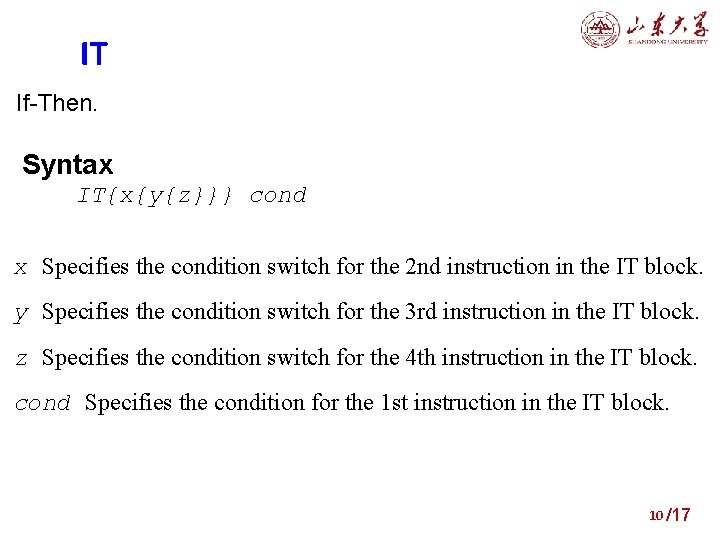

IT If-Then. Syntax IT{x{y{z}}} cond x Specifies the condition switch for the 2 nd instruction in the IT block. y Specifies the condition switch for the 3 rd instruction in the IT block. z Specifies the condition switch for the 4 th instruction in the IT block. cond Specifies the condition for the 1 st instruction in the IT block. 10 /17

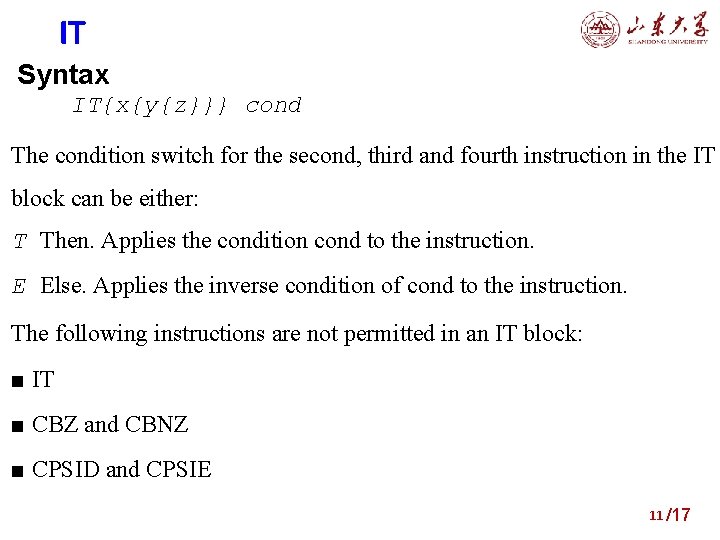

IT Syntax IT{x{y{z}}} cond The condition switch for the second, third and fourth instruction in the IT block can be either: T Then. Applies the condition cond to the instruction. E Else. Applies the inverse condition of cond to the instruction. The following instructions are not permitted in an IT block: ■ IT ■ CBZ and CBNZ ■ CPSID and CPSIE 11 /17

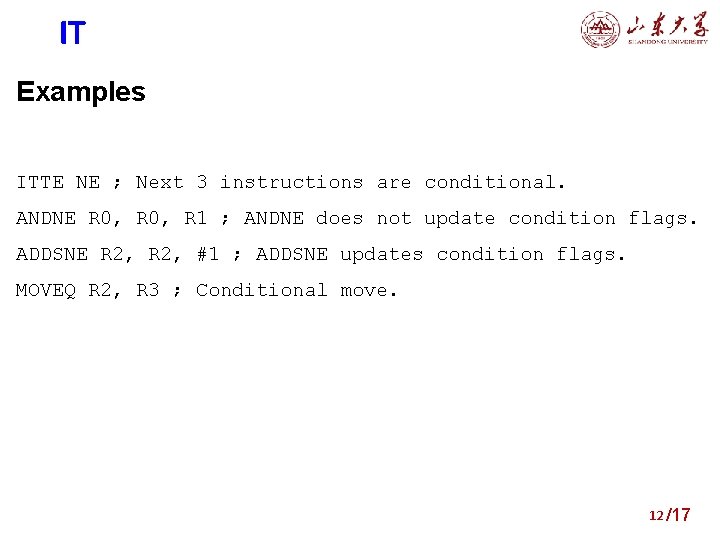

IT Examples ITTE NE ; Next 3 instructions are conditional. ANDNE R 0, R 1 ; ANDNE does not update condition flags. ADDSNE R 2, #1 ; ADDSNE updates condition flags. MOVEQ R 2, R 3 ; Conditional move. 12 /17

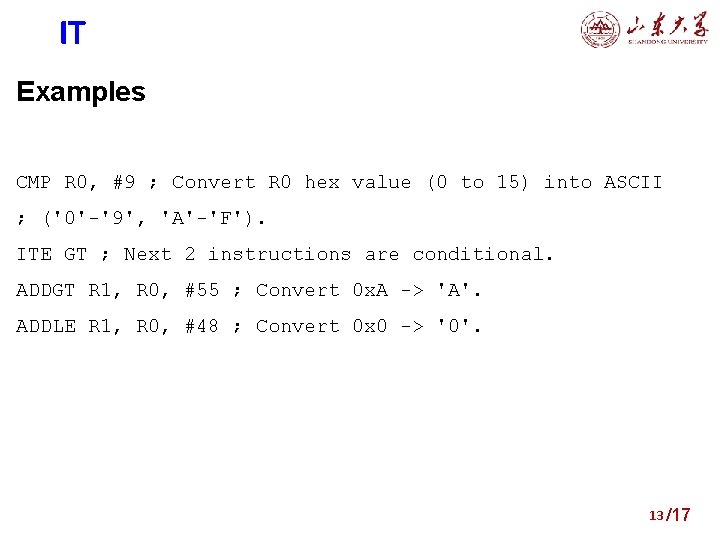

IT Examples CMP R 0, #9 ; Convert R 0 hex value (0 to 15) into ASCII ; ('0'-'9', 'A'-'F'). ITE GT ; Next 2 instructions are conditional. ADDGT R 1, R 0, #55 ; Convert 0 x. A -> 'A'. ADDLE R 1, R 0, #48 ; Convert 0 x 0 -> '0'. 13 /17

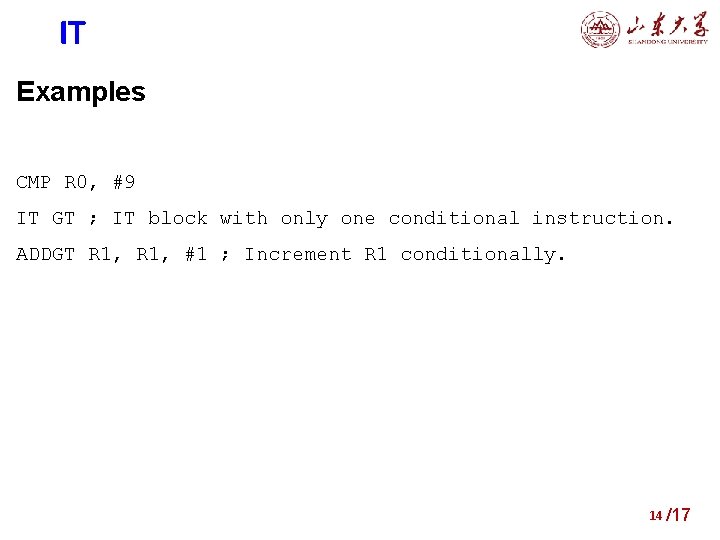

IT Examples CMP R 0, #9 IT GT ; IT block with only one conditional instruction. ADDGT R 1, #1 ; Increment R 1 conditionally. 14 /17

IT Examples CMP R 0, #9 ITTEE EQ ; Next 4 instructions are conditional. MOVEQ R 0, R 1 ; Conditional move. ADDEQ R 2, #10 ; Conditional add. ANDNE R 3, #1 ; Conditional AND. BNE. W dloop ; Branch instruction can only be used in the last instruction of an IT block. 15 /17

TBB and TBH Table Branch Byte and Table Branch Halfword. Self study by reading Cortex-M 3 -Instruction Set, P 80 -81 16 /17

Next lecture Miscellaneous Instructions 17 /17

- Slides: 17