ARM 1 ARM ARM Software Development Toolkit http

![fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1 fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1](https://slidetodoc.com/presentation_image/218512d90a6ac5043fd11b2bcefb4573/image-59.jpg)

![fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1 fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1](https://slidetodoc.com/presentation_image/218512d90a6ac5043fd11b2bcefb4573/image-61.jpg)

![fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1 fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1](https://slidetodoc.com/presentation_image/218512d90a6ac5043fd11b2bcefb4573/image-63.jpg)

![fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1 fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1](https://slidetodoc.com/presentation_image/218512d90a6ac5043fd11b2bcefb4573/image-65.jpg)

![fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1 fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1](https://slidetodoc.com/presentation_image/218512d90a6ac5043fd11b2bcefb4573/image-67.jpg)

![fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1 fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1](https://slidetodoc.com/presentation_image/218512d90a6ac5043fd11b2bcefb4573/image-68.jpg)

![fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1 fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1](https://slidetodoc.com/presentation_image/218512d90a6ac5043fd11b2bcefb4573/image-70.jpg)

- Slides: 78

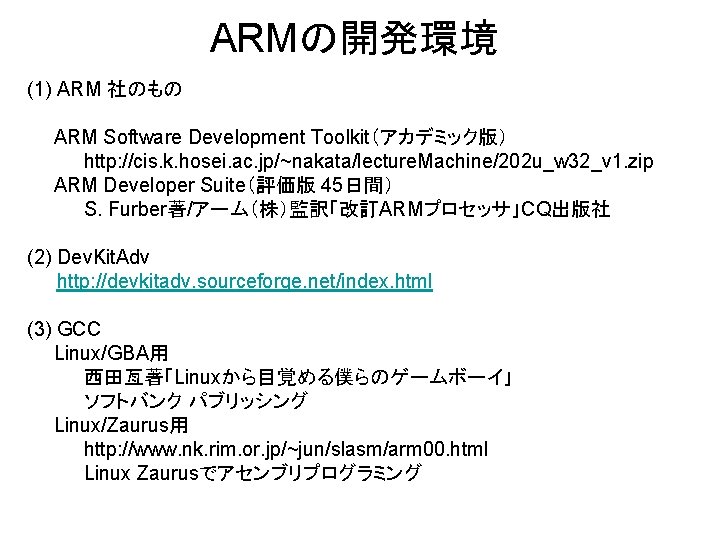

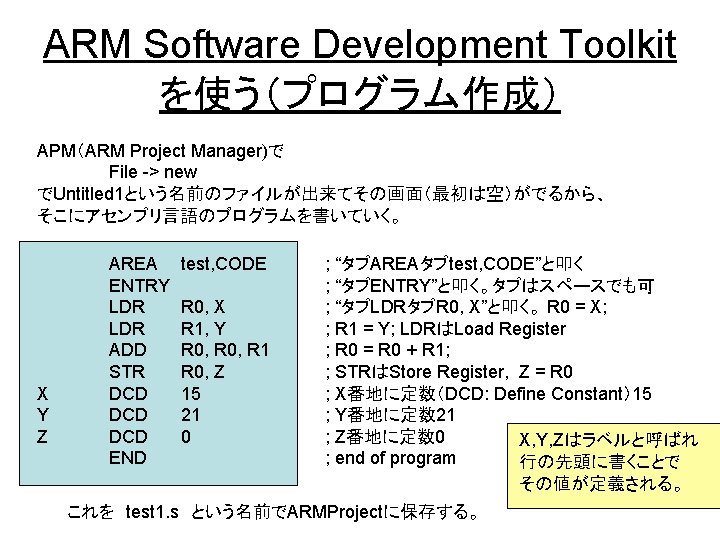

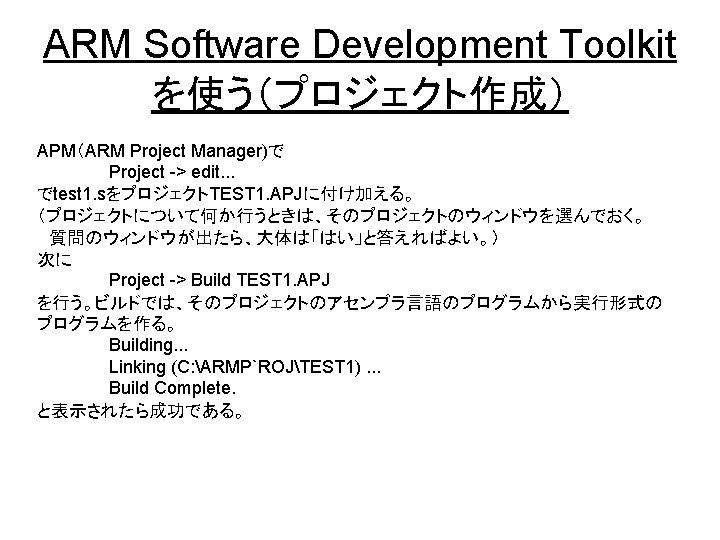

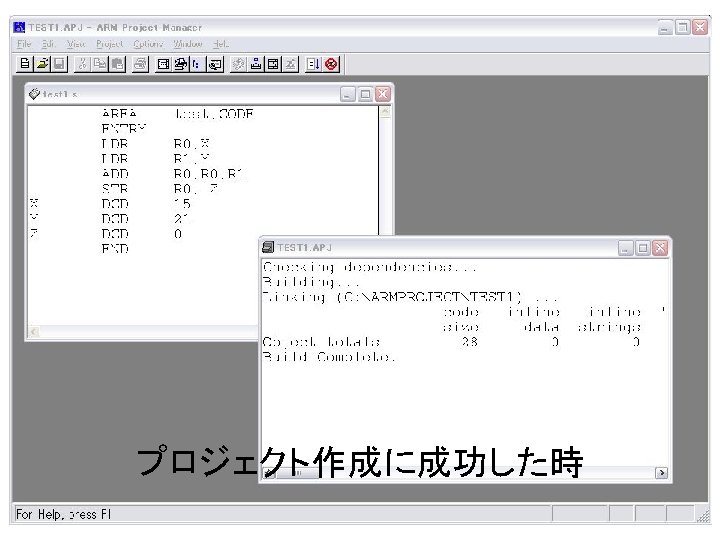

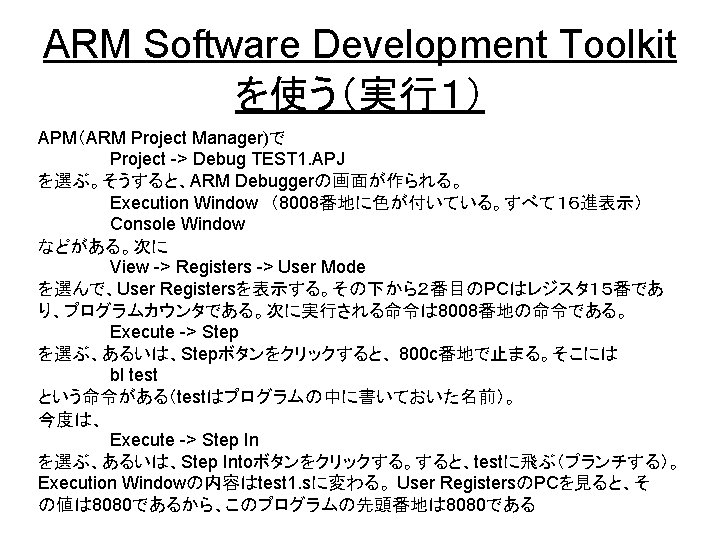

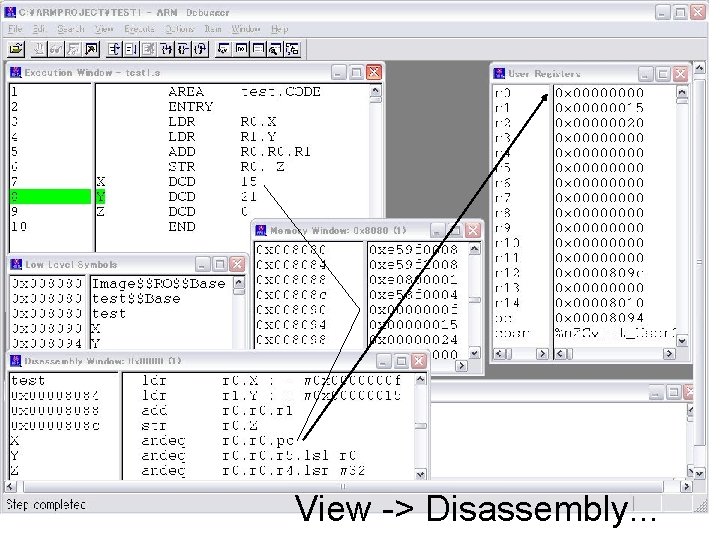

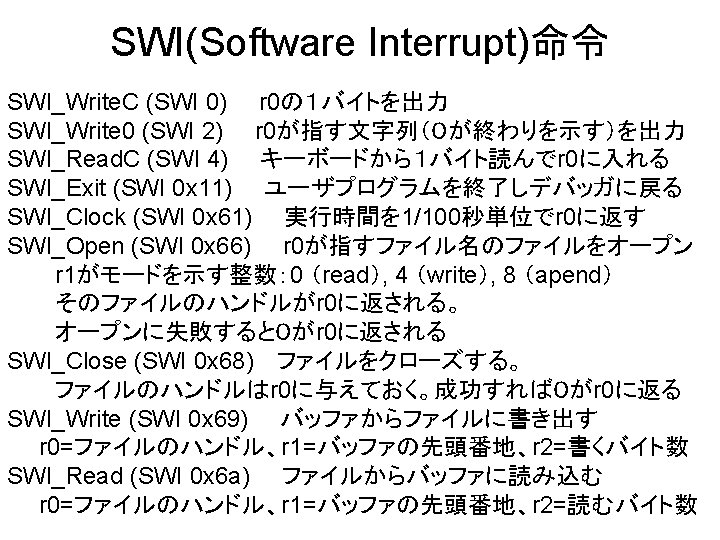

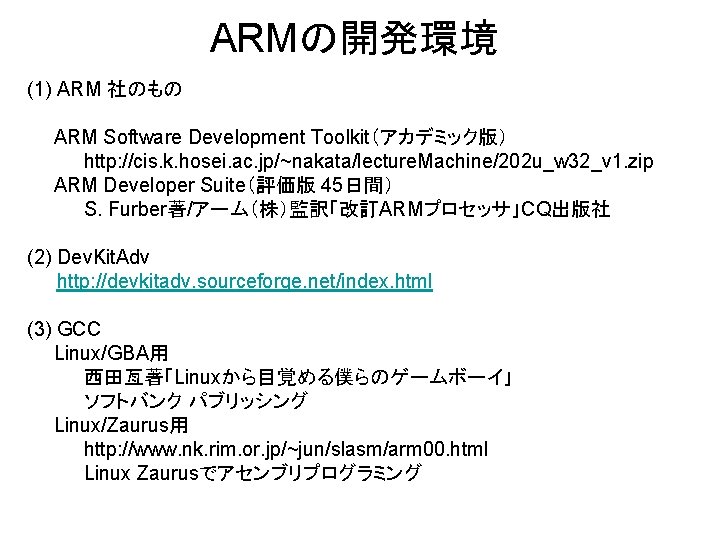

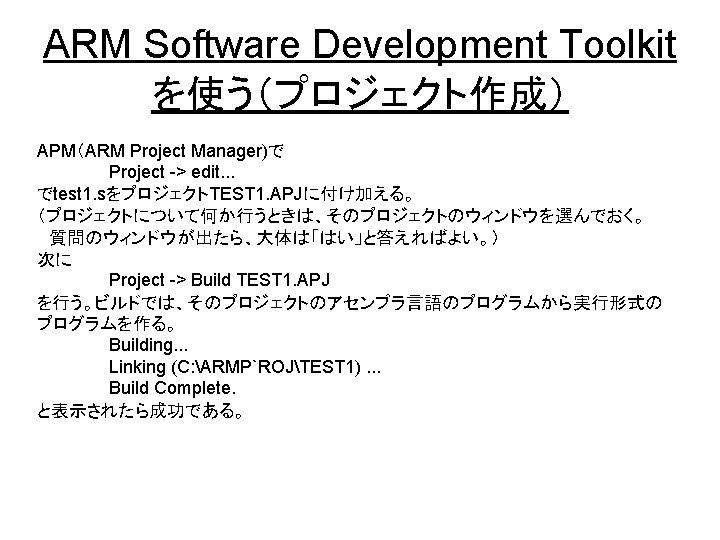

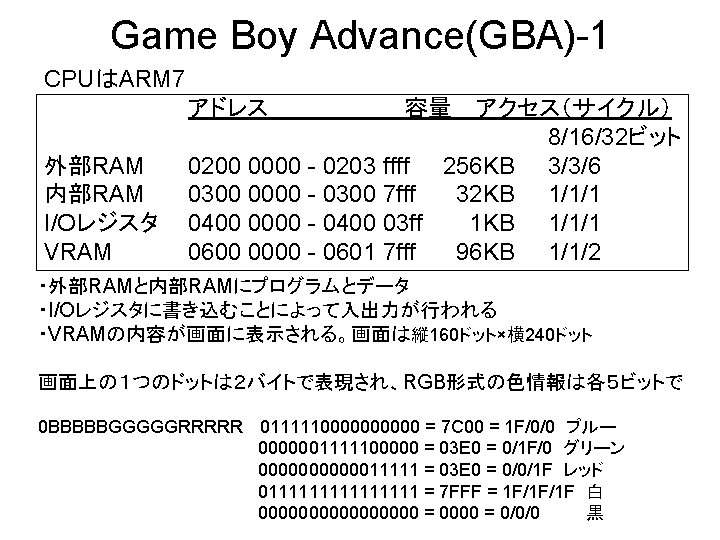

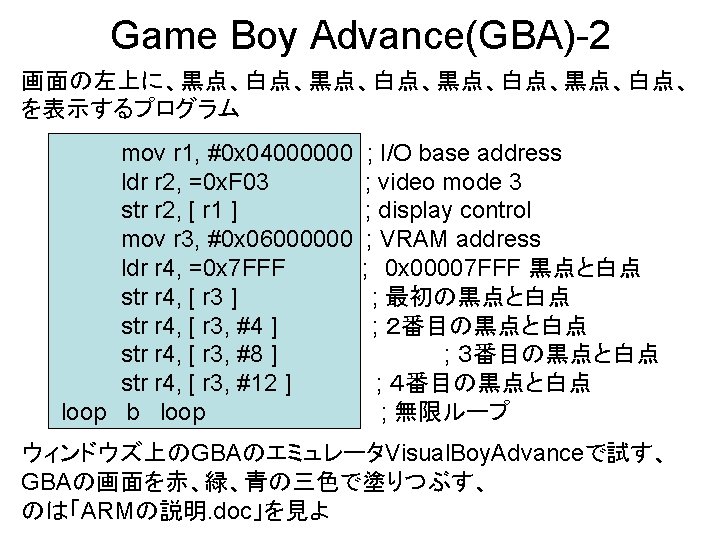

ARMの開発環境 (1) ARM 社のもの ARM Software Development Toolkit(アカデミック版) http: //cis. k. hosei. ac. jp/~nakata/lecture. Machine/202 u_w 32_v 1. zip ARM Developer Suite(評価版 45日間) S. Furber著/アーム(株)監訳「改訂ARMプロセッサ」CQ出版社 (2) Dev. Kit. Adv http: //devkitadv. sourceforge. net/index. html (3) GCC Linux/GBA用 西田亙著「Linuxから目覚める僕らのゲームボーイ」 ソフトバンク パブリッシング Linux/Zaurus用 http: //www. nk. rim. or. jp/~jun/slasm/arm 00. html Linux Zaurusでアセンブリプログラミング

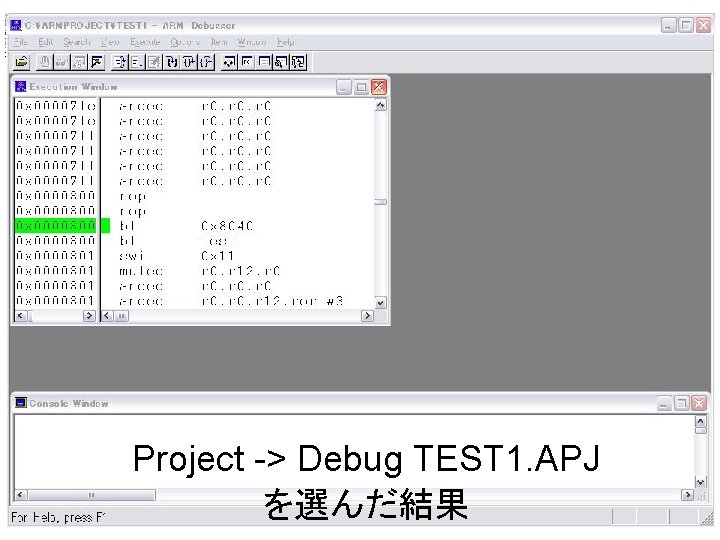

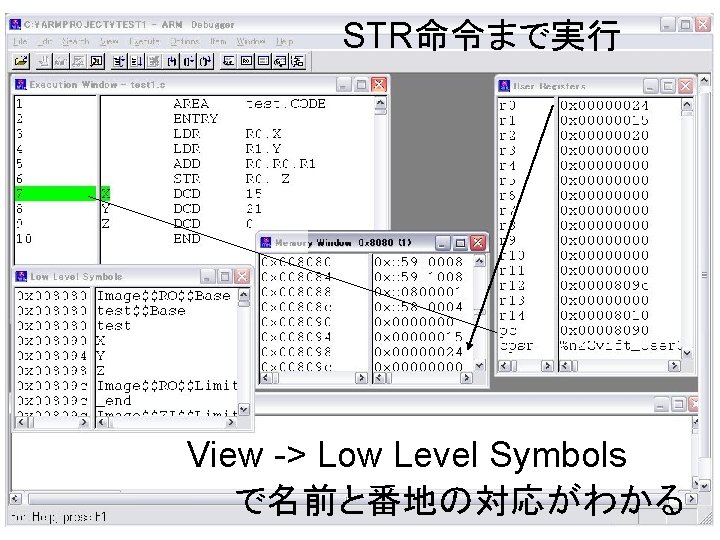

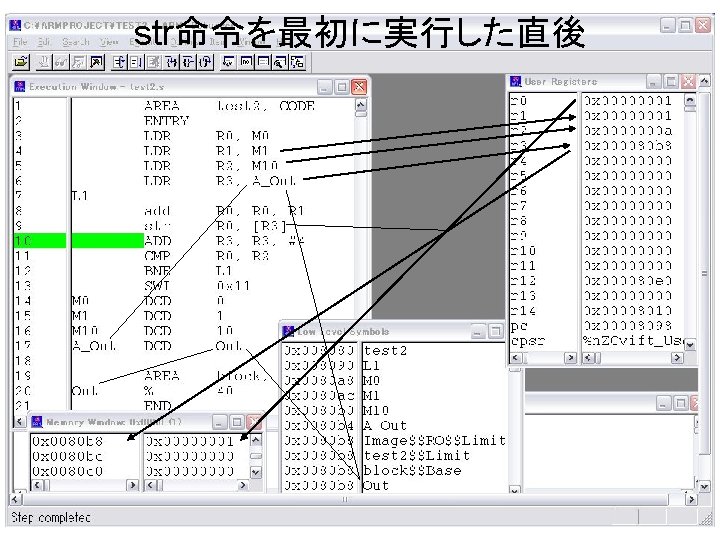

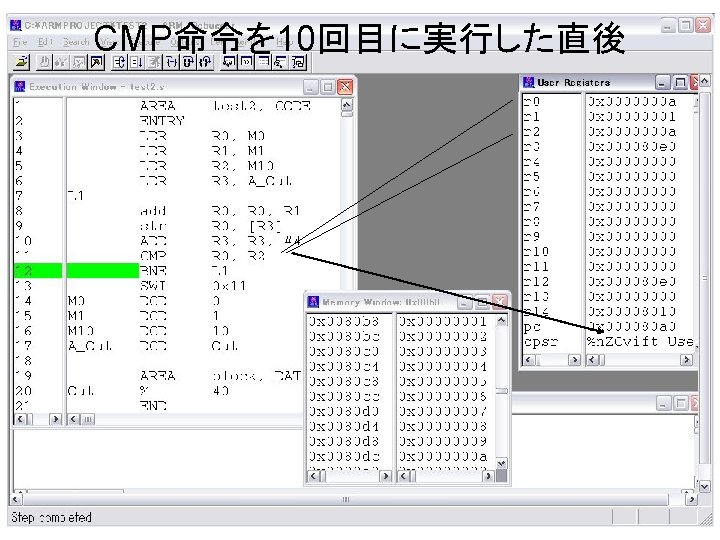

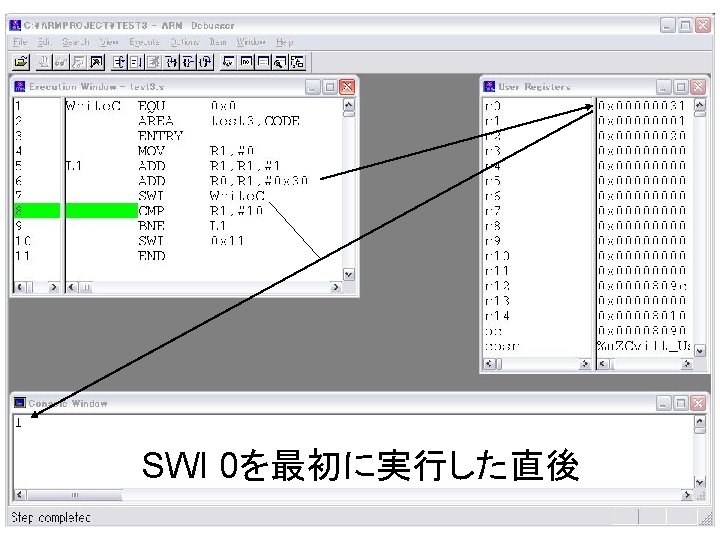

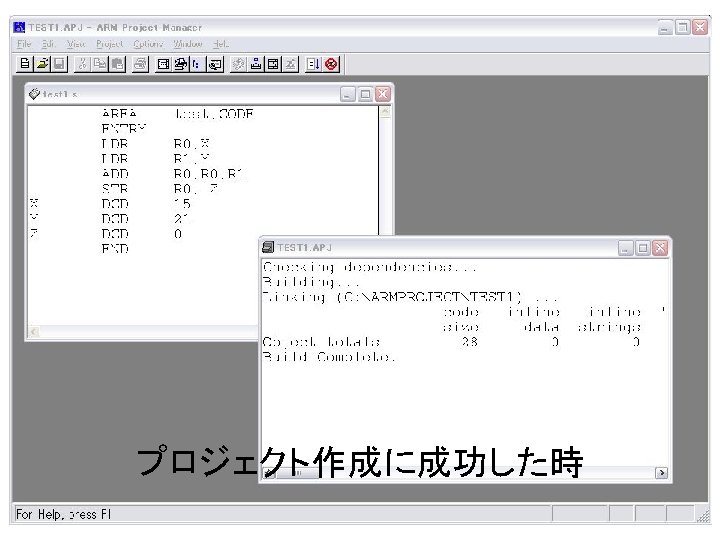

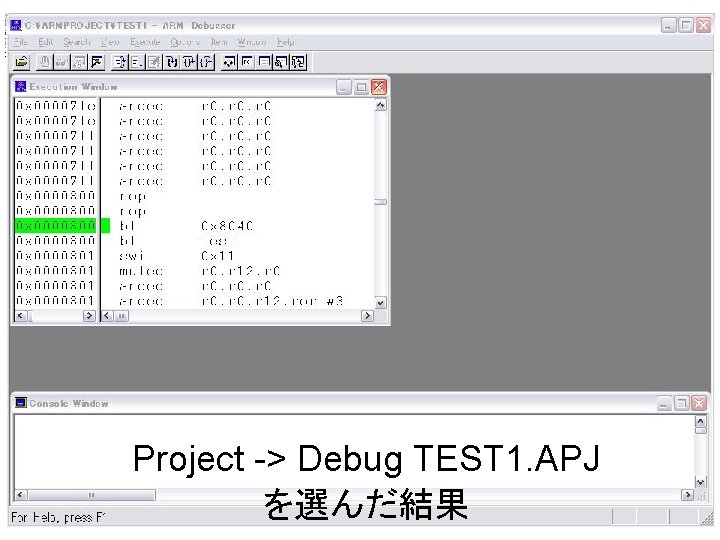

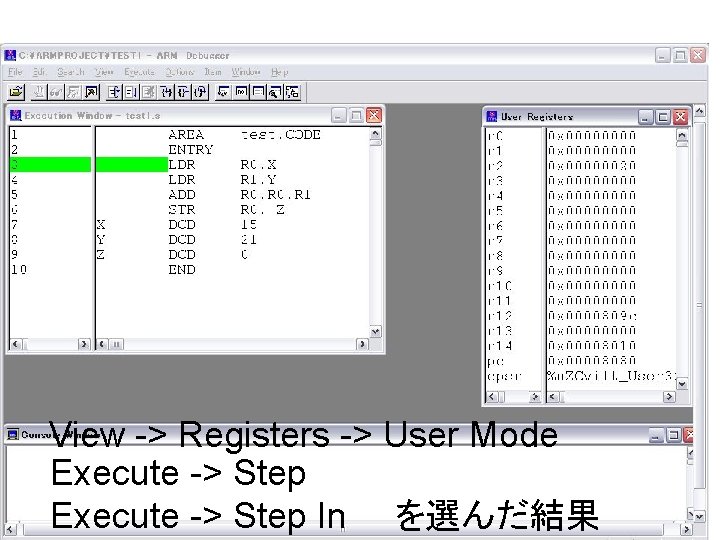

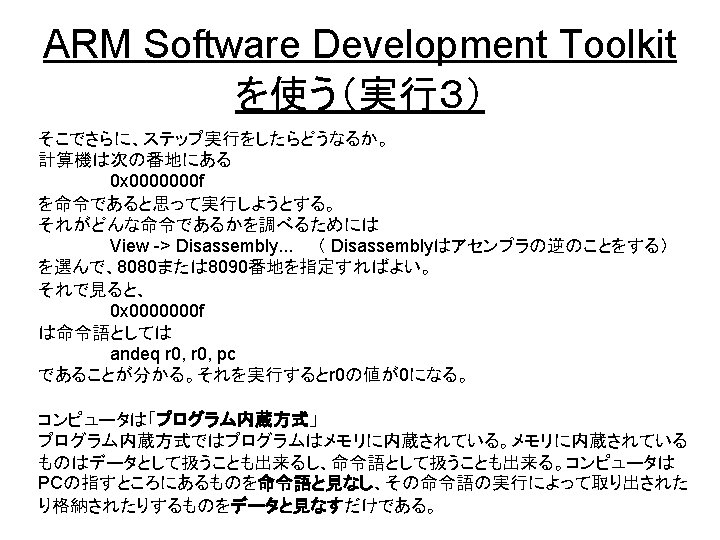

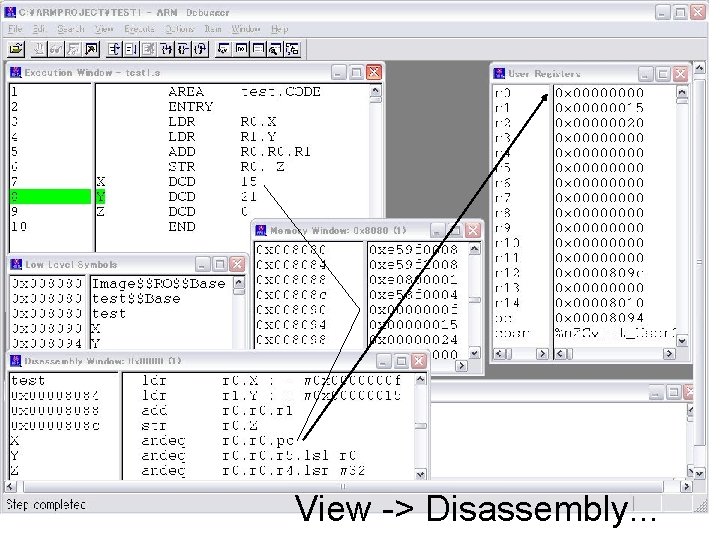

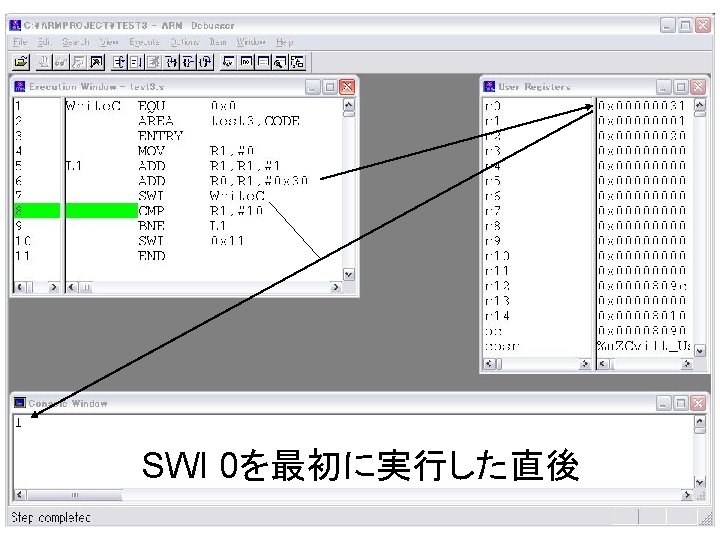

Project -> Debug TEST 1. APJ を選んだ結果

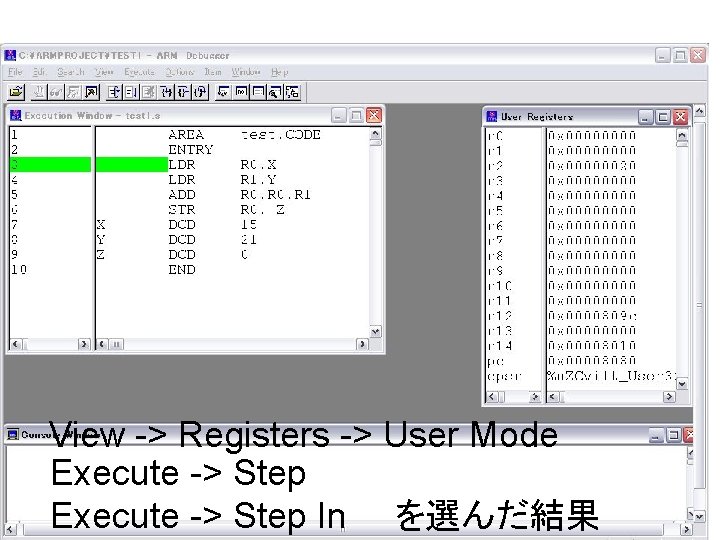

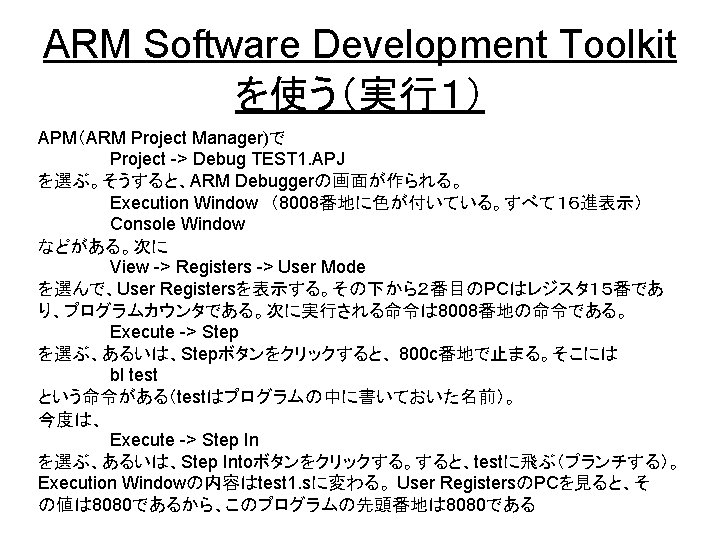

View -> Registers -> User Mode Execute -> Step In を選んだ結果

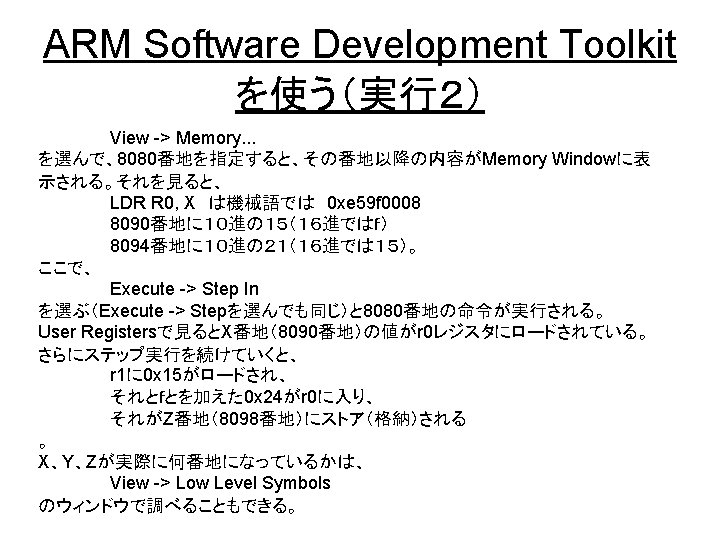

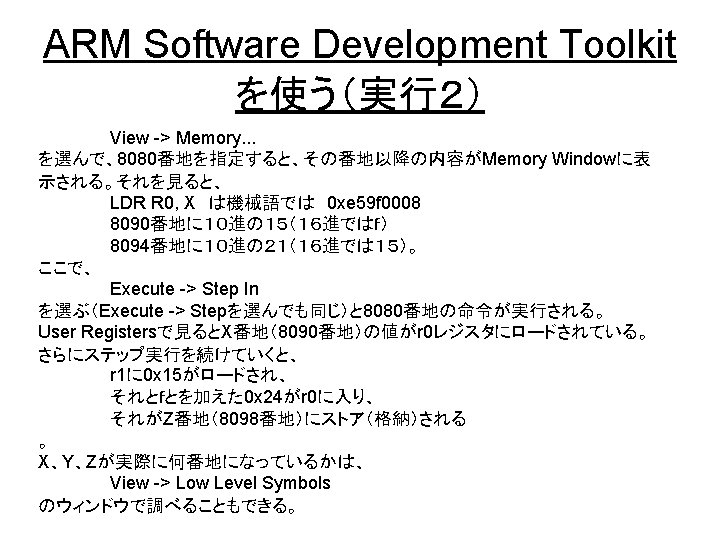

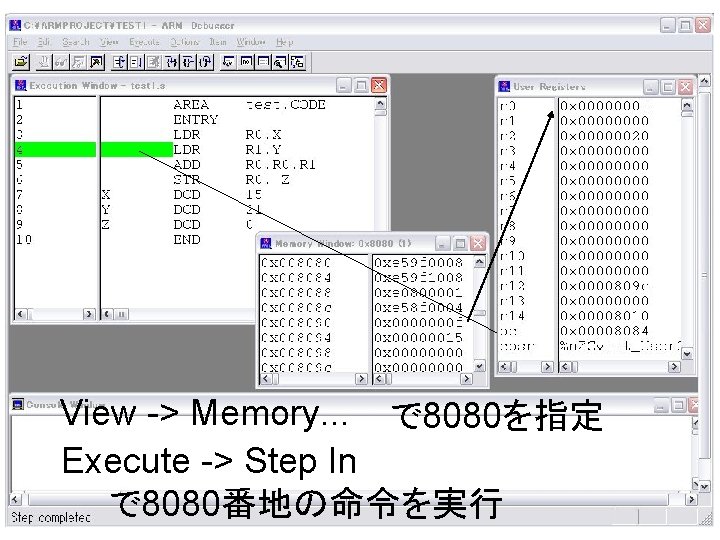

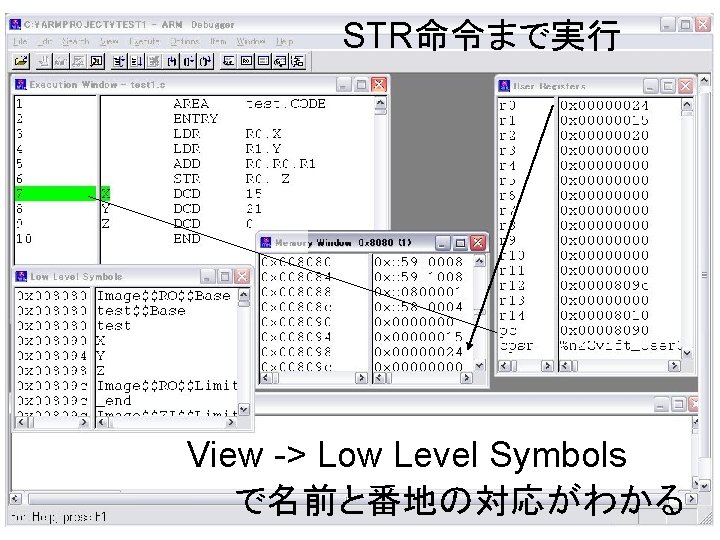

View -> Memory. . . で 8080を指定 Execute -> Step In で 8080番地の命令を実行

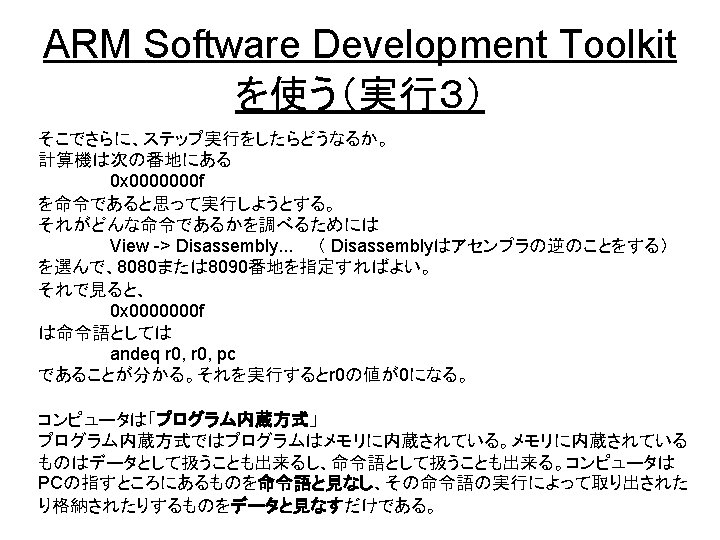

View -> Disassembly. . .

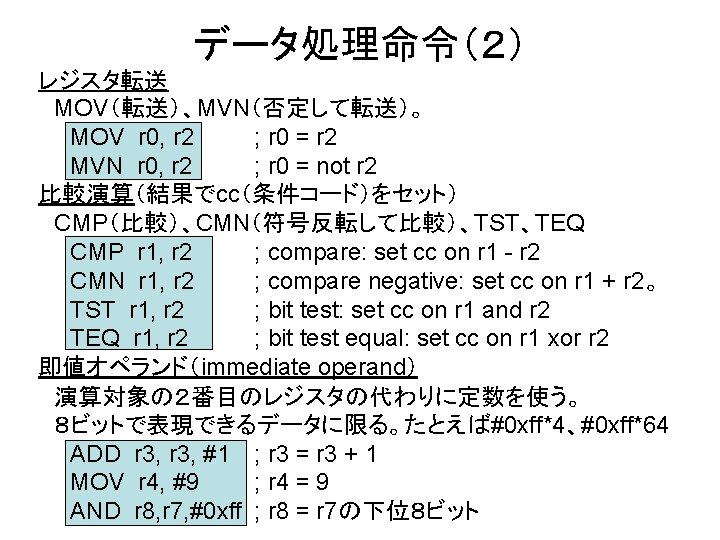

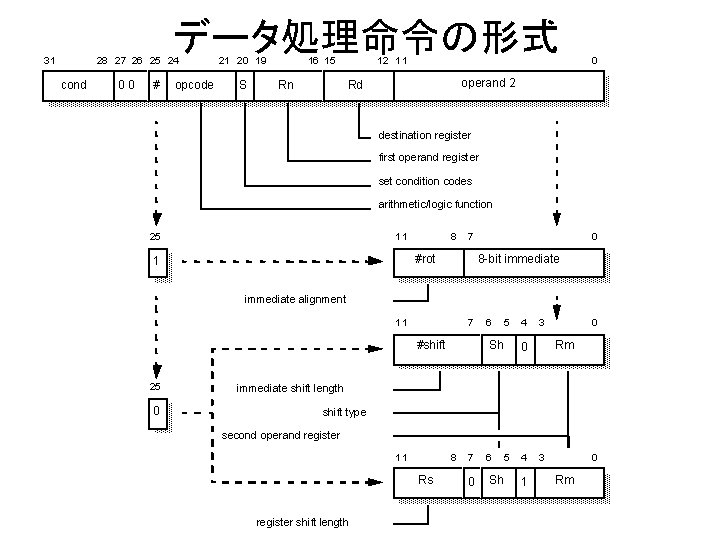

データ処理命令の形式 28 27 26 25 24 31 cond 00 # opcode 21 20 19 S 16 15 Rn 12 11 0 operand 2 Rd destination register first operand register set condition codes arithmetic/logic function 25 11 8 7 #rot 1 0 8 -bit immediate alignment 11 7 0 5 Sh #shift 25 6 4 3 0 Rm 0 immediate shift length shift type second operand register 11 8 Rs register shift length 7 0 6 Sh 5 4 1 3 0 Rm

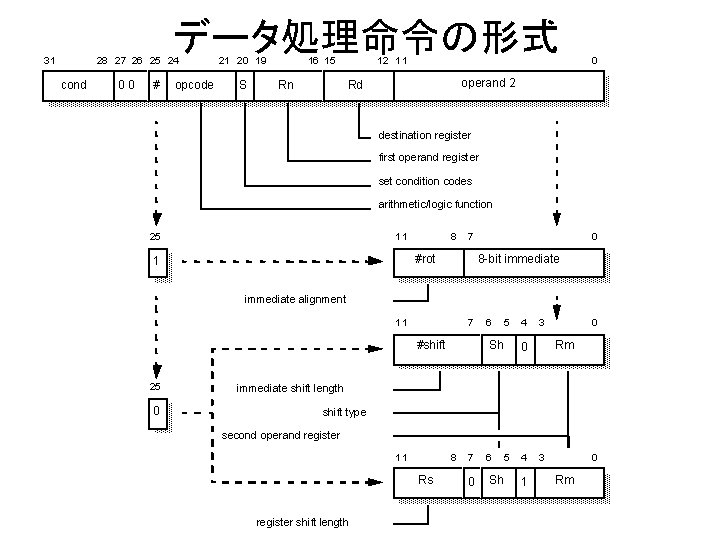

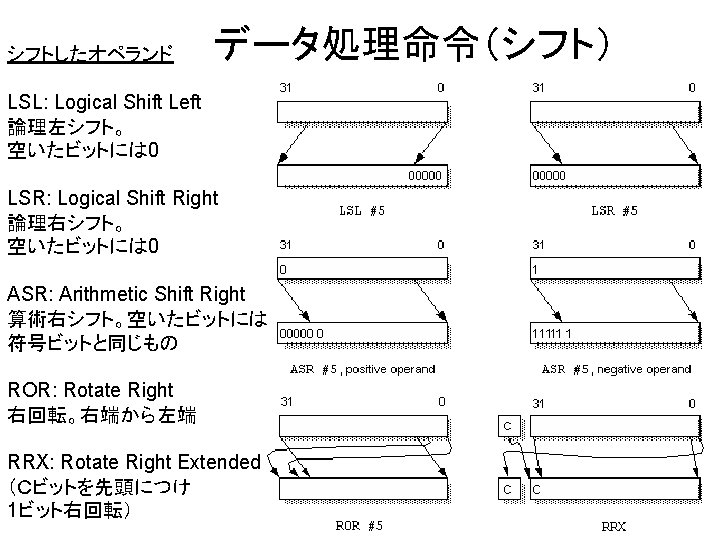

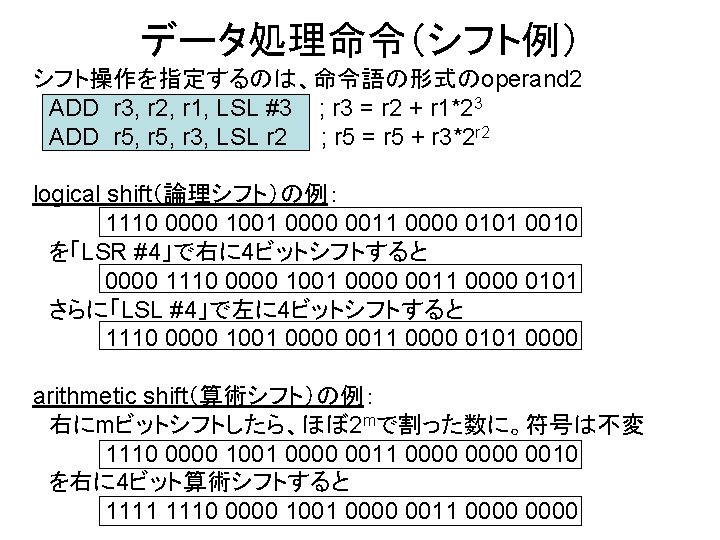

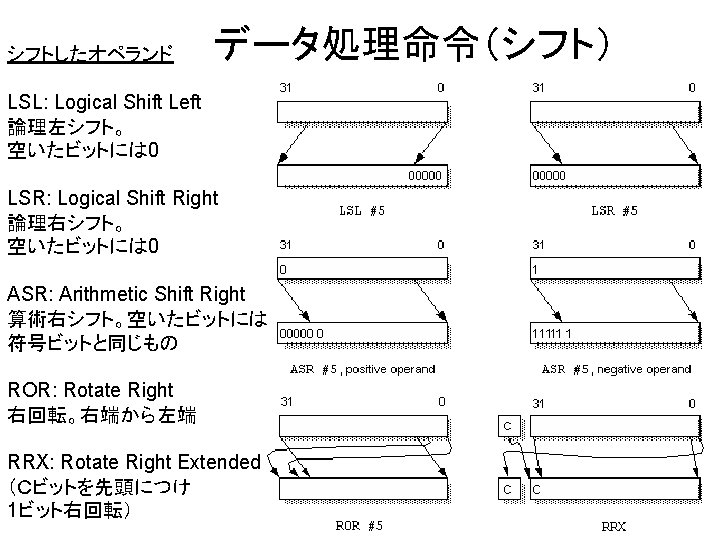

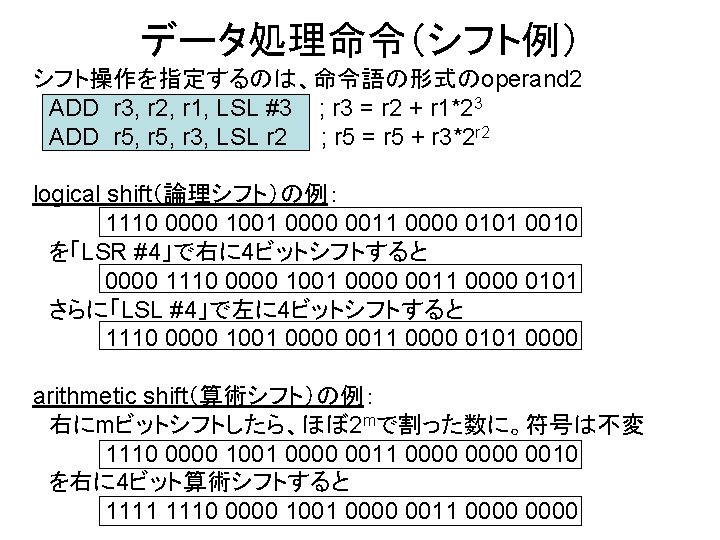

データ処理命令(シフト例) シフト操作を指定するのは、命令語の形式のoperand 2 ADD r 3, r 2, r 1, LSL #3 ; r 3 = r 2 + r 1*23 ADD r 5, r 3, LSL r 2 ; r 5 = r 5 + r 3*2 r 2 logical shift(論理シフト)の例: 1110 0000 1001 0000 0011 0000 0101 0010 を「LSR #4」で右に 4ビットシフトすると 0000 1110 0000 1001 0000 0011 0000 0101 さらに「LSL #4」で左に 4ビットシフトすると 1110 0000 1001 0000 0011 0000 0101 0000 arithmetic shift(算術シフト)の例: 右にmビットシフトしたら、ほぼ 2 mで割った数に。符号は不変 1110 0000 1001 0000 0011 0000 0010 を右に 4ビット算術シフトすると 1111 1110 0000 1001 0000 0011 0000

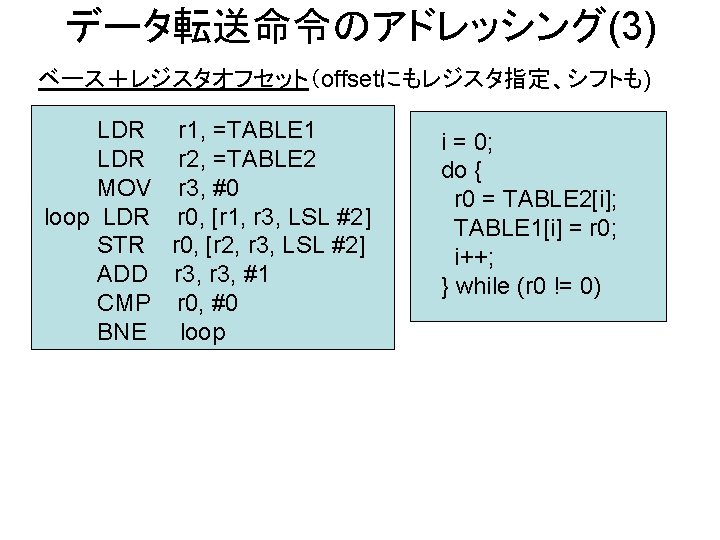

データ転送命令のアドレッシング(3) ベース+レジスタオフセット(offsetにもレジスタ指定、シフトも) LDR r 1, =TABLE 1 LDR r 2, =TABLE 2 MOV r 3, #0 loop LDR r 0, [r 1, r 3, LSL #2] STR r 0, [r 2, r 3, LSL #2] ADD r 3, #1 CMP r 0, #0 BNE loop i = 0; do { r 0 = TABLE 2[i]; TABLE 1[i] = r 0; i++; } while (r 0 != 0)

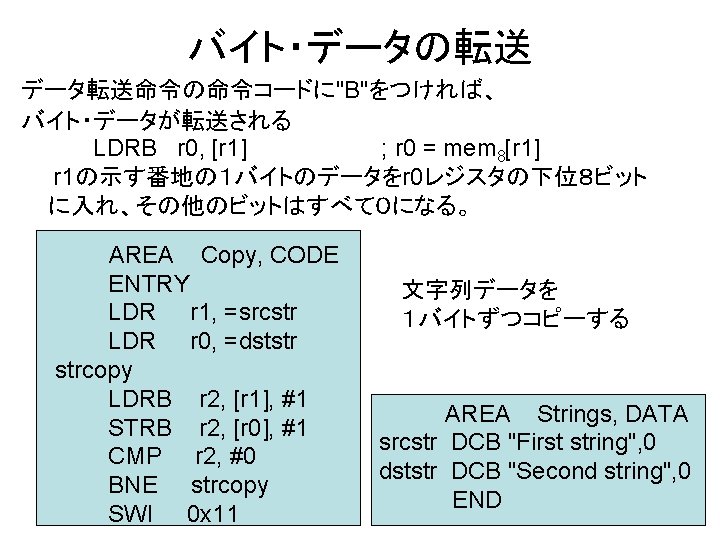

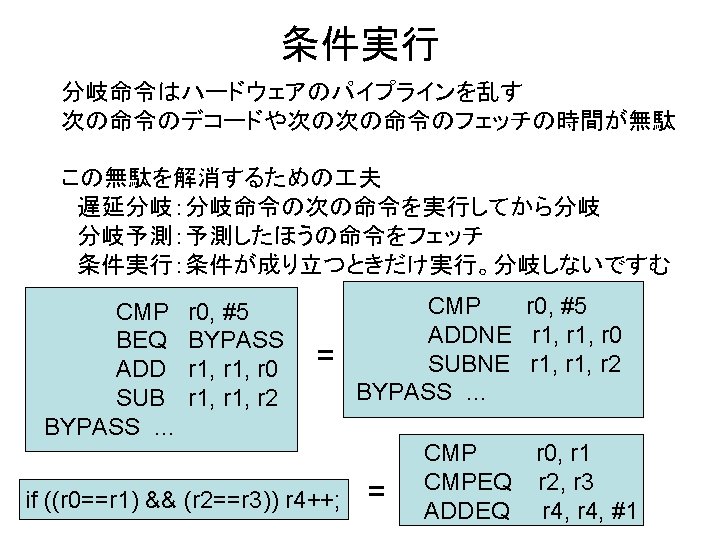

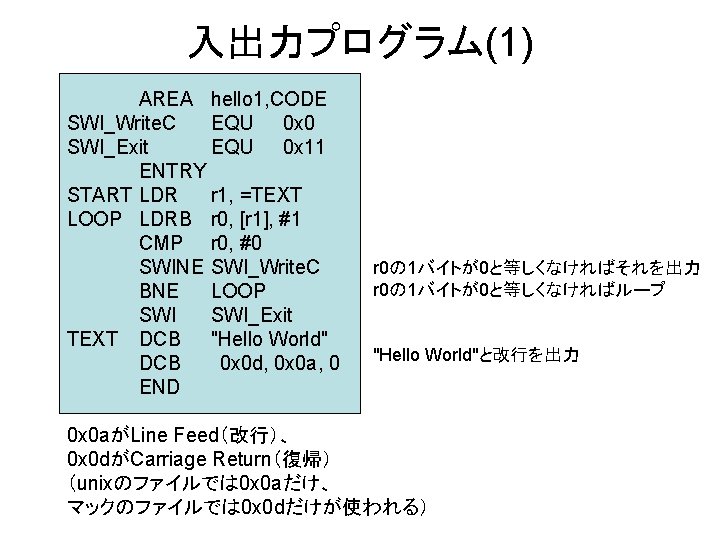

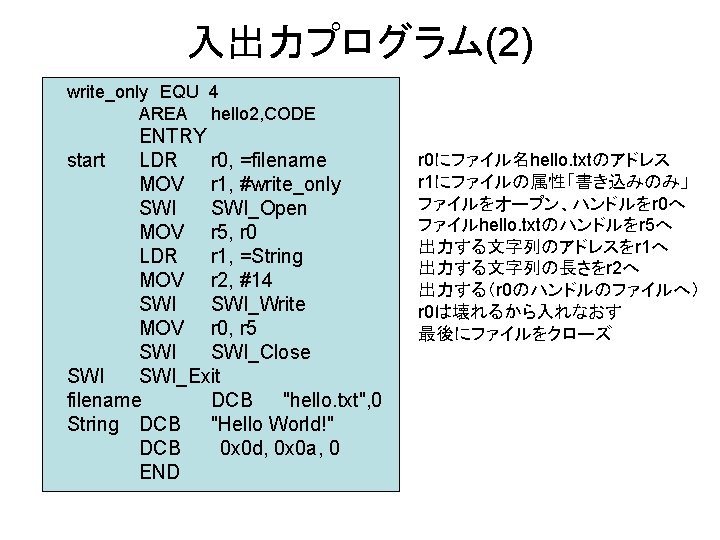

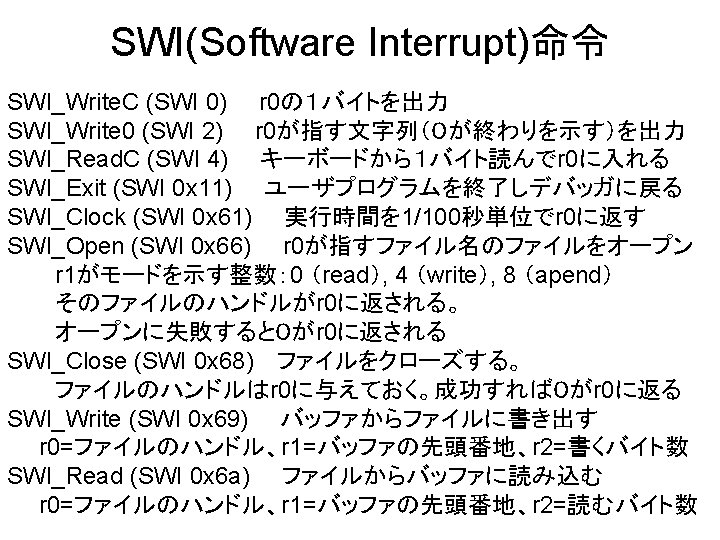

入出力プログラム(1) AREA hello 1, CODE SWI_Write. C EQU 0 x 0 SWI_Exit EQU 0 x 11 ENTRY START LDR r 1, =TEXT LOOP LDRB r 0, [r 1], #1 CMP r 0, #0 SWINE SWI_Write. C BNE LOOP SWI_Exit TEXT DCB "Hello World" DCB 0 x 0 d, 0 x 0 a, 0 END r 0の 1バイトが0と等しくなければそれを出力 r 0の 1バイトが0と等しくなければループ "Hello World"と改行を出力 0 x 0 aがLine Feed(改行)、 0 x 0 dがCarriage Return(復帰) (unixのファイルでは 0 x 0 aだけ、 マックのファイルでは 0 x 0 dだけが使われる)

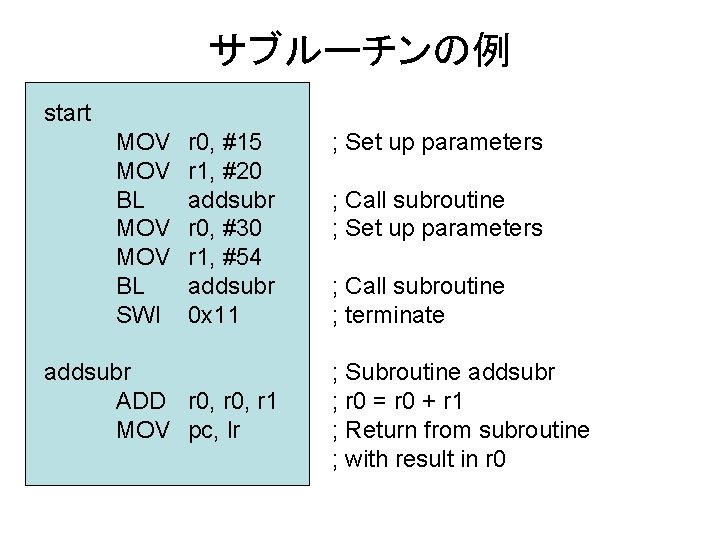

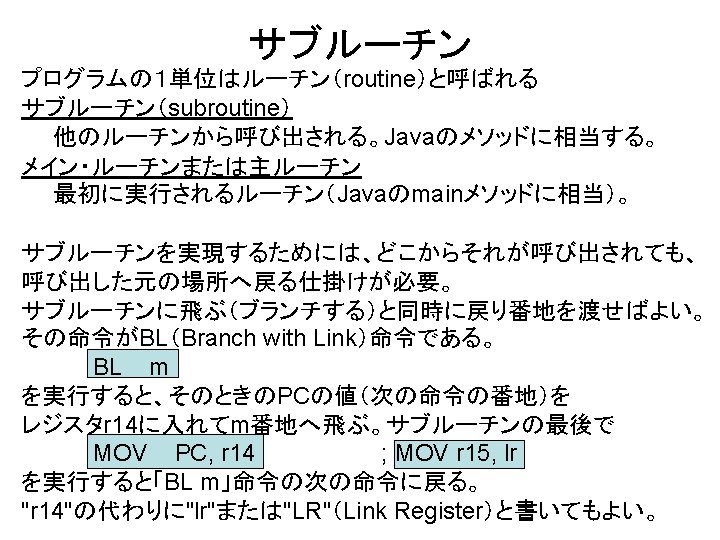

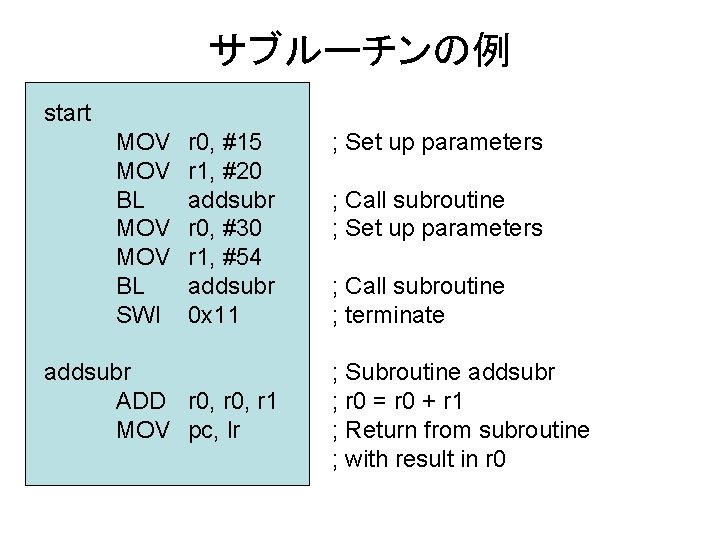

サブルーチンの例 start MOV MOV BL SWI r 0, #15 r 1, #20 addsubr r 0, #30 r 1, #54 addsubr 0 x 11 addsubr ADD r 0, r 1 MOV pc, lr ; Set up parameters ; Call subroutine ; terminate ; Subroutine addsubr ; r 0 = r 0 + r 1 ; Return from subroutine ; with result in r 0

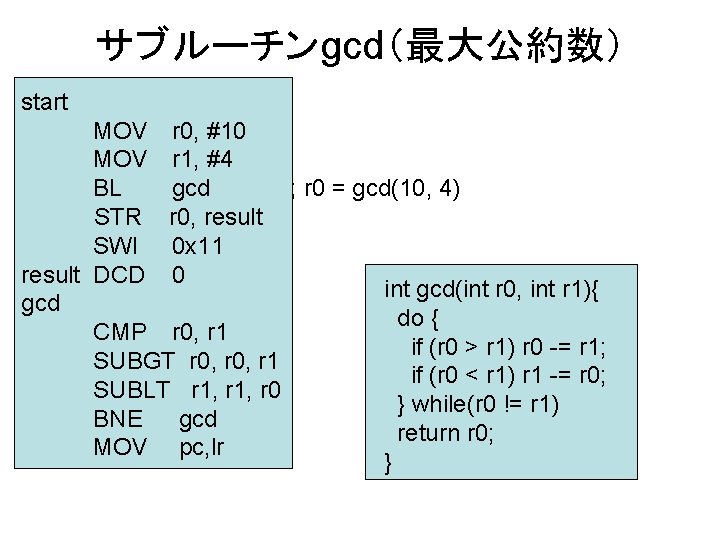

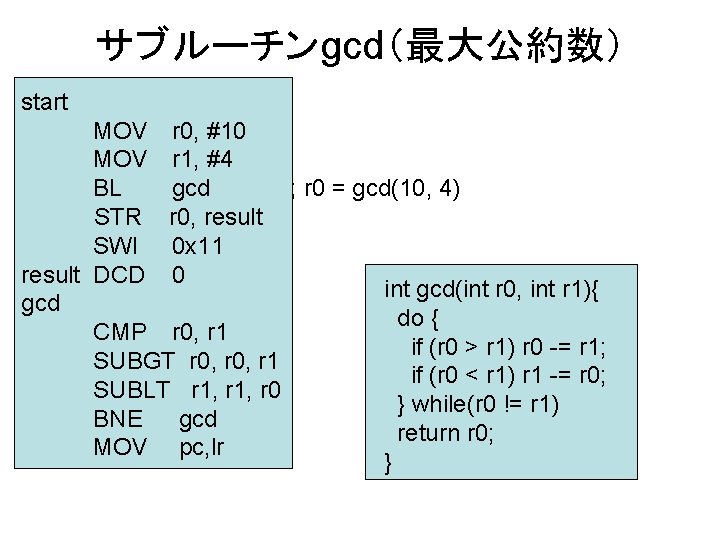

サブルーチンgcd(最大公約数) start MOV r 0, #10 MOV r 1, #4 BL gcd ; r 0 = gcd(10, 4) STR r 0, result SWI 0 x 11 result DCD 0 int gcd(int r 0, int r 1){ gcd do { CMP r 0, r 1 if (r 0 > r 1) r 0 -= r 1; SUBGT r 0, r 1 if (r 0 < r 1) r 1 -= r 0; SUBLT r 1, r 0 } while(r 0 != r 1) BNE gcd return r 0; MOV pc, lr }

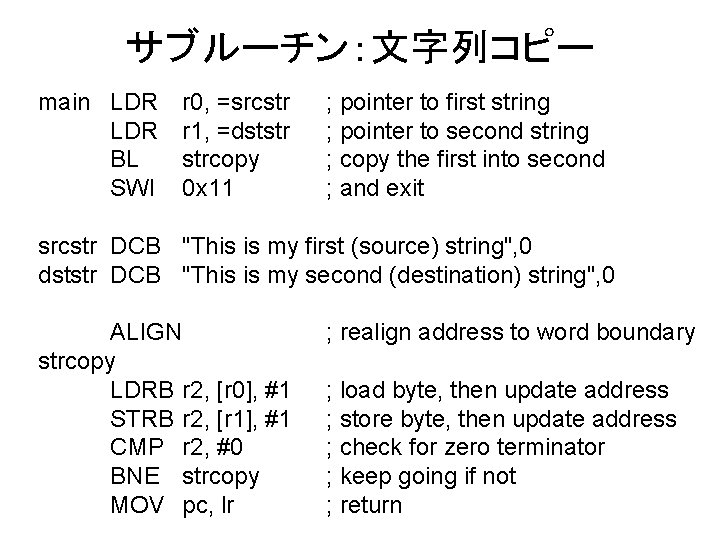

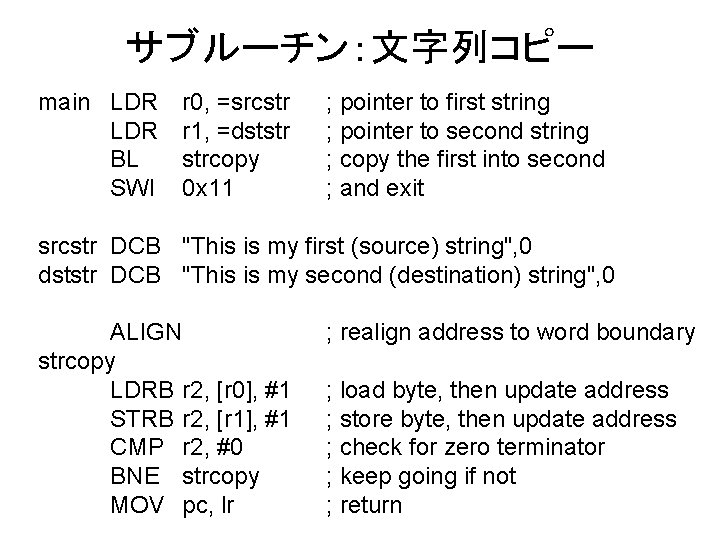

サブルーチン:文字列コピー main LDR BL SWI r 0, =srcstr r 1, =dststr strcopy 0 x 11 ; pointer to first string ; pointer to second string ; copy the first into second ; and exit srcstr DCB "This is my first (source) string", 0 dststr DCB "This is my second (destination) string", 0 ALIGN strcopy LDRB r 2, [r 0], #1 STRB r 2, [r 1], #1 CMP r 2, #0 BNE strcopy MOV pc, lr ; realign address to word boundary ; load byte, then update address ; store byte, then update address ; check for zero terminator ; keep going if not ; return

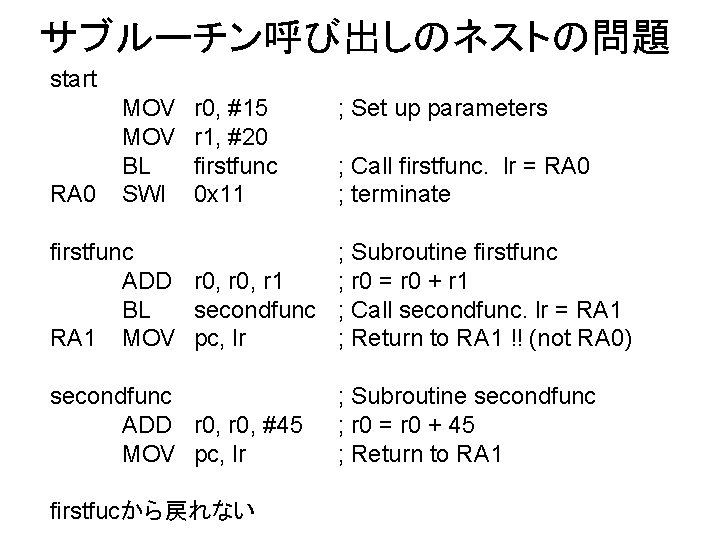

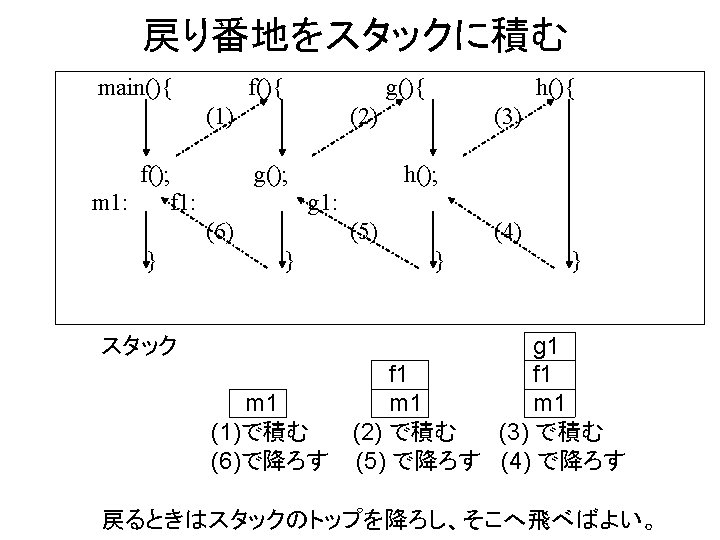

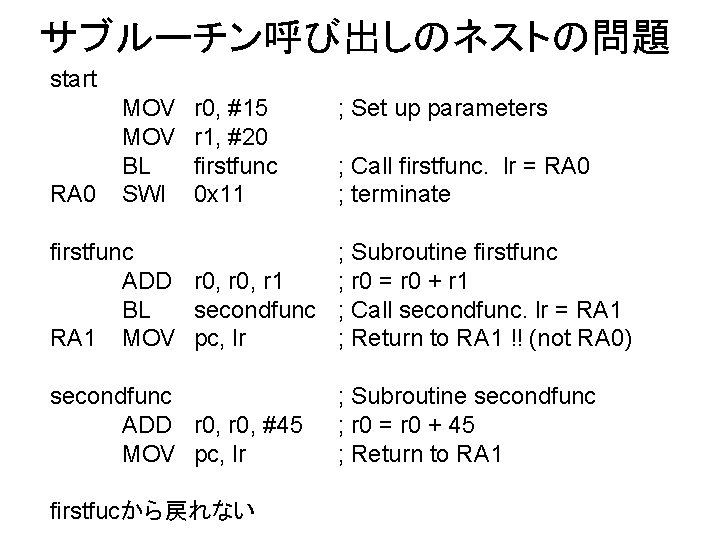

サブルーチン呼び出しのネストの問題 start RA 0 MOV BL SWI r 0, #15 r 1, #20 firstfunc 0 x 11 ; Set up parameters ; Call firstfunc. lr = RA 0 ; terminate firstfunc ADD r 0, r 1 BL secondfunc RA 1 MOV pc, lr ; Subroutine firstfunc ; r 0 = r 0 + r 1 ; Call secondfunc. lr = RA 1 ; Return to RA 1 !! (not RA 0) secondfunc ADD r 0, #45 MOV pc, lr ; Subroutine secondfunc ; r 0 = r 0 + 45 ; Return to RA 1 firstfucから戻れない

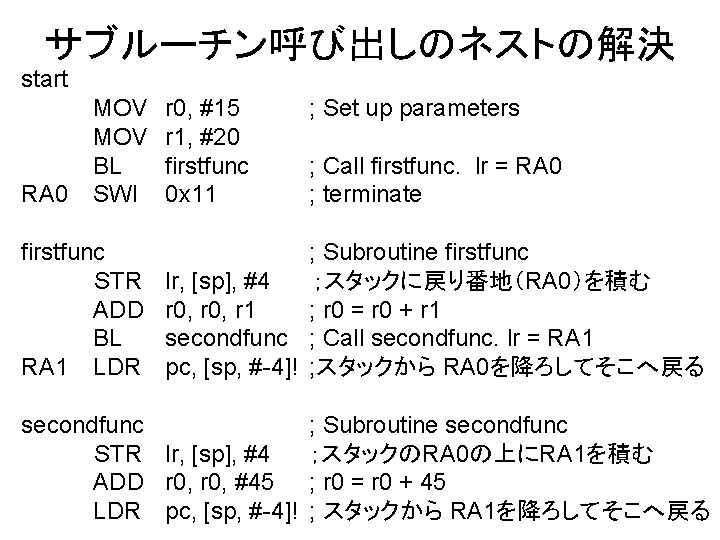

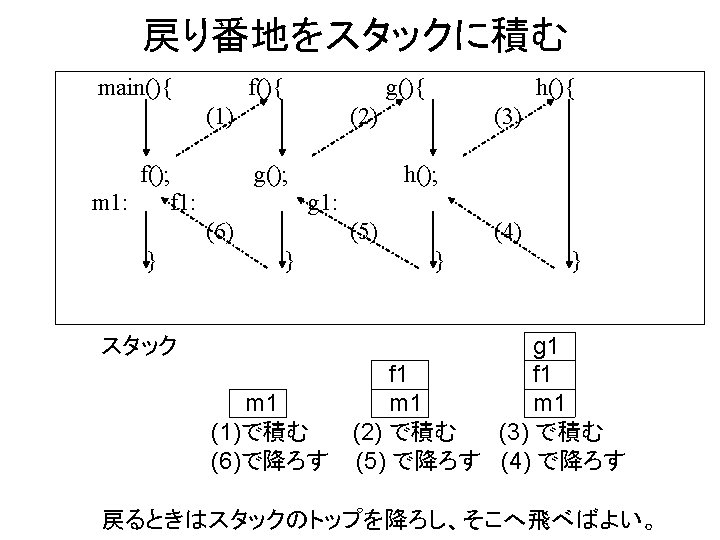

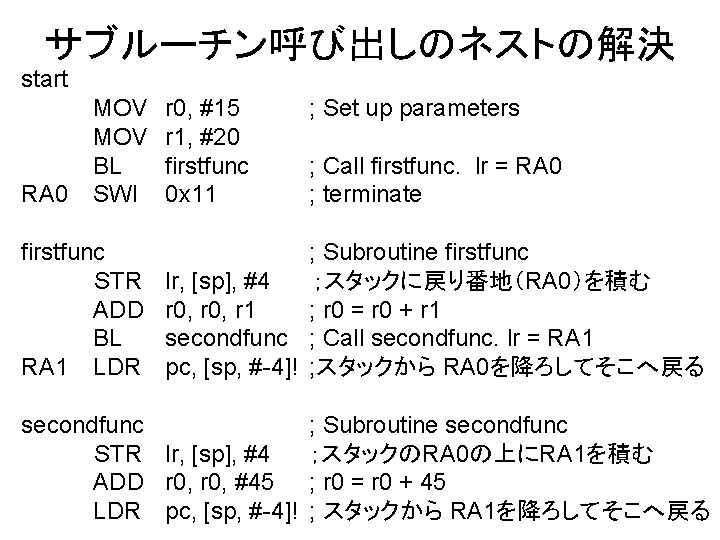

サブルーチン呼び出しのネストの解決 start RA 0 MOV BL SWI firstfunc STR ADD BL RA 1 LDR r 0, #15 r 1, #20 firstfunc 0 x 11 ; Set up parameters ; Call firstfunc. lr = RA 0 ; terminate ; Subroutine firstfunc lr, [sp], #4 ;スタックに戻り番地(RA 0)を積む r 0, r 1 ; r 0 = r 0 + r 1 secondfunc ; Call secondfunc. lr = RA 1 pc, [sp, #-4]! ; スタックから RA 0を降ろしてそこへ戻る secondfunc ; Subroutine secondfunc STR lr, [sp], #4 ;スタックのRA 0の上にRA 1を積む ADD r 0, #45 ; r 0 = r 0 + 45 LDR pc, [sp, #-4]! ; スタックから RA 1を降ろしてそこへ戻る

![fact STR lr sp 4 STR R 0 sp 4 SUBS R 0 1 fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1](https://slidetodoc.com/presentation_image/218512d90a6ac5043fd11b2bcefb4573/image-59.jpg)

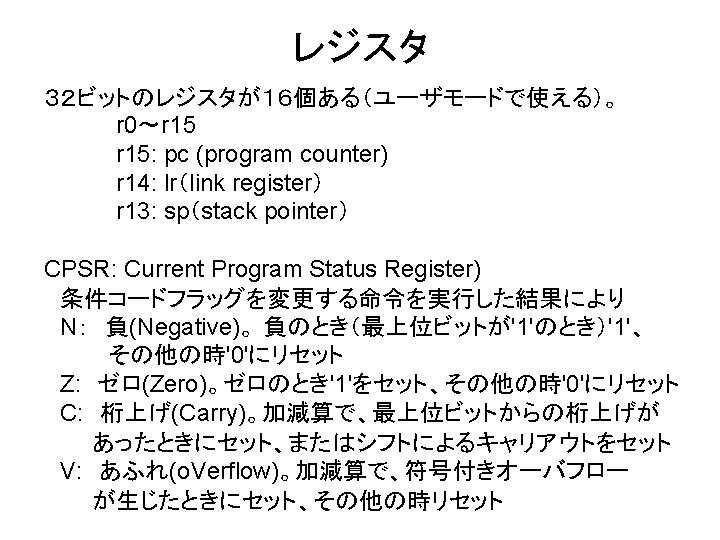

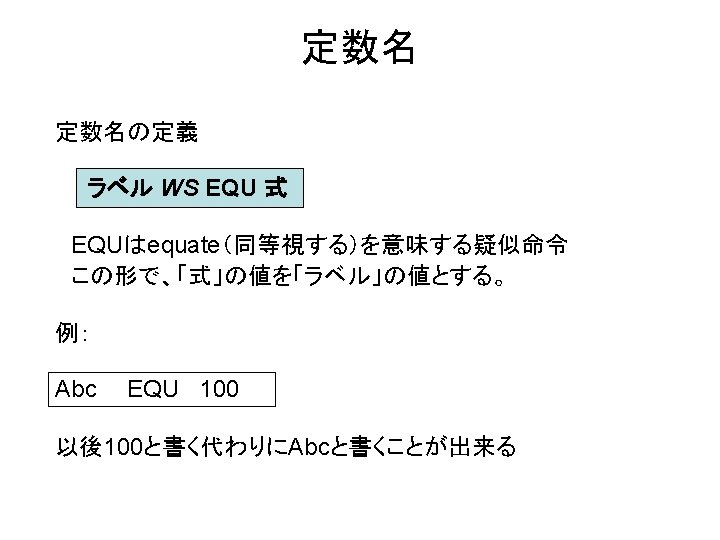

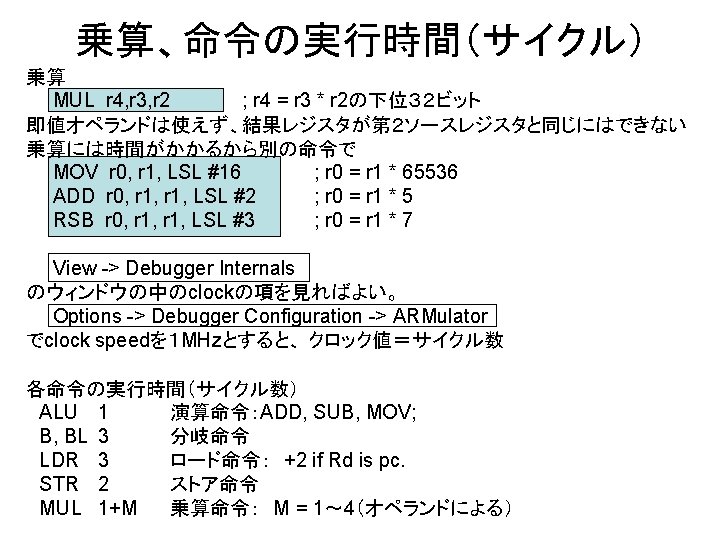

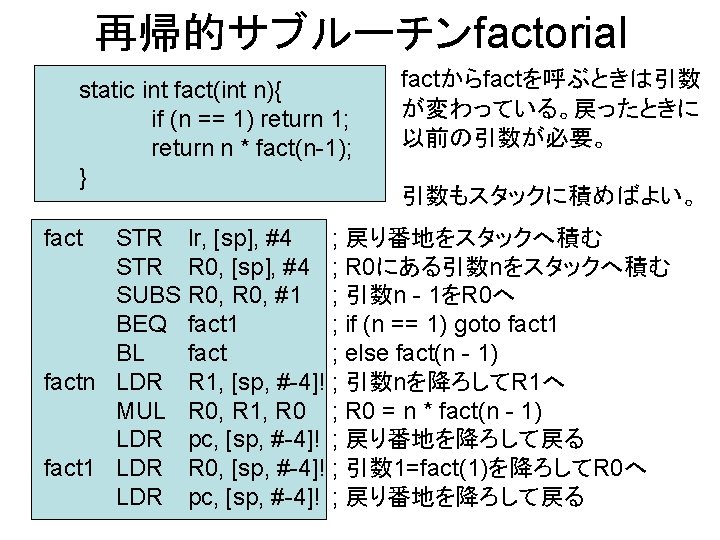

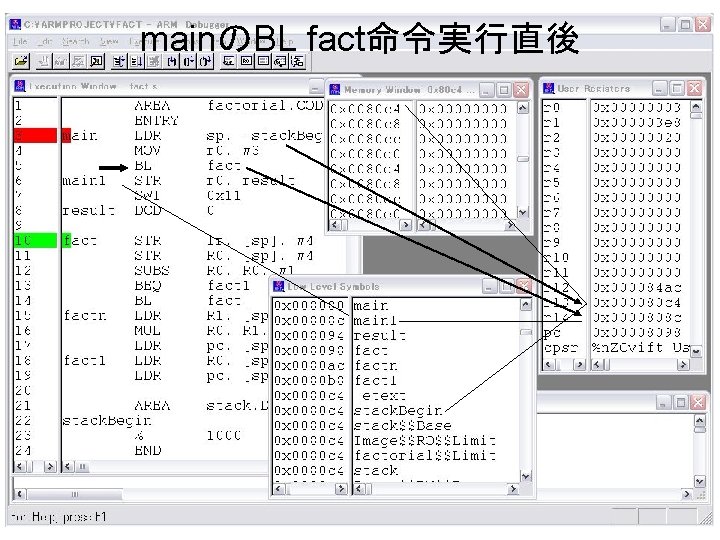

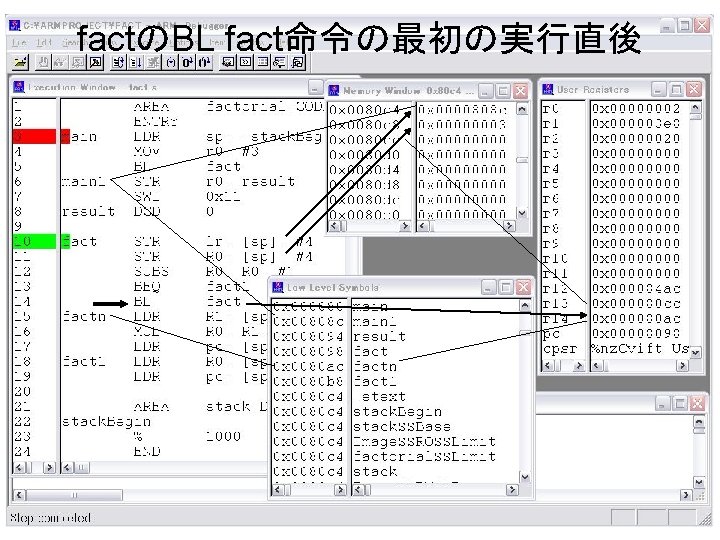

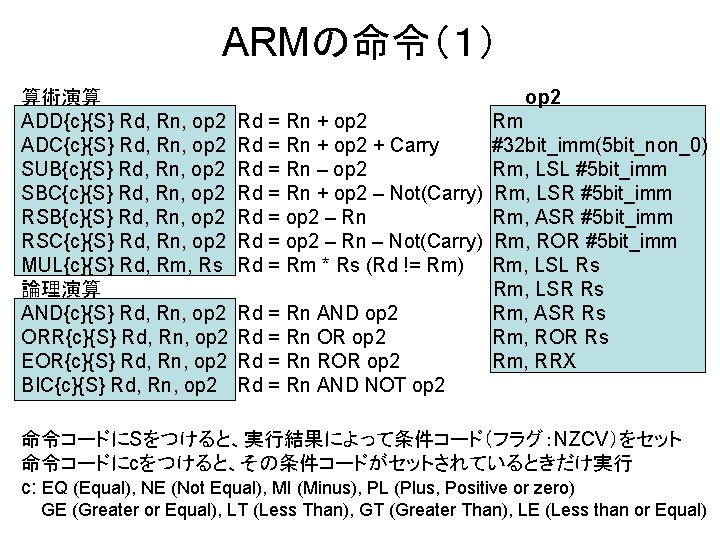

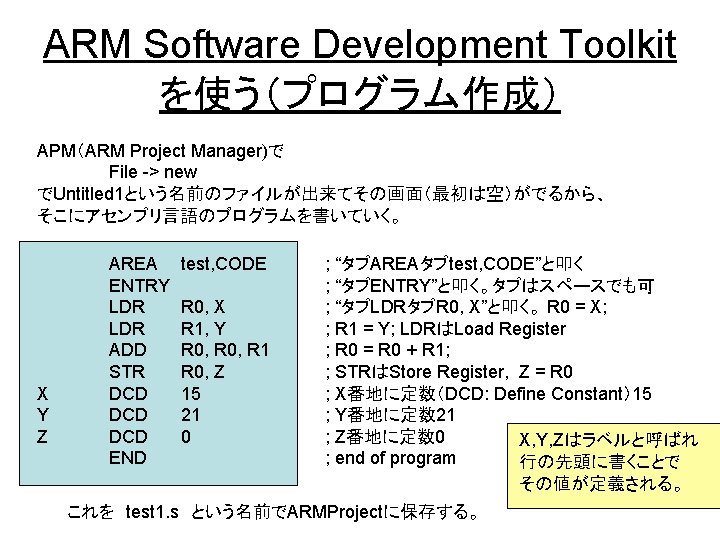

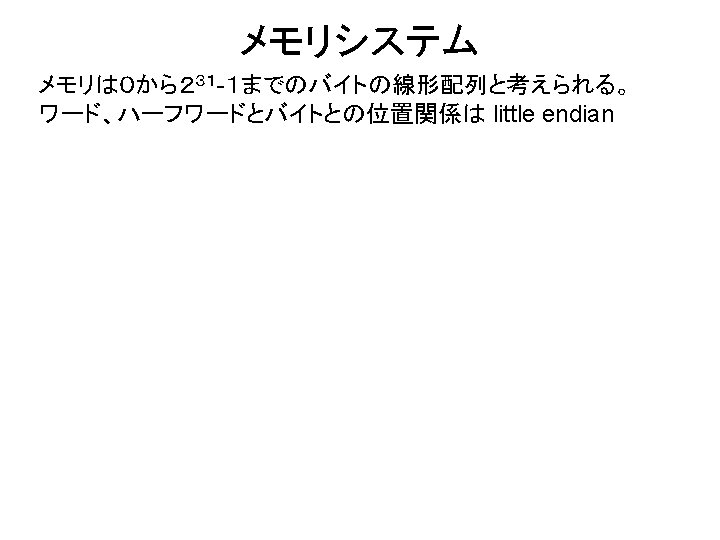

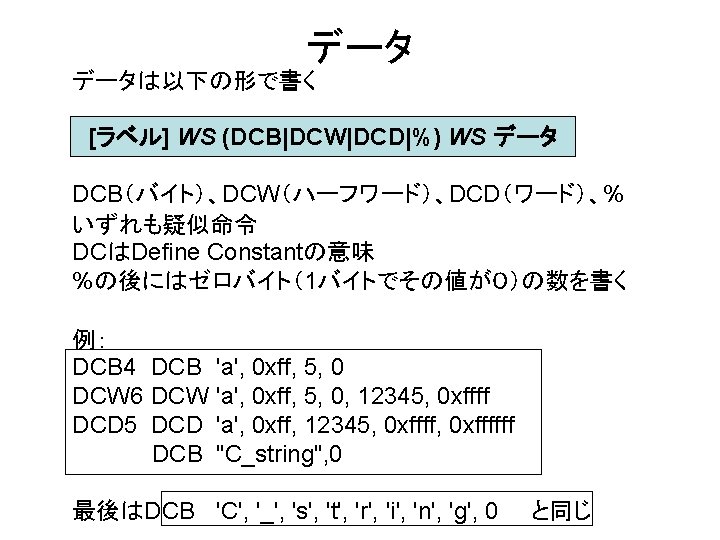

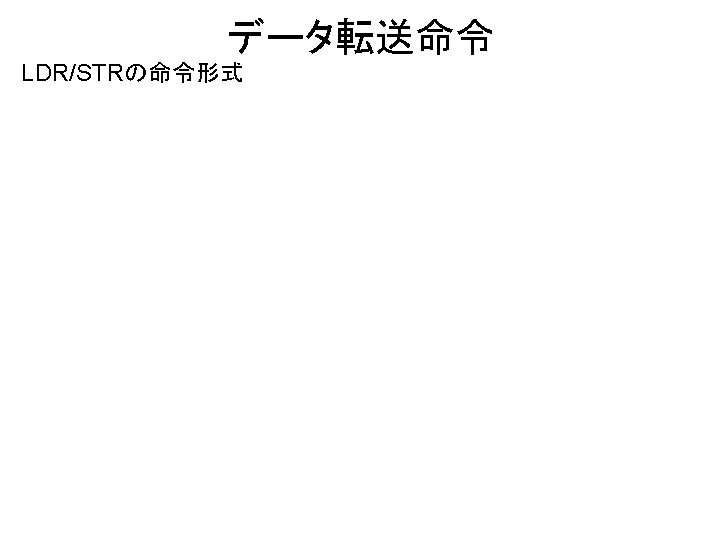

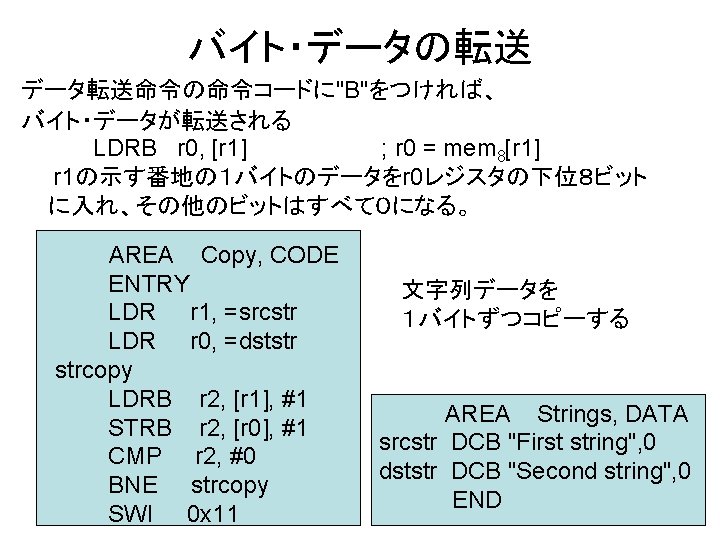

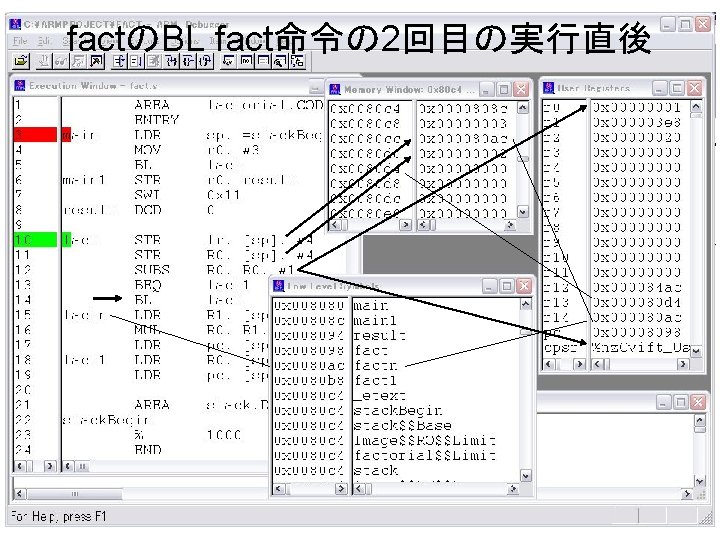

fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1 BEQ fact 1 r 0 3 BL factn LDR R 1, [sp, #-4]! MUL R 0, R 1, R 0 r 13(sp) LDR pc, [sp, #-4]! r 14(lr) main 1 fact 1 LDR R 0, [sp, #-4]! r 15(pc) fact LDR pc, [sp, #-4]! main LDR sp, =stack. Begin MOV R 0, #3 BL fact main 1 STR R 0, result ; result = fact(3) factorialの呼び出し(1) AREA stack, DATA, READWRITE stack. Begin % 1000 スタック

![fact STR lr sp 4 STR R 0 sp 4 SUBS R 0 1 fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1](https://slidetodoc.com/presentation_image/218512d90a6ac5043fd11b2bcefb4573/image-61.jpg)

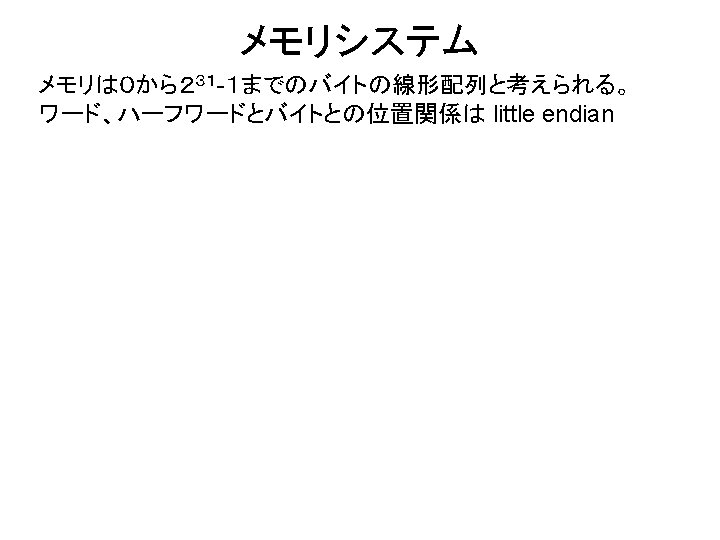

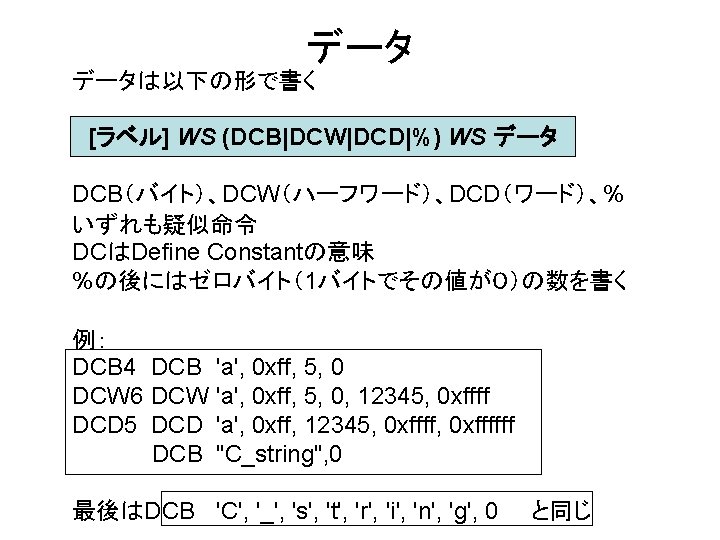

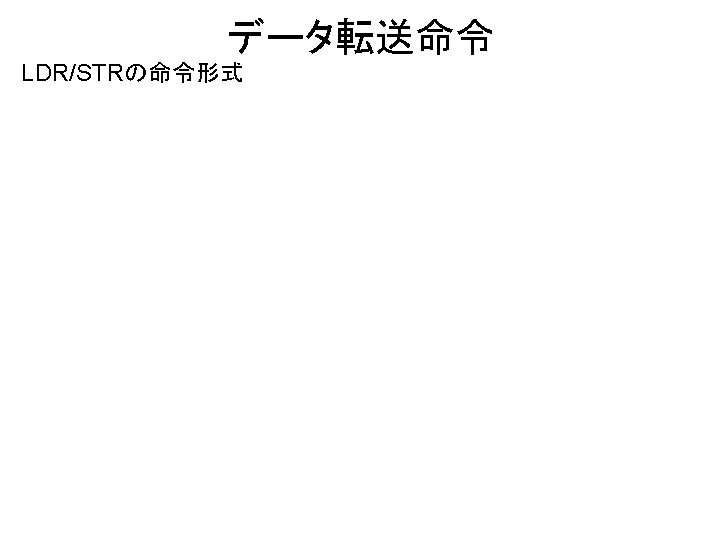

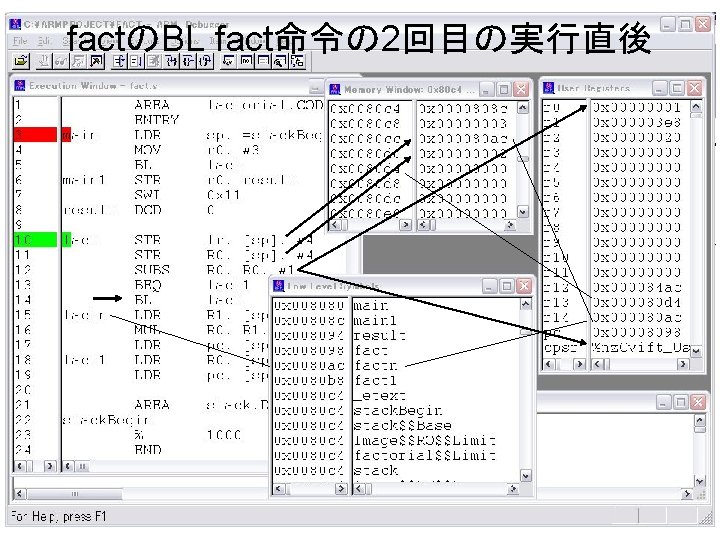

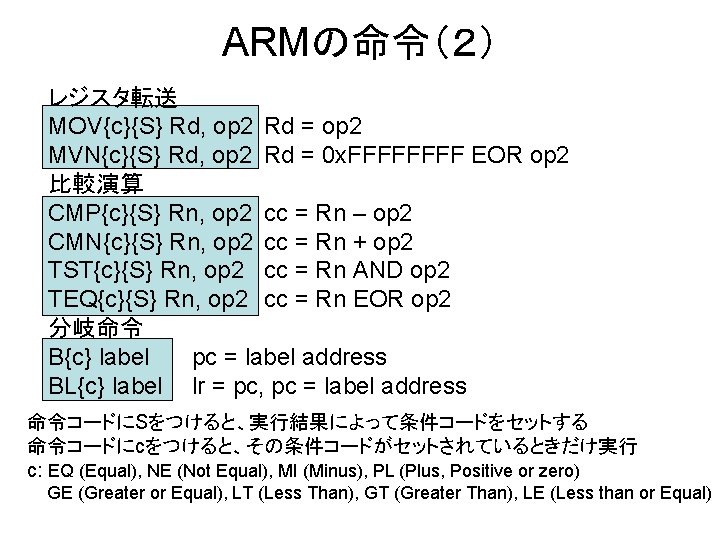

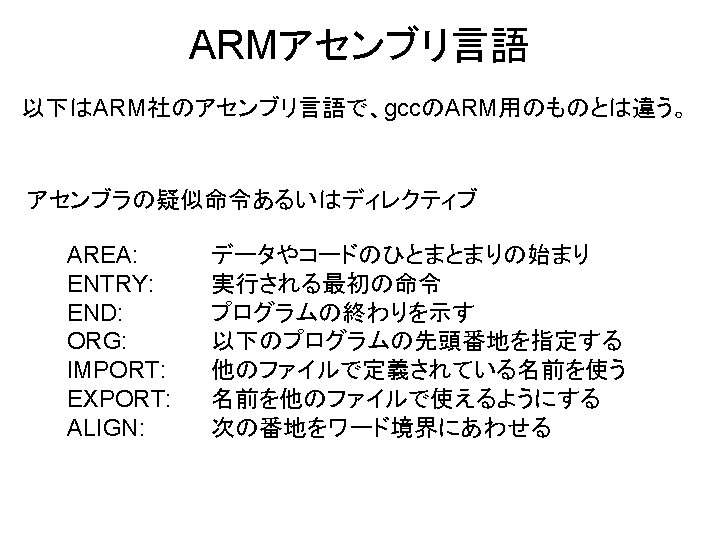

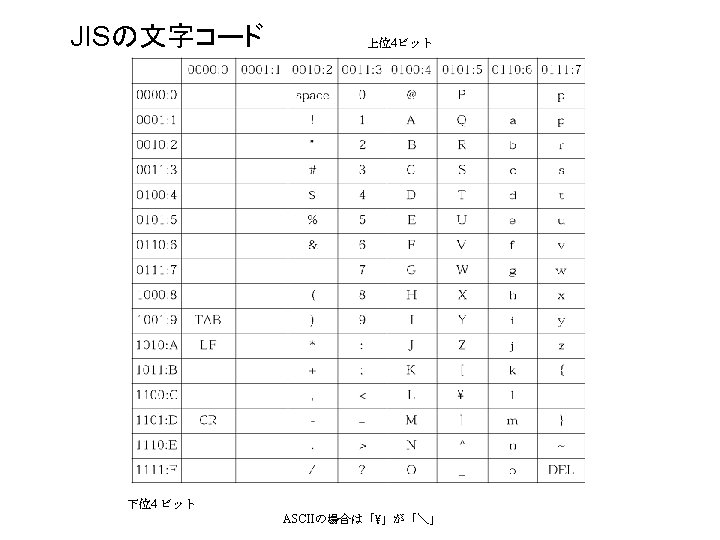

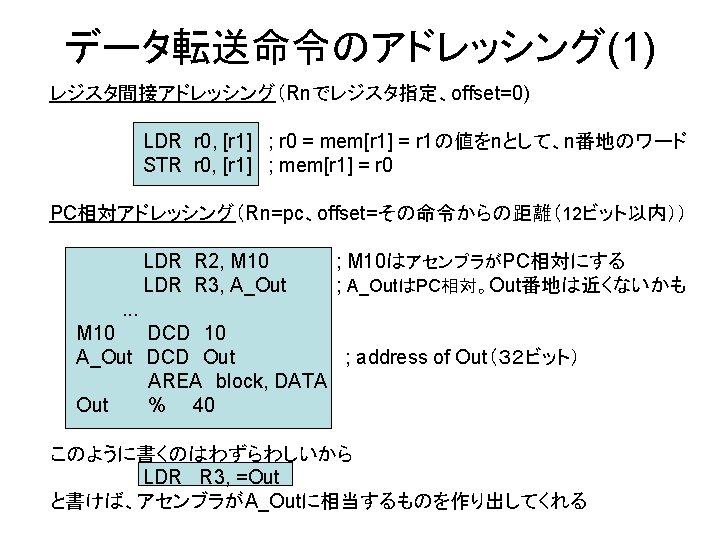

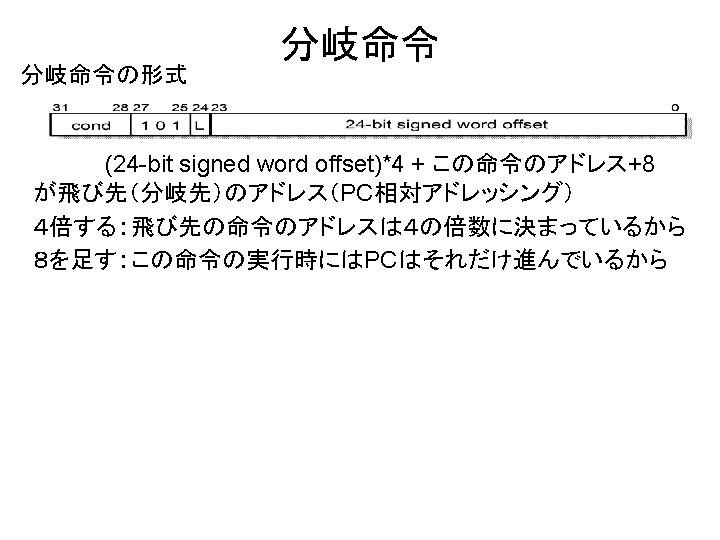

fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1 BEQ fact 1 r 0 2 BL factn LDR R 1, [sp, #-4]! MUL R 0, R 1, R 0 r 13(sp) LDR pc, [sp, #-4]! r 14(lr) factn fact 1 LDR R 0, [sp, #-4]! r 15(pc) fact LDR pc, [sp, #-4]! main LDR sp, =stack. Begin MOV R 0, #3 BL fact main 1 STR R 0, result ; result = fact(3) factorialの呼び出し(2) AREA stack, DATA, READWRITE stack. Begin % 1000 3 main 1 スタック

![fact STR lr sp 4 STR R 0 sp 4 SUBS R 0 1 fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1](https://slidetodoc.com/presentation_image/218512d90a6ac5043fd11b2bcefb4573/image-63.jpg)

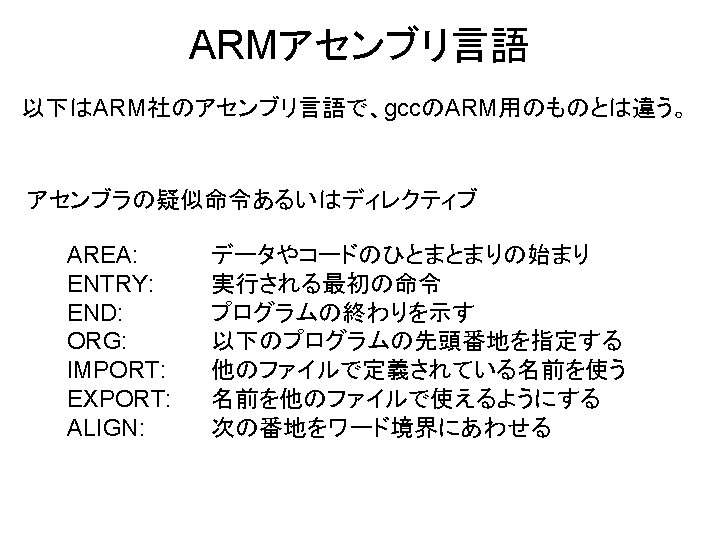

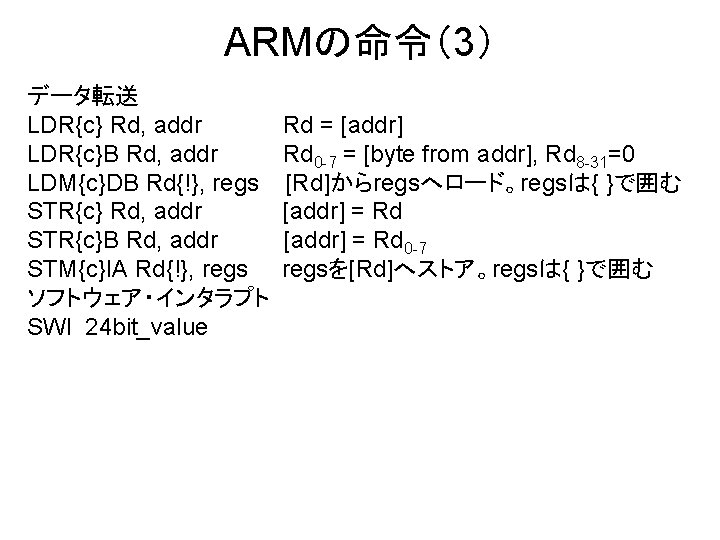

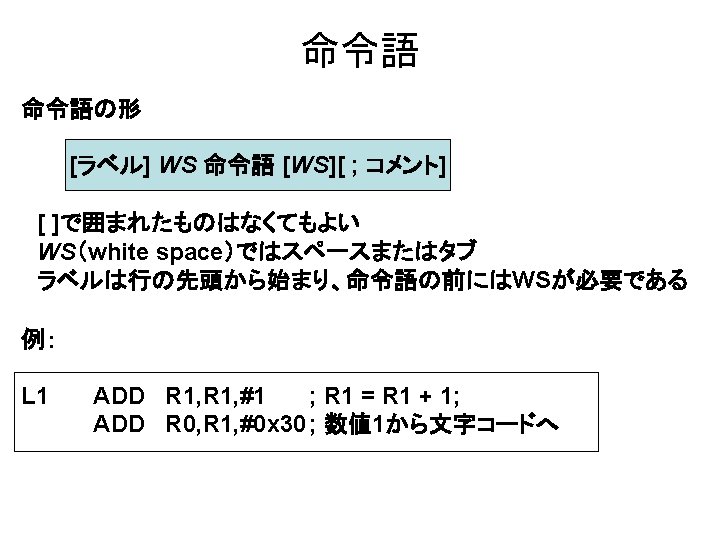

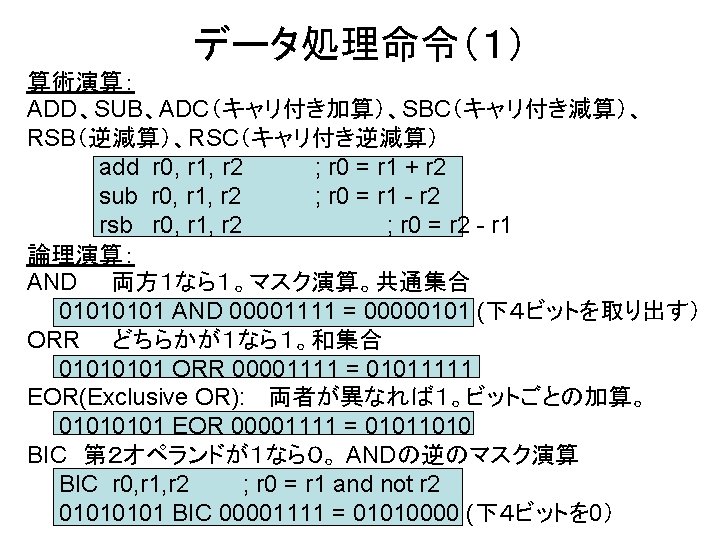

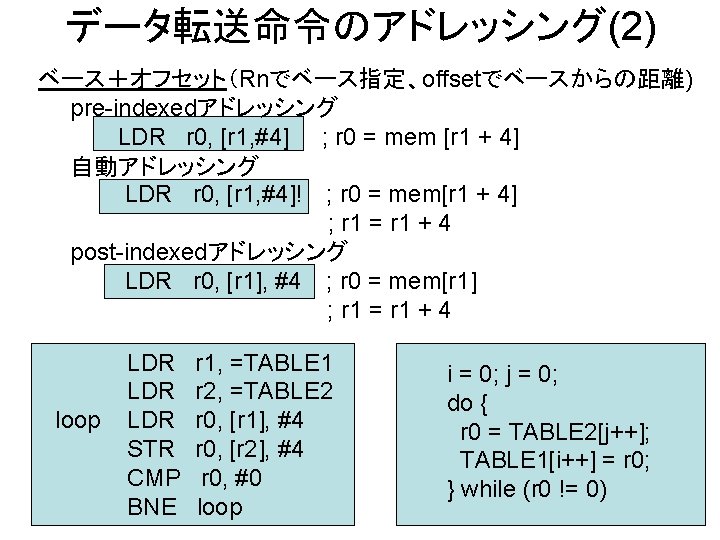

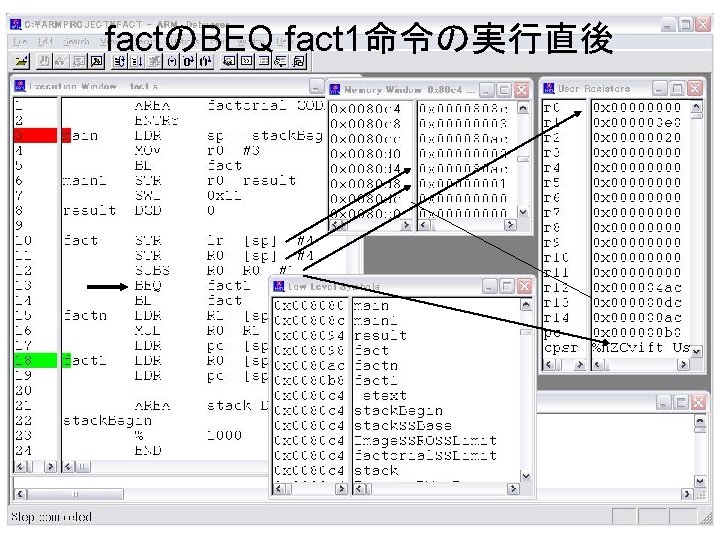

fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1 BEQ fact 1 r 0 1 BL factn LDR R 1, [sp, #-4]! MUL R 0, R 1, R 0 r 13(sp) LDR pc, [sp, #-4]! r 14(lr) factn fact 1 LDR R 0, [sp, #-4]! r 15(pc) fact LDR pc, [sp, #-4]! main LDR sp, =stack. Begin MOV R 0, #3 BL fact main 1 STR R 0, result ; result = fact(3) factorialの呼び出し(3) AREA stack, DATA, READWRITE stack. Begin % 1000 2 factn 3 main 1 スタック

![fact STR lr sp 4 STR R 0 sp 4 SUBS R 0 1 fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1](https://slidetodoc.com/presentation_image/218512d90a6ac5043fd11b2bcefb4573/image-65.jpg)

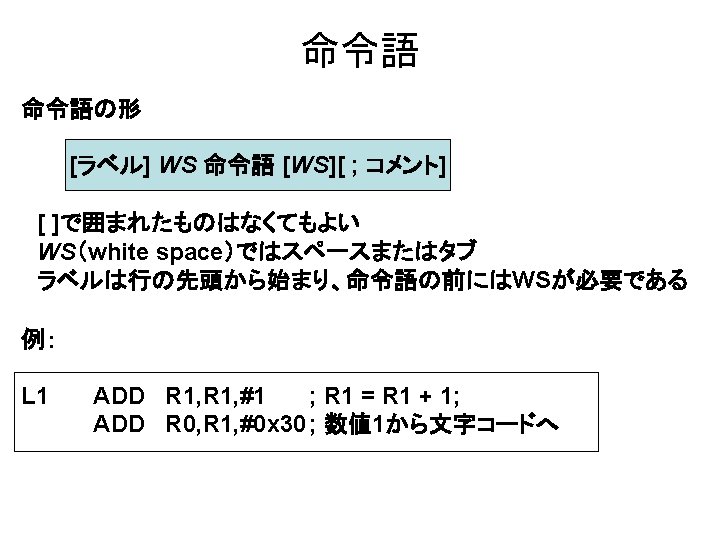

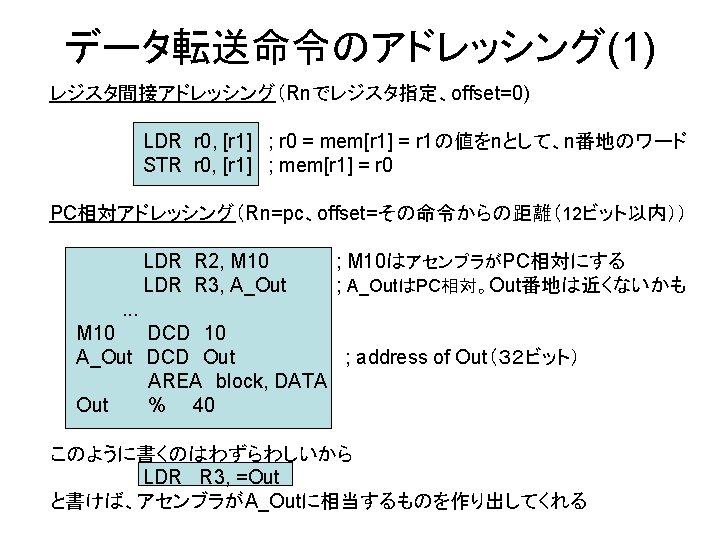

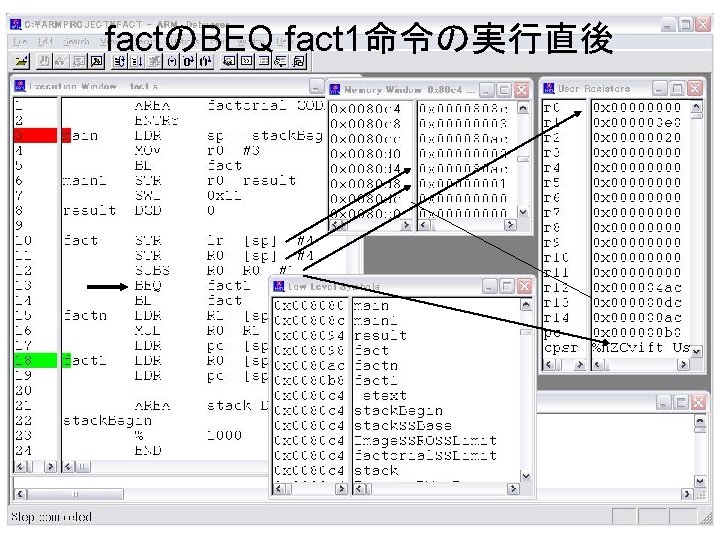

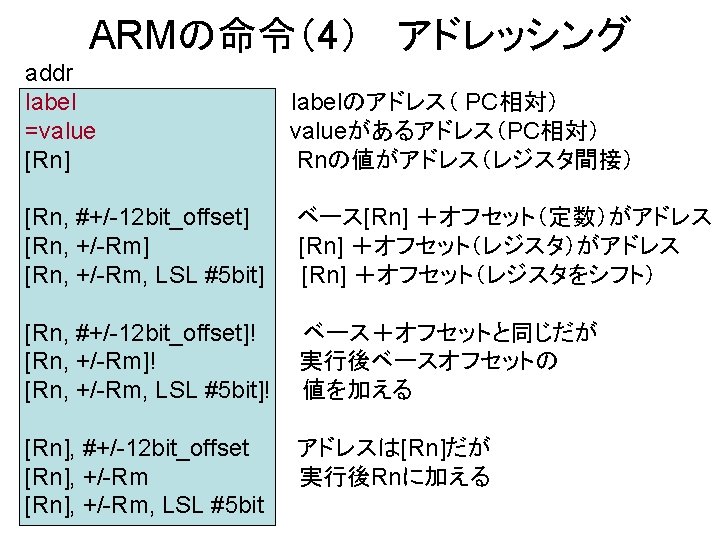

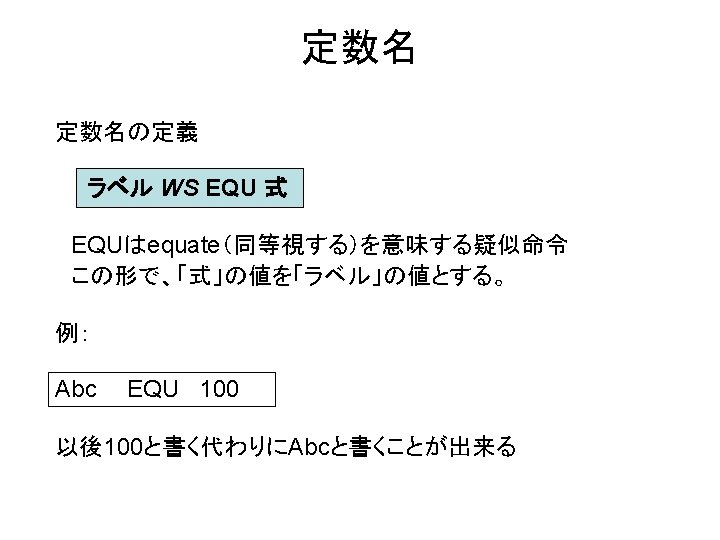

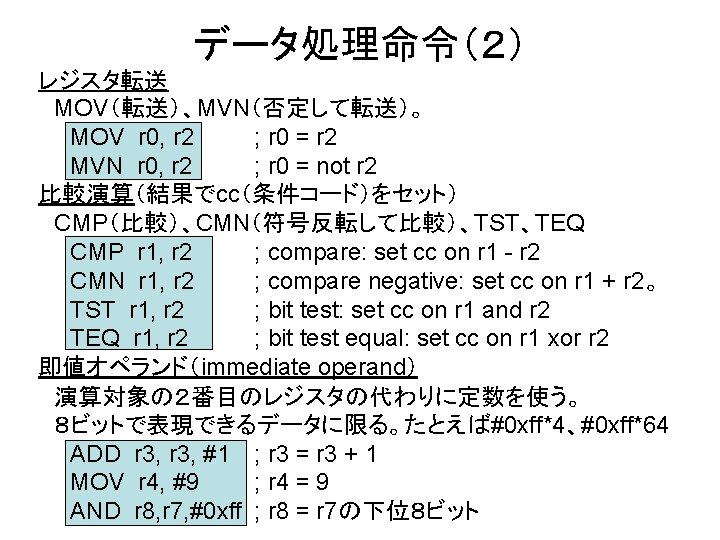

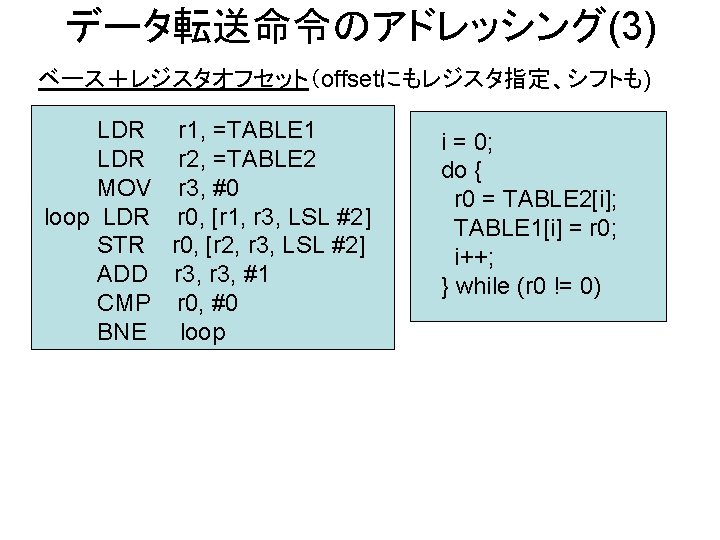

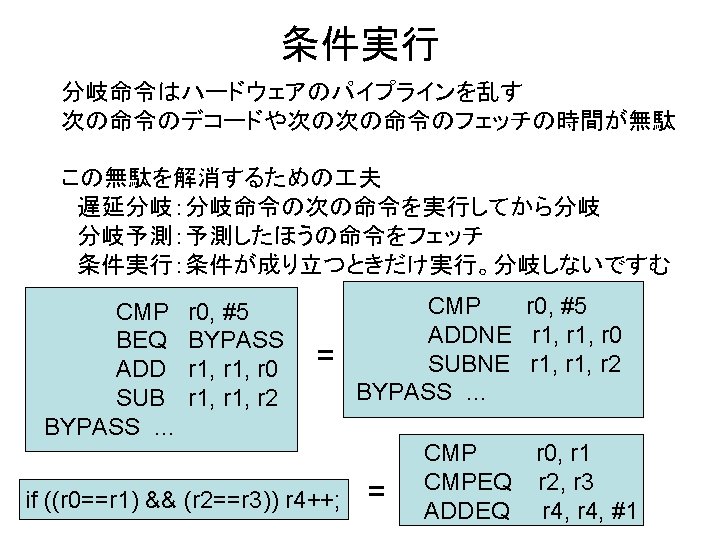

fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1 BEQ fact 1 r 0 0 BL factn LDR R 1, [sp, #-4]! MUL R 0, R 1, R 0 r 13(sp) LDR pc, [sp, #-4]! r 14(lr) factn fact 1 LDR R 0, [sp, #-4]! r 15(pc) fact 1 LDR pc, [sp, #-4]! main LDR sp, =stack. Begin MOV R 0, #3 BL fact main 1 STR R 0, result ; result = fact(3) factorialの呼び出し(4) AREA stack, DATA, READWRITE stack. Begin % 1000 1 factn 2 factn 3 main 1 スタック

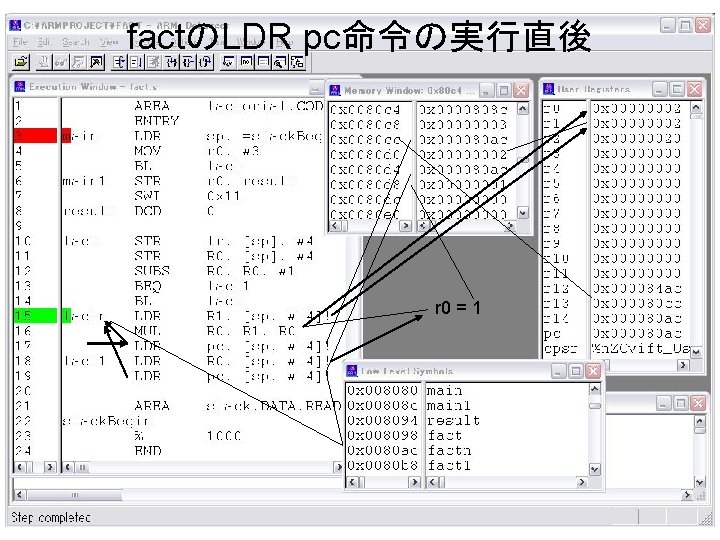

![fact STR lr sp 4 STR R 0 sp 4 SUBS R 0 1 fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1](https://slidetodoc.com/presentation_image/218512d90a6ac5043fd11b2bcefb4573/image-67.jpg)

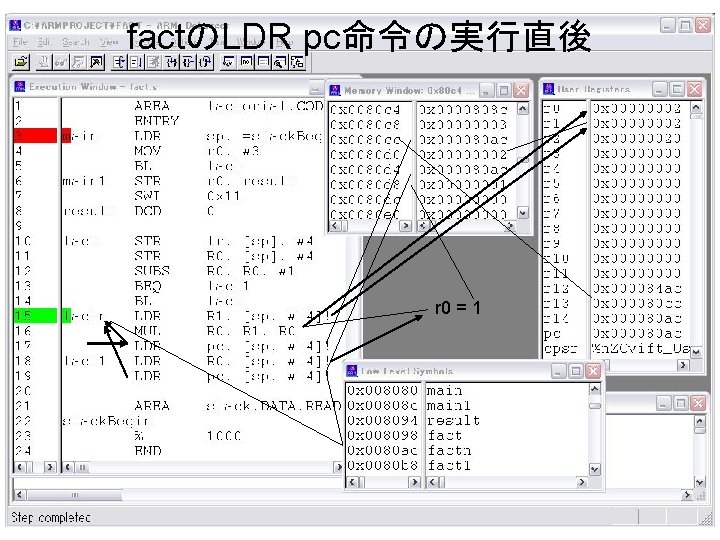

fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1 BEQ fact 1 r 0 1 BL factn LDR R 1, [sp, #-4]! MUL R 0, R 1, R 0 r 13(sp) LDR pc, [sp, #-4]! r 14(lr) factn fact 1 LDR R 0, [sp, #-4]! r 15(pc) factn LDR pc, [sp, #-4]! main LDR sp, =stack. Begin MOV R 0, #3 BL fact main 1 STR R 0, result ; result = fact(3) factorialの呼び出し(5) AREA stack, DATA, READWRITE stack. Begin % 1000 1 factn 2 factn 3 main 1 スタック

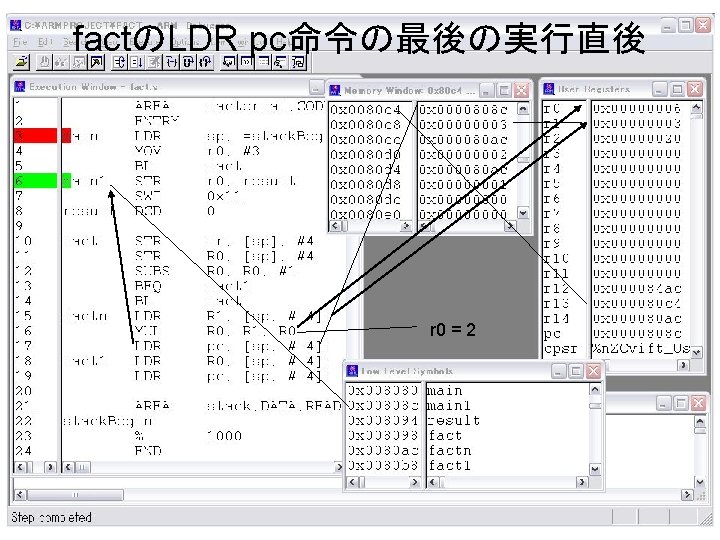

![fact STR lr sp 4 STR R 0 sp 4 SUBS R 0 1 fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1](https://slidetodoc.com/presentation_image/218512d90a6ac5043fd11b2bcefb4573/image-68.jpg)

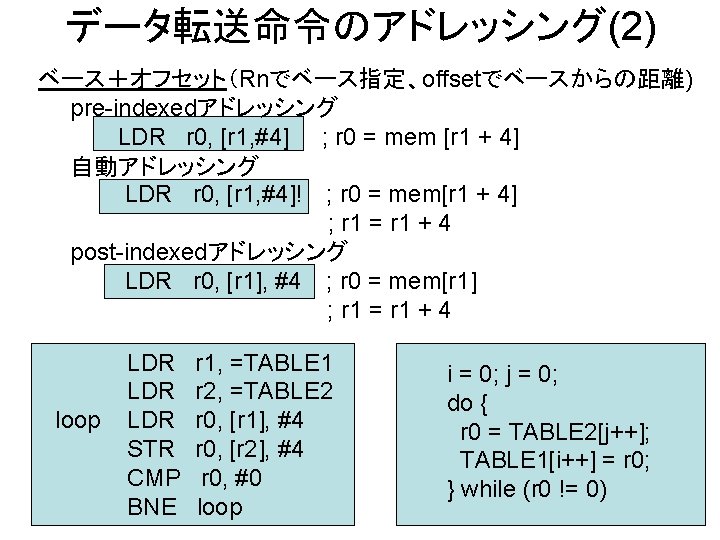

fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1 BEQ fact 1 r 0 2 BL fact r 1 2 factn LDR R 1, [sp, #-4]! MUL R 0, R 1, R 0 r 13(sp) LDR pc, [sp, #-4]! r 14(lr) factn fact 1 LDR R 0, [sp, #-4]! r 15(pc) factn LDR pc, [sp, #-4]! main LDR sp, =stack. Begin MOV R 0, #3 BL fact main 1 STR R 0, result ; result = fact(3) factorialの呼び出し(6) AREA stack, DATA, READWRITE stack. Begin % 1000 1 factn 2 factn 3 main 1 スタック

![fact STR lr sp 4 STR R 0 sp 4 SUBS R 0 1 fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1](https://slidetodoc.com/presentation_image/218512d90a6ac5043fd11b2bcefb4573/image-70.jpg)

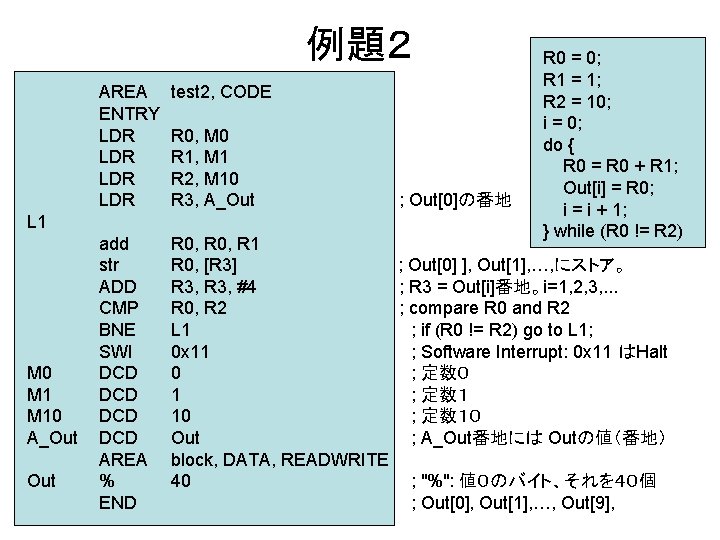

fact STR lr, [sp], #4 STR R 0, [sp], #4 SUBS R 0, #1 BEQ fact 1 r 0 6 BL fact r 1 3 factn LDR R 1, [sp, #-4]! MUL R 0, R 1, R 0 r 13(sp) LDR pc, [sp, #-4]! r 14(lr) factn fact 1 LDR R 0, [sp, #-4]! r 15(pc) main 1 LDR pc, [sp, #-4]! main LDR sp, =stack. Begin MOV R 0, #3 BL fact main 1 STR R 0, result ; result = fact(3) factorialの呼び出し(7) AREA stack, DATA, READWRITE stack. Begin % 1000 1 factn 2 factn 3 main 1 スタック

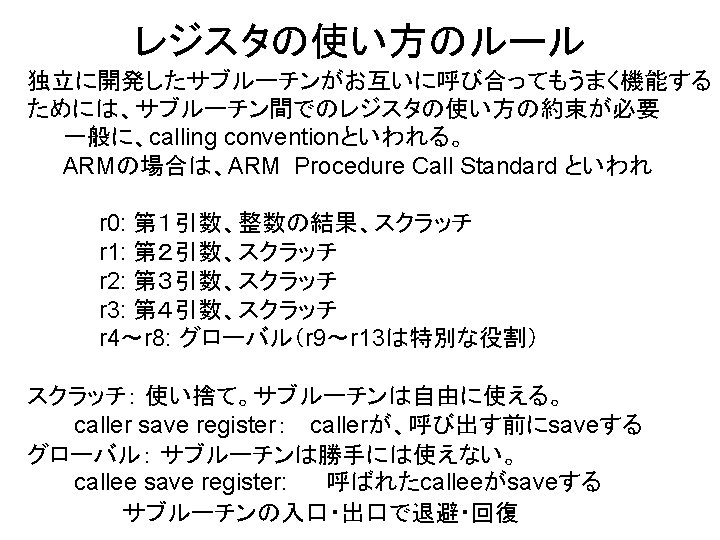

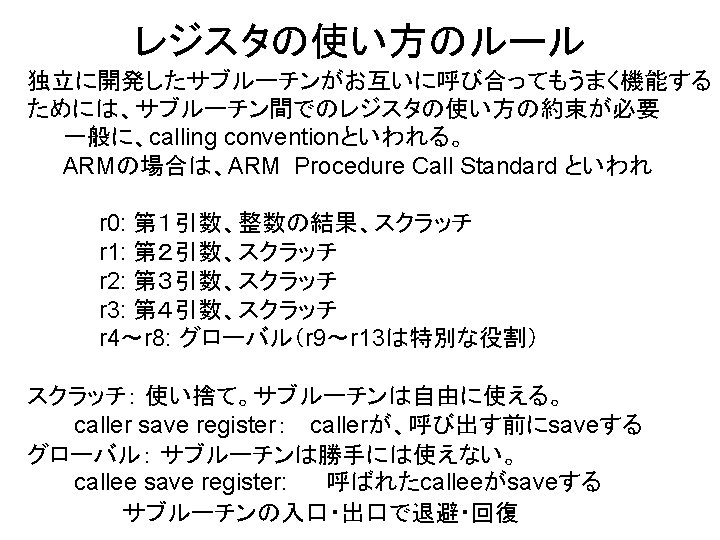

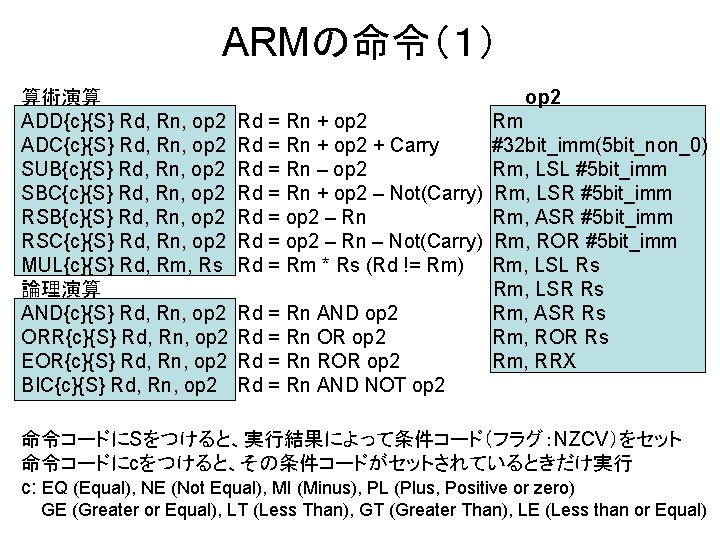

サブルーチンfactorial ルールに従ってレジスタの退避・回復を行う lr(戻り番地: callee save)、r 4(callee save)を使うから fact STMIA sp!, {r 4, lr} MOV r 4, r 0 SUBS r 0, #1 BEQ fact 1 BL factn MUL r 0, r 4, r 0 LDMDB sp!, {r 4, pc} fact 1 MOV r 0, #1 LDMDB sp!, {r 4, pc} ; 戻り番地とr 4をスタックへ退避 ; r 4 = n ; 引数n - 1をr 0へ ; if (n == 1) goto fact 1 ; else fact(n - 1) ; r 0 = n * fact(n - 1) ; スタックから回復してreturn ; r 0 = 1 ( = fact(1) ) ; スタックから回復してreturn

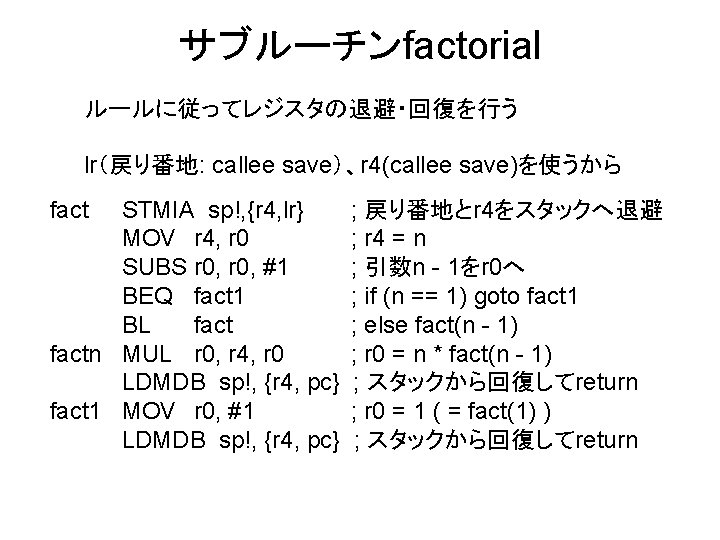

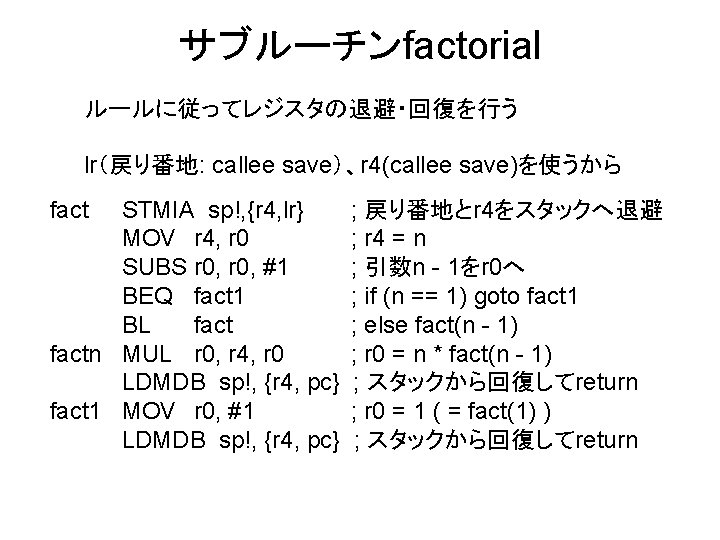

複数ファイルで構成するプロジェクト ファイルfactsub. s ファイルfactmain. s IMPORT fact AREA factmain, CODE ENTRY main LDR sp, =stack. Begin MOV r 0, #3 BL fact main 1 STR r 0, result SWI 0 x 11 result DCD 0 AREA stack, DATA stack. Begin % 1000 END EXPORT fact AREA factsub, CODE fact STMIA sp!, {r 4, lr} MOV r 4, r 0 SUBS r 0, #1 BEQ fact 1 BL factn MUL r 0, r 4, r 0 LDMDB sp!, {r 4, pc} fact 1 MOV r 0, #1 LDMDB sp!, {r 4, pc} END 別のファイルでの定義名を使うときは、 定義側でEXPORT、使う側でIMPORT

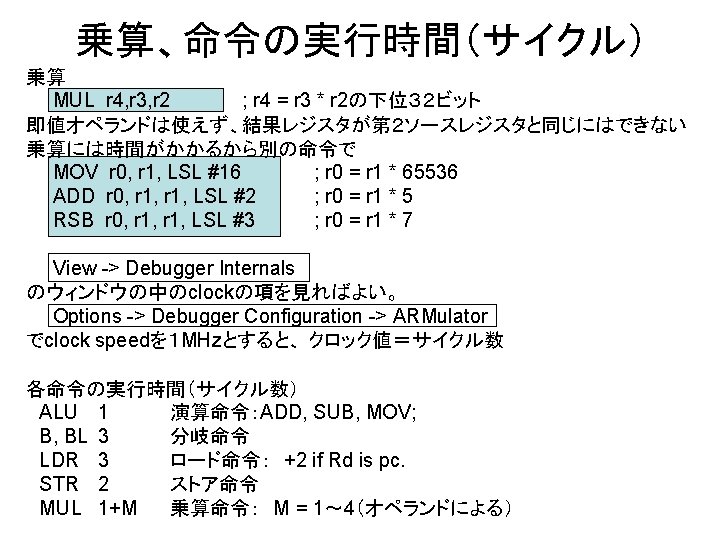

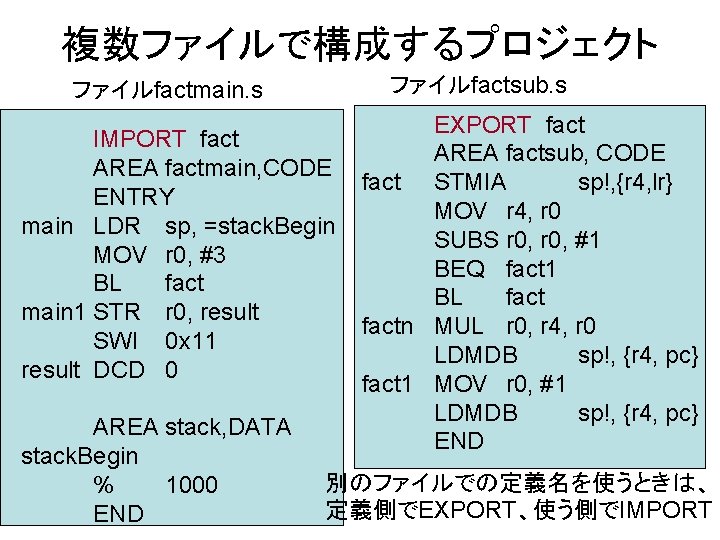

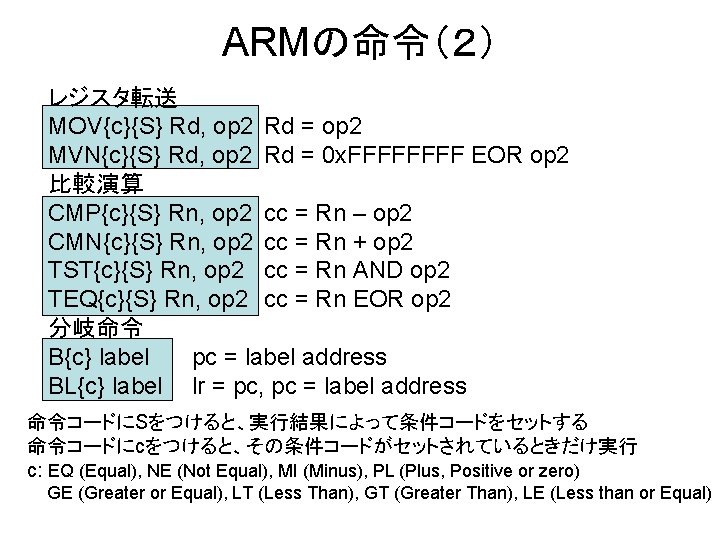

ARMの命令(1) 算術演算 ADD{c}{S} Rd, Rn, op 2 ADC{c}{S} Rd, Rn, op 2 SUB{c}{S} Rd, Rn, op 2 SBC{c}{S} Rd, Rn, op 2 RSB{c}{S} Rd, Rn, op 2 RSC{c}{S} Rd, Rn, op 2 MUL{c}{S} Rd, Rm, Rs 論理演算 AND{c}{S} Rd, Rn, op 2 ORR{c}{S} Rd, Rn, op 2 EOR{c}{S} Rd, Rn, op 2 BIC{c}{S} Rd, Rn, op 2 Rd = Rn + op 2 + Carry Rd = Rn – op 2 Rd = Rn + op 2 – Not(Carry) Rd = op 2 – Rn – Not(Carry) Rd = Rm * Rs (Rd != Rm) Rd = Rn AND op 2 Rd = Rn OR op 2 Rd = Rn ROR op 2 Rd = Rn AND NOT op 2 Rm #32 bit_imm(5 bit_non_0) Rm, LSL #5 bit_imm Rm, LSR #5 bit_imm Rm, ASR #5 bit_imm Rm, ROR #5 bit_imm Rm, LSL Rs Rm, LSR Rs Rm, ASR Rs Rm, ROR Rs Rm, RRX 命令コードにSをつけると、実行結果によって条件コード(フラグ:NZCV)をセット 命令コードにcをつけると、その条件コードがセットされているときだけ実行 c: EQ (Equal), NE (Not Equal), MI (Minus), PL (Plus, Positive or zero) GE (Greater or Equal), LT (Less Than), GT (Greater Than), LE (Less than or Equal)

ARMの命令(2) レジスタ転送 MOV{c}{S} Rd, op 2 Rd = op 2 MVN{c}{S} Rd, op 2 Rd = 0 x. FFFF EOR op 2 比較演算 CMP{c}{S} Rn, op 2 cc = Rn – op 2 CMN{c}{S} Rn, op 2 cc = Rn + op 2 TST{c}{S} Rn, op 2 cc = Rn AND op 2 TEQ{c}{S} Rn, op 2 cc = Rn EOR op 2 分岐命令 B{c} label pc = label address BL{c} label lr = pc, pc = label address 命令コードにSをつけると、実行結果によって条件コードをセットする 命令コードにcをつけると、その条件コードがセットされているときだけ実行 c: EQ (Equal), NE (Not Equal), MI (Minus), PL (Plus, Positive or zero) GE (Greater or Equal), LT (Less Than), GT (Greater Than), LE (Less than or Equal)

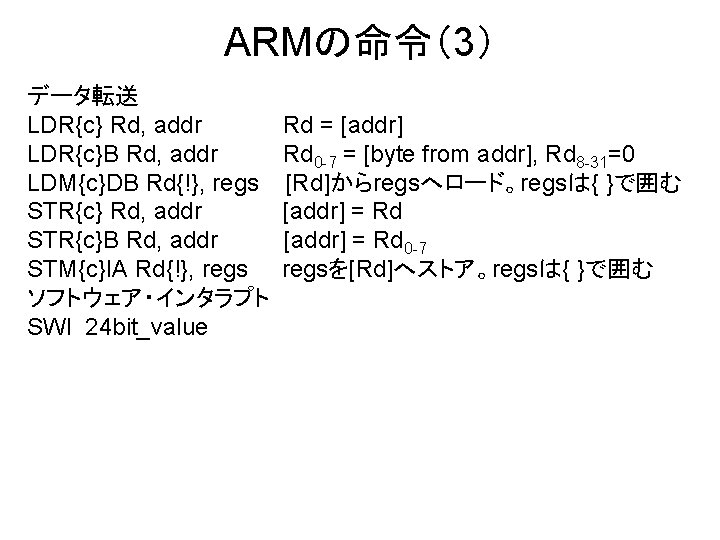

ARMの命令(3) データ転送 LDR{c} Rd, addr LDR{c}B Rd, addr LDM{c}DB Rd{!}, regs STR{c} Rd, addr STR{c}B Rd, addr STM{c}IA Rd{!}, regs ソフトウェア・インタラプト SWI 24 bit_value Rd = [addr] Rd 0 -7 = [byte from addr], Rd 8 -31=0 [Rd]からregsへロード。regsは{ }で囲む [addr] = Rd 0 -7 regsを[Rd]へストア。regsは{ }で囲む