UnitI Advanced Processors ARM 7 ARM 9 ARM

- Slides: 34

Unit-I Advanced Processors ARM 7, ARM 9 & ARM 11 Processors

Contents • • • Introduction to ARM processors and it’s versions ARM 7, ARM 9 &ARM 11 features Advantages and suitability in embedded application Registers, CPSR, SPSR ARM and RISC design philosophy ARM 7 data flow model Programmers model Modes of operations Introduction to Tiva TM 4 C 123 G series overview Programming model Tivaware Library

Contents • • • Introduction to ARM processors and it’s versions ARM 7, ARM 9 &ARM 11 features Advantages and suitability in embedded application Registers, CPSR, SPSR ARM and RISC design philosophy ARM 7 data flow model Programmers model Modes of operations Introduction to Tiva TM 4 C 123 G series overview Programming model Tivaware Library

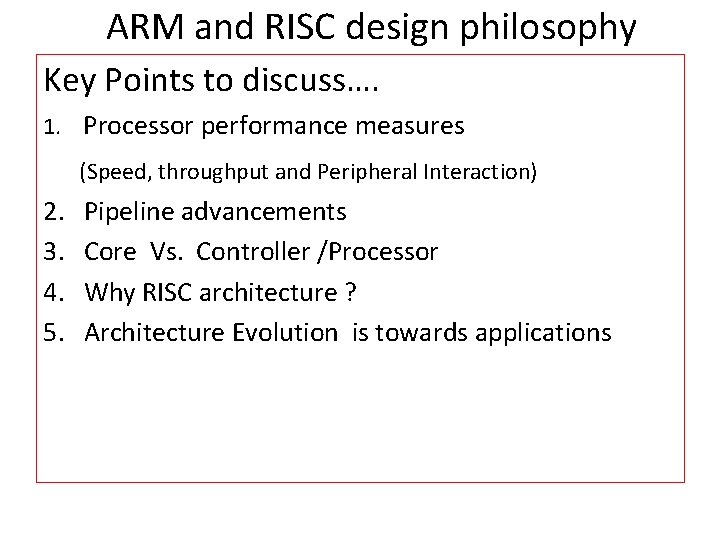

ARM and RISC design philosophy Key Points to discuss…. 1. Processor performance measures (Speed, throughput and Peripheral Interaction) 2. 3. 4. 5. Pipeline advancements Core Vs. Controller /Processor Why RISC architecture ? Architecture Evolution is towards applications

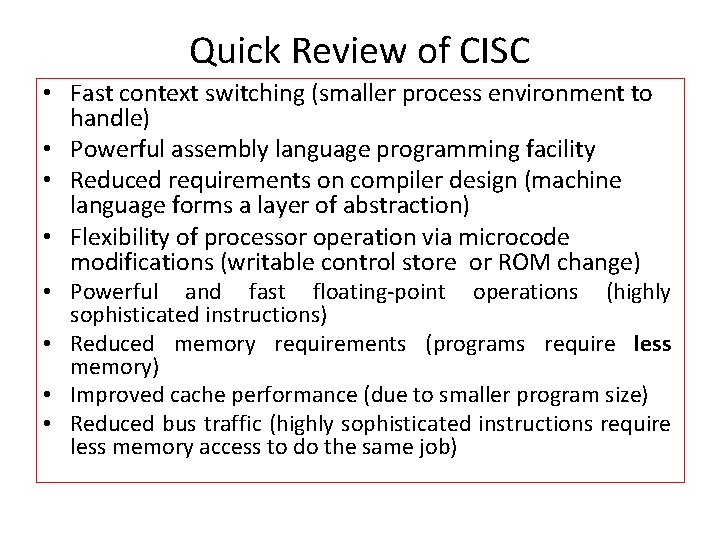

Quick Review of CISC • Fast context switching (smaller process environment to handle) • Powerful assembly language programming facility • Reduced requirements on compiler design (machine language forms a layer of abstraction) • Flexibility of processor operation via microcode modifications (writable control store or ROM change) • Powerful and fast floating-point operations (highly sophisticated instructions) • Reduced memory requirements (programs require less memory) • Improved cache performance (due to smaller program size) • Reduced bus traffic (highly sophisticated instructions require less memory access to do the same job)

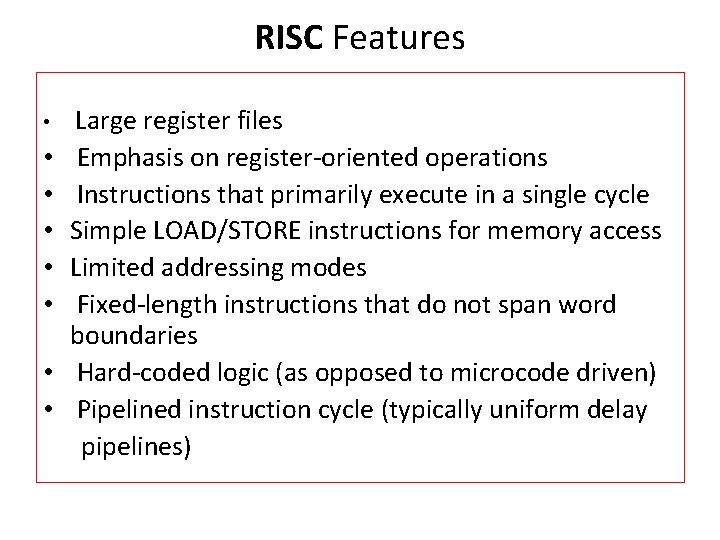

RISC Features • • Large register files Emphasis on register-oriented operations Instructions that primarily execute in a single cycle Simple LOAD/STORE instructions for memory access Limited addressing modes Fixed-length instructions that do not span word boundaries Hard-coded logic (as opposed to microcode driven) Pipelined instruction cycle (typically uniform delay pipelines)

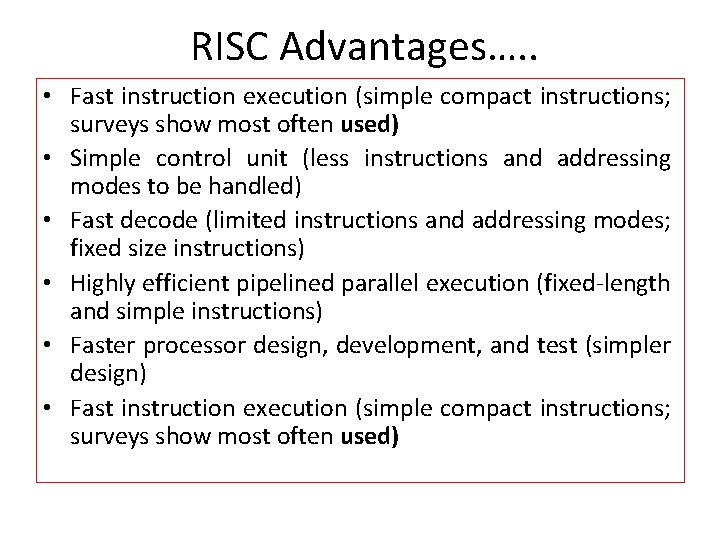

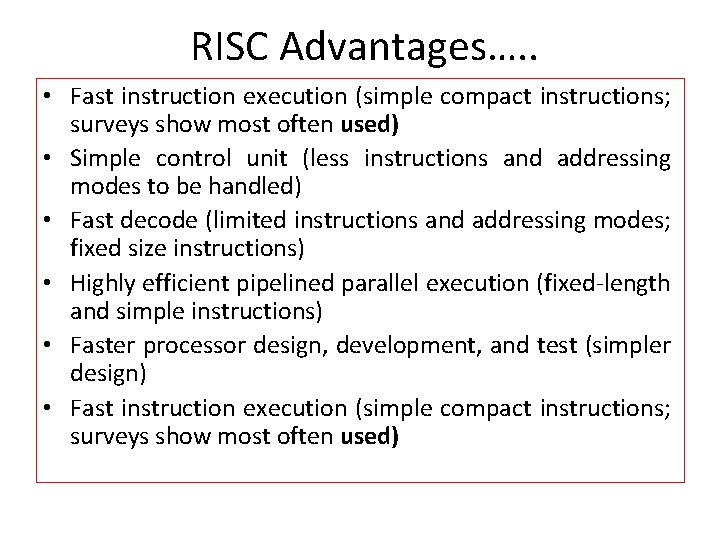

RISC Advantages…. . • Fast instruction execution (simple compact instructions; surveys show most often used) • Simple control unit (less instructions and addressing modes to be handled) • Fast decode (limited instructions and addressing modes; fixed size instructions) • Highly efficient pipelined parallel execution (fixed-length and simple instructions) • Faster processor design, development, and test (simpler design) • Fast instruction execution (simple compact instructions; surveys show most often used)

RISC Advantages…. . • Improved optimizing compiler support (simple machine language generally preferred) • Reduced pipeline branching penalties (due to delayed branch technique used in many RISCs) • Improved subroutine parameter passing speed (register windows) • ……………………………. .

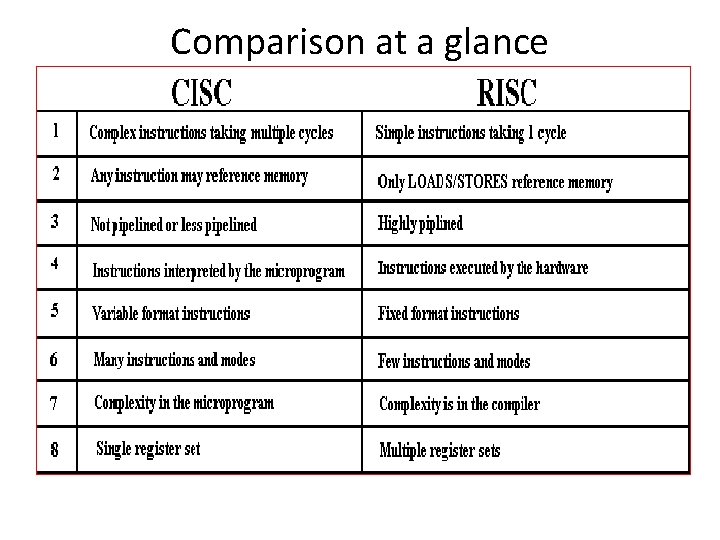

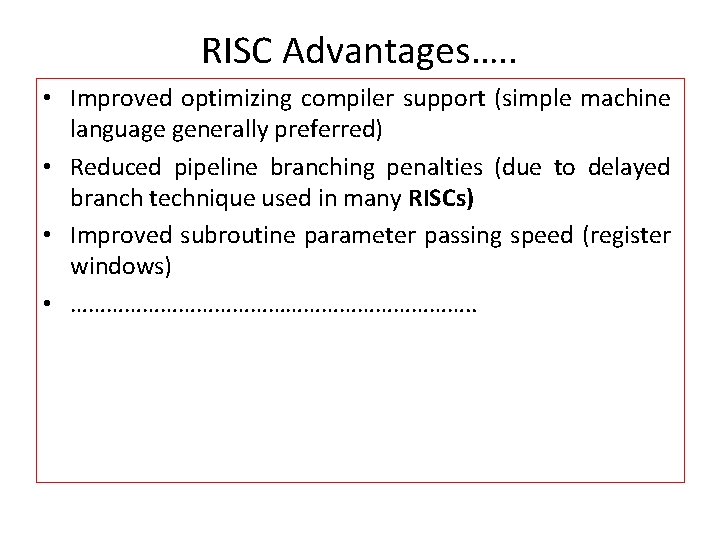

Comparison at a glance

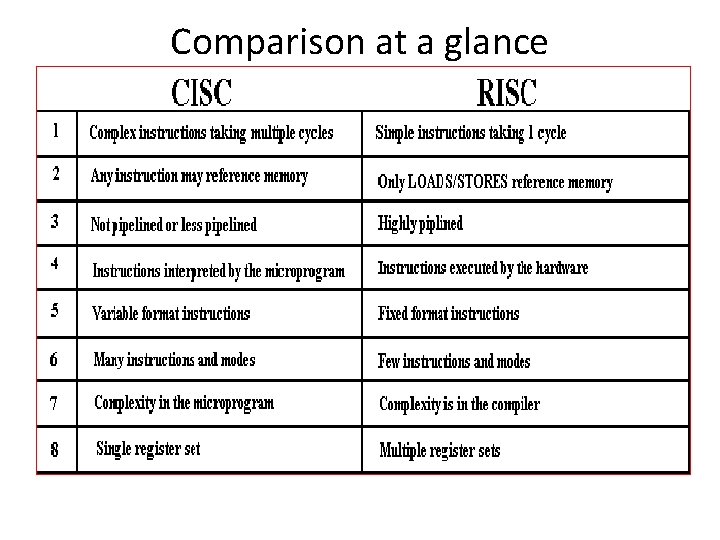

RISC Design Philosophy • Instruction • Pipeline • Registers • Load and store

Early days Today's trend

ARM Design Philosophy advantages /Suitability towards Embedded System Hardware Aspect (Technology Perspective) • Low Power • High code density • Reduced die area • Adoption of standard bus architecture • Hardware debug technology

ARM Design Philosophy advantages /Suitability towards Embedded System Software Aspect (Developers’ Perspective) • Variable cycle executions for certain Instructions • • Inline barrel shifter Thumb Instruction Conditional Execution Enhanced Instructions

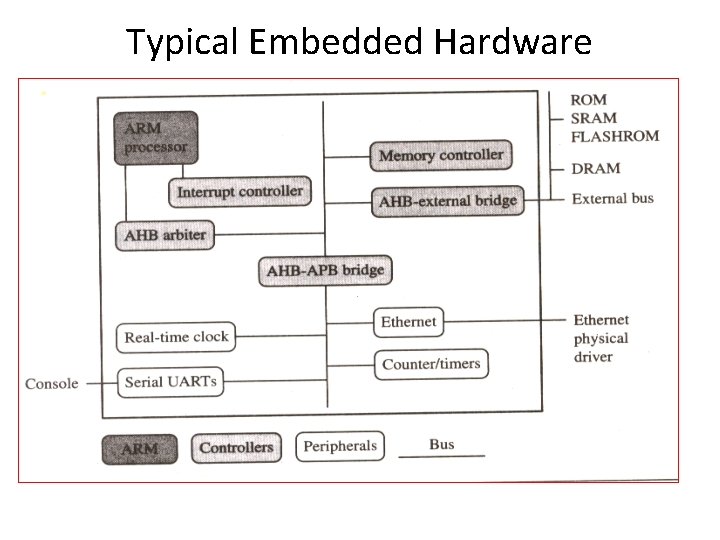

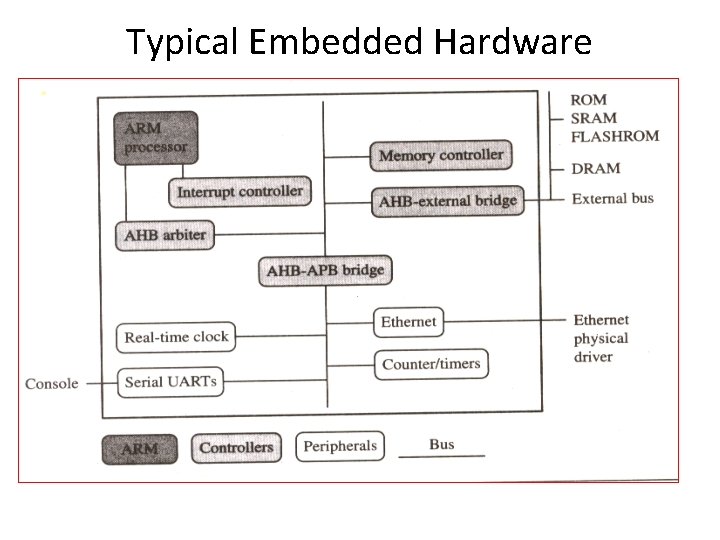

Typical Embedded Hardware

Typical ARM Feature. . • Large Uniform Register file • Load /store architecture • Simple addressing modes • Uniform and simple Instruction fields

Non. RISC ARM features • Control over both the Arithmetic Logic Unit(ALU) and shifter in every data-processing instruction to maximize the use of an ALU and a shifter. • auto-increment and auto-decrement addressing modes to optimize program loops • Load and Store Multiple instructions to maximize data throughput • conditional execution of all instructions to maximize execution throughput. • Orthogonal instruction Set

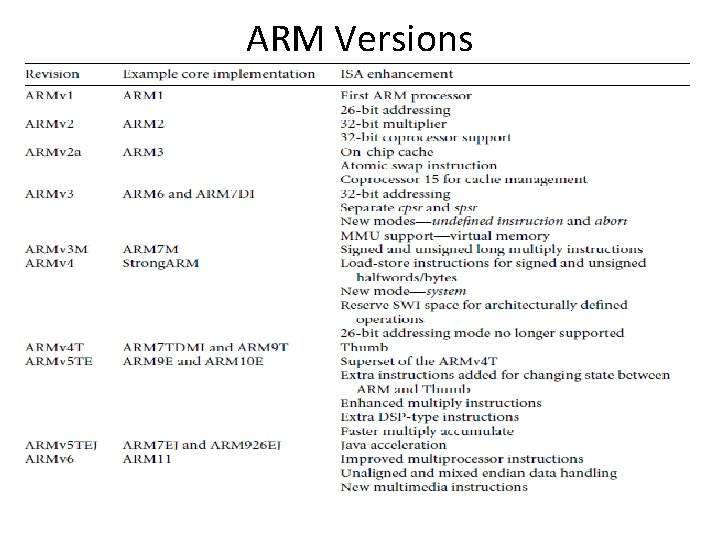

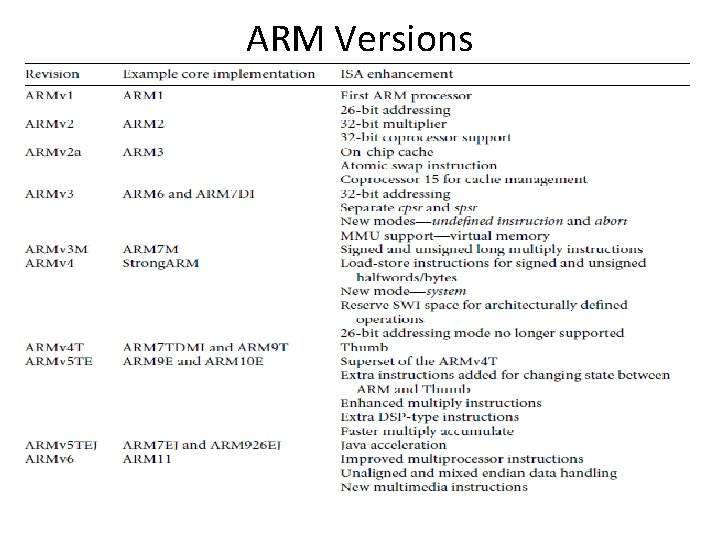

ARM Versions

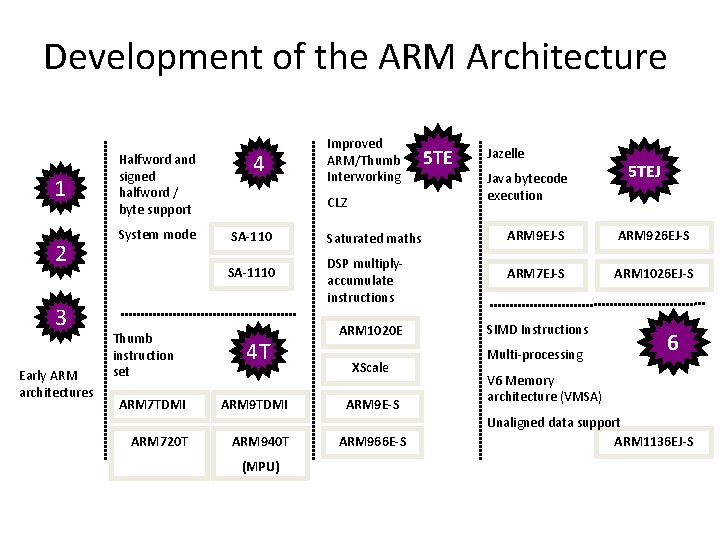

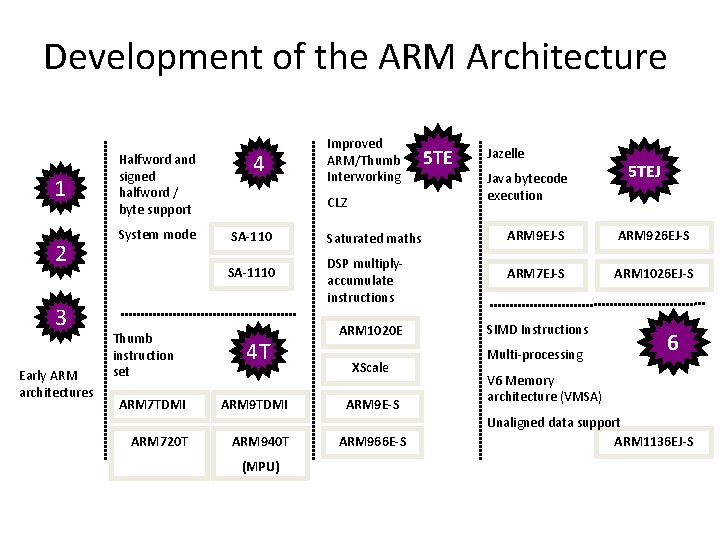

Development of the ARM Architecture 1 2 3 Early ARM architectures Halfword and signed halfword / byte support System mode 4 CLZ SA-110 SA-1110 Thumb instruction set ARM 7 TDMI ARM 720 T Improved ARM/Thumb Interworking 4 T ARM 9 TDMI ARM 940 T (MPU) Saturated maths DSP multiplyaccumulate instructions ARM 1020 E XScale ARM 9 E-S ARM 966 E-S 5 TE Jazelle Java bytecode execution 5 TEJ ARM 9 EJ-S ARM 926 EJ-S ARM 7 EJ-S ARM 1026 EJ-S SIMD Instructions Multi-processing 6 V 6 Memory architecture (VMSA) Unaligned data support ARM 1136 EJ-S

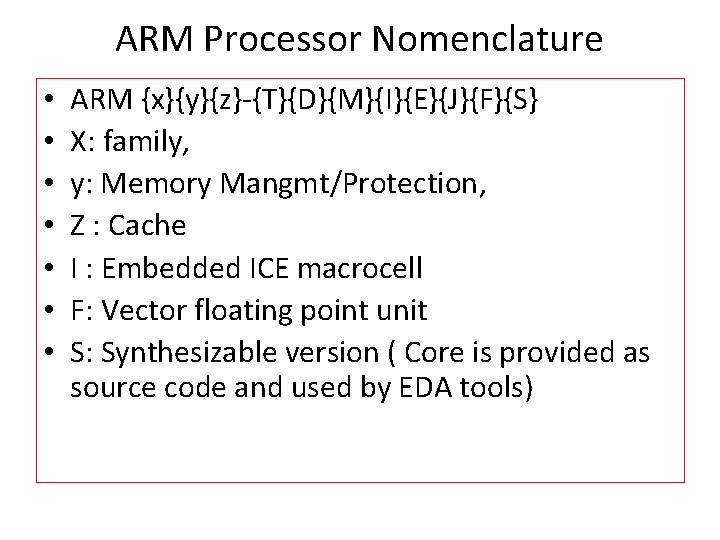

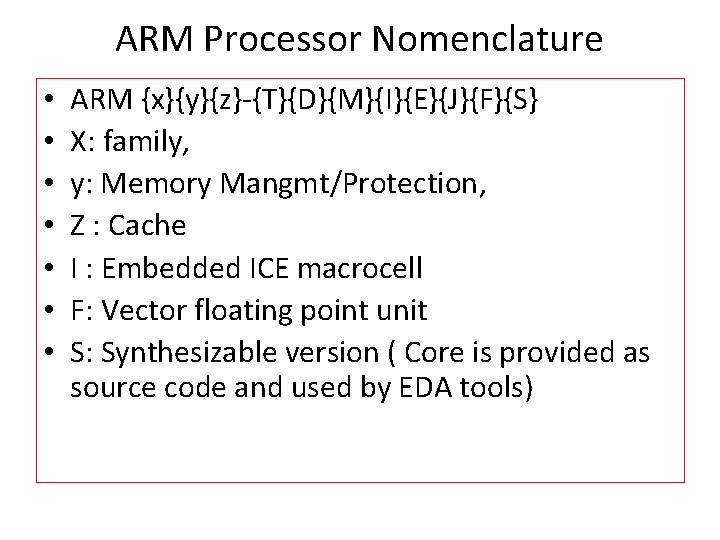

ARM Processor Nomenclature • • ARM {x}{y}{z}-{T}{D}{M}{I}{E}{J}{F}{S} X: family, y: Memory Mangmt/Protection, Z : Cache I : Embedded ICE macrocell F: Vector floating point unit S: Synthesizable version ( Core is provided as source code and used by EDA tools)

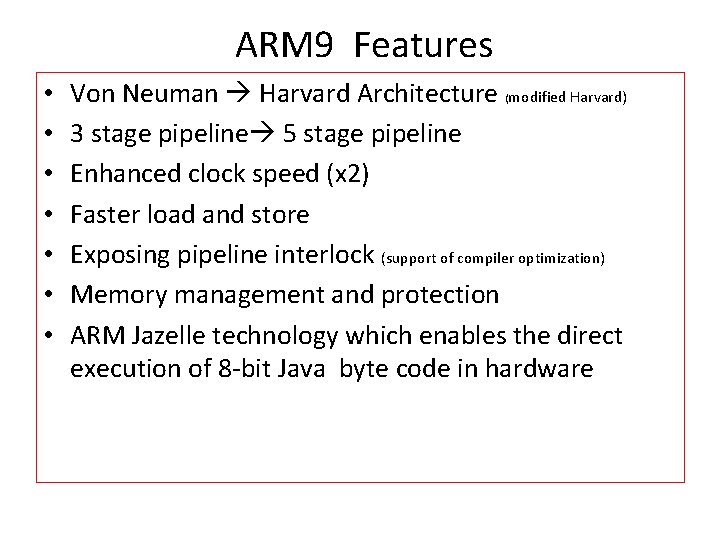

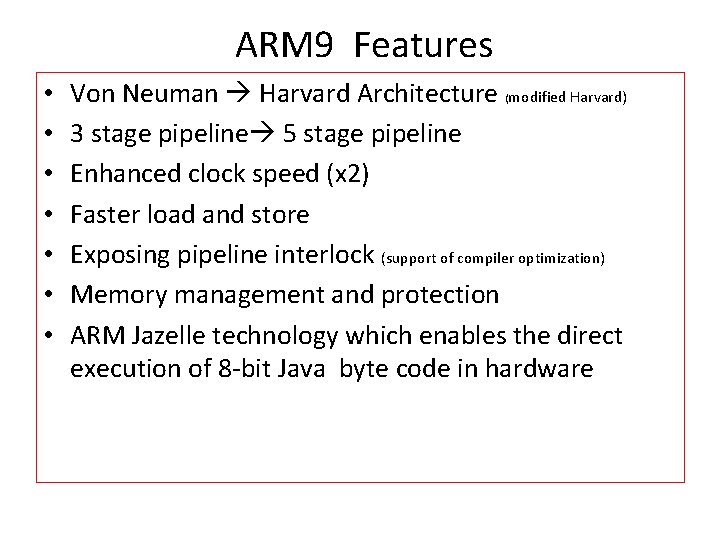

ARM 9 Features • • Von Neuman Harvard Architecture (modified Harvard) 3 stage pipeline 5 stage pipeline Enhanced clock speed (x 2) Faster load and store Exposing pipeline interlock (support of compiler optimization) Memory management and protection ARM Jazelle technology which enables the direct execution of 8 -bit Java byte code in hardware

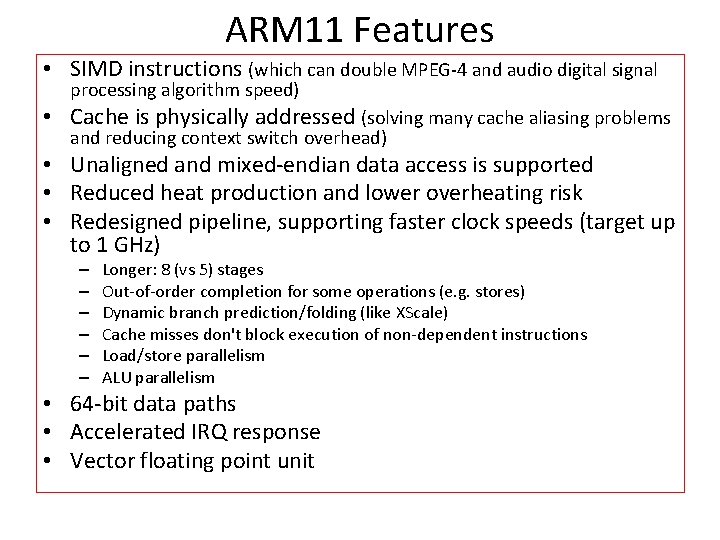

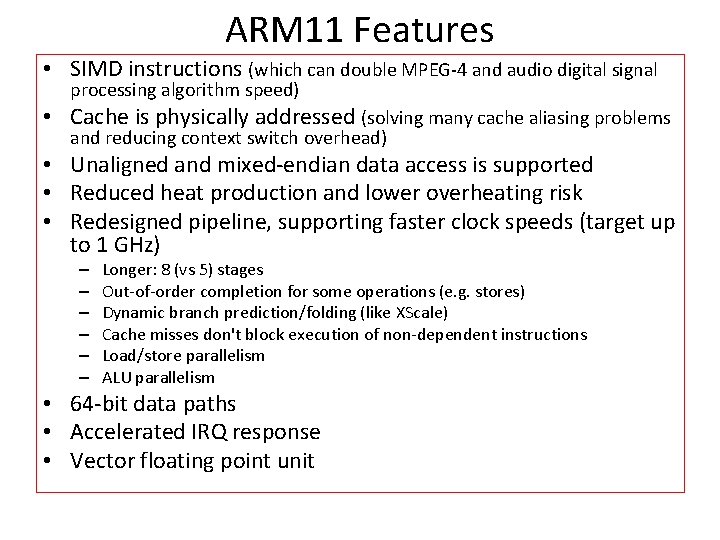

ARM 11 Features • SIMD instructions (which can double MPEG-4 and audio digital signal processing algorithm speed) • Cache is physically addressed (solving many cache aliasing problems and reducing context switch overhead) • Unaligned and mixed-endian data access is supported • Reduced heat production and lower overheating risk • Redesigned pipeline, supporting faster clock speeds (target up to 1 GHz) – – – Longer: 8 (vs 5) stages Out-of-order completion for some operations (e. g. stores) Dynamic branch prediction/folding (like XScale) Cache misses don't block execution of non-dependent instructions Load/store parallelism ALU parallelism • 64 -bit data paths • Accelerated IRQ response • Vector floating point unit

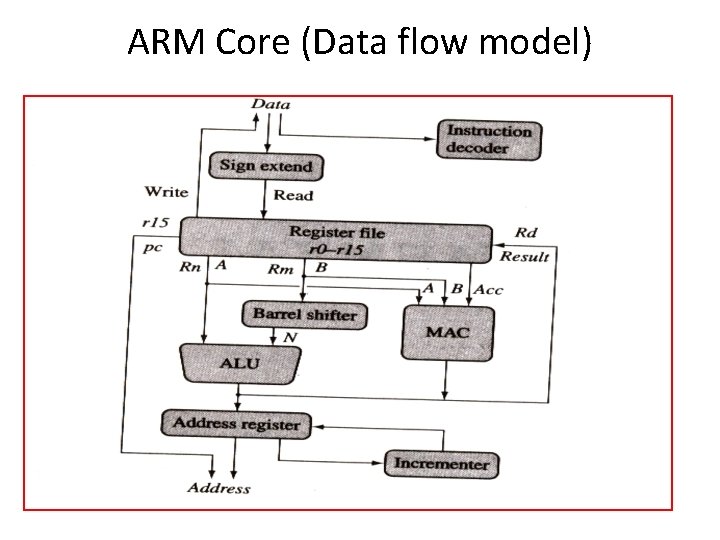

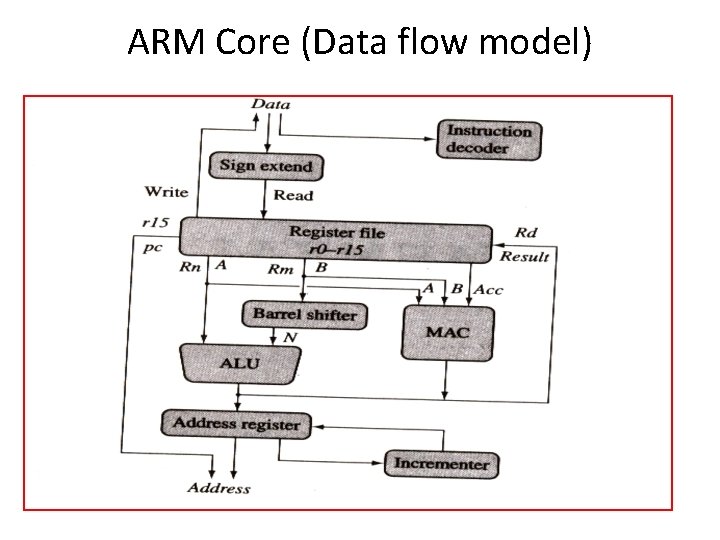

ARM Core (Data flow model)

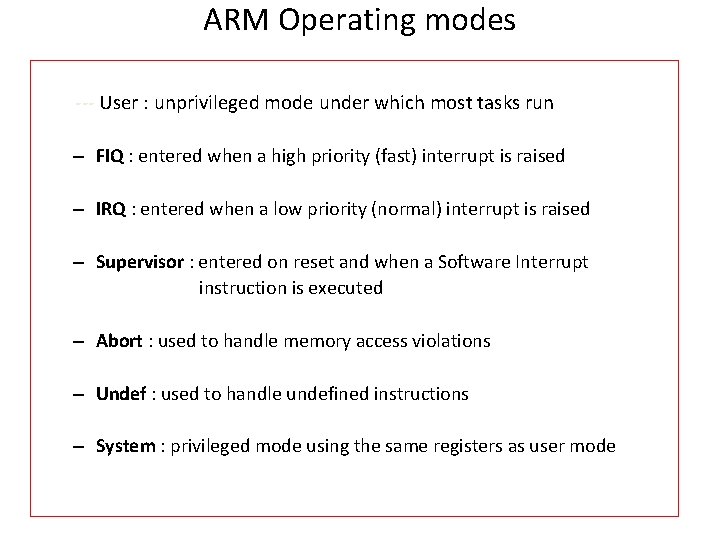

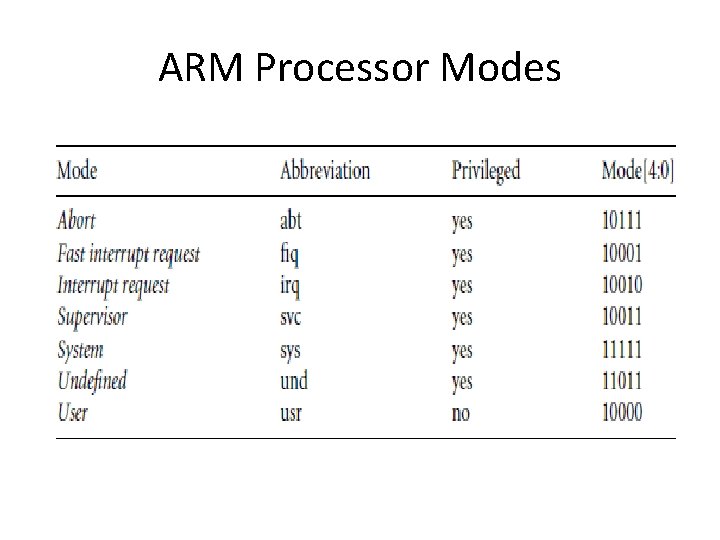

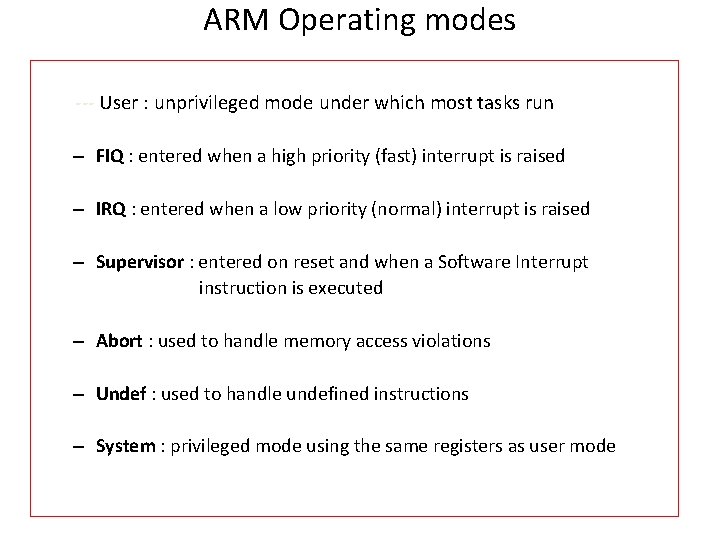

ARM Operating modes --- User : unprivileged mode under which most tasks run – FIQ : entered when a high priority (fast) interrupt is raised – IRQ : entered when a low priority (normal) interrupt is raised – Supervisor : entered on reset and when a Software Interrupt instruction is executed – Abort : used to handle memory access violations – Undef : used to handle undefined instructions – System : privileged mode using the same registers as user mode

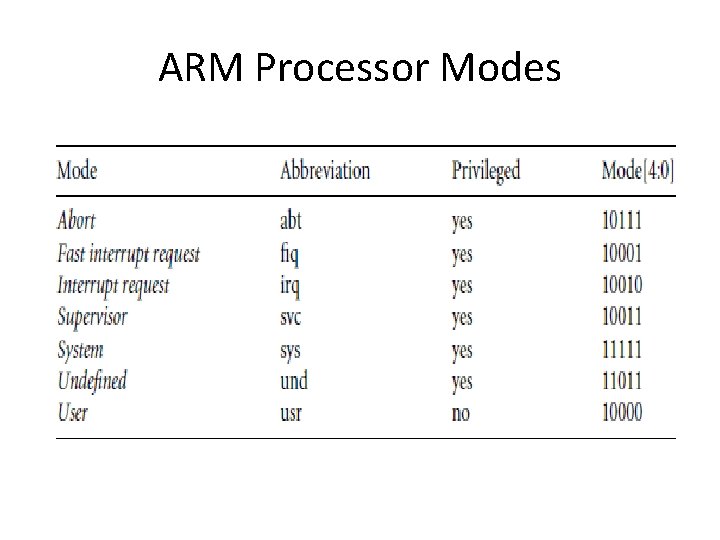

ARM Processor Modes

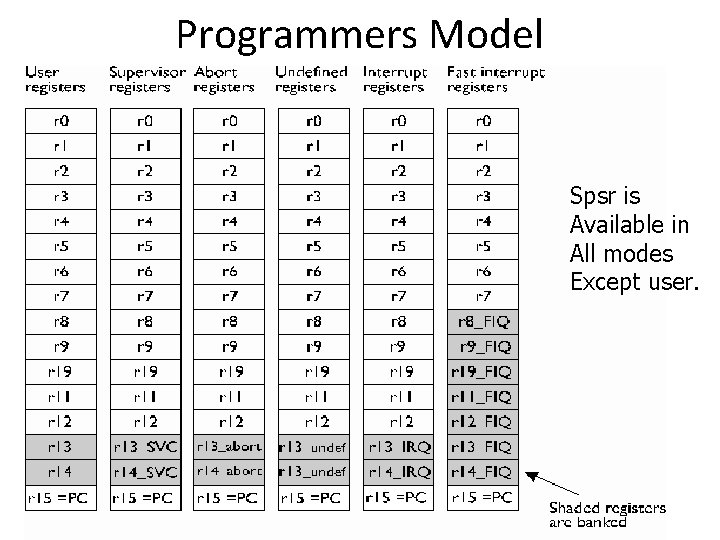

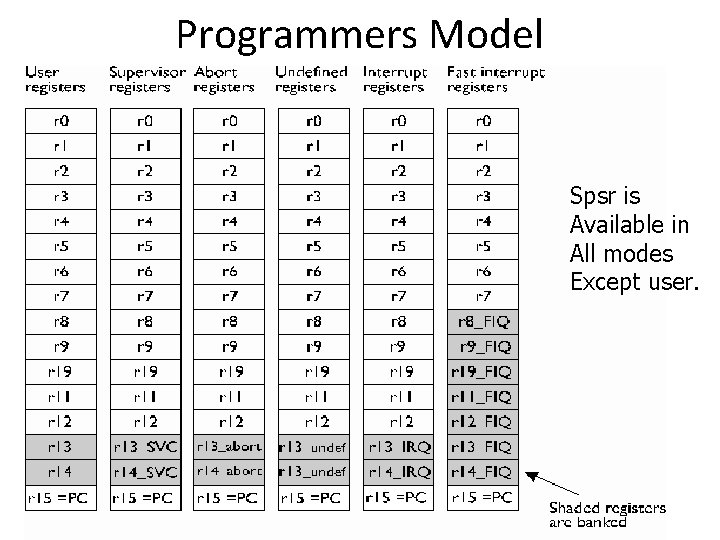

Programmers Model Spsr is Available in All modes Except user.

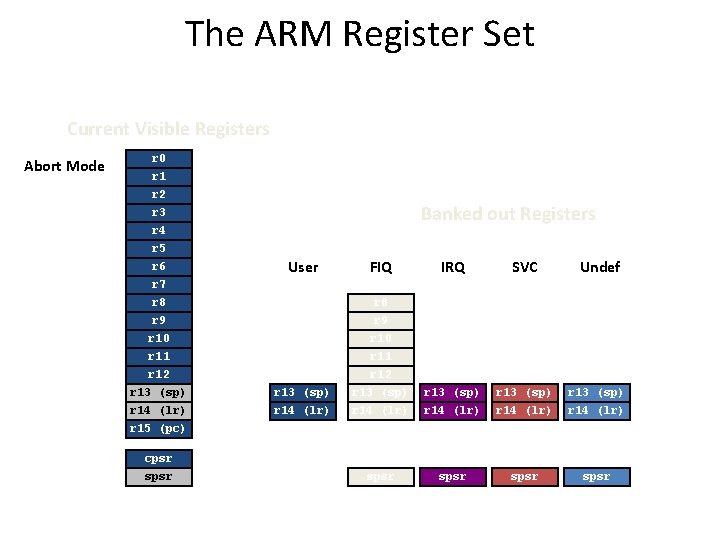

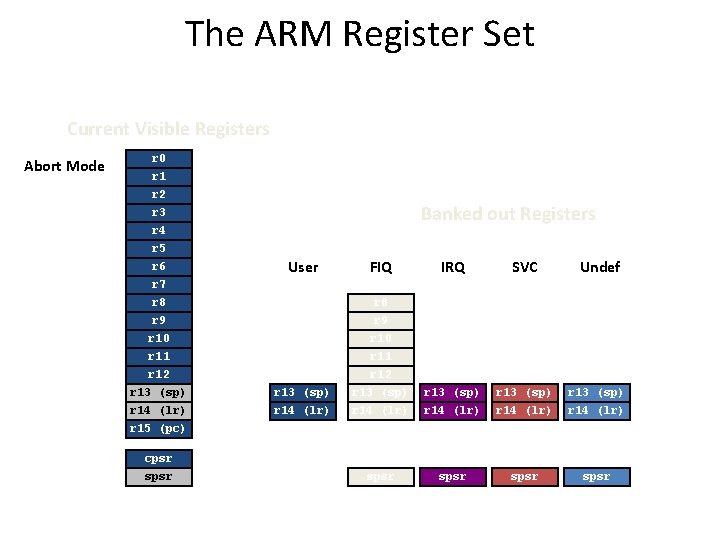

The ARM Register Set Current Visible Registers Abort Mode Undef SVCMode FIQ User Mode IRQ r 0 r 1 r 2 r 3 r 4 r 5 r 6 r 7 r 8 r 9 r 10 r 11 r 12 r 13 (sp) r 14 (lr) r 15 (pc) cpsr spsr Banked out Registers User FIQ IRQ SVC Undef Abort r 8 r 9 r 10 r 11 r 12 r 13 (sp) r 14 (lr) r 13 (sp) r 14 (lr) spsr spsr

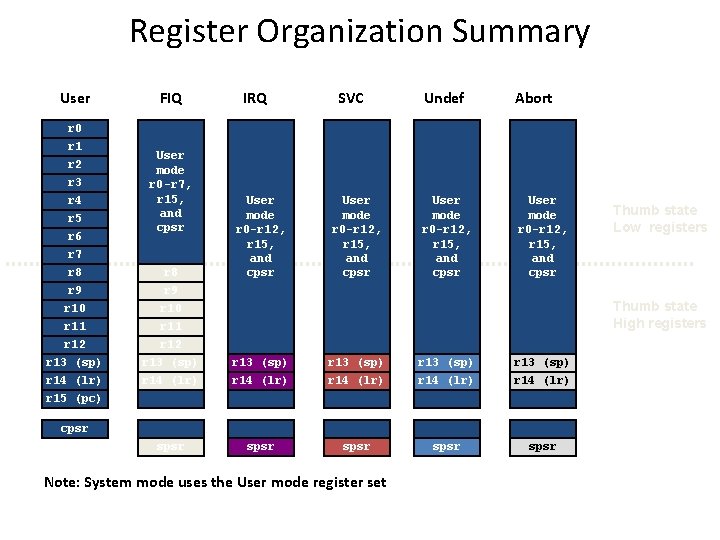

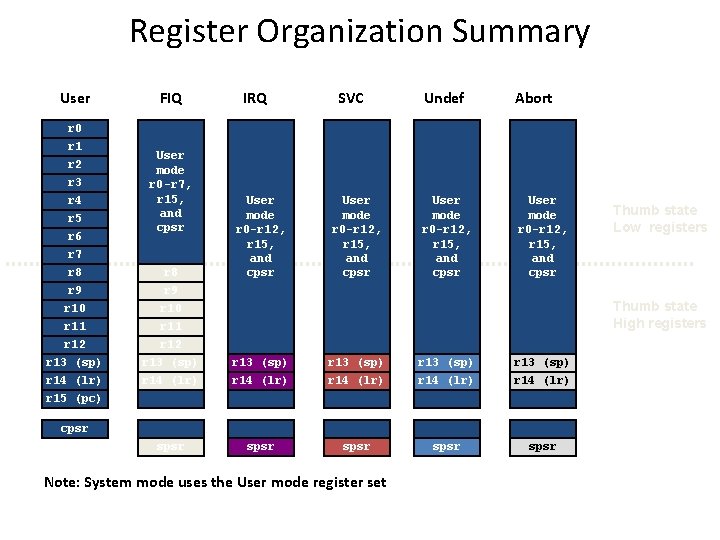

Register Organization Summary User FIQ IRQ SVC Undef Abort User mode r 0 -r 12, r 15, and cpsr r 0 r 1 r 2 r 3 r 4 r 5 r 6 r 7 r 8 r 9 r 10 r 11 r 12 r 13 (sp) r 14 (lr) r 15 (pc) User mode r 0 -r 7, r 15, and cpsr User mode r 0 -r 12, r 15, and cpsr r 8 r 9 r 10 r 11 r 12 r 13 (sp) r 14 (lr) r 13 (sp) r 14 (lr) spsr spsr Thumb state Low registers Thumb state High registers cpsr Note: System mode uses the User mode register set

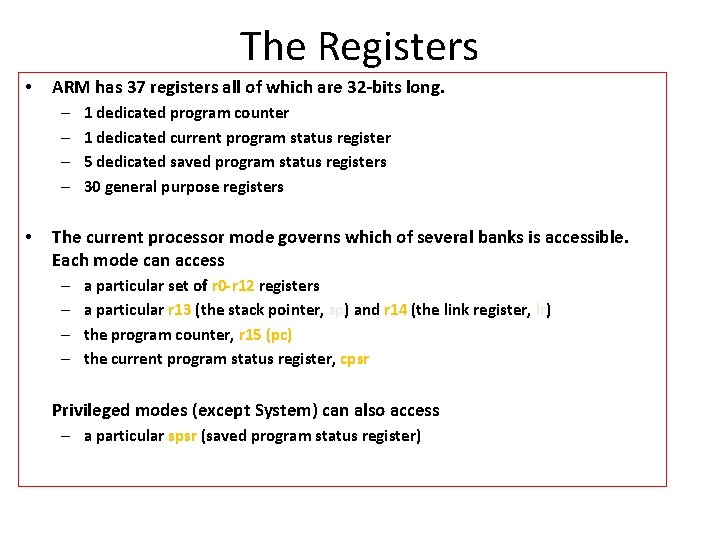

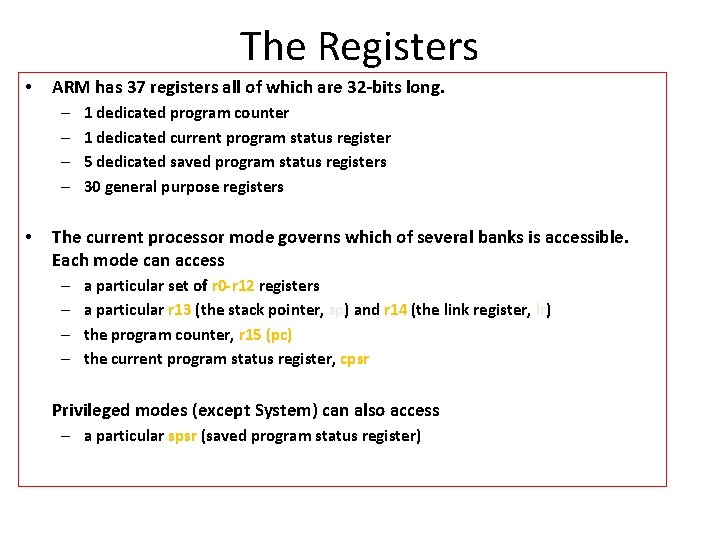

The Registers • ARM has 37 registers all of which are 32 -bits long. – – • 1 dedicated program counter 1 dedicated current program status register 5 dedicated saved program status registers 30 general purpose registers The current processor mode governs which of several banks is accessible. Each mode can access – – a particular set of r 0 -r 12 registers a particular r 13 (the stack pointer, sp) and r 14 (the link register, lr) the program counter, r 15 (pc) the current program status register, cpsr Privileged modes (except System) can also access – a particular spsr (saved program status register)

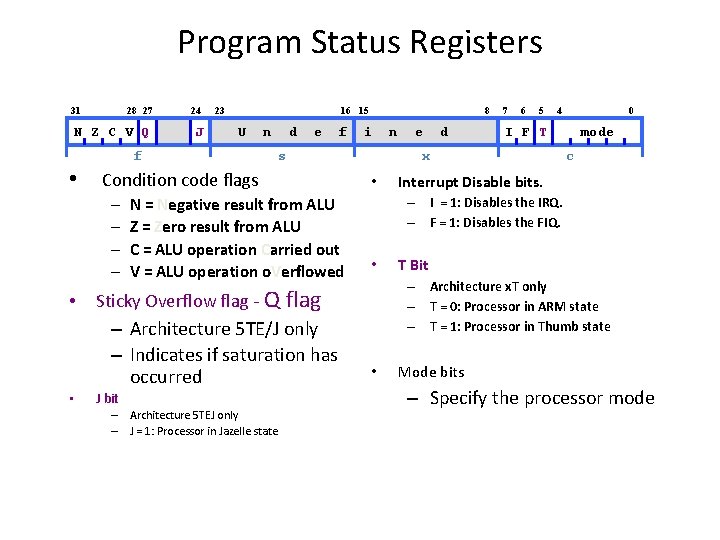

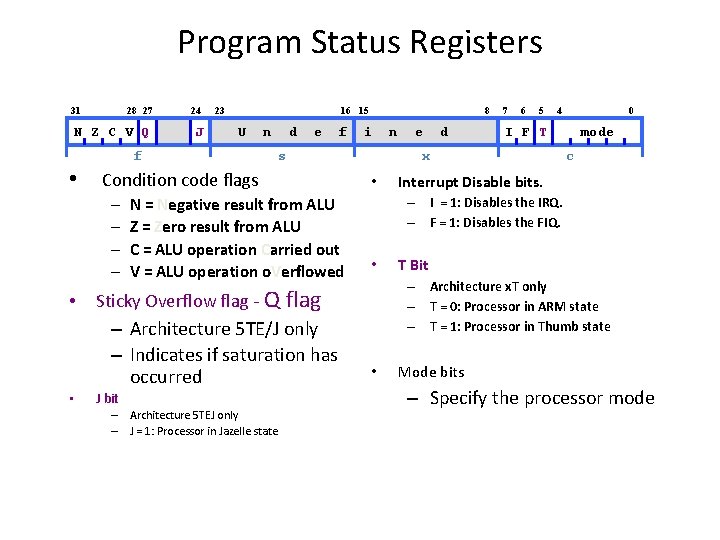

Program Status Registers 31 28 27 N Z C V Q • J 23 16 15 U f n d e 8 i s N = Negative result from ALU Z = Zero result from ALU C = ALU operation Carried out V = ALU operation o. Verflowed J bit – Architecture 5 TEJ only – J = 1: Processor in Jazelle state n e d 7 6 5 4 • 0 I F T x mode c Interrupt Disable bits. – I = 1: Disables the IRQ. – F = 1: Disables the FIQ. • T Bit – Architecture x. T only – T = 0: Processor in ARM state – T = 1: Processor in Thumb state Sticky Overflow flag - Q flag – Architecture 5 TE/J only – Indicates if saturation has occurred • f Condition code flags – – • 24 • Mode bits – Specify the processor mode

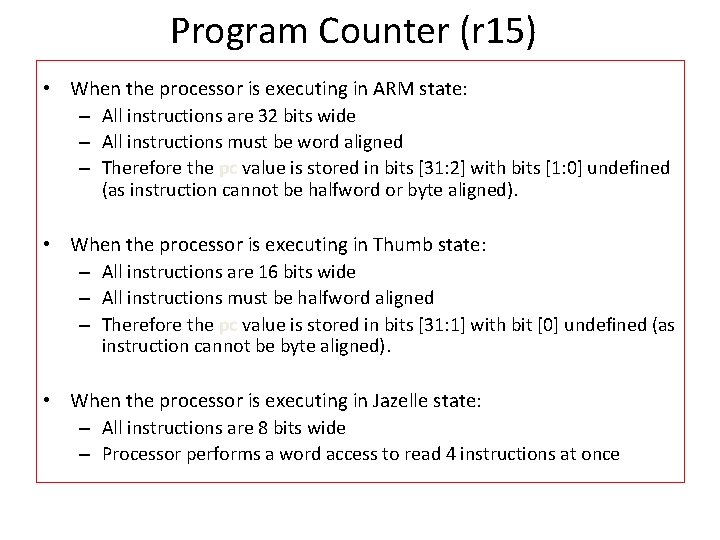

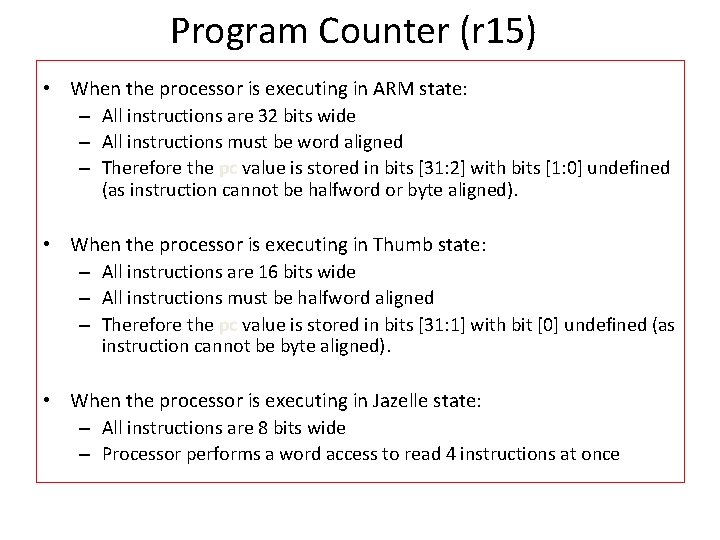

Program Counter (r 15) • When the processor is executing in ARM state: – All instructions are 32 bits wide – All instructions must be word aligned – Therefore the pc value is stored in bits [31: 2] with bits [1: 0] undefined (as instruction cannot be halfword or byte aligned). • When the processor is executing in Thumb state: – All instructions are 16 bits wide – All instructions must be halfword aligned – Therefore the pc value is stored in bits [31: 1] with bit [0] undefined (as instruction cannot be byte aligned). • When the processor is executing in Jazelle state: – All instructions are 8 bits wide – Processor performs a word access to read 4 instructions at once

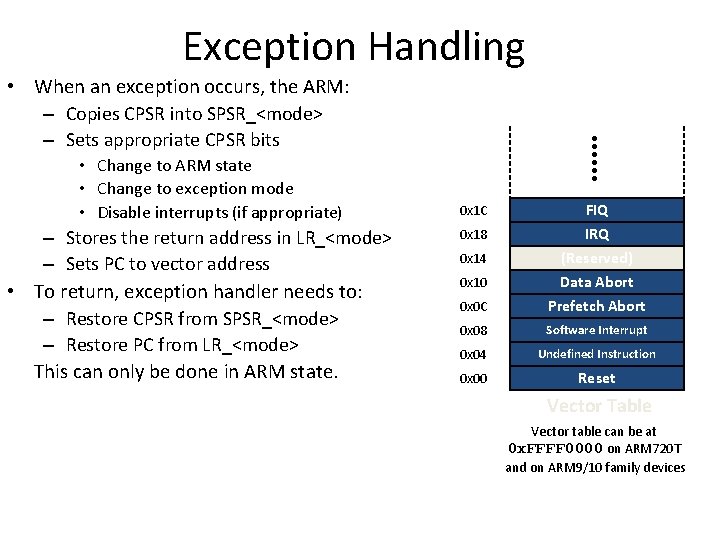

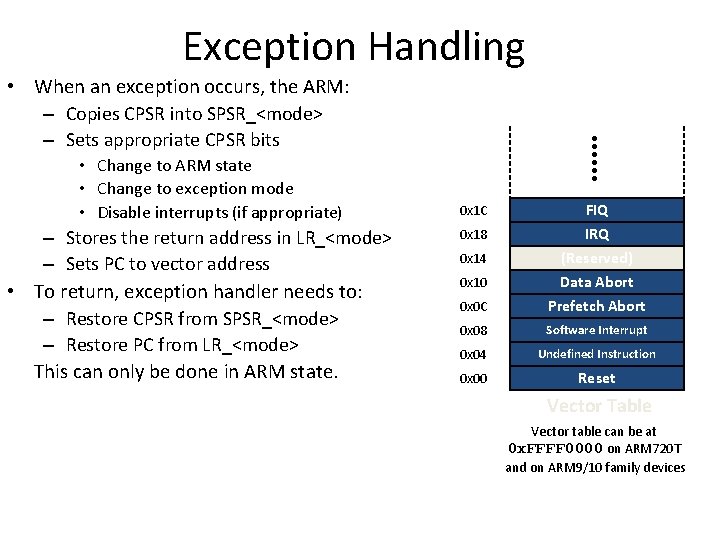

Exception Handling • When an exception occurs, the ARM: – Copies CPSR into SPSR_<mode> – Sets appropriate CPSR bits • Change to ARM state • Change to exception mode • Disable interrupts (if appropriate) – Stores the return address in LR_<mode> – Sets PC to vector address • To return, exception handler needs to: – Restore CPSR from SPSR_<mode> – Restore PC from LR_<mode> This can only be done in ARM state. 0 x 1 C 0 x 18 0 x 14 FIQ IRQ (Reserved) 0 x 0 C Data Abort Prefetch Abort 0 x 08 Software Interrupt 0 x 04 Undefined Instruction 0 x 00 Reset 0 x 10 Vector Table Vector table can be at 0 x. FFFF 0000 on ARM 720 T and on ARM 9/10 family devices

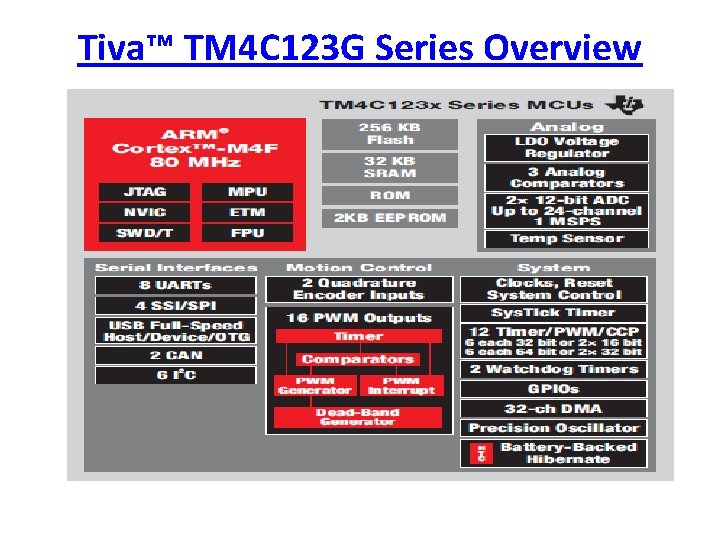

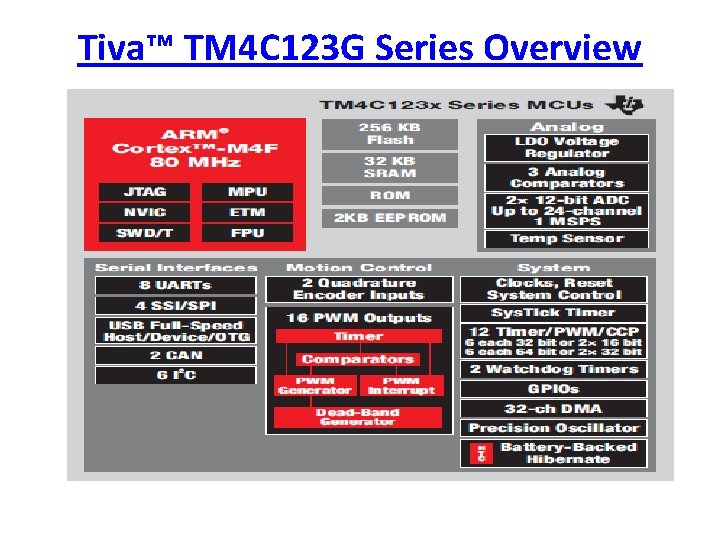

Tiva™ TM 4 C 123 G Series Overview

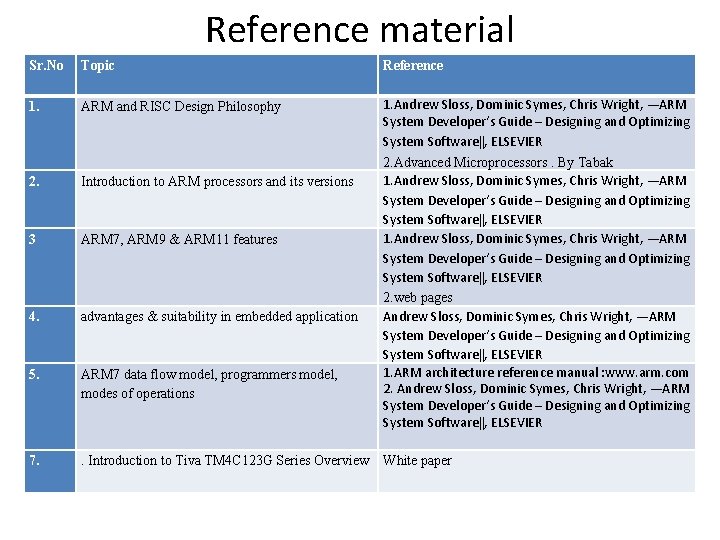

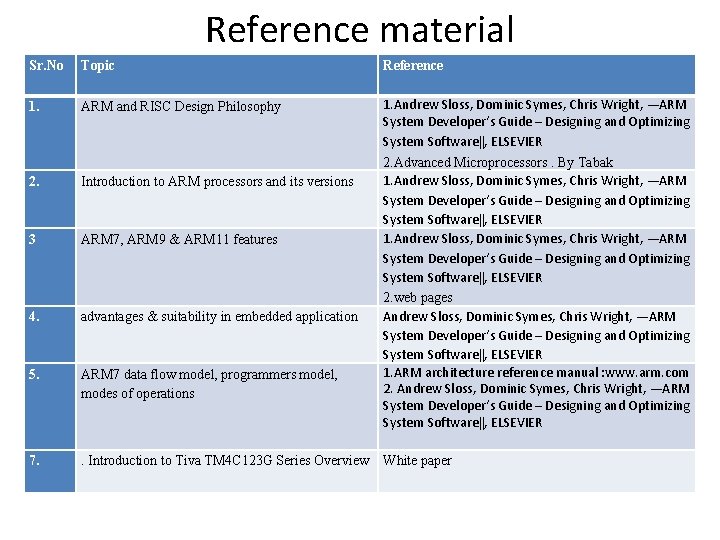

Reference material Sr. No Topic Reference 1. ARM and RISC Design Philosophy 2. Introduction to ARM processors and its versions 3 ARM 7, ARM 9 & ARM 11 features 4. advantages & suitability in embedded application 5. ARM 7 data flow model, programmers model, modes of operations 1. Andrew Sloss, Dominic Symes, Chris Wright, ―ARM System Developer‘s Guide – Designing and Optimizing System Software‖, ELSEVIER 2. Advanced Microprocessors. By Tabak 1. Andrew Sloss, Dominic Symes, Chris Wright, ―ARM System Developer‘s Guide – Designing and Optimizing System Software‖, ELSEVIER 2. web pages Andrew Sloss, Dominic Symes, Chris Wright, ―ARM System Developer‘s Guide – Designing and Optimizing System Software‖, ELSEVIER 1. ARM architecture reference manual : www. arm. com 2. Andrew Sloss, Dominic Symes, Chris Wright, ―ARM System Developer‘s Guide – Designing and Optimizing System Software‖, ELSEVIER 7. . Introduction to Tiva TM 4 C 123 G Series Overview White paper