Microprocessor Interfacing THE 8253 IC PIT Vatsal N

- Slides: 18

Microprocessor & Interfacing THE 8253 IC (PIT) Vatsal N Shah – IU 1241090055 Sharon Benedict – IU 1241090056 Electronics and Communication Engineering Dept. Indus University 1

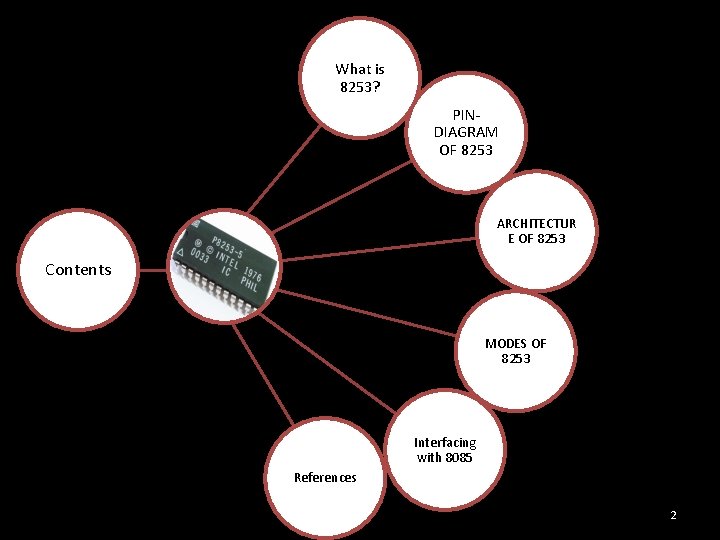

What is 8253? PINDIAGRAM OF 8253 ARCHITECTUR E OF 8253 Contents MODES OF 8253 Interfacing with 8085 References 2

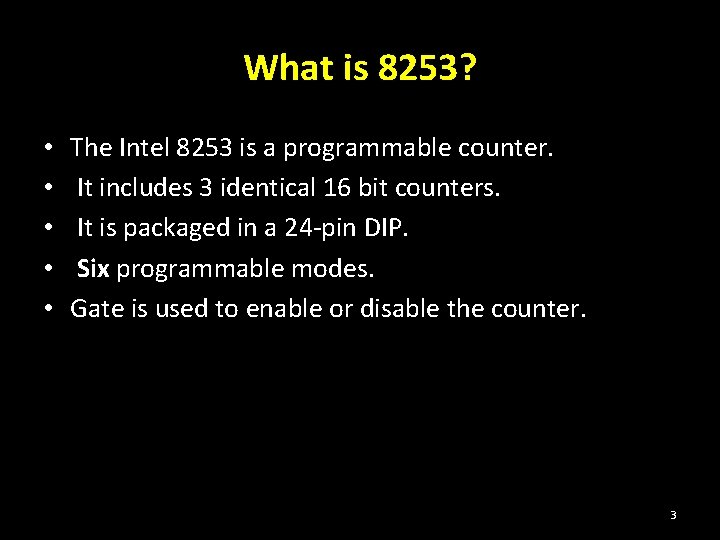

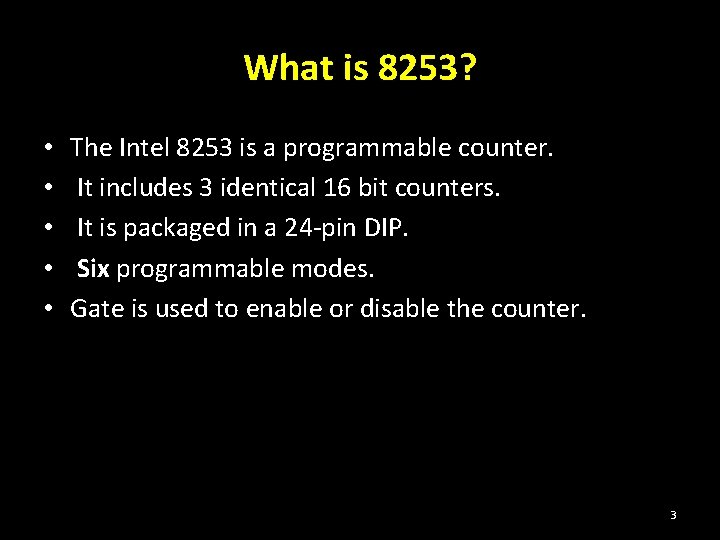

What is 8253? • • • The Intel 8253 is a programmable counter. It includes 3 identical 16 bit counters. It is packaged in a 24 -pin DIP. Six programmable modes. Gate is used to enable or disable the counter. 3

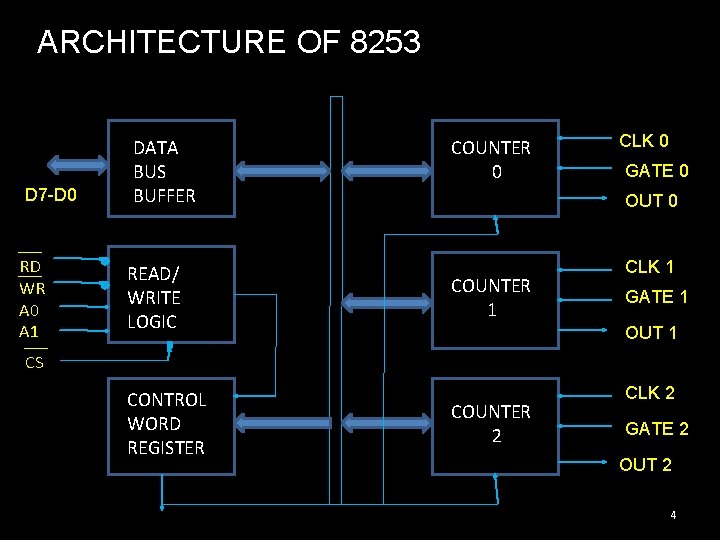

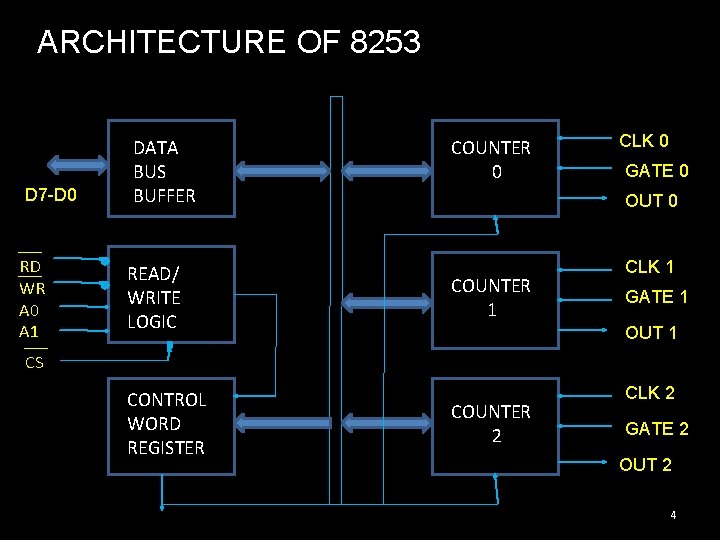

ARCHITECTURE OF 8253 D 7 -D 0 RD WR A 0 A 1 DATA BUS BUFFER READ/ WRITE LOGIC COUNTER 0 CLK 0 GATE 0 OUT 0 COUNTER 1 CLK 1 GATE 1 OUT 1 CS CONTROL WORD REGISTER COUNTER 2 CLK 2 GATE 2 OUT 2 4

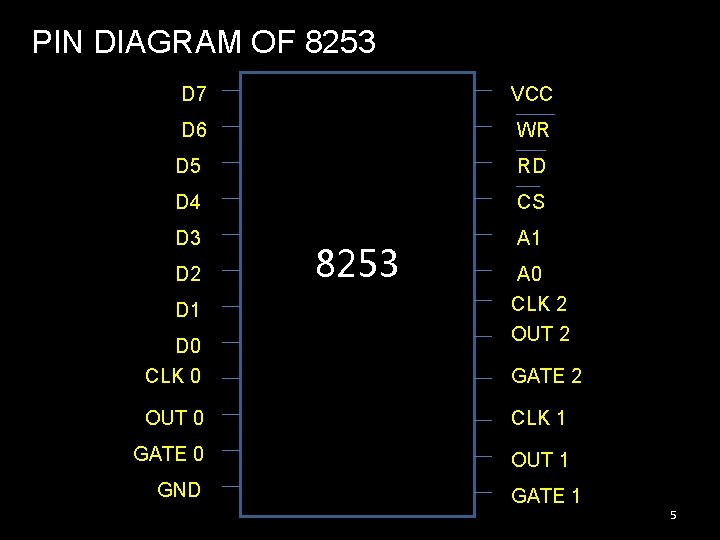

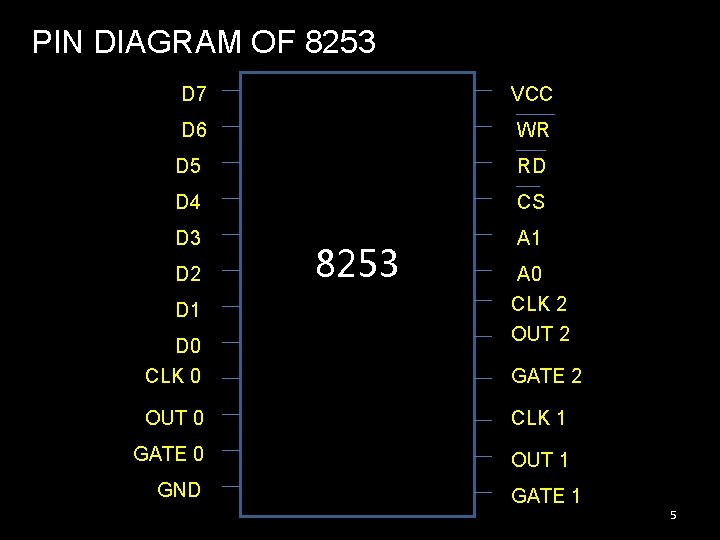

PIN DIAGRAM OF 8253 D 7 VCC D 6 WR D 5 RD D 4 CS D 3 A 1 D 2 D 1 D 0 CLK 0 8253 A 0 CLK 2 OUT 2 GATE 2 OUT 0 CLK 1 GATE 0 OUT 1 GND GATE 1 5

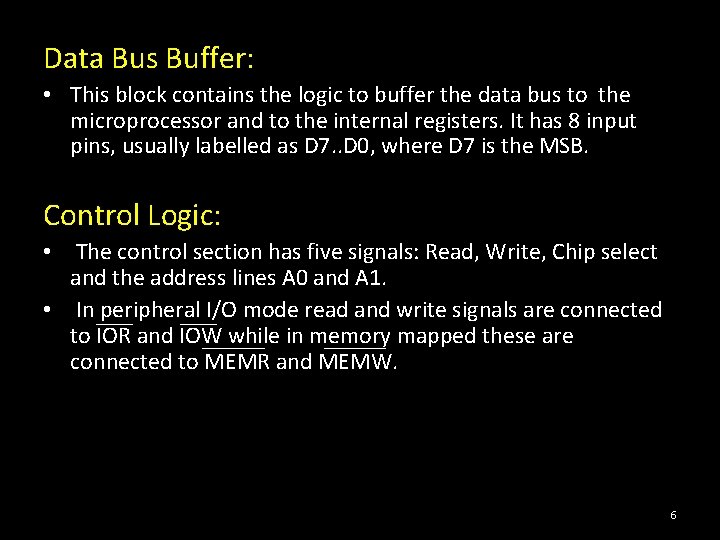

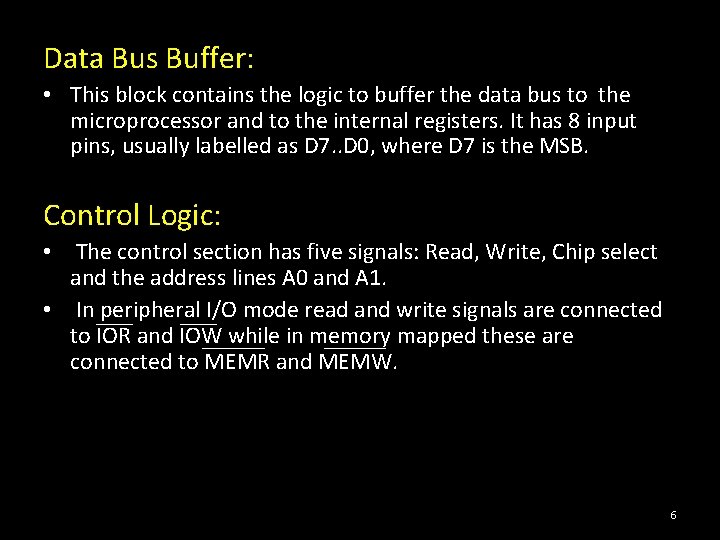

Data Bus Buffer: • This block contains the logic to buffer the data bus to the microprocessor and to the internal registers. It has 8 input pins, usually labelled as D 7. . D 0, where D 7 is the MSB. Control Logic: • The control section has five signals: Read, Write, Chip select and the address lines A 0 and A 1. • In peripheral I/O mode read and write signals are connected to IOR and IOW while in memory mapped these are connected to MEMR and MEMW. 6

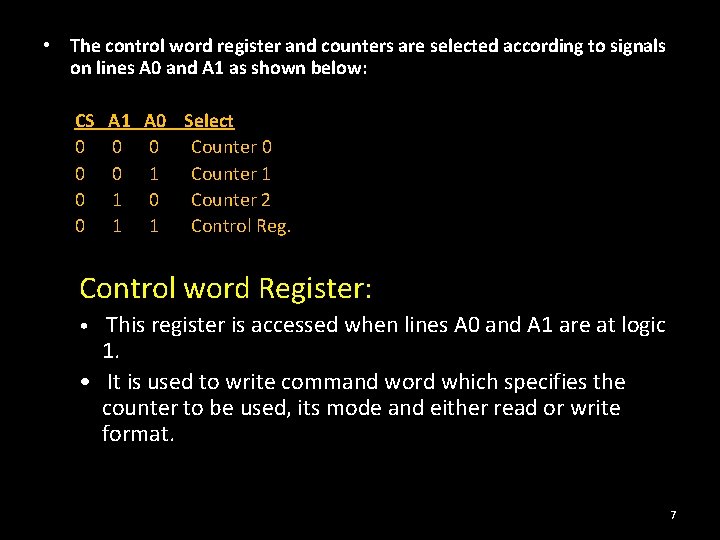

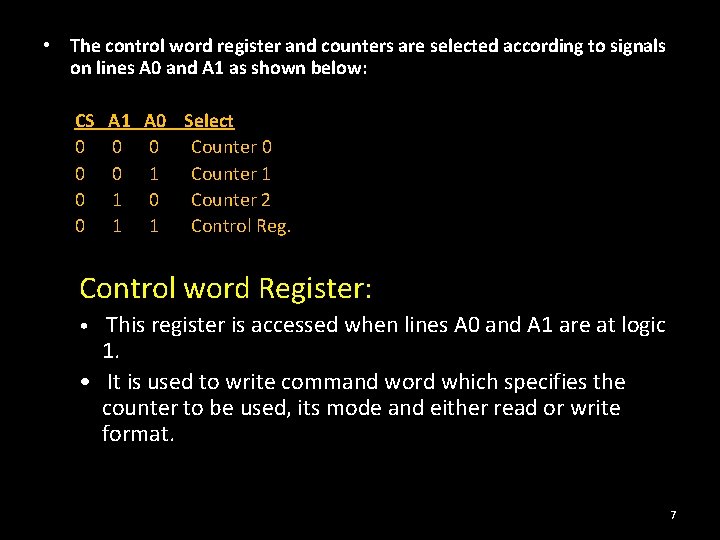

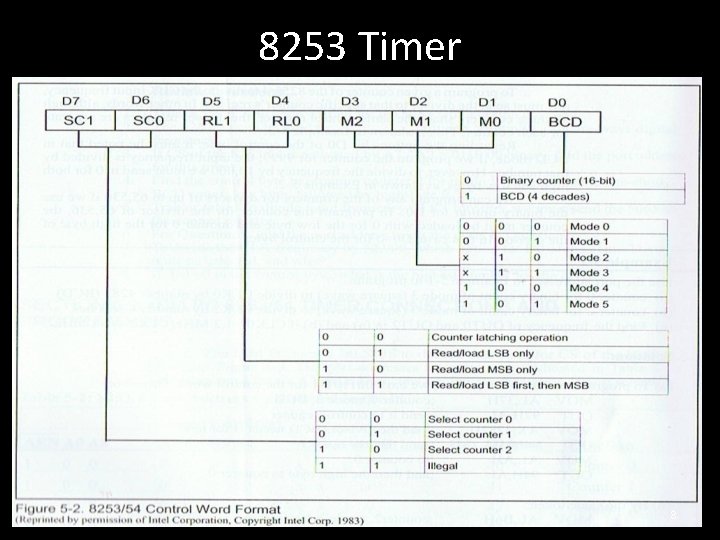

• The control word register and counters are selected according to signals on lines A 0 and A 1 as shown below: CS 0 0 A 1 0 0 1 1 A 0 Select 0 Counter 0 1 Counter 1 0 Counter 2 1 Control Reg. Control word Register: • This register is accessed when lines A 0 and A 1 are at logic 1. • It is used to write command word which specifies the counter to be used, its mode and either read or write format. 7

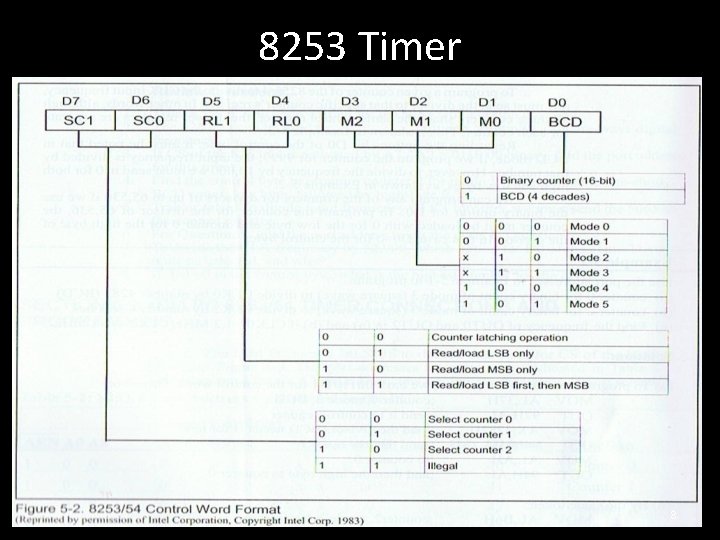

8253 Timer 8

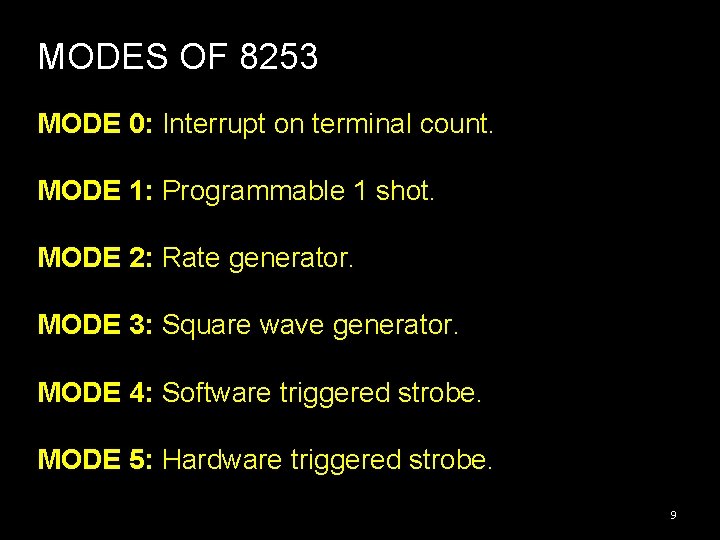

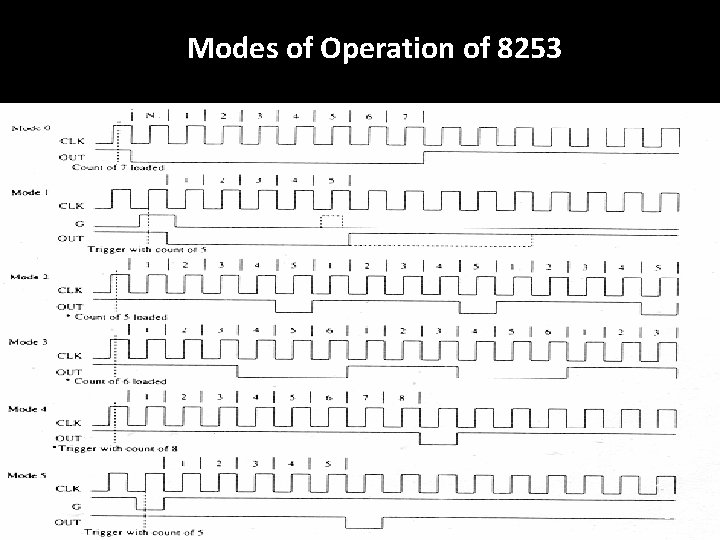

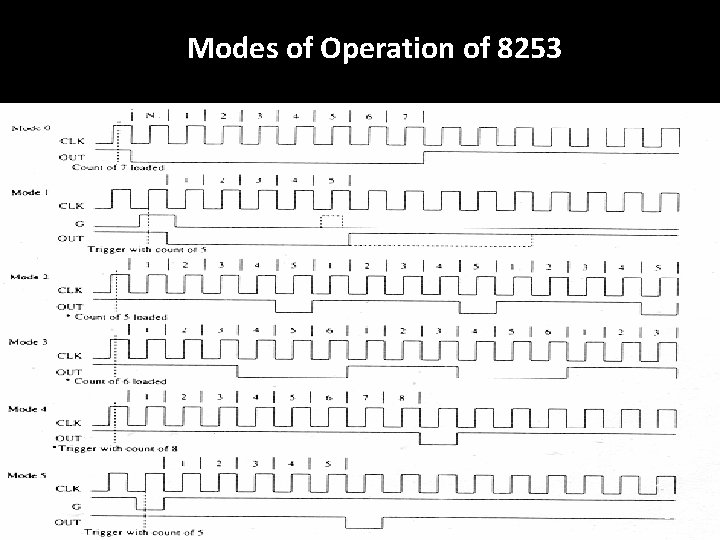

MODES OF 8253 MODE 0: Interrupt on terminal count. MODE 1: Programmable 1 shot. MODE 2: Rate generator. MODE 3: Square wave generator. MODE 4: Software triggered strobe. MODE 5: Hardware triggered strobe. 9

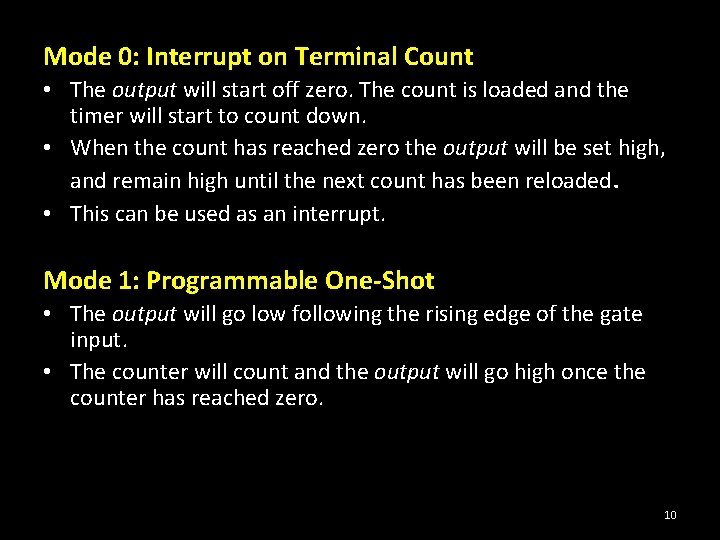

Mode 0: Interrupt on Terminal Count • The output will start off zero. The count is loaded and the timer will start to count down. • When the count has reached zero the output will be set high, and remain high until the next count has been reloaded. • This can be used as an interrupt. Mode 1: Programmable One-Shot • The output will go low following the rising edge of the gate input. • The counter will count and the output will go high once the counter has reached zero. 10

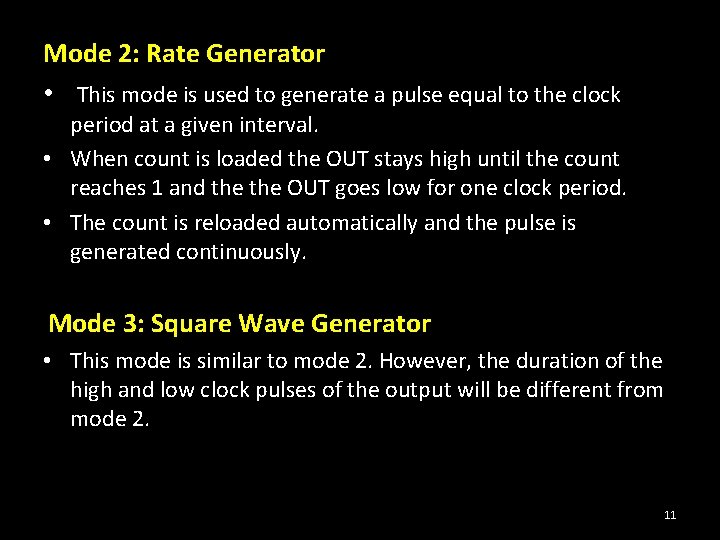

Mode 2: Rate Generator • This mode is used to generate a pulse equal to the clock period at a given interval. • When count is loaded the OUT stays high until the count reaches 1 and the OUT goes low for one clock period. • The count is reloaded automatically and the pulse is generated continuously. Mode 3: Square Wave Generator • This mode is similar to mode 2. However, the duration of the high and low clock pulses of the output will be different from mode 2. 11

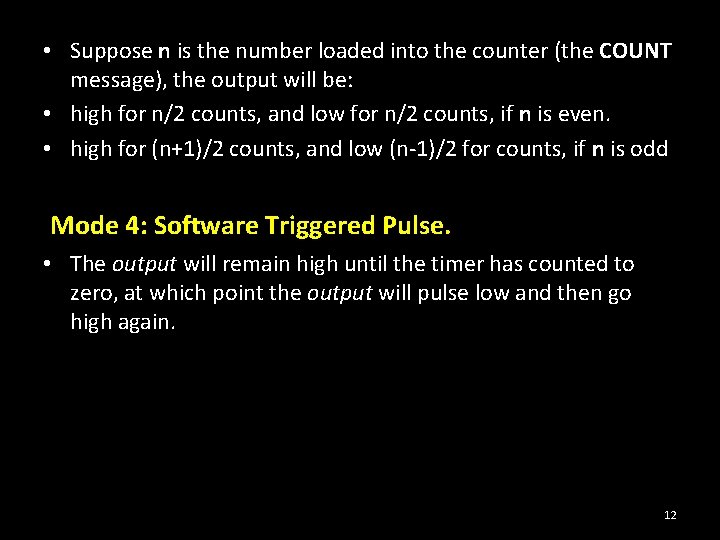

• Suppose n is the number loaded into the counter (the COUNT message), the output will be: • high for n/2 counts, and low for n/2 counts, if n is even. • high for (n+1)/2 counts, and low (n-1)/2 for counts, if n is odd Mode 4: Software Triggered Pulse. • The output will remain high until the timer has counted to zero, at which point the output will pulse low and then go high again. 12

Mode 5: Hardware Triggered Pulse • The counter will start counting once the gate input goes high, when the counter reaches zero the output will pulse low and then go high again. 13

Modes of Operation of 8253 14

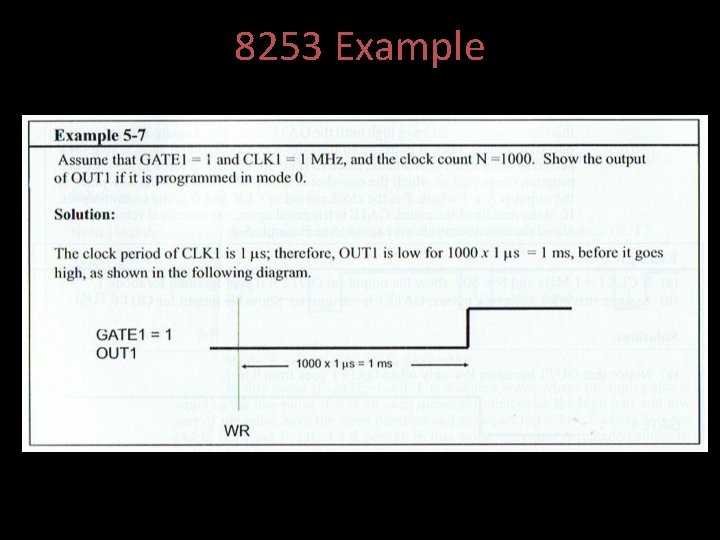

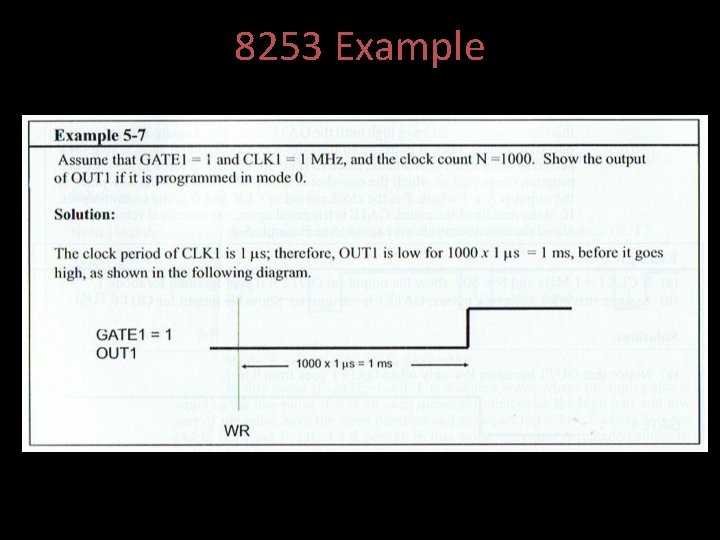

8253 Example

References • http: //www. circuitstoday. com/ • http: //www. ti. com/lit/an/slyt 145. pdf • http: //8085 projects. info/page/free-programsfor-8085 -microprocessor. html • http: //www. learnaboutelectronics. org/index. php • https: //www. youtube. com/watch? v=nx. AQ 1 PF Ed 5 U 16

17

18