Memory Copyright Nahrstedt Angrave Abdelzaher 1 Copyright Nahrstedt

Memory Copyright ©: Nahrstedt, Angrave, Abdelzaher 1

Copyright ©: Nahrstedt, Angrave, Abdelzaher Memory Allocation n n Compile for overlays Compile for fixed Partitions n n n Relocation and variable partitions n n Separate queue per partition Single queue Dynamic contiguous allocation (bit maps versus linked lists) Fragmentation issues Swapping Paging 2

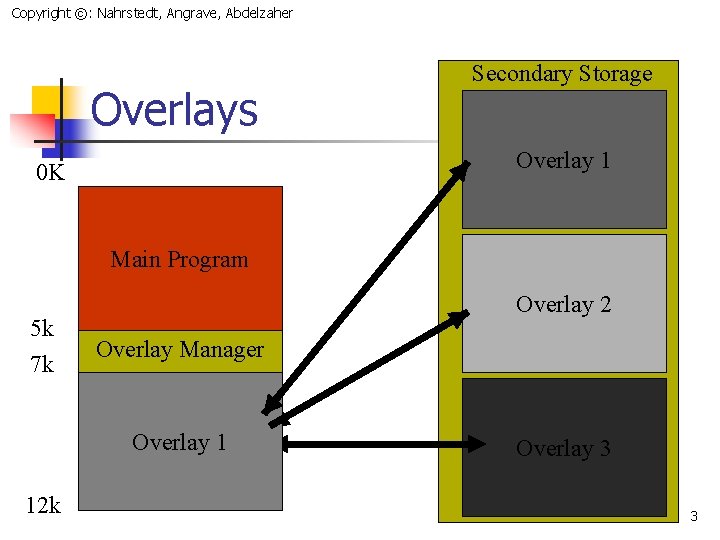

Copyright ©: Nahrstedt, Angrave, Abdelzaher Overlays Secondary Storage Overlay 1 0 K Main Program 5 k 7 k Overlay 2 Overlay Manager Overlay. Area 132 12 k Overlay 3 3

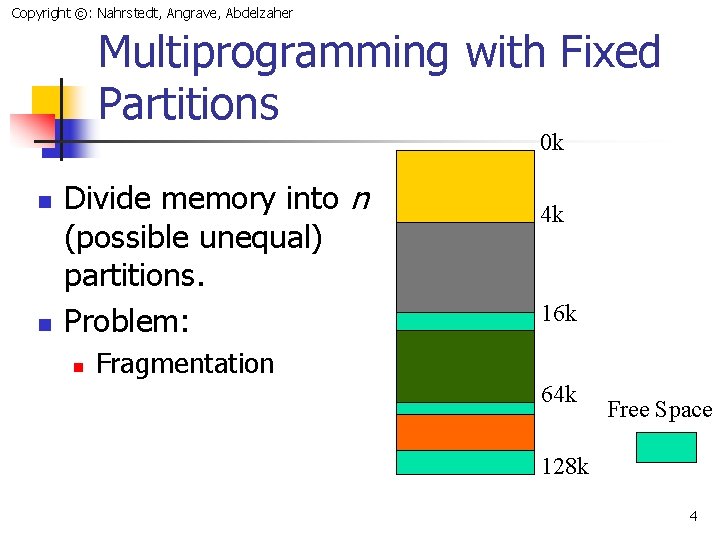

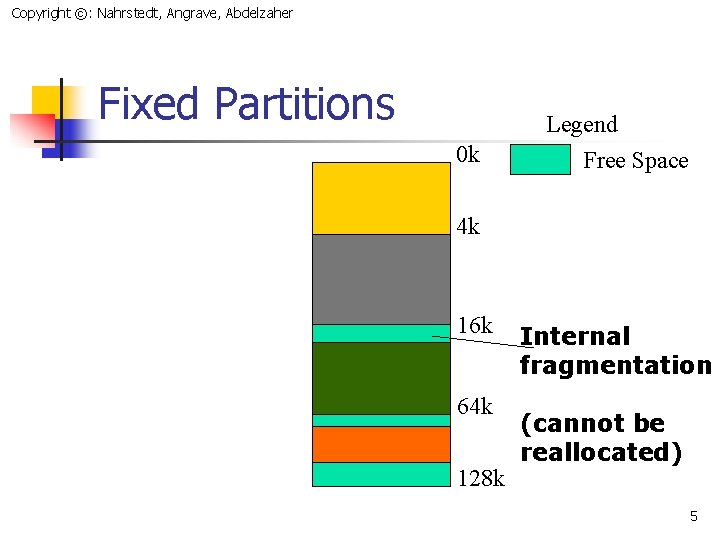

Copyright ©: Nahrstedt, Angrave, Abdelzaher Multiprogramming with Fixed Partitions 0 k n n Divide memory into n (possible unequal) partitions. Problem: n 4 k 16 k Fragmentation 64 k Free Space 128 k 4

Copyright ©: Nahrstedt, Angrave, Abdelzaher Fixed Partitions Legend 0 k Free Space 4 k 16 k 64 k 128 k Internal fragmentation (cannot be reallocated) 5

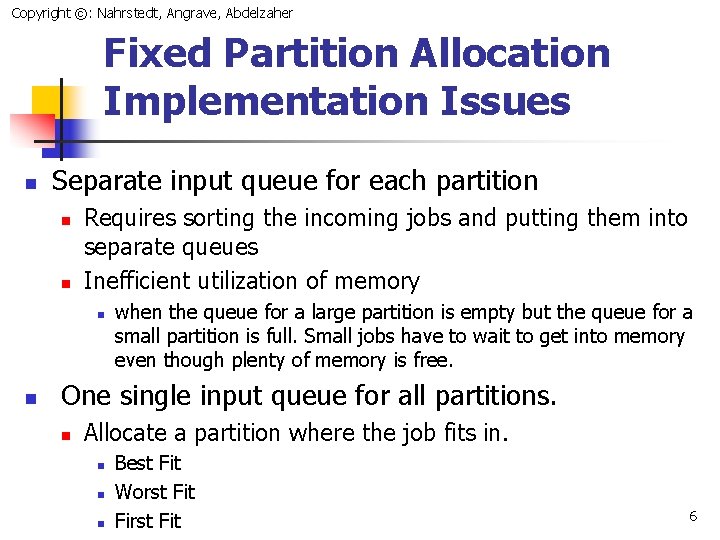

Copyright ©: Nahrstedt, Angrave, Abdelzaher Fixed Partition Allocation Implementation Issues n Separate input queue for each partition n n Requires sorting the incoming jobs and putting them into separate queues Inefficient utilization of memory n n when the queue for a large partition is empty but the queue for a small partition is full. Small jobs have to wait to get into memory even though plenty of memory is free. One single input queue for all partitions. n Allocate a partition where the job fits in. n n n Best Fit Worst First Fit 6

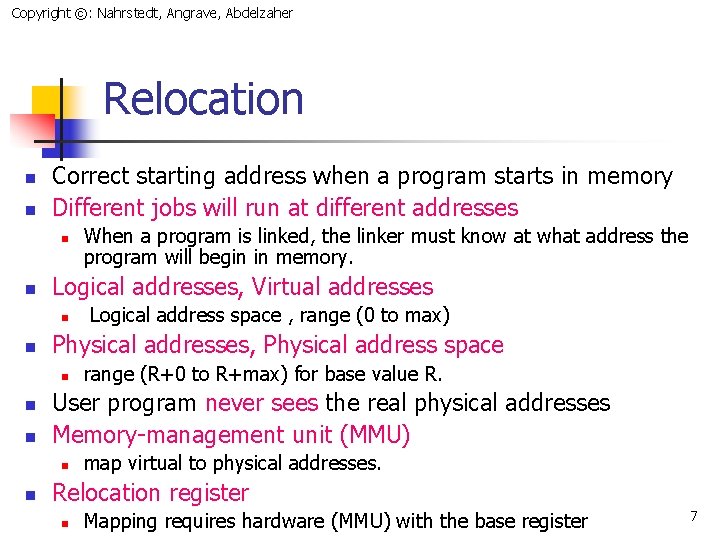

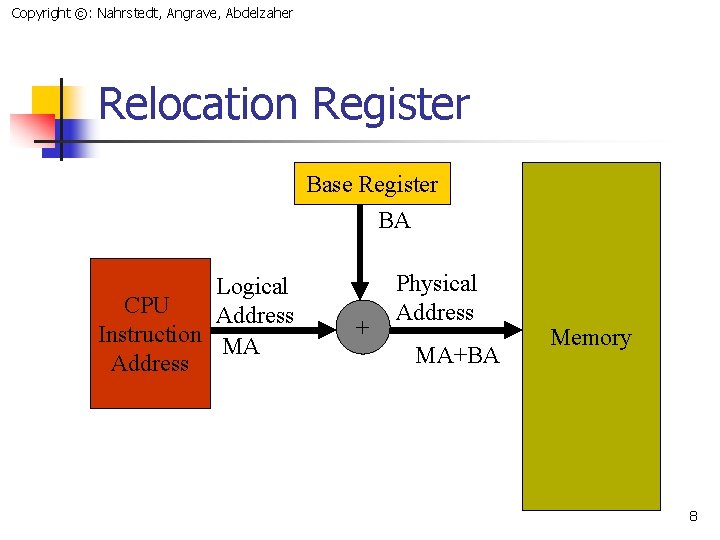

Copyright ©: Nahrstedt, Angrave, Abdelzaher Relocation n n Correct starting address when a program starts in memory Different jobs will run at different addresses n n Logical addresses, Virtual addresses n n n range (R+0 to R+max) for base value R. User program never sees the real physical addresses Memory-management unit (MMU) n n Logical address space , range (0 to max) Physical addresses, Physical address space n n When a program is linked, the linker must know at what address the program will begin in memory. map virtual to physical addresses. Relocation register n Mapping requires hardware (MMU) with the base register 7

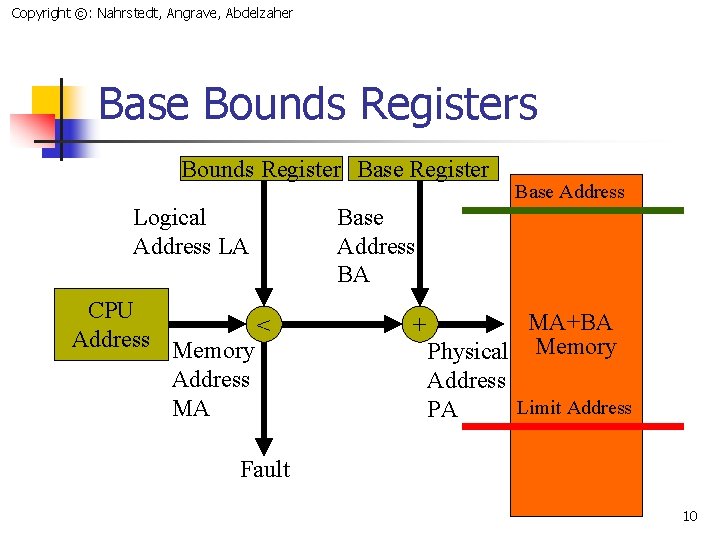

Copyright ©: Nahrstedt, Angrave, Abdelzaher Relocation Register Base Register BA Logical CPU Address Instruction MA Address + Physical Address MA+BA Memory 8

Copyright ©: Nahrstedt, Angrave, Abdelzaher Question 1 - Protection n Problem: n n How to prevent a malicious process to write or jump into other user's or OS partitions Solution: n Base bounds registers 9

Copyright ©: Nahrstedt, Angrave, Abdelzaher Base Bounds Registers Bounds Register Base Register Logical Address LA CPU < Address Memory Address MA Base Address BA + MA+BA Physical Memory Address Limit Address PA Fault 10

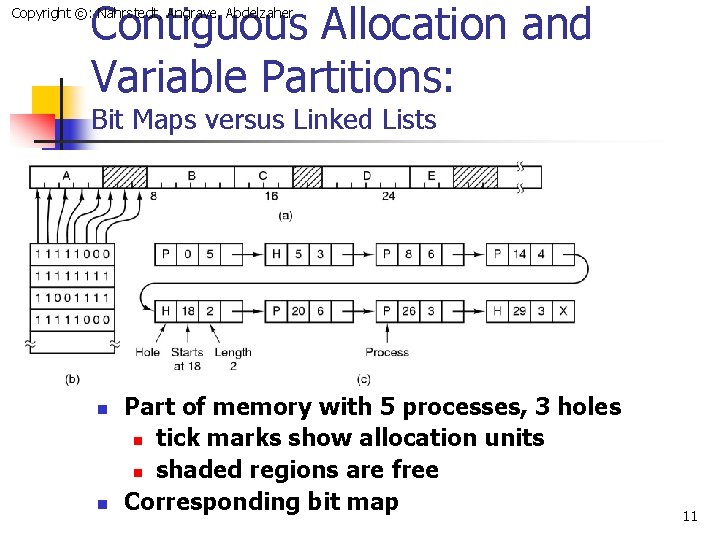

Contiguous Allocation and Variable Partitions: Copyright ©: Nahrstedt, Angrave, Abdelzaher Bit Maps versus Linked Lists n n Part of memory with 5 processes, 3 holes n tick marks show allocation units n shaded regions are free Corresponding bit map 11

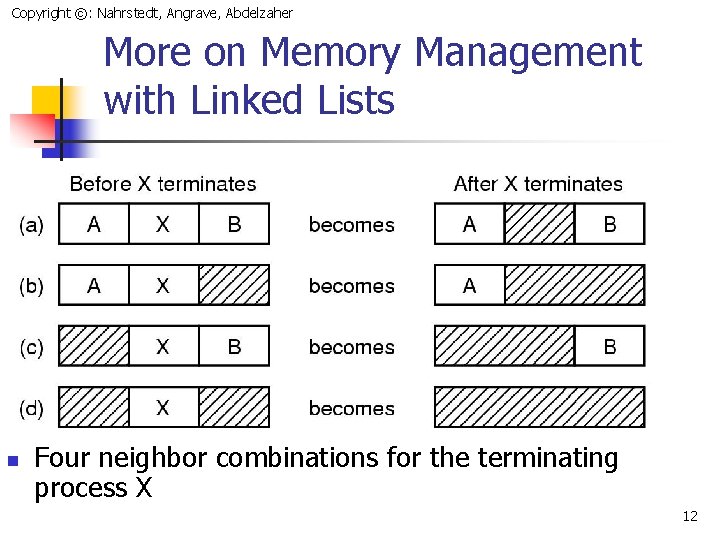

Copyright ©: Nahrstedt, Angrave, Abdelzaher More on Memory Management with Linked Lists n Four neighbor combinations for the terminating process X 12

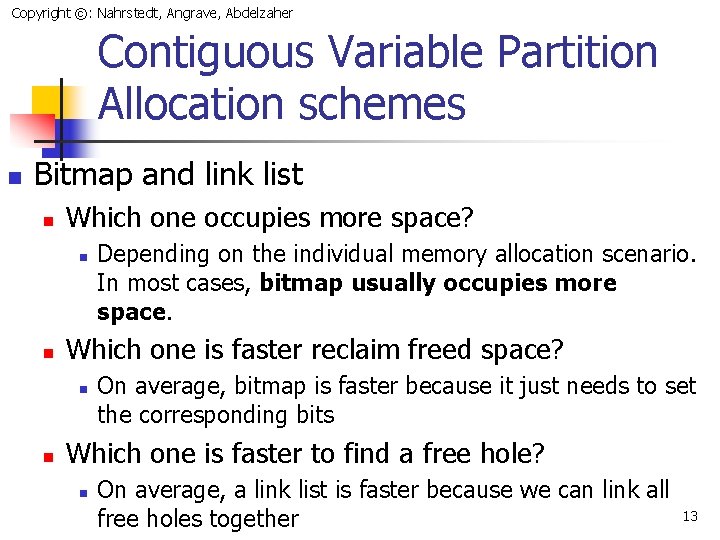

Copyright ©: Nahrstedt, Angrave, Abdelzaher Contiguous Variable Partition Allocation schemes n Bitmap and link list n Which one occupies more space? n n Which one is faster reclaim freed space? n n Depending on the individual memory allocation scenario. In most cases, bitmap usually occupies more space. On average, bitmap is faster because it just needs to set the corresponding bits Which one is faster to find a free hole? n On average, a link list is faster because we can link all free holes together 13

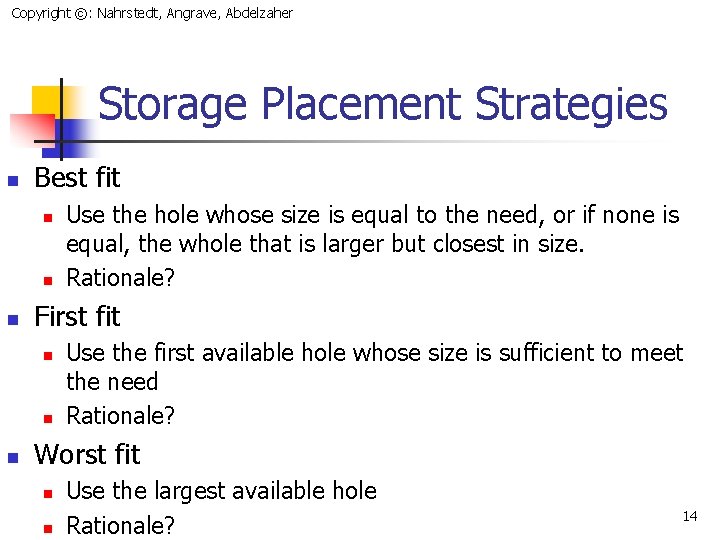

Copyright ©: Nahrstedt, Angrave, Abdelzaher Storage Placement Strategies n Best fit n n n First fit n n n Use the hole whose size is equal to the need, or if none is equal, the whole that is larger but closest in size. Rationale? Use the first available hole whose size is sufficient to meet the need Rationale? Worst fit n n Use the largest available hole Rationale? 14

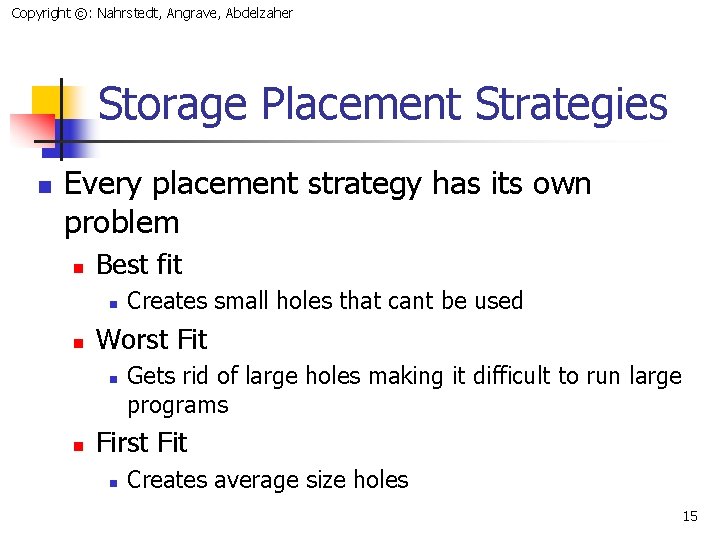

Copyright ©: Nahrstedt, Angrave, Abdelzaher Storage Placement Strategies n Every placement strategy has its own problem n Best fit n n Worst Fit n n Creates small holes that cant be used Gets rid of large holes making it difficult to run large programs First Fit n Creates average size holes 15

Copyright ©: Nahrstedt, Angrave, Abdelzaher How Bad Is Fragmentation? n n n Statistical arguments - Random sizes First-fit Given N allocated blocks 0. 5 N blocks will be lost because of fragmentation Known as 50% RULE 16

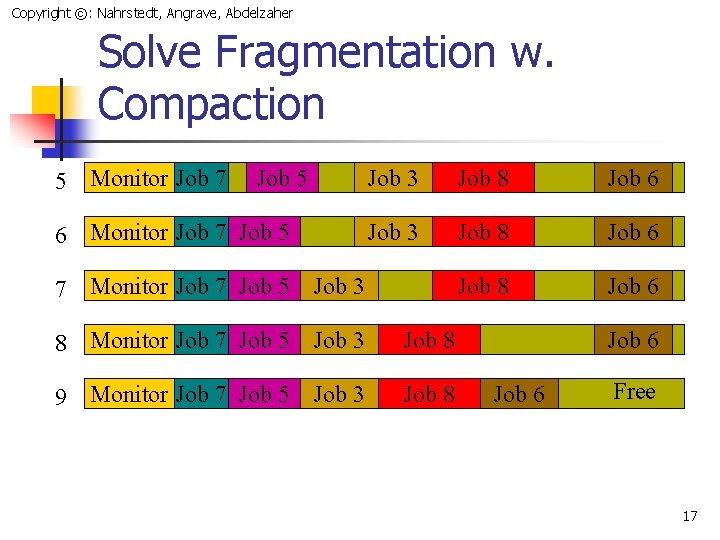

Copyright ©: Nahrstedt, Angrave, Abdelzaher Solve Fragmentation w. Compaction 5 Monitor Job 7 Job 5 6 Monitor Job 7 Job 5 Job 3 Job 8 Free 6 Job 7 Monitor Job 7 Job 5 Job 3 8 Monitor Job 7 Job 5 Job 3 Job 8 9 Monitor Job 7 Job 5 Job 3 Job 8 Free 6 Job 6 Free 17

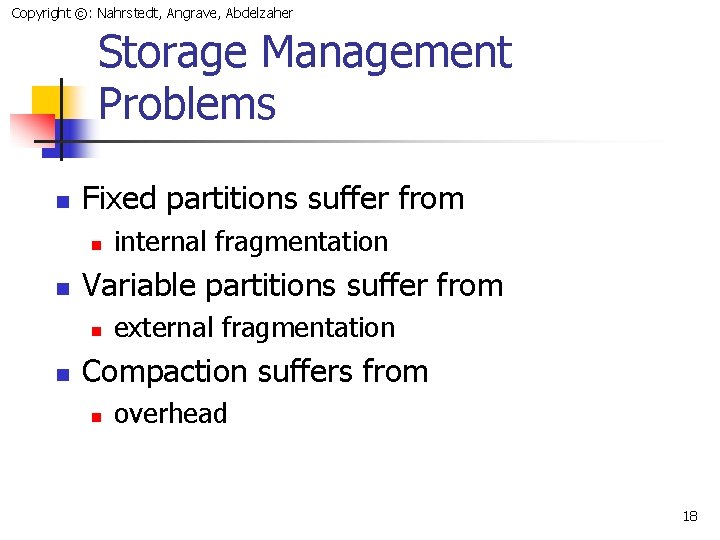

Copyright ©: Nahrstedt, Angrave, Abdelzaher Storage Management Problems n Fixed partitions suffer from n n Variable partitions suffer from n n internal fragmentation external fragmentation Compaction suffers from n overhead 18

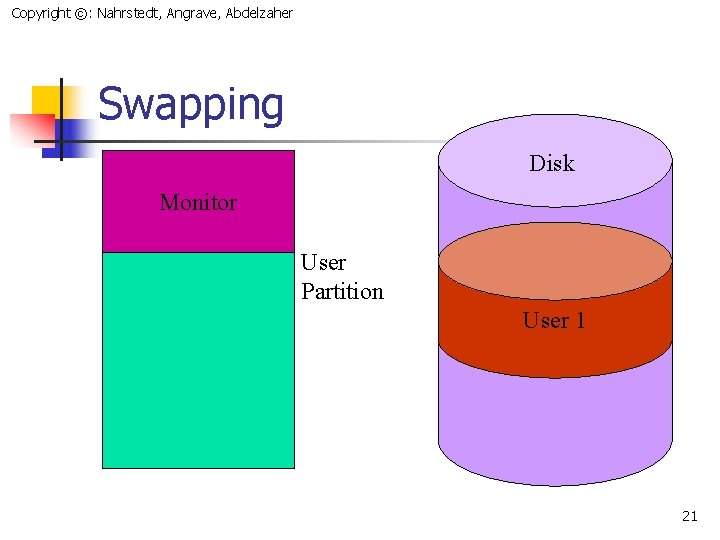

Copyright ©: Nahrstedt, Angrave, Abdelzaher Question n What if there are more processes than what could fit into the memory? 19

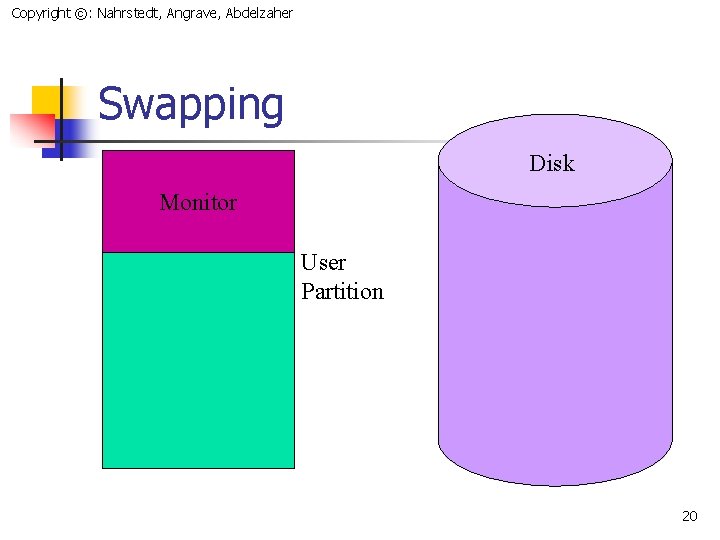

Copyright ©: Nahrstedt, Angrave, Abdelzaher Swapping Disk Monitor User Partition 20

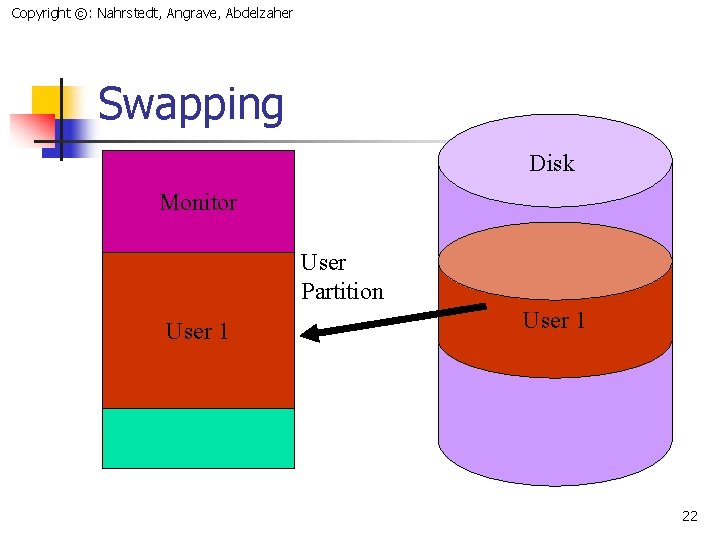

Copyright ©: Nahrstedt, Angrave, Abdelzaher Swapping Disk Monitor User Partition User 1 21

Copyright ©: Nahrstedt, Angrave, Abdelzaher Swapping Disk Monitor User Partition User 1 22

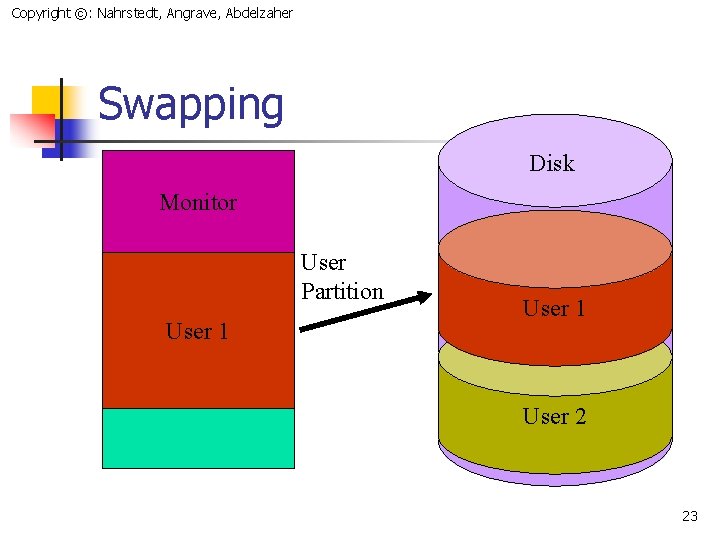

Copyright ©: Nahrstedt, Angrave, Abdelzaher Swapping Disk Monitor User Partition User 1 User 2 23

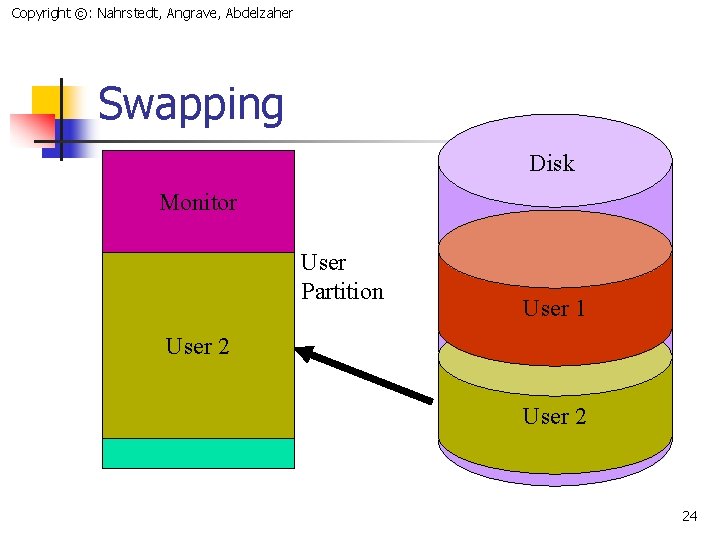

Copyright ©: Nahrstedt, Angrave, Abdelzaher Swapping Disk Monitor User Partition User 1 User 2 24

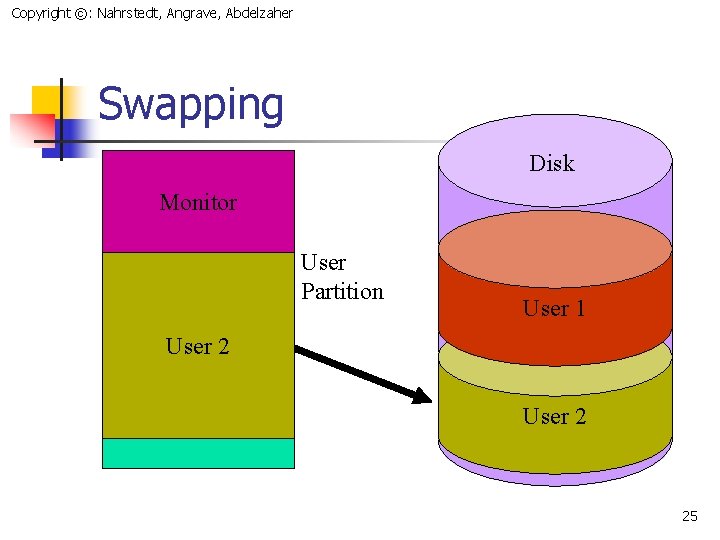

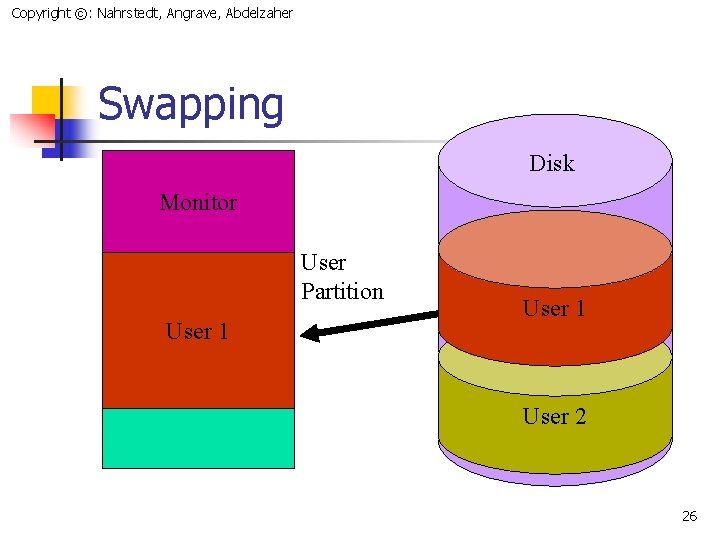

Copyright ©: Nahrstedt, Angrave, Abdelzaher Swapping Disk Monitor User Partition User 1 User 2 25

Copyright ©: Nahrstedt, Angrave, Abdelzaher Swapping Disk Monitor User Partition User 1 User 2 26

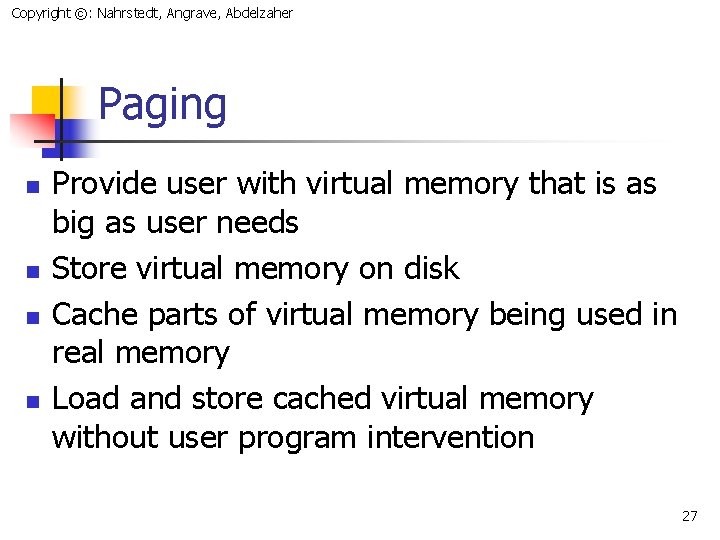

Copyright ©: Nahrstedt, Angrave, Abdelzaher Paging n n Provide user with virtual memory that is as big as user needs Store virtual memory on disk Cache parts of virtual memory being used in real memory Load and store cached virtual memory without user program intervention 27

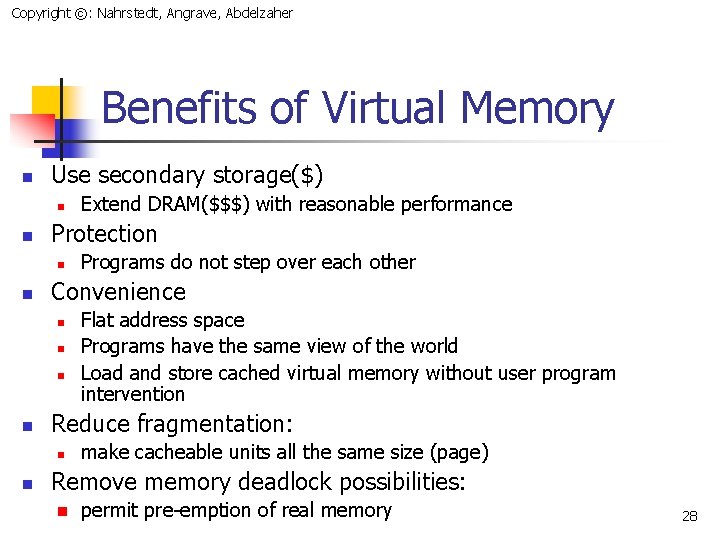

Copyright ©: Nahrstedt, Angrave, Abdelzaher Benefits of Virtual Memory n Use secondary storage($) n n Protection n n Flat address space Programs have the same view of the world Load and store cached virtual memory without user program intervention Reduce fragmentation: n n Programs do not step over each other Convenience n n Extend DRAM($$$) with reasonable performance make cacheable units all the same size (page) Remove memory deadlock possibilities: n permit pre-emption of real memory 28

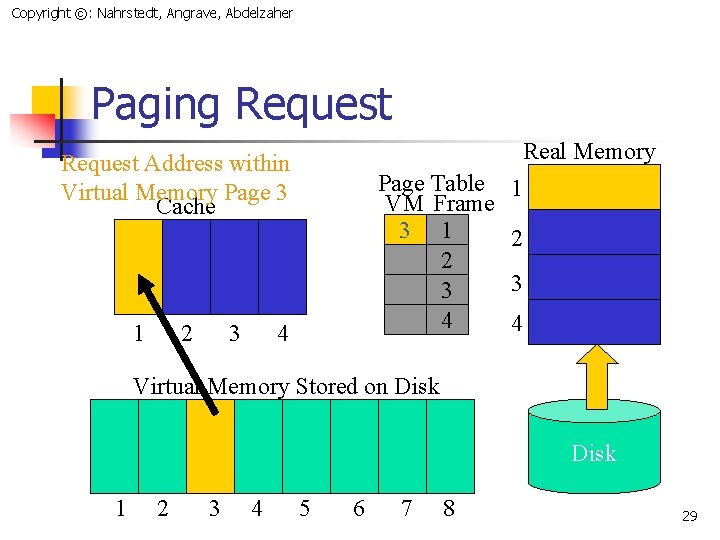

Copyright ©: Nahrstedt, Angrave, Abdelzaher Paging Request Real Memory Request Address within Virtual Memory Page 3 Cache 1 2 3 Page Table VM Frame 3 1 2 3 4 4 1 2 3 4 Virtual Memory Stored on Disk 1 2 3 4 5 6 7 8 29

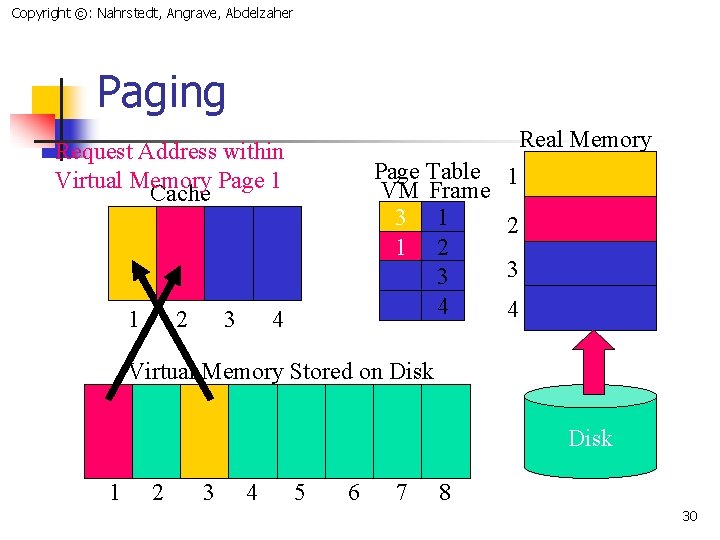

Copyright ©: Nahrstedt, Angrave, Abdelzaher Paging Real Memory Request Address within Virtual Memory Page 1 Cache 1 2 3 Page Table VM Frame 3 1 1 2 3 4 4 1 2 3 4 Virtual Memory Stored on Disk 1 2 3 4 5 6 7 8 30

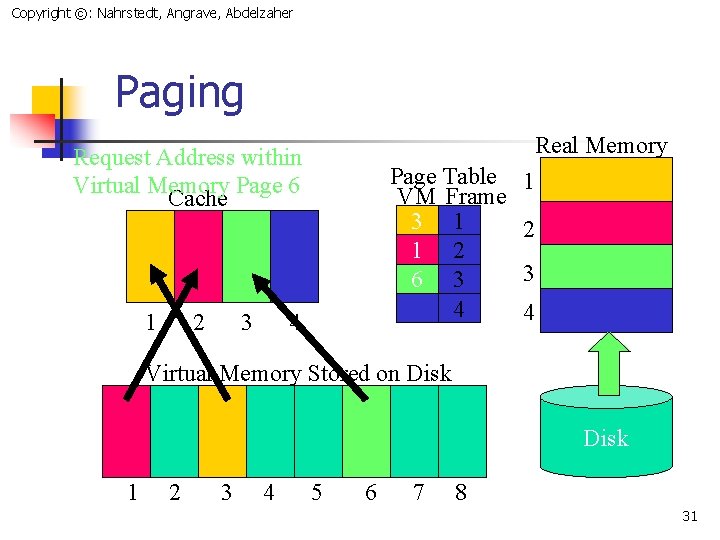

Copyright ©: Nahrstedt, Angrave, Abdelzaher Paging Real Memory Request Address within Virtual Memory Page 6 Cache 1 2 3 Page Table VM Frame 3 1 1 2 6 3 4 4 1 2 3 4 Virtual Memory Stored on Disk 1 2 3 4 5 6 7 8 31

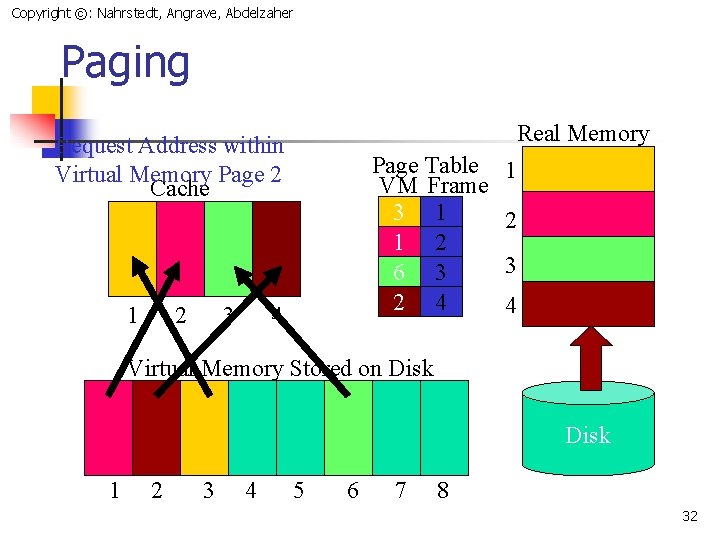

Copyright ©: Nahrstedt, Angrave, Abdelzaher Paging Real Memory Request Address within Virtual Memory Page 2 Cache 1 2 3 Page Table VM Frame 3 1 1 2 6 3 2 4 4 1 2 3 4 Virtual Memory Stored on Disk 1 2 3 4 5 6 7 8 32

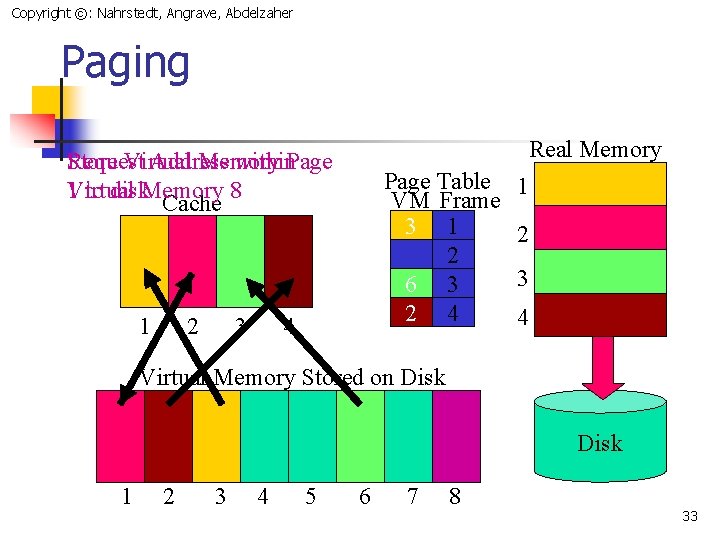

Copyright ©: Nahrstedt, Angrave, Abdelzaher Paging Real Memory Request Store Virtual Address Memory within. Page 1 to disk. Memory 8 Virtual Cache 1 2 3 Page Table VM Frame 3 1 1 2 6 3 2 4 4 1 2 3 4 Virtual Memory Stored on Disk 1 2 3 4 5 6 7 8 33

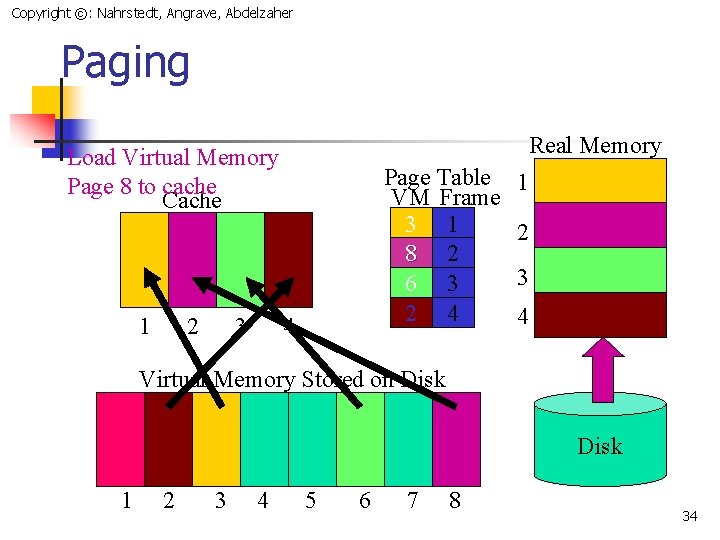

Copyright ©: Nahrstedt, Angrave, Abdelzaher Paging Real Memory Load Virtual Memory Page 8 to cache Cache 1 2 3 Page Table VM Frame 3 1 8 2 6 3 2 4 4 1 2 3 4 Virtual Memory Stored on Disk 1 2 3 4 5 6 7 8 34

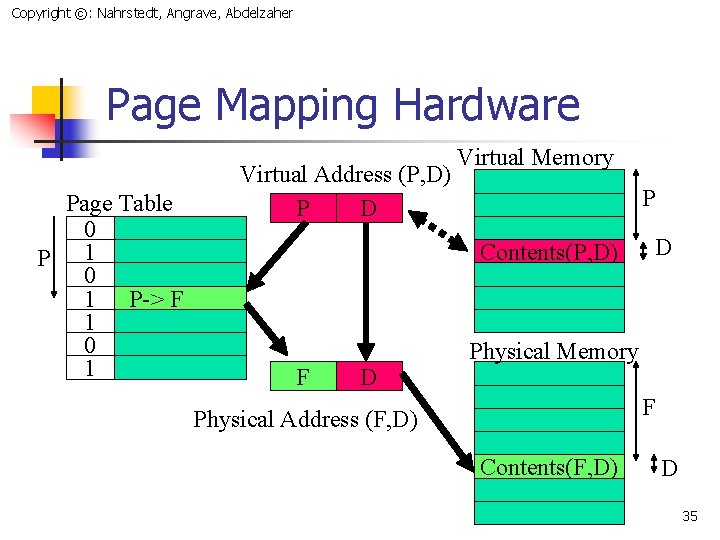

Copyright ©: Nahrstedt, Angrave, Abdelzaher Page Mapping Hardware Page Table 0 P 1 0 1 P-> F 1 0 1 Virtual Address (P, D) P D Virtual Memory P Contents(P, D) F D D Physical Memory F Physical Address (F, D) Contents(F, D) D 35

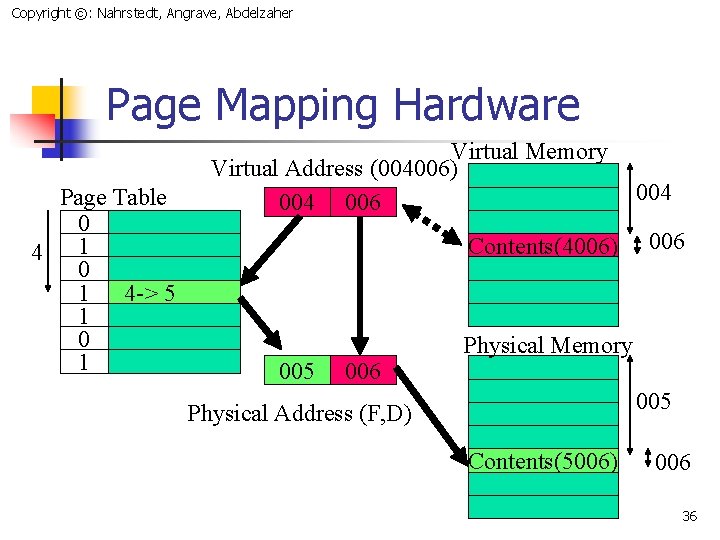

Copyright ©: Nahrstedt, Angrave, Abdelzaher Page Mapping Hardware Page Table 0 4 1 0 1 4 -> 5 1 0 1 Virtual Memory Virtual Address (004006) 004 006 Contents(4006) 005 006 004 006 Physical Memory 005 Physical Address (F, D) Contents(5006) 006 36

Copyright ©: Nahrstedt, Angrave, Abdelzaher Paging Issues n size of page is 2 n , usually 512, 1 k, 2 k, 4 k, or 8 k n n E. g. 32 bit VM address may have 220 (1 meg) pages with 4 k (212 ) bytes per page Rational? 37

Copyright ©: Nahrstedt, Angrave, Abdelzaher Paging Issues n n 220 (1 meg) 32 bit page entries take 222 bytes (4 meg) page frames must map into real memory 38

Copyright ©: Nahrstedt, Angrave, Abdelzaher Paging Issues n Question n Physical memory size: 32 MB (2^25 ) Page size 4 K bytes How many pages? n n Page Table base register must be changed for context switch n Why? n n n 2^13 Different page table NO external fragmentation Internal fragmentation on last page ONLY 39

Copyright ©: Nahrstedt, Angrave, Abdelzaher Paging - Caching the Page Table n n Can cache page table in registers and keep page table in memory at location given by a page table base register Page table base register changed at context switch time 40

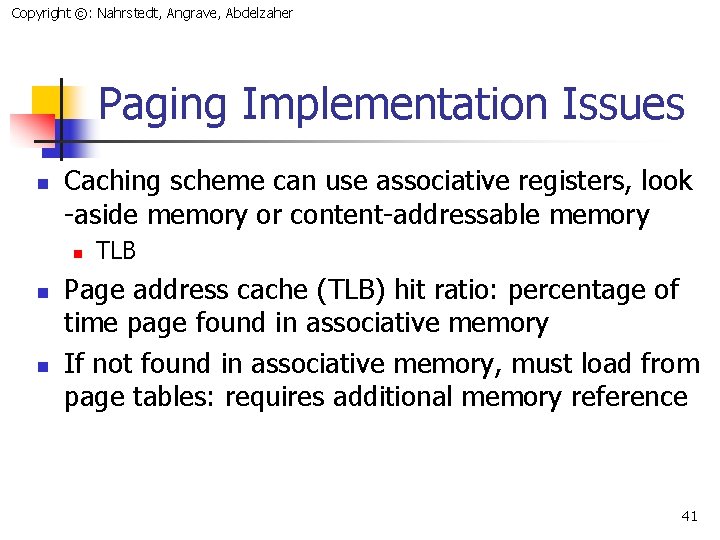

Copyright ©: Nahrstedt, Angrave, Abdelzaher Paging Implementation Issues n Caching scheme can use associative registers, look -aside memory or content-addressable memory n n n TLB Page address cache (TLB) hit ratio: percentage of time page found in associative memory If not found in associative memory, must load from page tables: requires additional memory reference 41

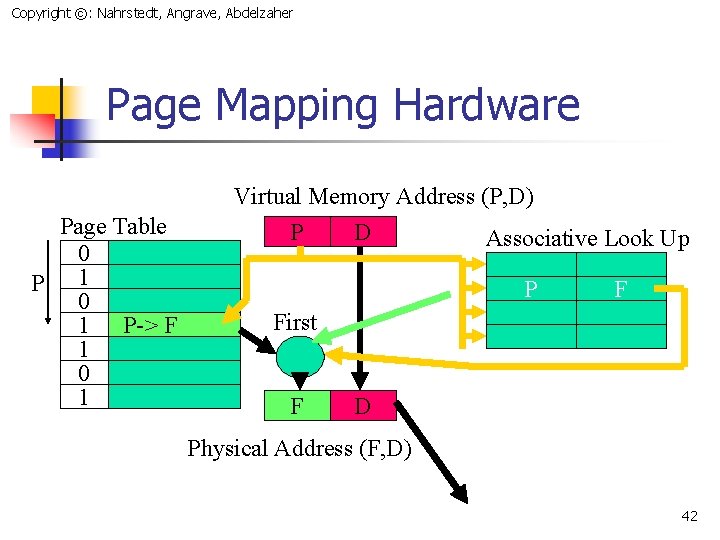

Copyright ©: Nahrstedt, Angrave, Abdelzaher Page Mapping Hardware Page Table 0 P 1 0 1 P-> F 1 0 1 Virtual Memory Address (P, D) P D Associative Look Up P F First F D Physical Address (F, D) 42

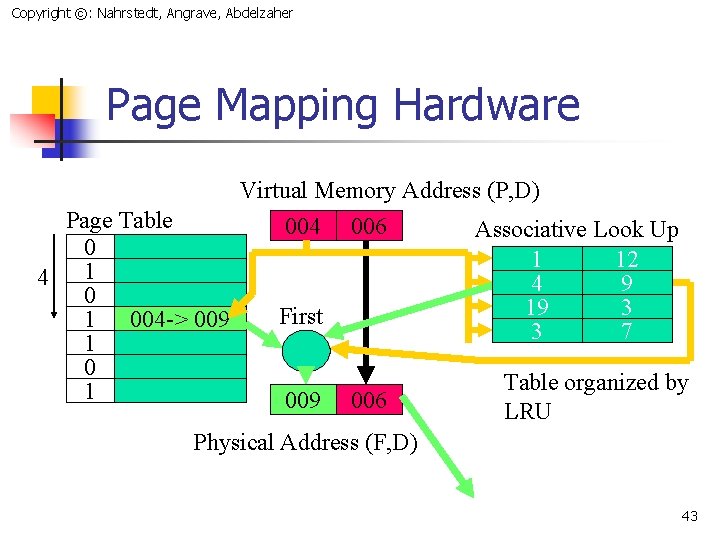

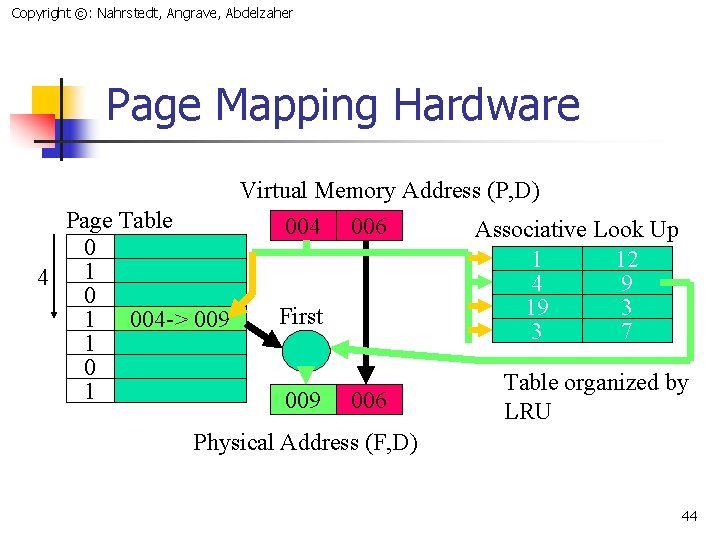

Copyright ©: Nahrstedt, Angrave, Abdelzaher Page Mapping Hardware Virtual Memory Address (P, D) Page Table 004 006 Associative Look Up 0 1 12 1 4 47 96 0 19 3 First 1 004 -> 009 3 7 1 0 Table organized by 1 009 006 LRU Physical Address (F, D) 43

Copyright ©: Nahrstedt, Angrave, Abdelzaher Page Mapping Hardware Virtual Memory Address (P, D) Page Table 004 006 Associative Look Up 0 1 12 1 4 4 9 0 19 3 First 1 004 -> 009 3 7 1 0 Table organized by 1 009 006 LRU Physical Address (F, D) 44

- Slides: 44