Lecture 21 IDDQ Current Testing n n n

- Slides: 39

Lecture 21 IDDQ Current Testing n n n n Definition Faults detected by IDDQ tests Vector generation for IDDQ tests § Full-scan § Quietest Instrumentation difficulties Sematech study Limitations of IDDQ testing Summary Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 1

Motivation n Early 1990’s – Fabrication Line had 50 to 1000 defects per million (dpm) chips § IBM wants to get 3. 4 defects per million (dpm) chips (0 defects, 6 s) Conventional way to reduce defects: § Increasing test fault coverage § Increasing burn-in coverage § Increase Electro-Static Damage awareness New way to reduce defects: § IDDQ Testing – also useful for Failure Effect Analysis Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 2

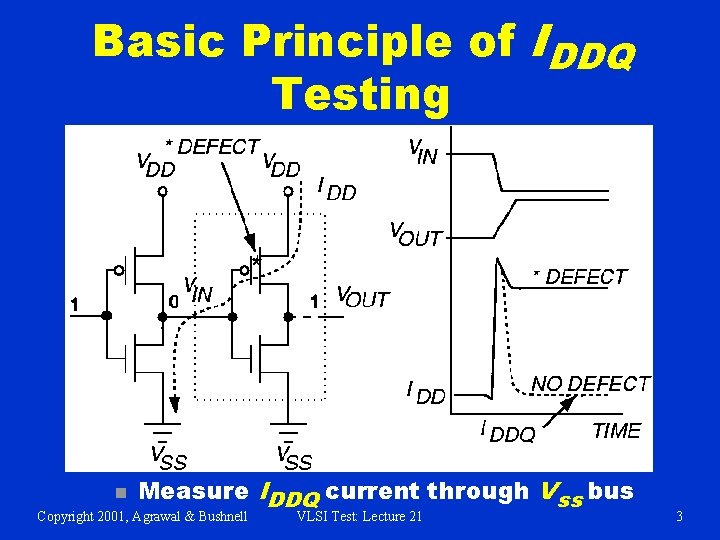

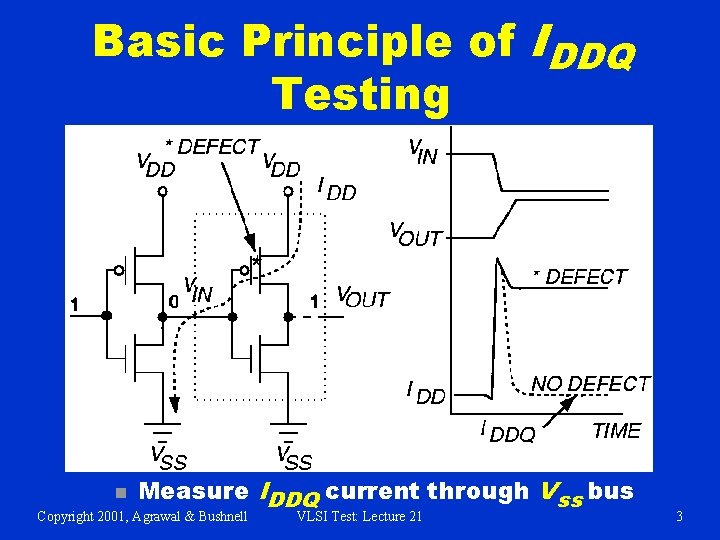

Basic Principle of IDDQ Testing n Measure IDDQ current through Vss bus Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 3

Faults Detected by IDDQ Tests Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 4

Stuck-at Faults Detected by IDDQ Tests n n Bridging faults with stuck-at fault behavior § Levi – Bridging of a logic node to VDD or VSS – few of these § Transistor gate oxide short of 1 KW to 5 KW Floating MOSFET gate defects – do not fully turn off transistor Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 5

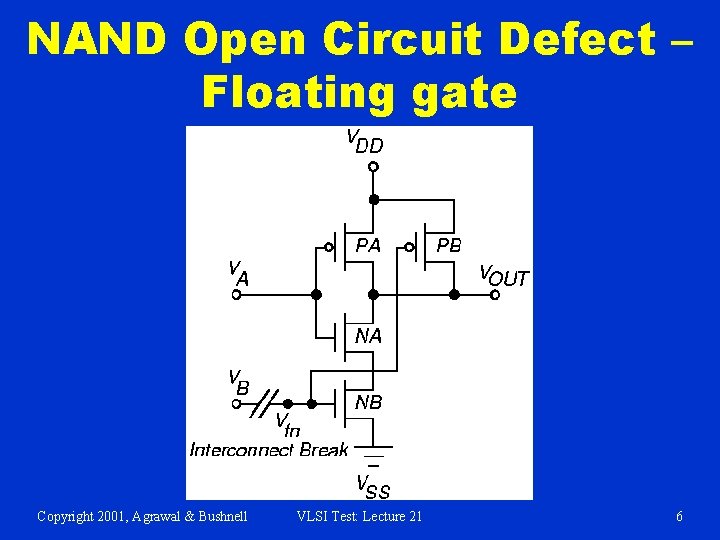

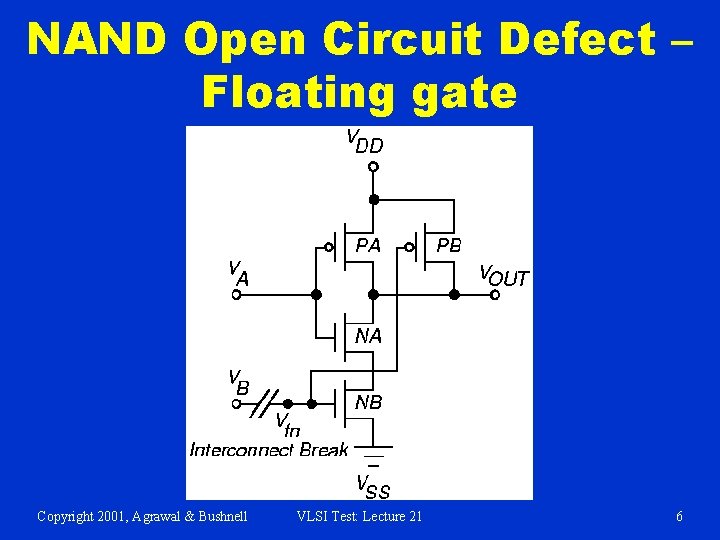

NAND Open Circuit Defect – Floating gate Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 6

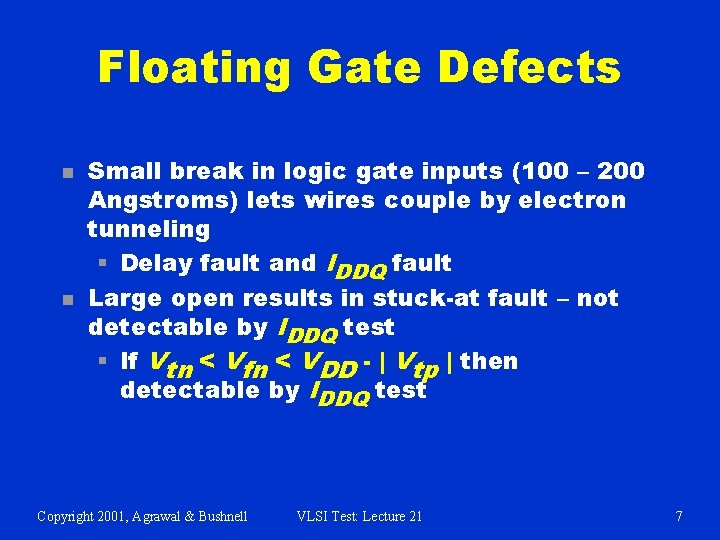

Floating Gate Defects n n Small break in logic gate inputs (100 – 200 Angstroms) lets wires couple by electron tunneling § Delay fault and IDDQ fault Large open results in stuck-at fault – not detectable by IDDQ test § If Vtn < Vfn < VDD - | Vtp | then detectable by IDDQ test Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 7

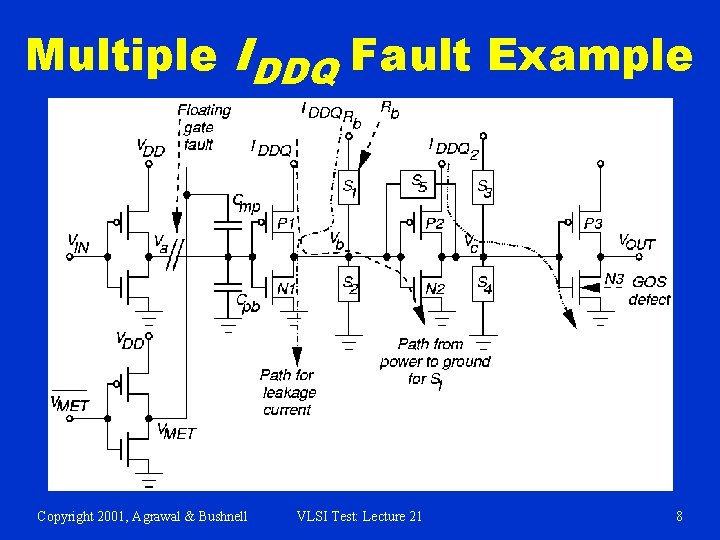

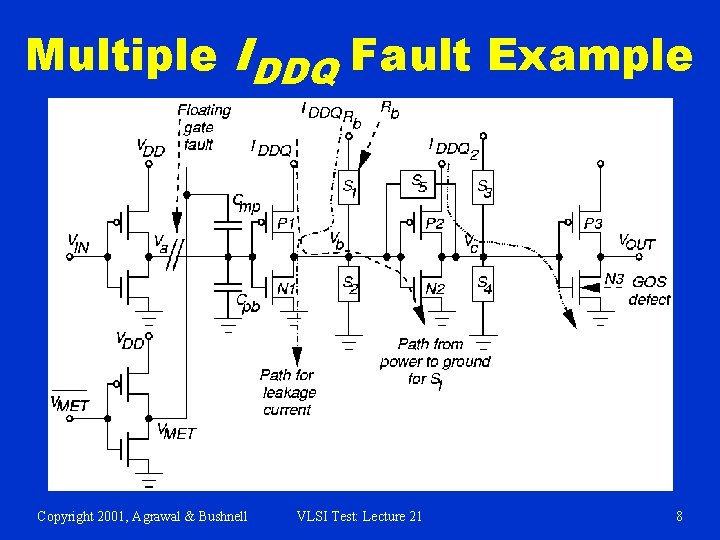

Multiple IDDQ Fault Example Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 8

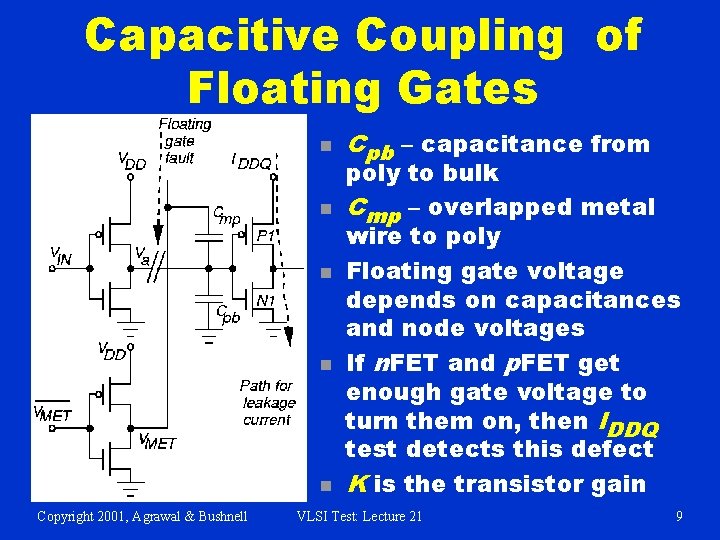

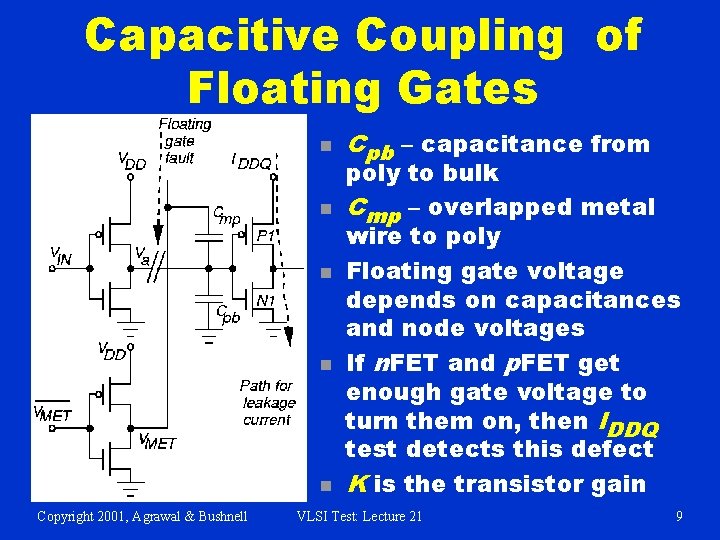

Capacitive Coupling of Floating Gates n n n Copyright 2001, Agrawal & Bushnell Cpb – capacitance from poly to bulk Cmp – overlapped metal wire to poly Floating gate voltage depends on capacitances and node voltages If n. FET and p. FET get enough gate voltage to turn them on, then IDDQ test detects this defect K is the transistor gain VLSI Test: Lecture 21 9

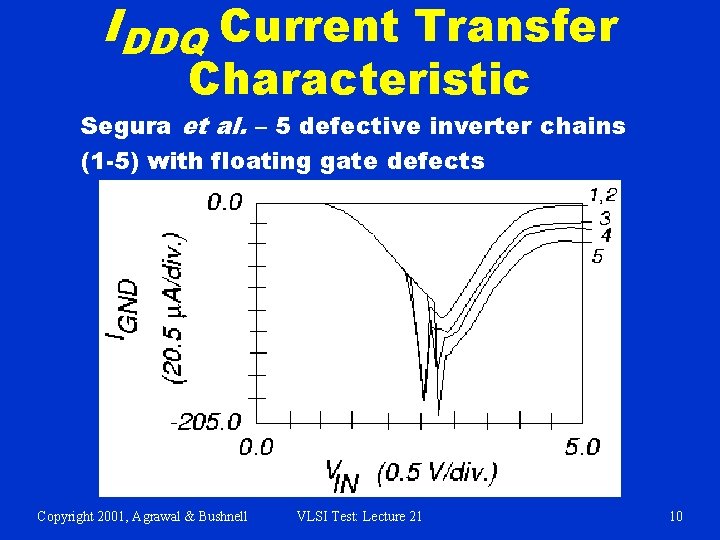

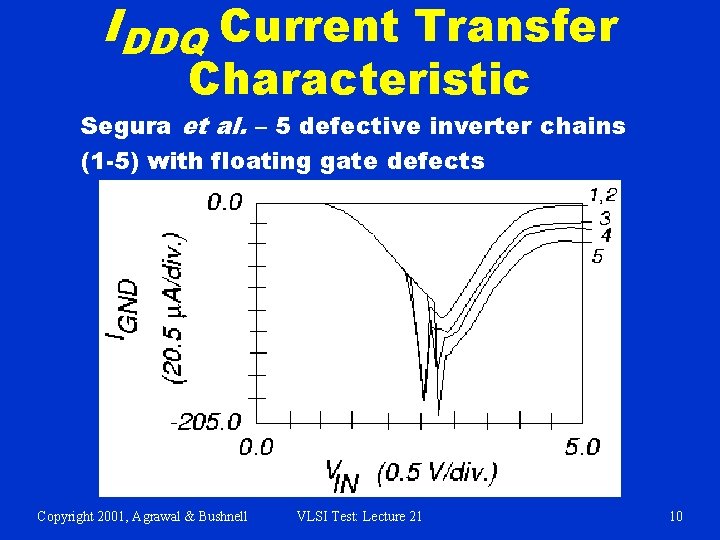

IDDQ Current Transfer Characteristic Segura et al. – 5 defective inverter chains (1 -5) with floating gate defects Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 10

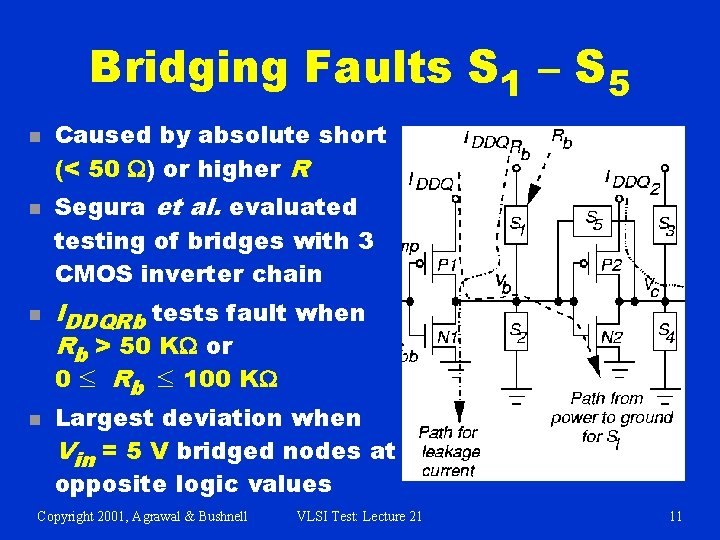

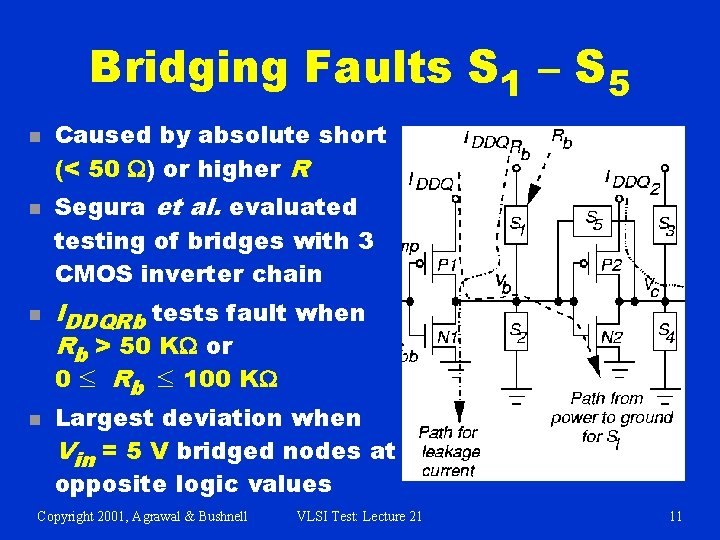

Bridging Faults S 1 – S 5 n n Caused by absolute short (< 50 W) or higher R Segura et al. evaluated testing of bridges with 3 CMOS inverter chain IDDQRb tests fault when Rb > 50 KW or 0 £ Rb £ 100 KW Largest deviation when Vin = 5 V bridged nodes at opposite logic values Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 11

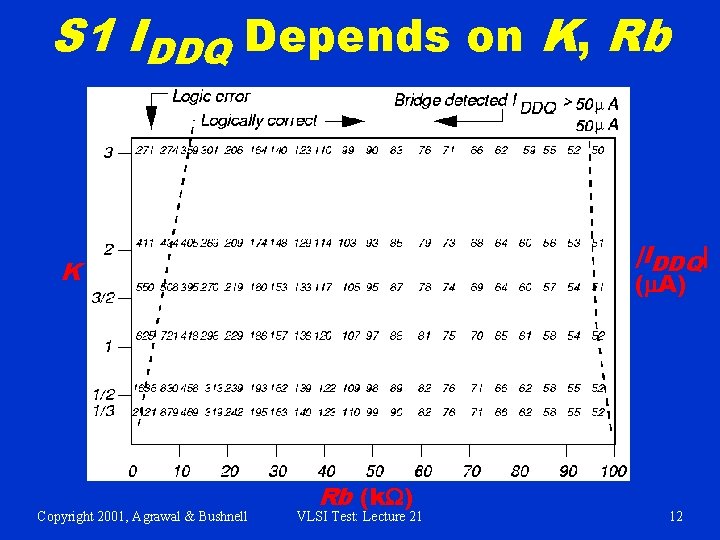

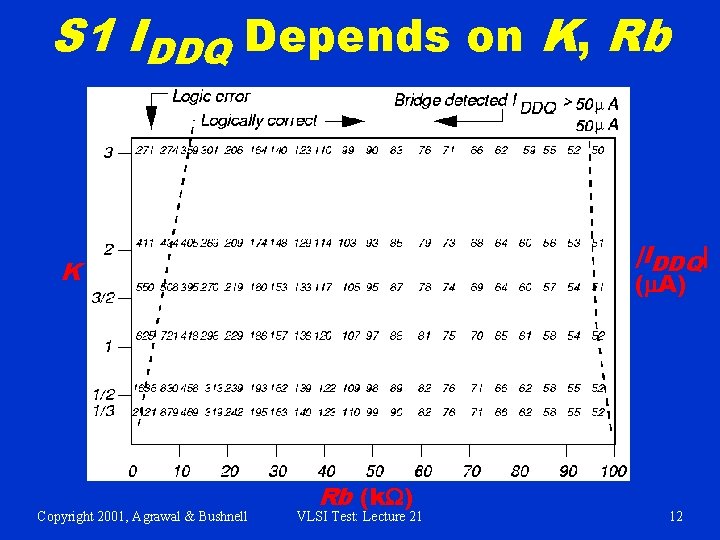

S 1 IDDQ Depends on K, Rb |IDDQ| K Copyright 2001, Agrawal & Bushnell (m. A) Rb (k. W) VLSI Test: Lecture 21 12

CMOS Transistor Stuck. Open Faults n IDDQ test can sometimes detect fault § Works in practice due to body effect Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 13

Delay Faults n n n Most random CMOS defects cause a timing delay fault, not catastrophic failure Many delay faults detected by IDDQ test – late switching of logic gates keeps IDDQ elevated Delay faults not detected by IDDQ test § Resistive via fault in interconnect § Increased transistor threshold voltage fault Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 14

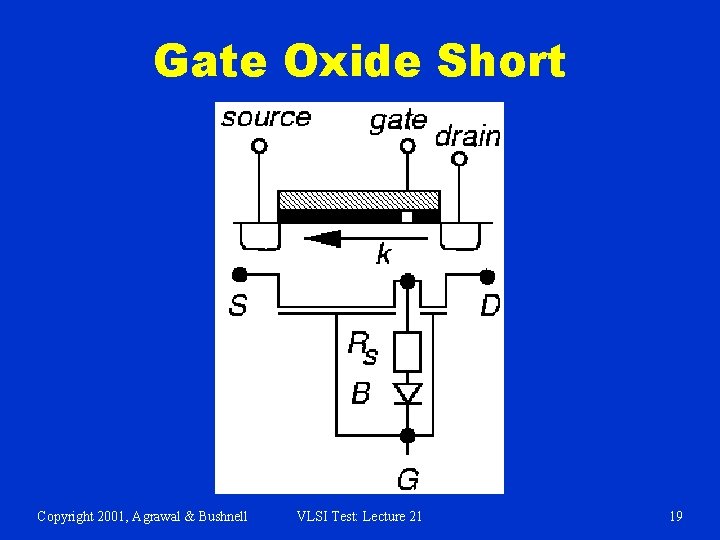

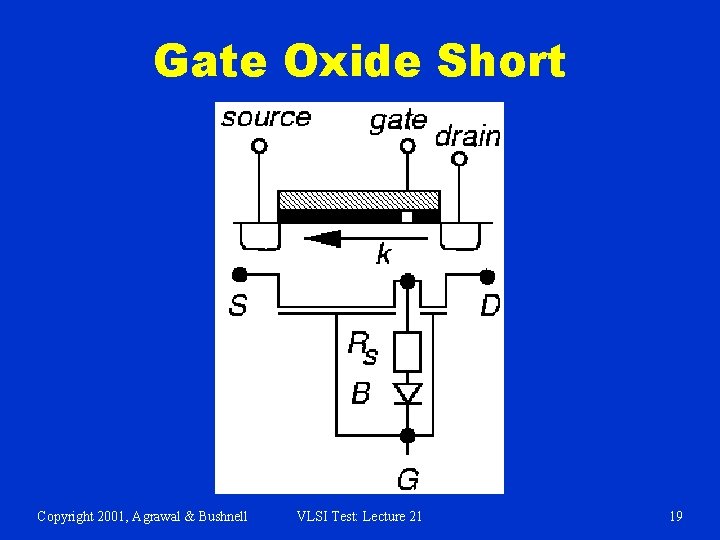

Leakage Faults n Gate oxide shorts cause leaks between gate & source or gate & drain n Mao and Gulati leakage fault model: § Leakage path flags: f. GS, f. GD, f. SD, f. BS, f. BD, f. BG G = gate, S = source, D = drain, B = bulk n Assume that short does not change logic values Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 15

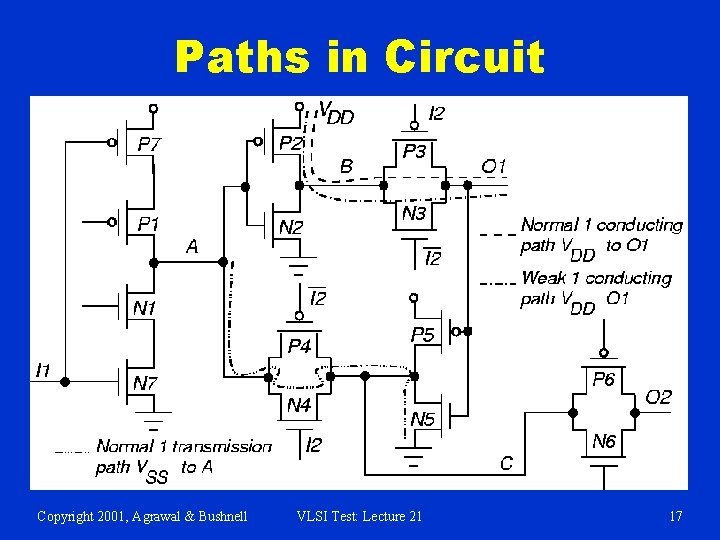

Weak Faults n n. FET passes logic 1 as 5 V – Vtn p. FET passes logic 0 as 0 V + |Vtp| Weak fault – one device in C-switch does not turn on § Causes logic value degradation in C-switch Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 16

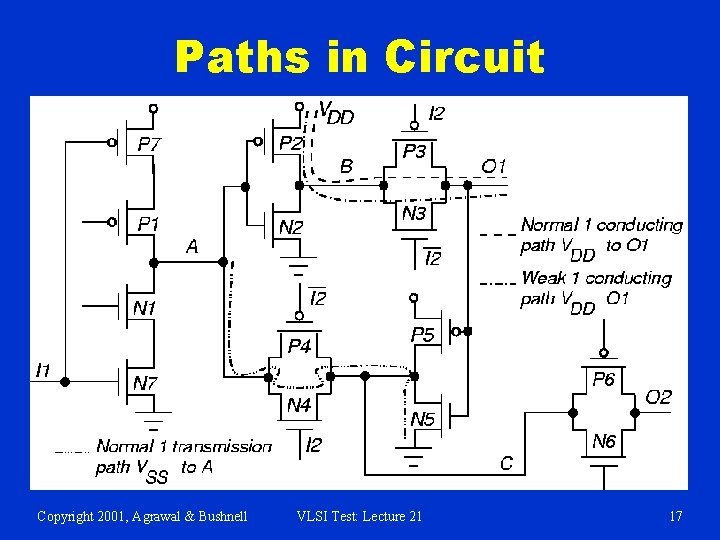

Paths in Circuit Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 17

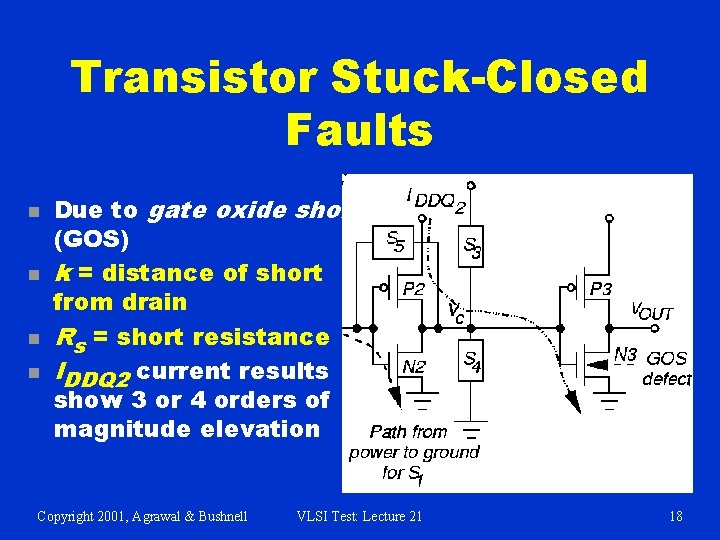

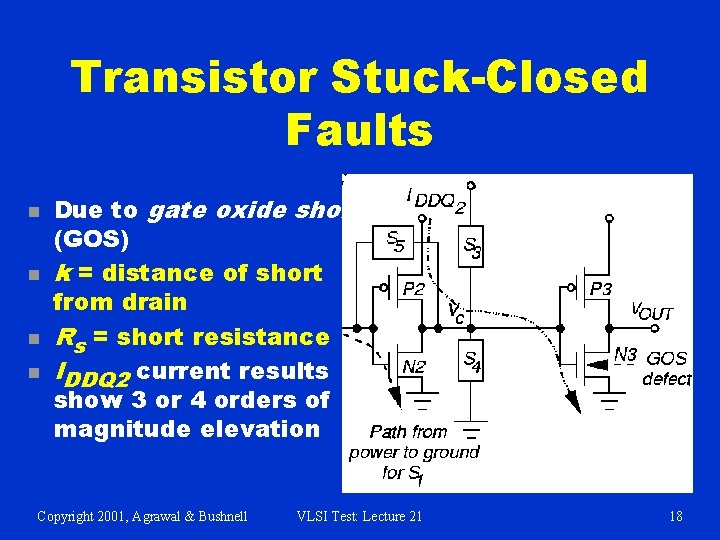

Transistor Stuck-Closed Faults n n Due to gate oxide short (GOS) k = distance of short from drain Rs = short resistance IDDQ 2 current results show 3 or 4 orders of magnitude elevation Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 18

Gate Oxide Short Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 19

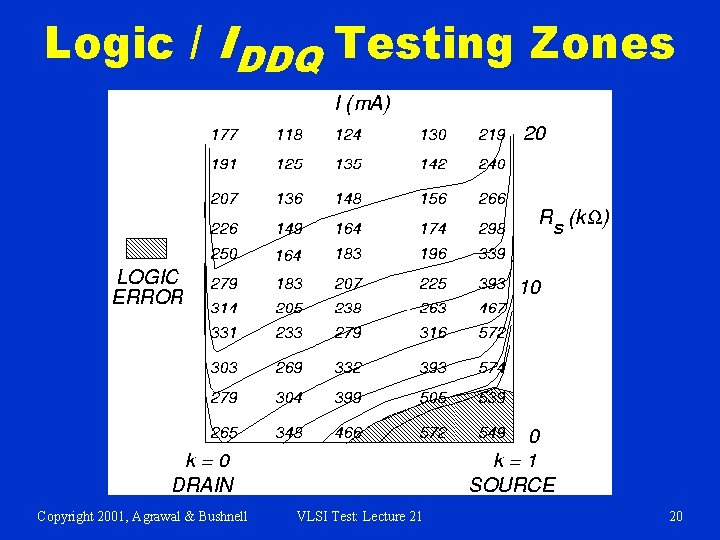

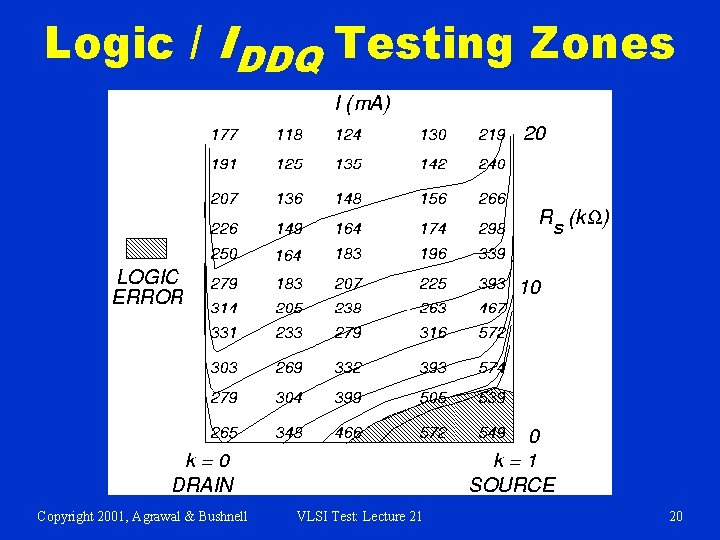

Logic / IDDQ Testing Zones Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 20

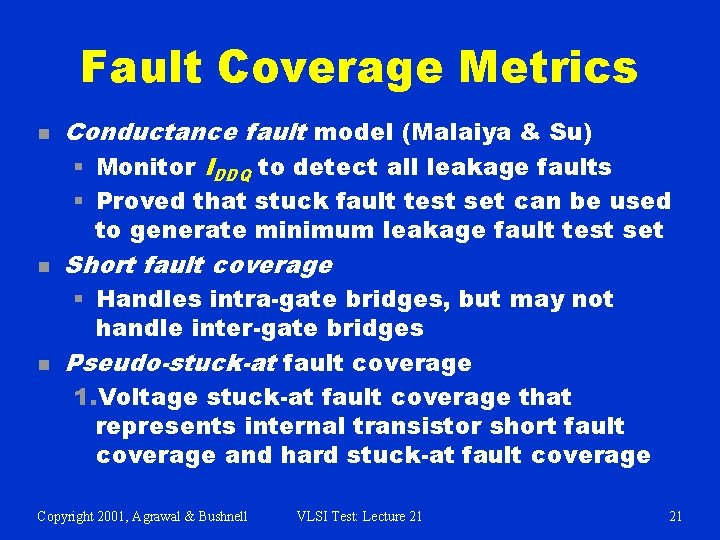

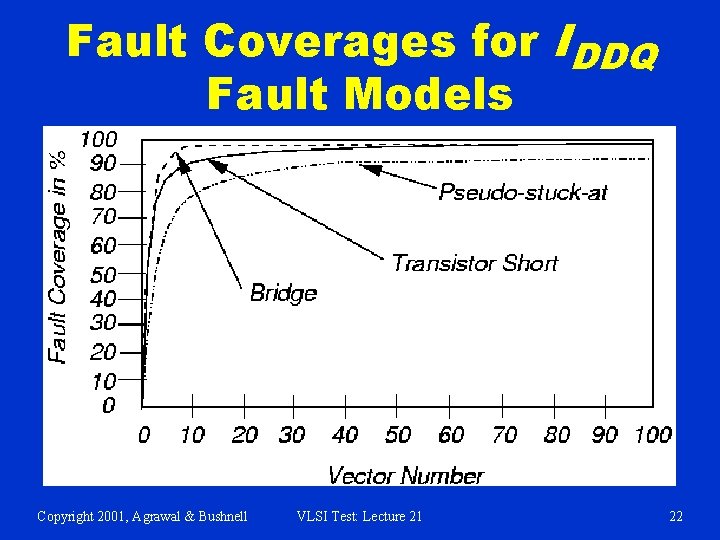

Fault Coverage Metrics n Conductance fault model (Malaiya & Su) § Monitor IDDQ to detect all leakage faults § Proved that stuck fault test set can be used to generate minimum leakage fault test set n n Short fault coverage § Handles intra-gate bridges, but may not handle inter-gate bridges Pseudo-stuck-at fault coverage 1. Voltage stuck-at fault coverage that represents internal transistor short fault coverage and hard stuck-at fault coverage Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 21

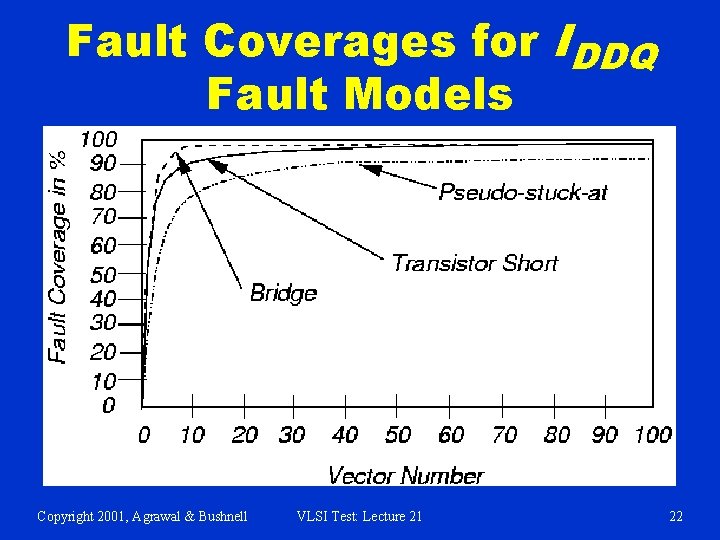

Fault Coverages for IDDQ Fault Models Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 22

Vector Selection with Full Scan -- Perry n n Use voltage testing & full scan for IDDQ tests Measure IDDQ current when voltage vector set hits internal scan boundary § Set all nodes, inputs & outputs in known state § Stop clock & apply minimum IDDQ current vector § Wait 30 ms for settling, measure IDDQ against 75 m. A Limit, with 1 m. A accuracy Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 23

Quietest Leakage Fault Detection – Mao and Gulati n Sensitize leakage fault n Detection – 2 transistor terminals with leakage must have opposite logic values, & be at driving strengths n Non-driving, high-impedance states won’t work – current cannot go through them Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 24

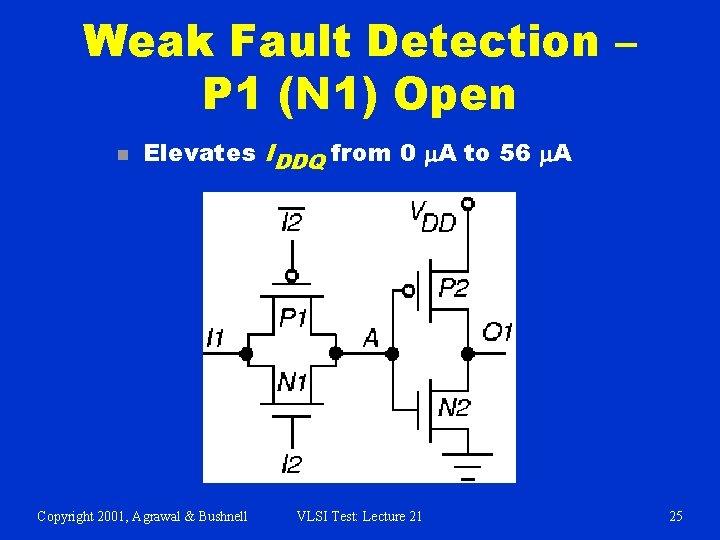

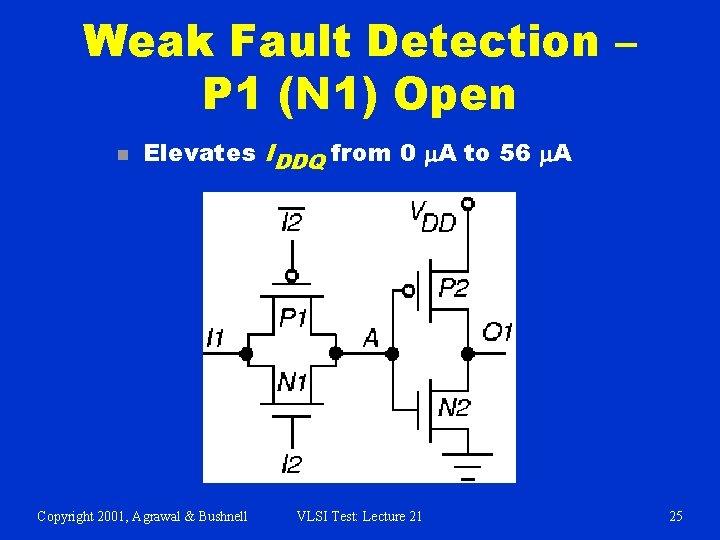

Weak Fault Detection – P 1 (N 1) Open n Elevates IDDQ from 0 m. A to 56 m. A Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 25

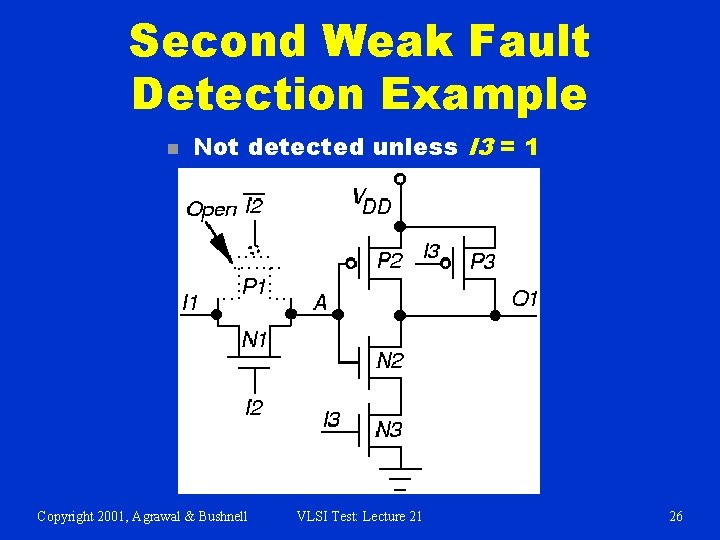

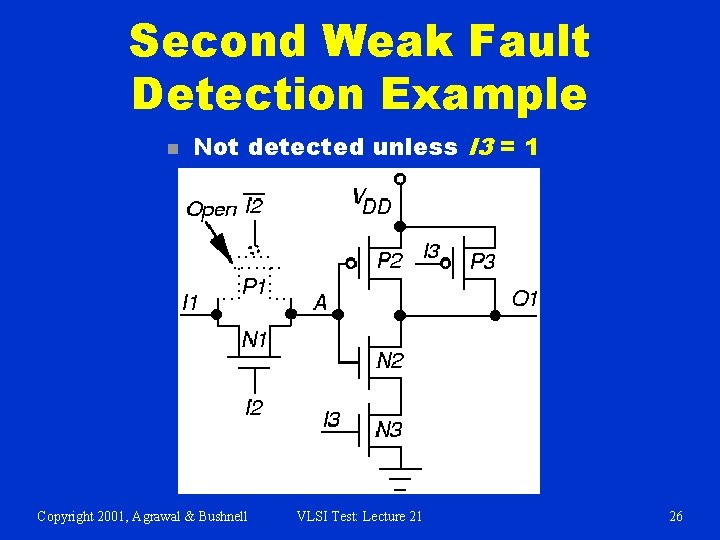

Second Weak Fault Detection Example n Not detected unless I 3 = 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 26

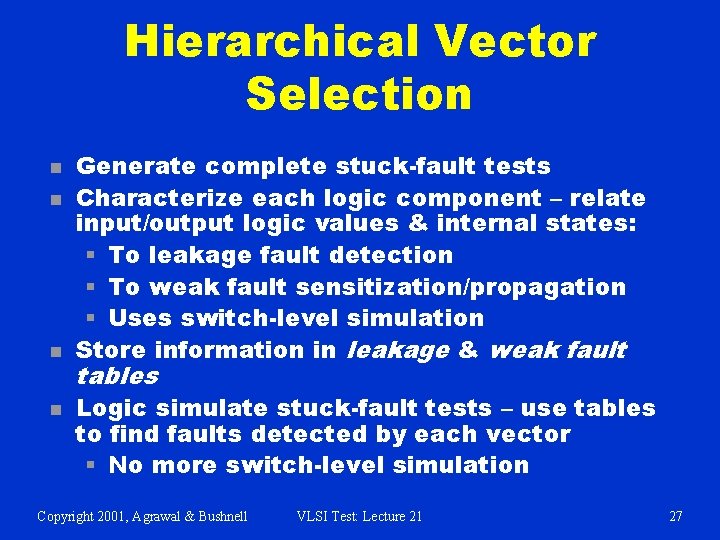

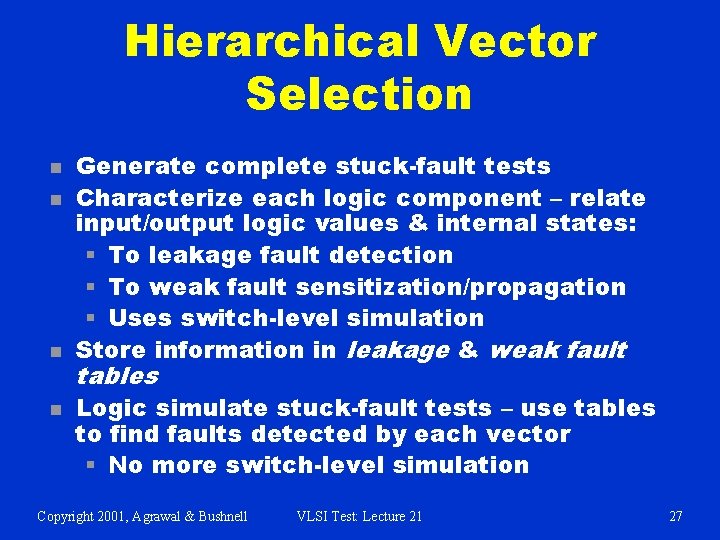

Hierarchical Vector Selection n n Generate complete stuck-fault tests Characterize each logic component – relate input/output logic values & internal states: § To leakage fault detection § To weak fault sensitization/propagation § Uses switch-level simulation Store information in leakage & weak fault tables Logic simulate stuck-fault tests – use tables to find faults detected by each vector § No more switch-level simulation Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 27

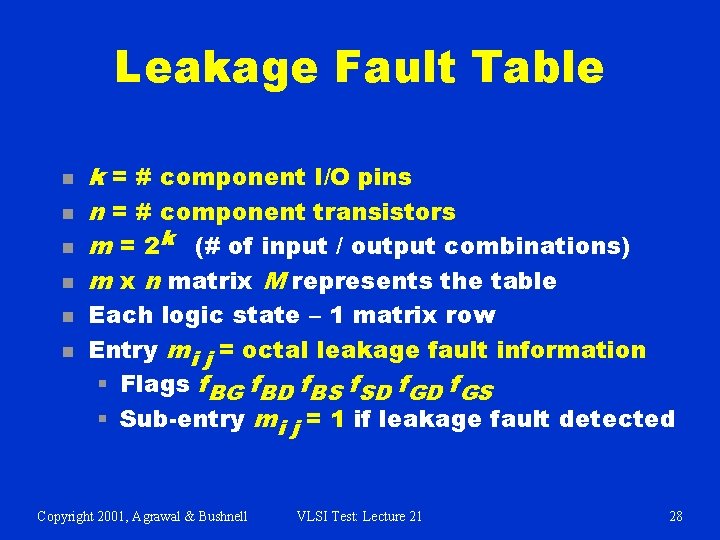

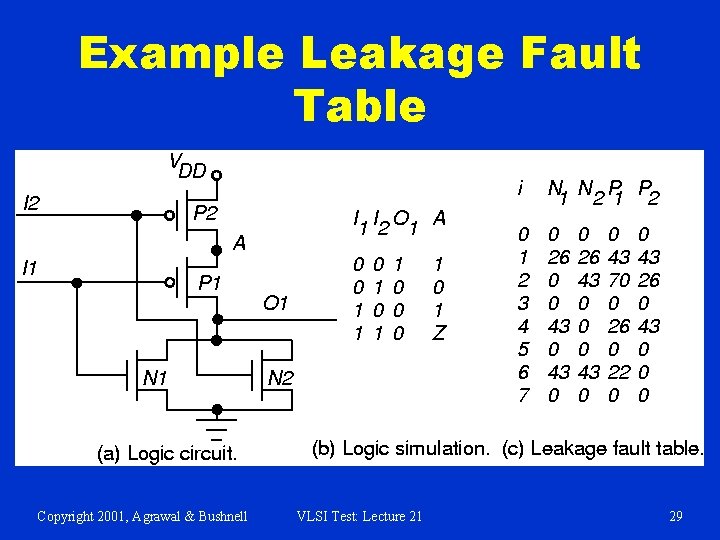

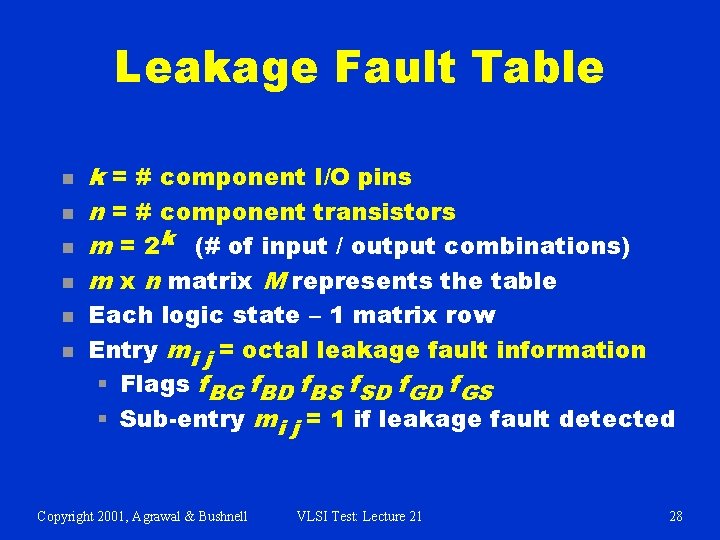

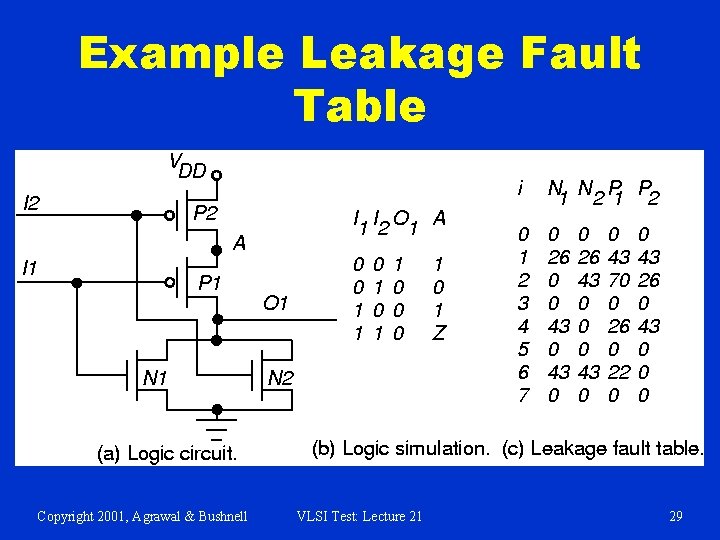

Leakage Fault Table n n n k = # component I/O pins n = # component transistors m = 2 k (# of input / output combinations) m x n matrix M represents the table Each logic state – 1 matrix row Entry mi j = octal leakage fault information § Flags f. BG f. BD f. BS f. SD f. GS § Sub-entry mi j = 1 if leakage fault detected Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 28

Example Leakage Fault Table Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 29

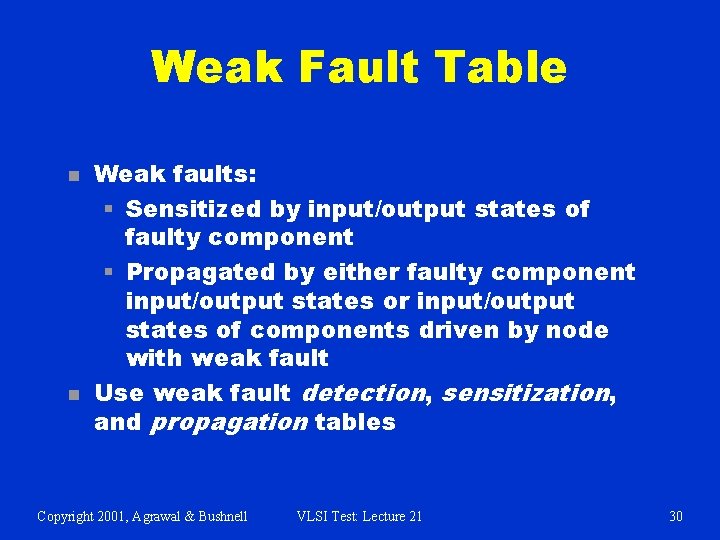

Weak Fault Table n n Weak faults: § Sensitized by input/output states of faulty component § Propagated by either faulty component input/output states or input/output states of components driven by node with weak fault Use weak fault detection, sensitization, and propagation tables Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 30

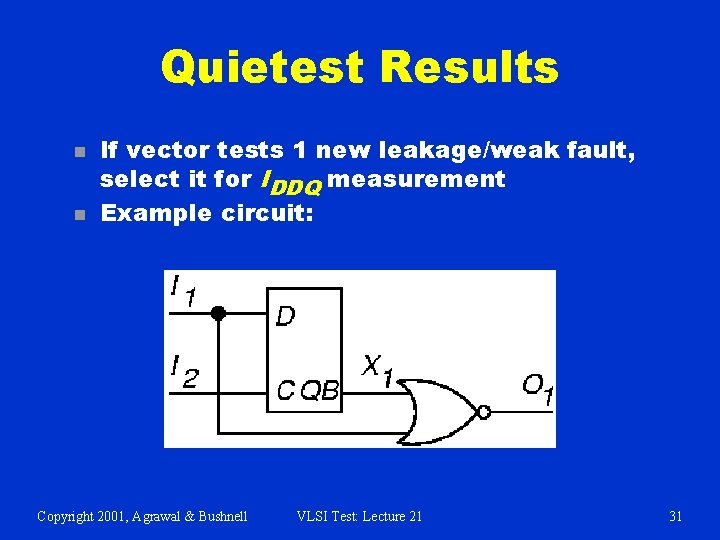

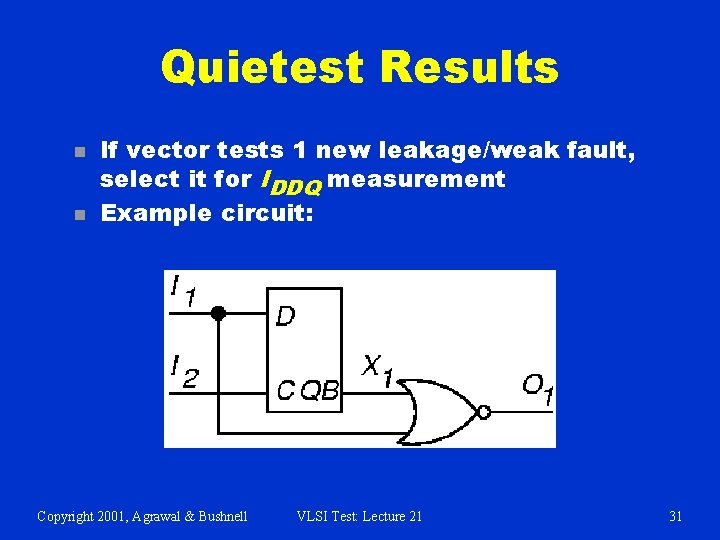

Quietest Results n n If vector tests 1 new leakage/weak fault, select it for IDDQ measurement Example circuit: Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 31

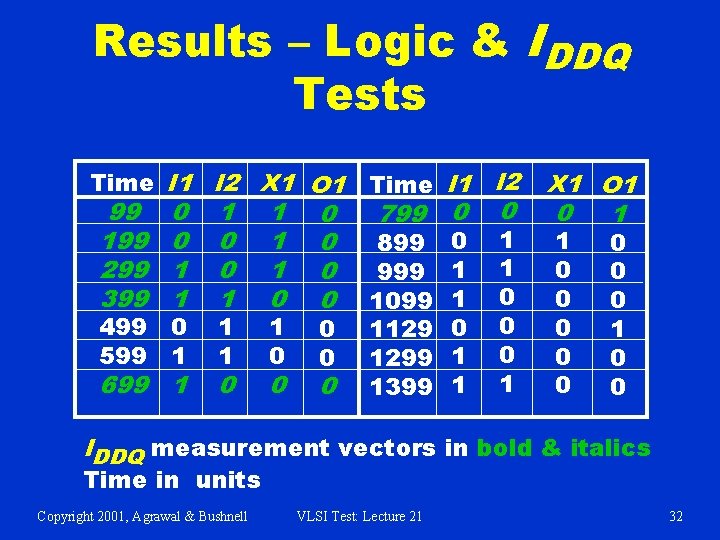

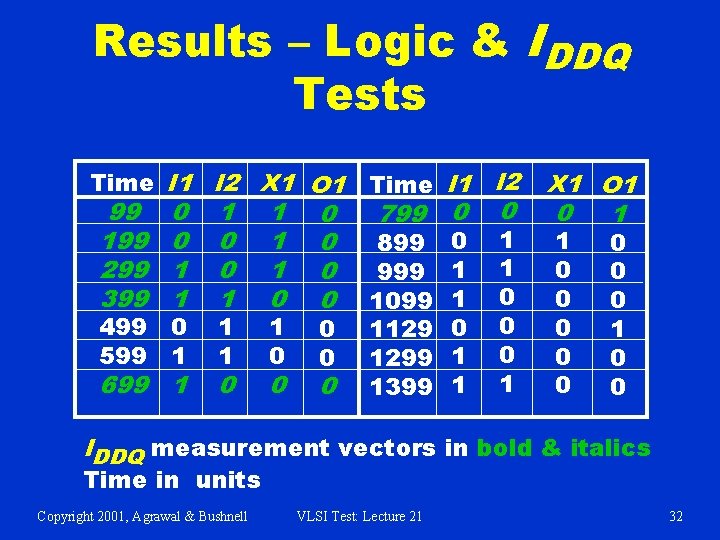

Results – Logic & IDDQ Tests Time I 1 I 2 X 1 O 1 0 0 1 1 1 1 0 0 0 699 1 0 0 0 99 199 299 399 499 599 0 1 1 0 0 0 Time I 1 I 2 799 0 899 999 1099 1129 1299 1399 0 1 1 0 0 0 1 X 1 O 1 0 1 1 0 0 0 0 1 0 0 IDDQ measurement vectors in bold & italics Time in units Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 32

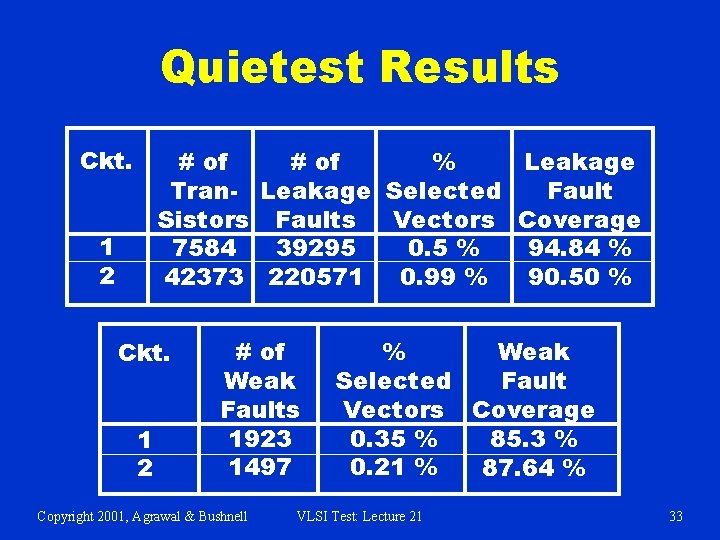

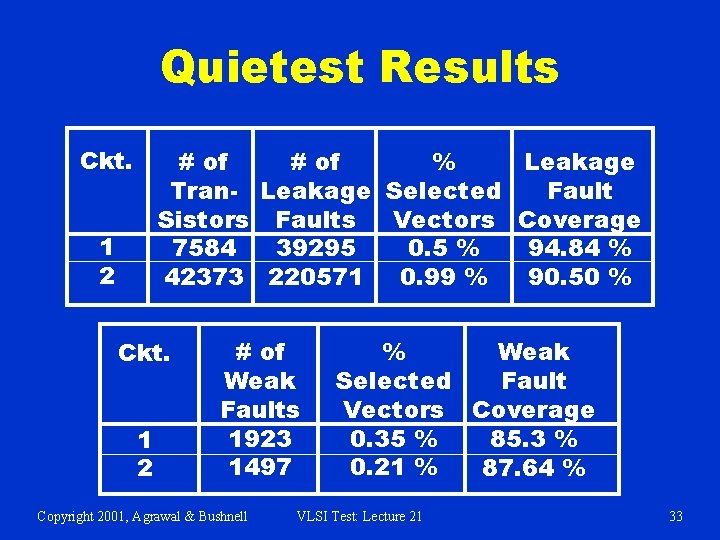

Quietest Results Ckt. # of % Leakage Tran- Leakage Selected Fault Sistors Faults Vectors Coverage 7584 39295 0. 5 % 94. 84 % 42373 220571 0. 99 % 90. 50 % 1 2 Ckt. 1 2 # of Weak Faults 1923 1497 Copyright 2001, Agrawal & Bushnell % Weak Selected Fault Vectors Coverage 0. 35 % 85. 3 % 0. 21 % 87. 64 % VLSI Test: Lecture 21 33

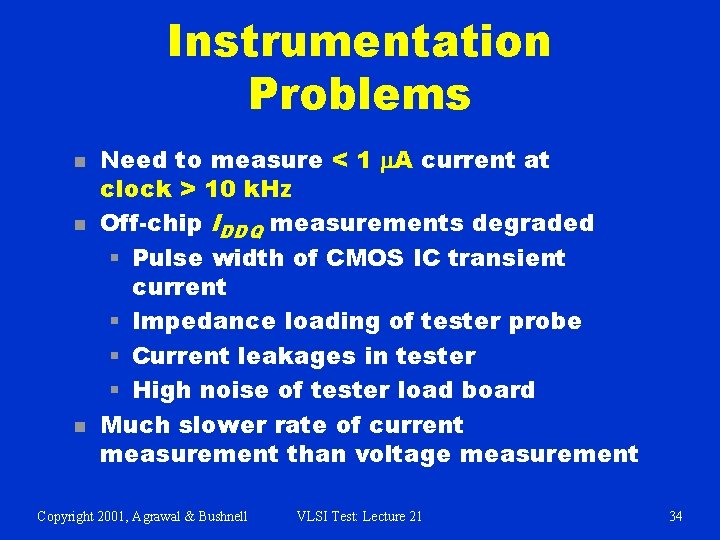

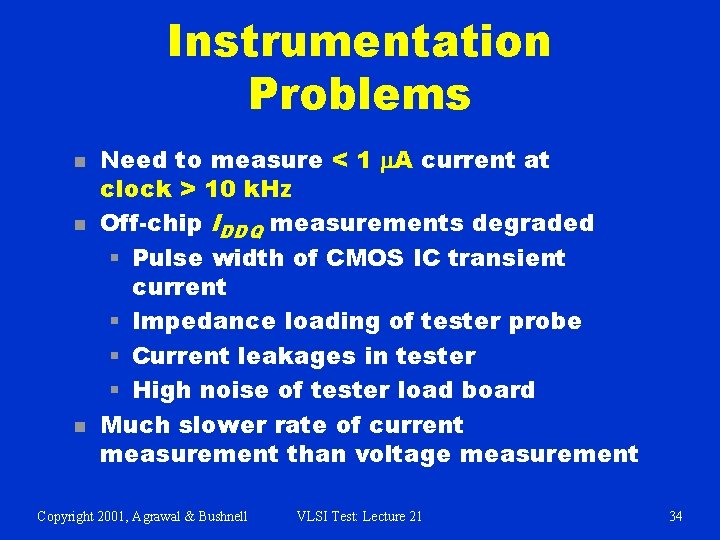

Instrumentation Problems n n n Need to measure < 1 m. A current at clock > 10 k. Hz Off-chip IDDQ measurements degraded § Pulse width of CMOS IC transient current § Impedance loading of tester probe § Current leakages in tester § High noise of tester load board Much slower rate of current measurement than voltage measurement Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 34

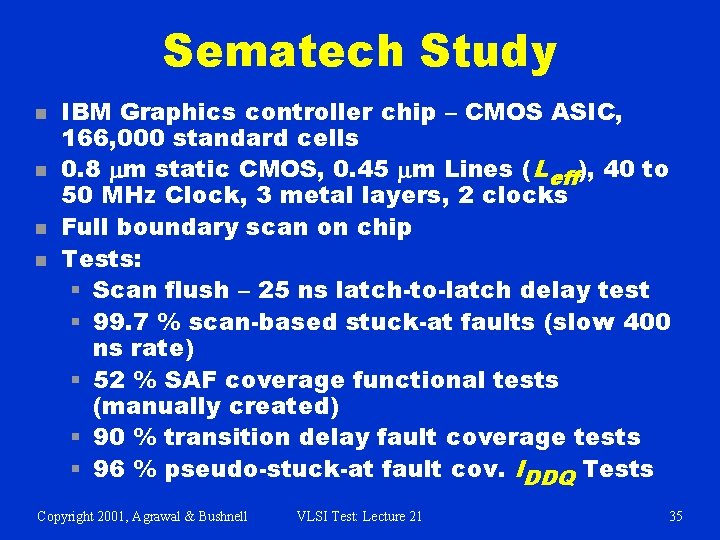

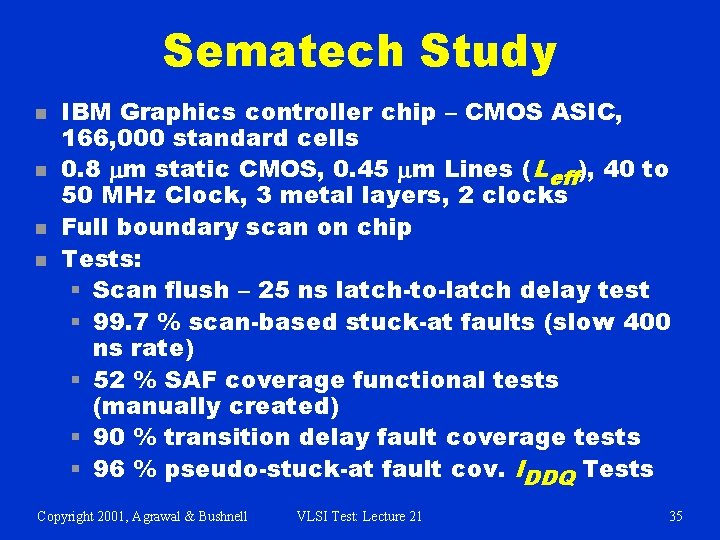

Sematech Study n n IBM Graphics controller chip – CMOS ASIC, 166, 000 standard cells 0. 8 mm static CMOS, 0. 45 mm Lines (Leff), 40 to 50 MHz Clock, 3 metal layers, 2 clocks Full boundary scan on chip Tests: § Scan flush – 25 ns latch-to-latch delay test § 99. 7 % scan-based stuck-at faults (slow 400 ns rate) § 52 % SAF coverage functional tests (manually created) § 90 % transition delay fault coverage tests § 96 % pseudo-stuck-at fault cov. IDDQ Tests Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 35

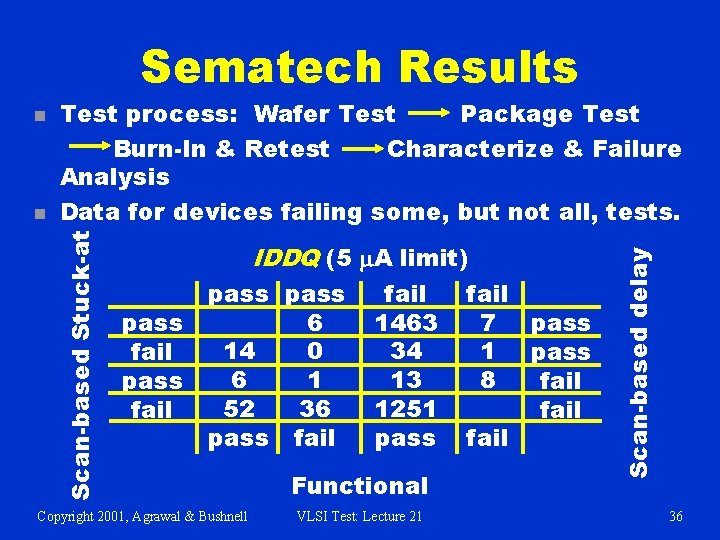

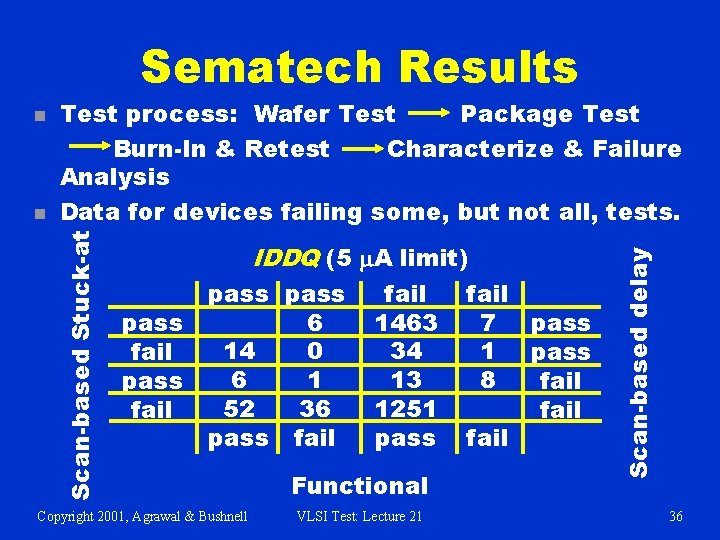

Sematech Results Scan-based Stuck-at n Test process: Wafer Test Package Test Burn-In & Retest Characterize & Failure Analysis Data for devices failing some, but not all, tests. IDDQ (5 m. A limit) pass fail pass 6 14 0 6 1 52 36 pass fail Copyright 2001, Agrawal & Bushnell fail 1463 34 13 1251 pass Functional VLSI Test: Lecture 21 fail 7 pass 1 pass 8 fail Scan-based delay n 36

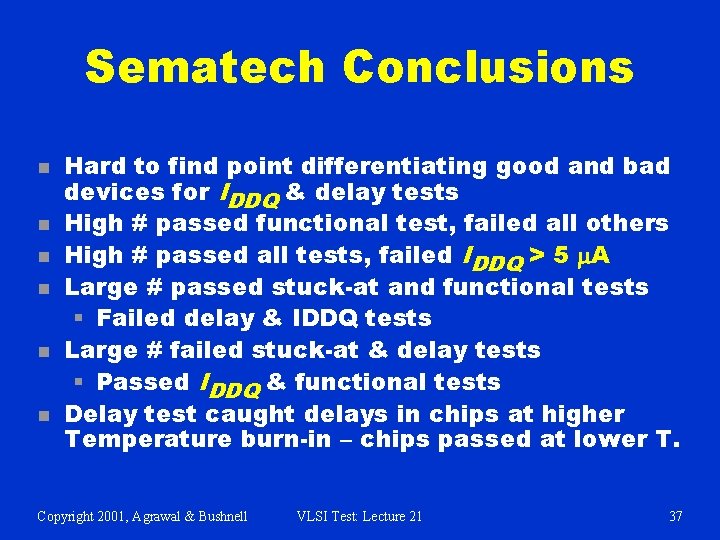

Sematech Conclusions n n n Hard to find point differentiating good and bad devices for IDDQ & delay tests High # passed functional test, failed all others High # passed all tests, failed IDDQ > 5 m. A Large # passed stuck-at and functional tests § Failed delay & IDDQ tests Large # failed stuck-at & delay tests § Passed IDDQ & functional tests Delay test caught delays in chips at higher Temperature burn-in – chips passed at lower T. Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 37

Limitations of IDDQ Testing n n n Sub-micron technologies have increased leakage currents § Transistor sub-threshold conduction § Harder to find IDDQ threshold separating good & bad chips IDDQ tests work: § When average defect-induced current greater than average good IC current § Small variation in IDDQ over test sequence & between chips Now less likely to obtain two conditions Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 38

Summary n n IDDQ tests improve reliability, find defects causing: § Delay, bridging, weak faults § Chips damaged by electro-static discharge No natural breakpoint for current threshold § Get continuous distribution – bimodal would be better Conclusion: now need stuck-fault, IDDQ, and delay fault testing combined Still uncertain whether IDDQ tests will remain useful as chip feature sizes shrink further Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 21 39