Lecture 22 Delta IDDQ Testing and BuiltIn Current

Lecture 22 Delta IDDQ Testing and Built-In Current Testing n n n Current limit setting Testing time issues Delta IDDQ testing (D IDDQ) Built-in current testing sensors Summary Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 1

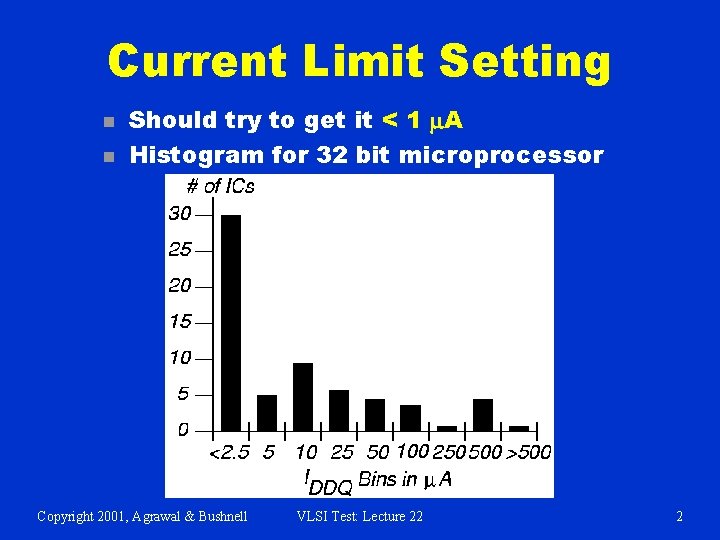

Current Limit Setting n n Should try to get it < 1 m. A Histogram for 32 bit microprocessor Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 2

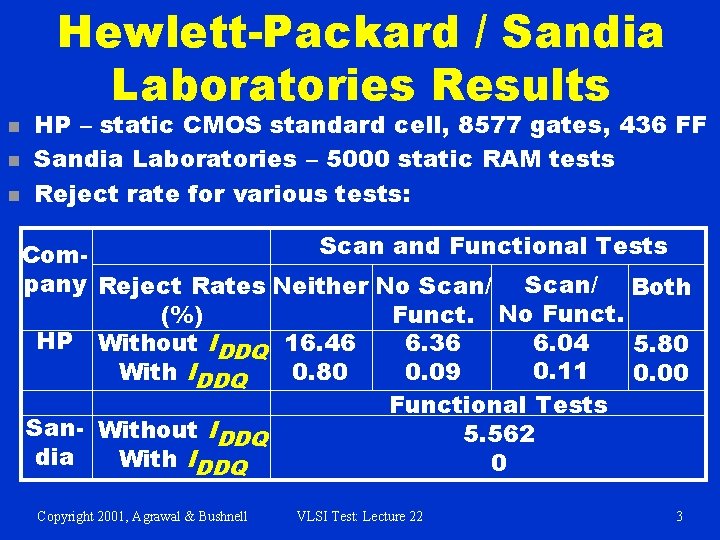

Hewlett-Packard / Sandia Laboratories Results n n n HP – static CMOS standard cell, 8577 gates, 436 FF Sandia Laboratories – 5000 static RAM tests Reject rate for various tests: Scan and Functional Tests Company Reject Rates Neither No Scan/ Both (%) Funct. No Funct. HP Without IDDQ 16. 46 6. 04 6. 36 5. 80 0. 11 With IDDQ 0. 80 0. 09 0. 00 Functional Tests San- Without IDDQ 5. 562 dia With IDDQ 0 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 3

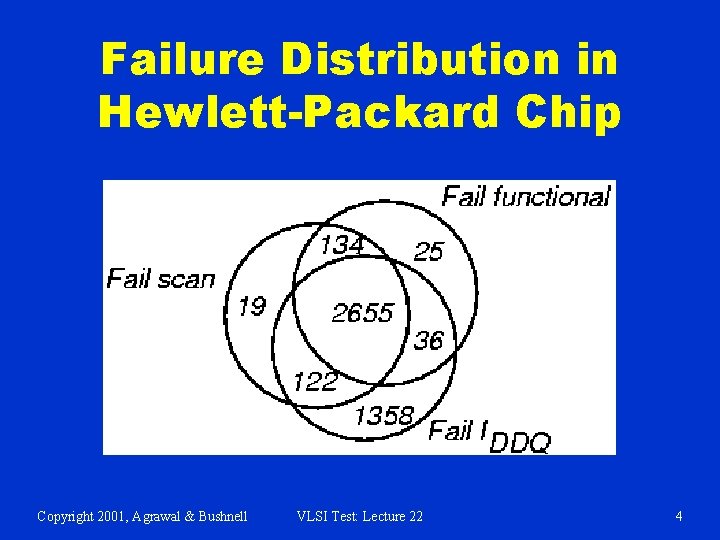

Failure Distribution in Hewlett-Packard Chip Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 4

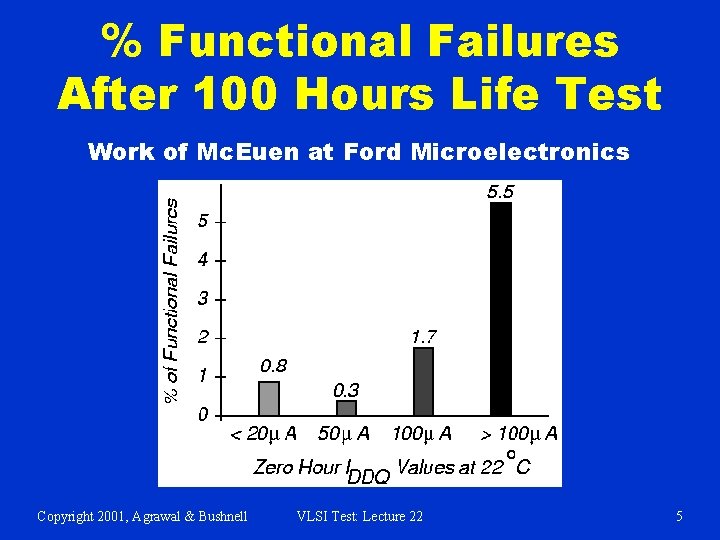

% Functional Failures After 100 Hours Life Test Work of Mc. Euen at Ford Microelectronics Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 5

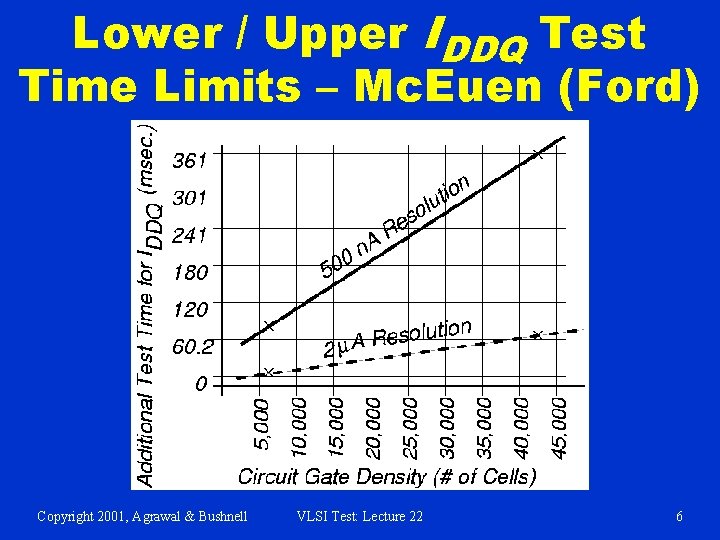

Lower / Upper IDDQ Test Time Limits – Mc. Euen (Ford) Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 6

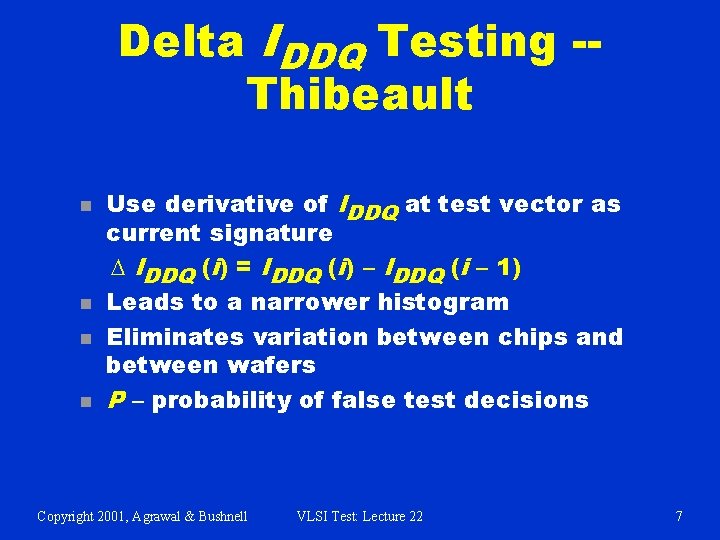

Delta IDDQ Testing -Thibeault n n Use derivative of IDDQ at test vector as current signature D IDDQ (i) = IDDQ (i) – IDDQ (i – 1) Leads to a narrower histogram Eliminates variation between chips and between wafers P – probability of false test decisions Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 7

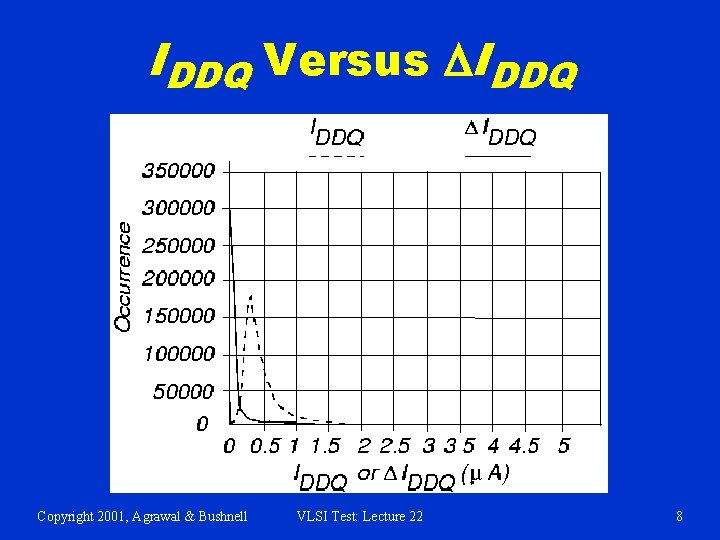

IDDQ Versus DIDDQ Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 8

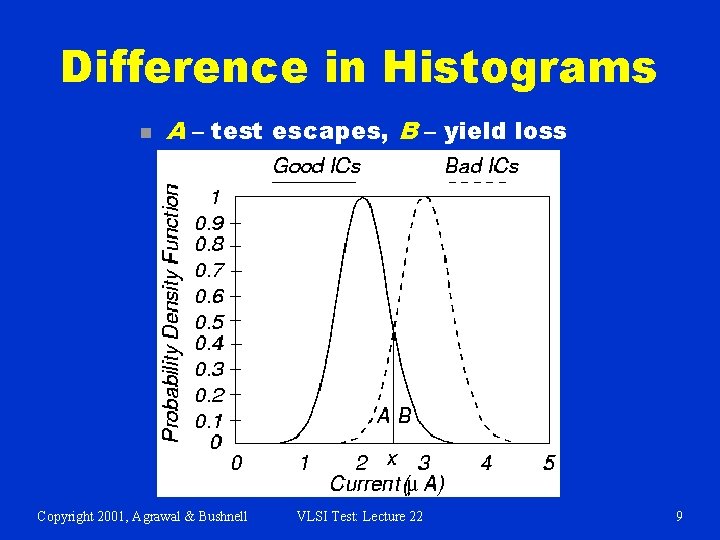

Difference in Histograms n A – test escapes, B – yield loss Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 9

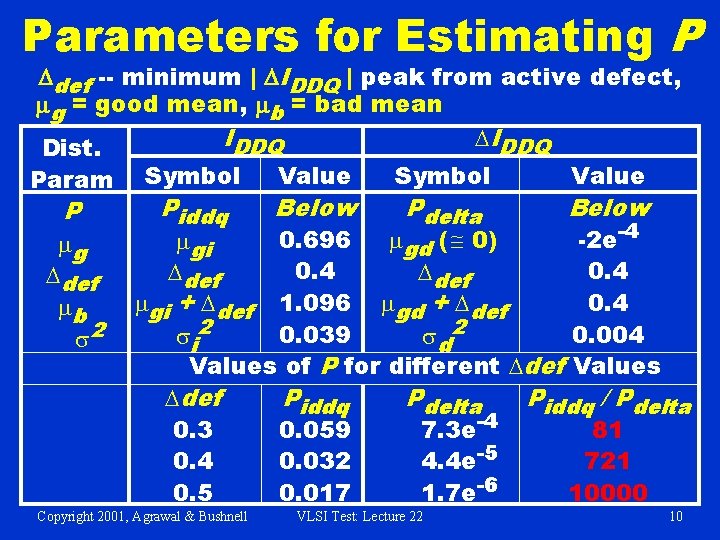

Parameters for Estimating P Ddef -- minimum | DIDDQ | peak from active defect, mg = good mean, mb = bad mean IDDQ Dist. Param P mg Ddef mb s 2 Symbol Piddq Value Below Symbol Pdelta mgd ( @ 0) Value Below 0. 696 -2 e-4 mgi 0. 4 Ddef mgi + Ddef 1. 096 mgd + Ddef 0. 4 0. 039 0. 004 s i 2 sd 2 Values of P for different Ddef Values Ddef Pdelta Piddq / Pdelta 0. 3 0. 059 7. 3 e-4 81 0. 4 0. 032 4. 4 e-5 721 0. 5 0. 017 1. 7 e-6 10000 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 10

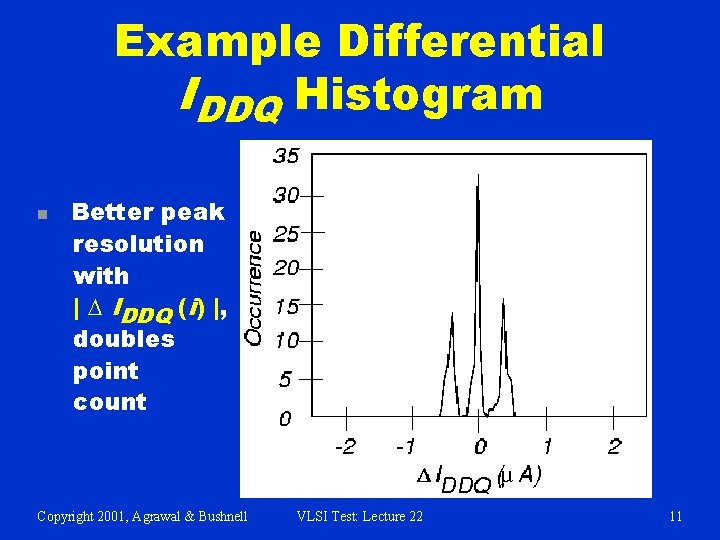

Example Differential IDDQ Histogram n Better peak resolution with | D IDDQ (i) |, doubles point count Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 11

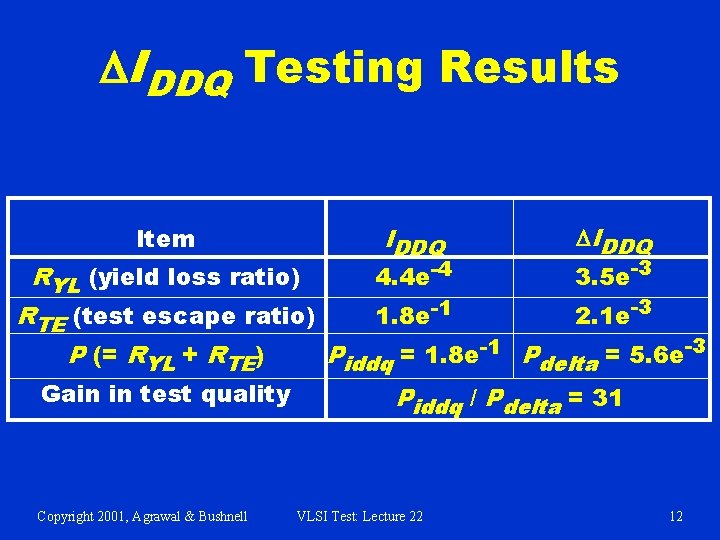

DIDDQ Testing Results Item RYL (yield loss ratio) RTE (test escape ratio) P (= RYL + RTE) Gain in test quality Copyright 2001, Agrawal & Bushnell IDDQ 4. 4 e-4 1. 8 e-1 DIDDQ 3. 5 e-3 2. 1 e-3 Piddq = 1. 8 e-1 Pdelta = 5. 6 e-3 Piddq / Pdelta = 31 VLSI Test: Lecture 22 12

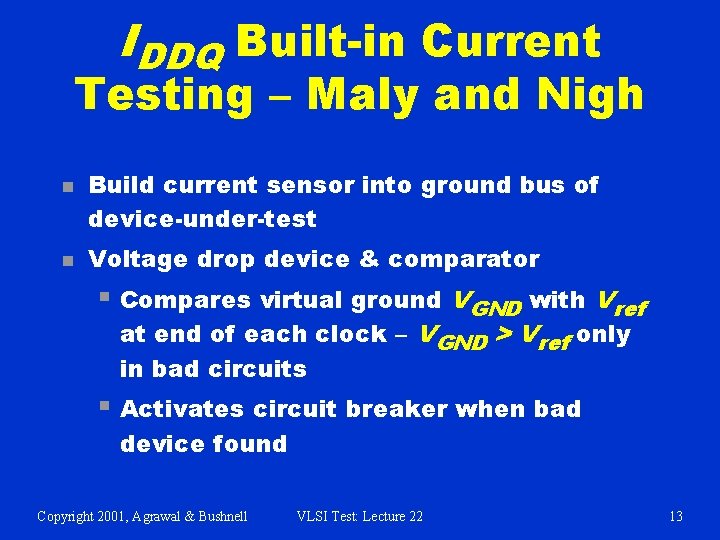

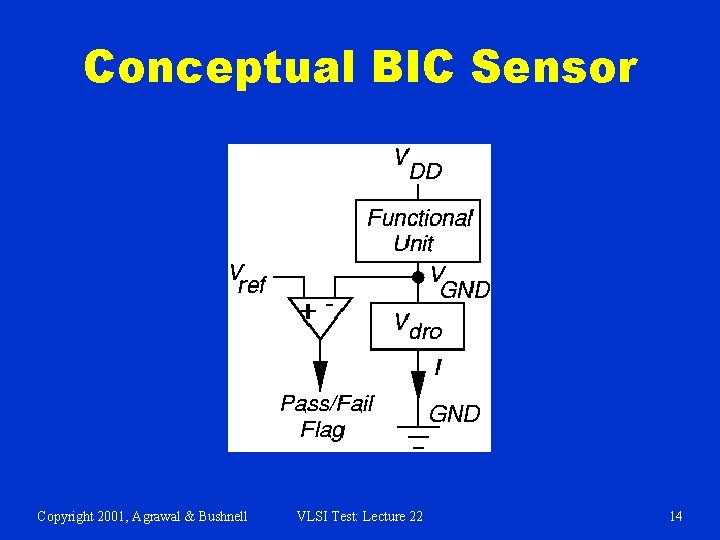

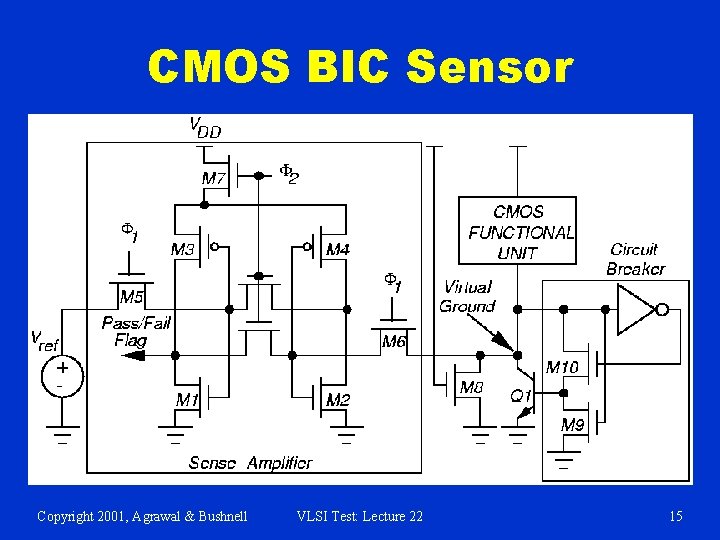

IDDQ Built-in Current Testing – Maly and Nigh n n Build current sensor into ground bus of device-under-test Voltage drop device & comparator § Compares virtual ground VGND with Vref at end of each clock – VGND > Vref only in bad circuits § Activates circuit breaker when bad device found Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 13

Conceptual BIC Sensor Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 14

CMOS BIC Sensor Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 15

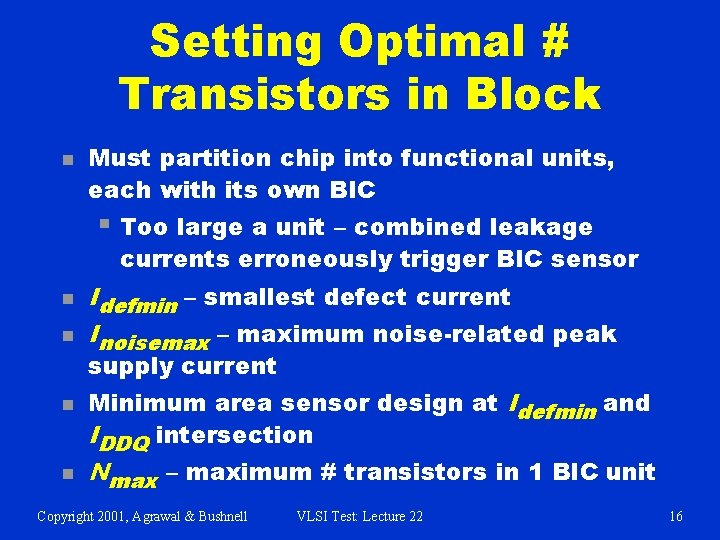

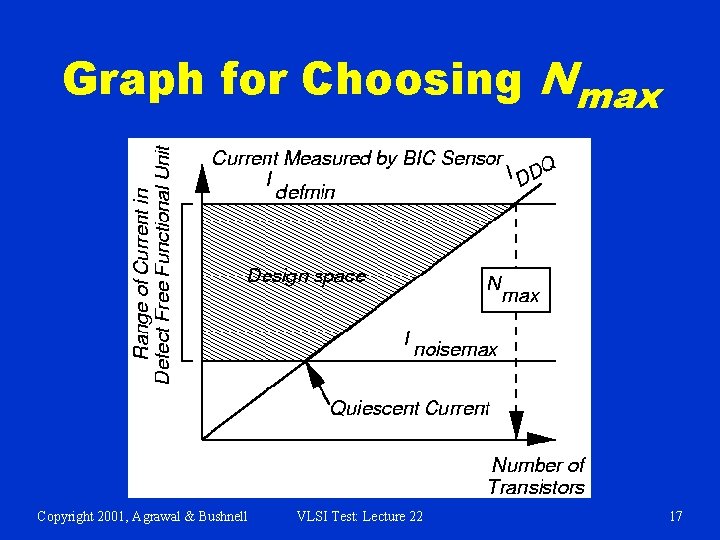

Setting Optimal # Transistors in Block n Must partition chip into functional units, each with its own BIC § Too large a unit – combined leakage currents erroneously trigger BIC sensor n n Idefmin – smallest defect current Inoisemax – maximum noise-related peak supply current n n Minimum area sensor design at Idefmin and IDDQ intersection Nmax – maximum # transistors in 1 BIC unit Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 16

Graph for Choosing Nmax Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 17

Summary n IDDQ current limit setting to differentiate between good and bad circuits is difficult n IDDQ testing is becoming more problematic § Greater leakage currents in MOSFETs in deep sub-micron technologies § Harder to discriminate elevated IDDQ from 100, 000 transistor leakage currents n n DIDDQ holds promise to alleviate problems Built-in current testing holds promise Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 22 18

- Slides: 18