Introduction to VLSI Programming High Performance DLX course

- Slides: 23

Introduction to VLSI Programming High Performance DLX (course 2 IN 30) Prof. dr. ir. Kees van Berkel

Demonstrator ICs 9/16/2020 Kees van Berkel 2

Added value • 1985: modularity, ease of design (no value added to product!) • 1990: low power (ESPRIT project ) • 1992: low noise, low EME (Electro-Magnetic Emission) • 2000: . . . 9/16/2020 Kees van Berkel 3

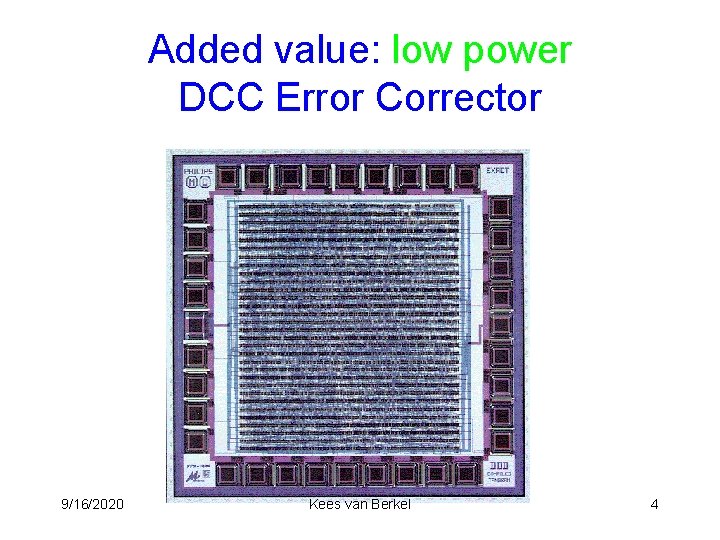

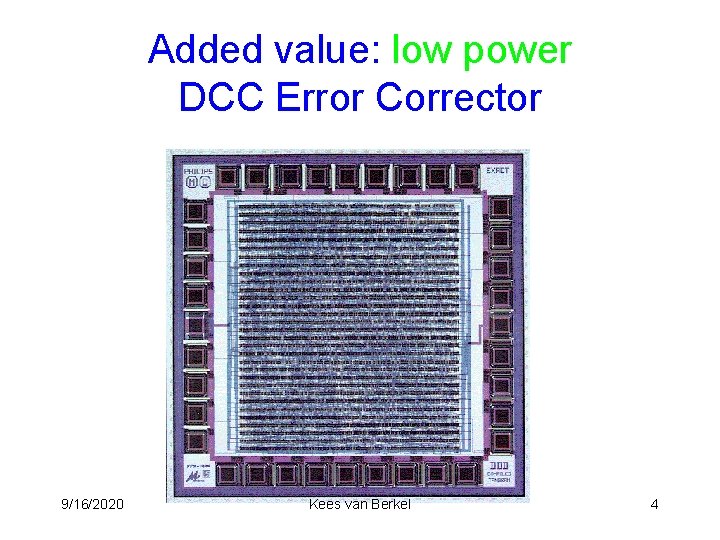

Added value: low power DCC Error Corrector 9/16/2020 Kees van Berkel 4

A sync-async “arms race” 9/16/2020 Kees van Berkel 5

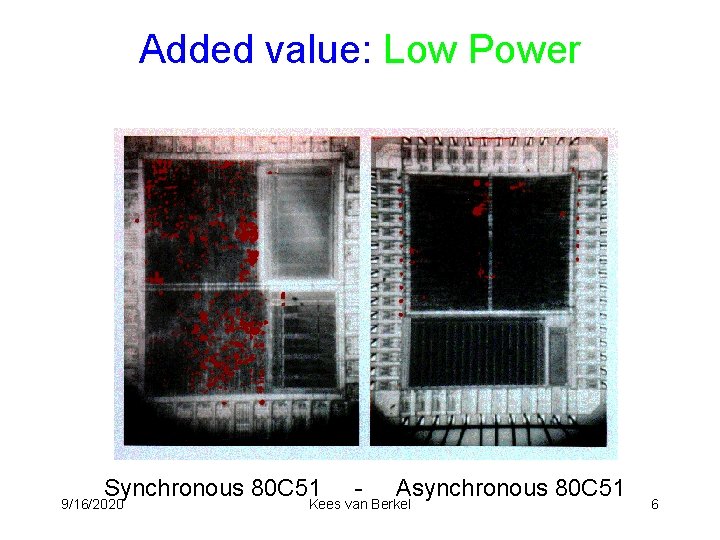

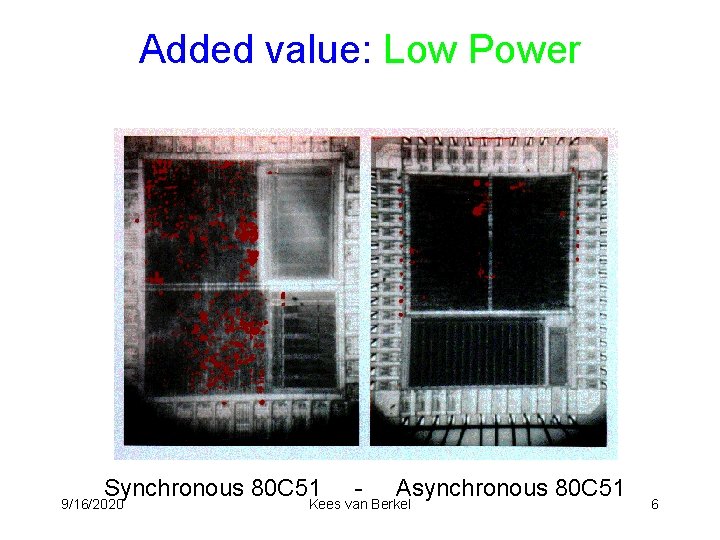

Added value: Low Power Synchronous 80 C 51 9/16/2020 - Asynchronous 80 C 51 Kees van Berkel 6

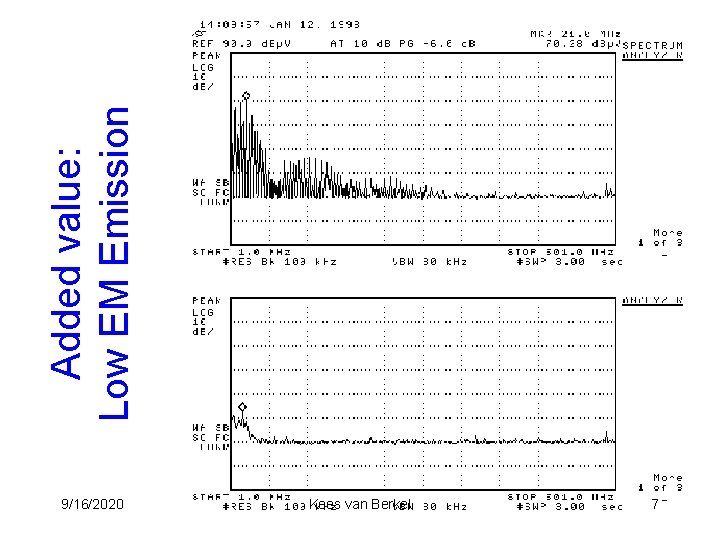

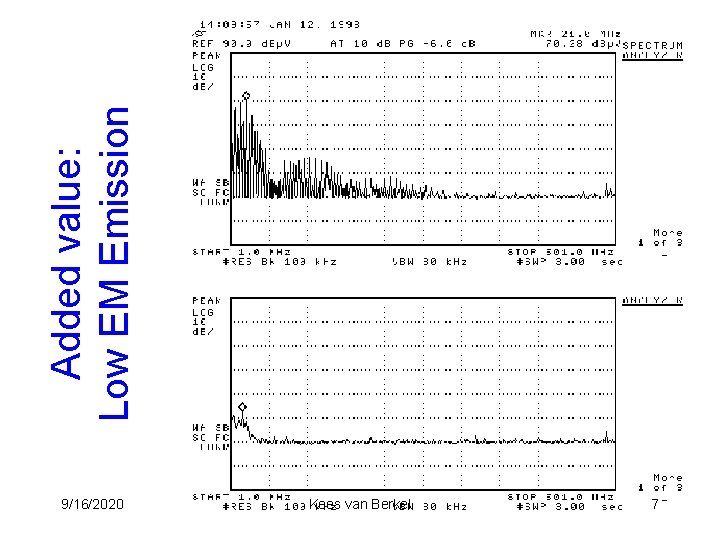

9/16/2020 Kees van Berkel 7 Added value: Low EM Emission

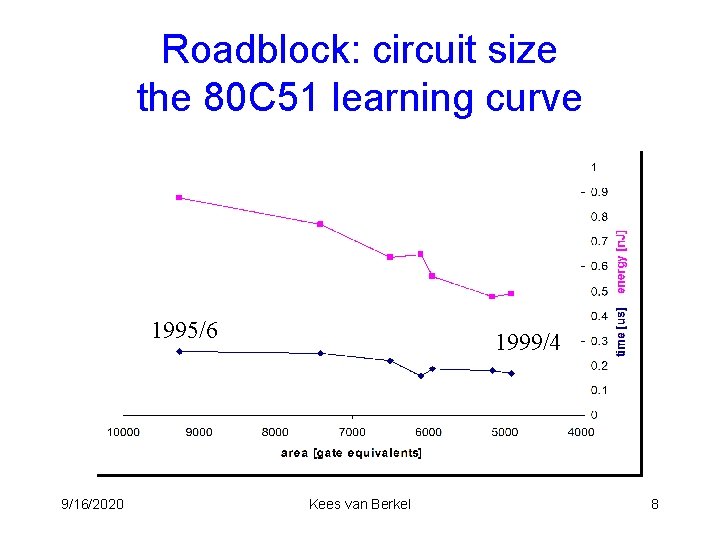

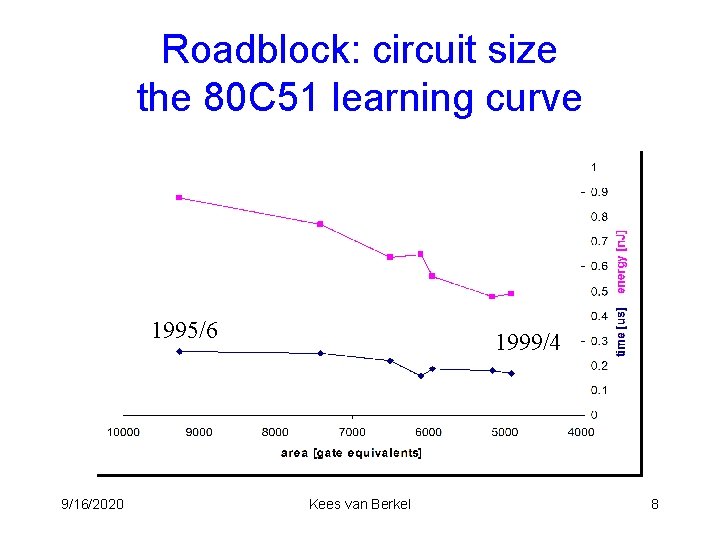

Roadblock: circuit size the 80 C 51 learning curve 1995/6 9/16/2020 1999/4 Kees van Berkel 8

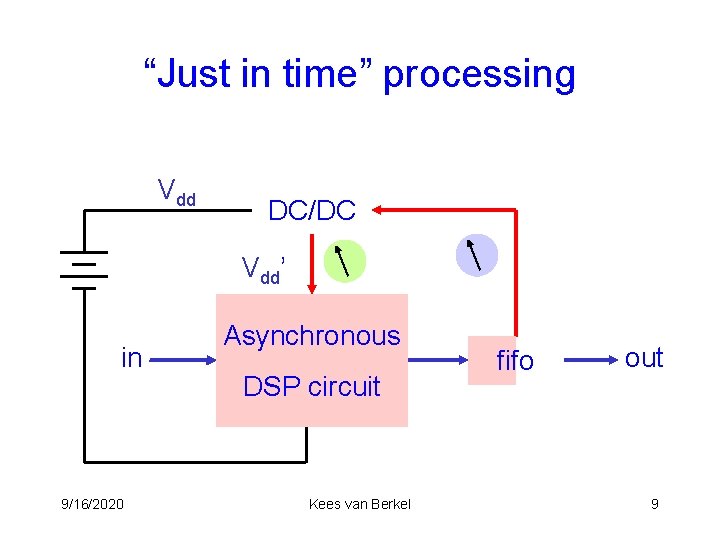

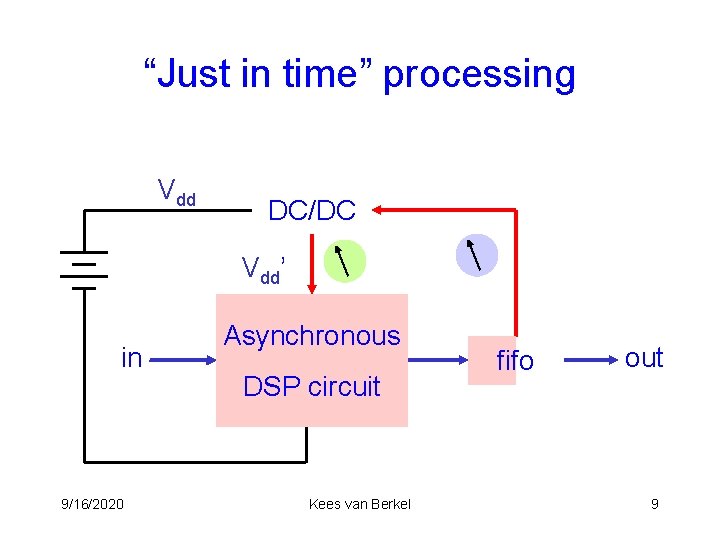

“Just in time” processing Vdd DC/DC Vdd’ in 9/16/2020 Asynchronous DSP circuit. Kees van Berkel fifo out 9

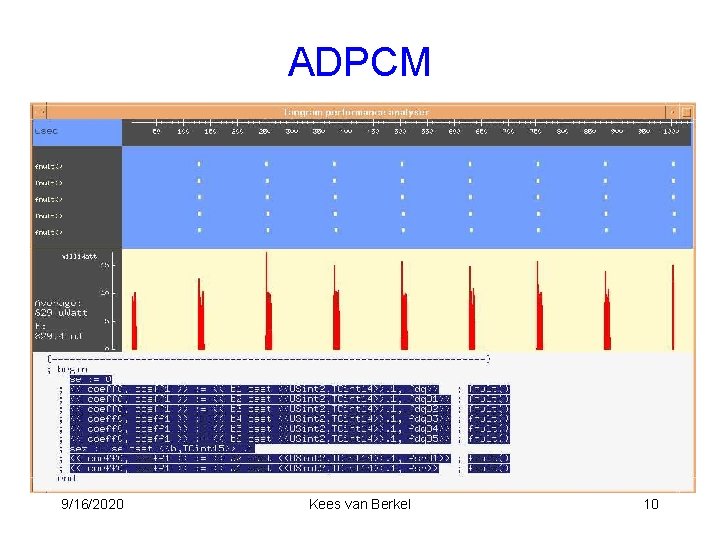

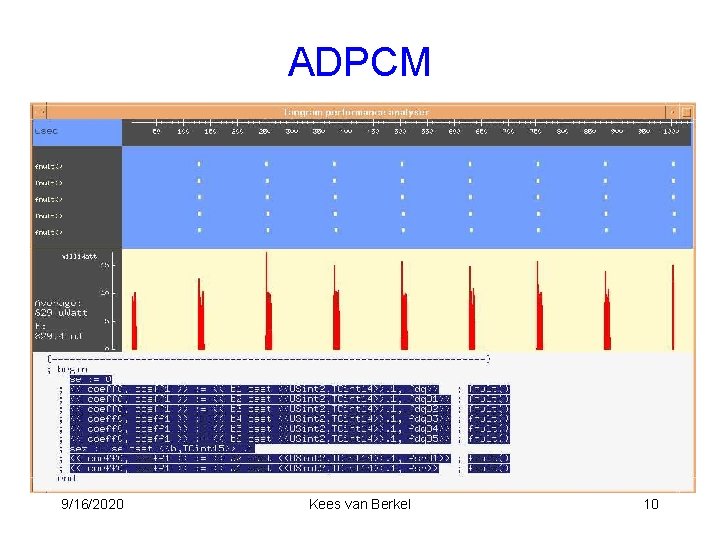

ADPCM 9/16/2020 Kees van Berkel 10

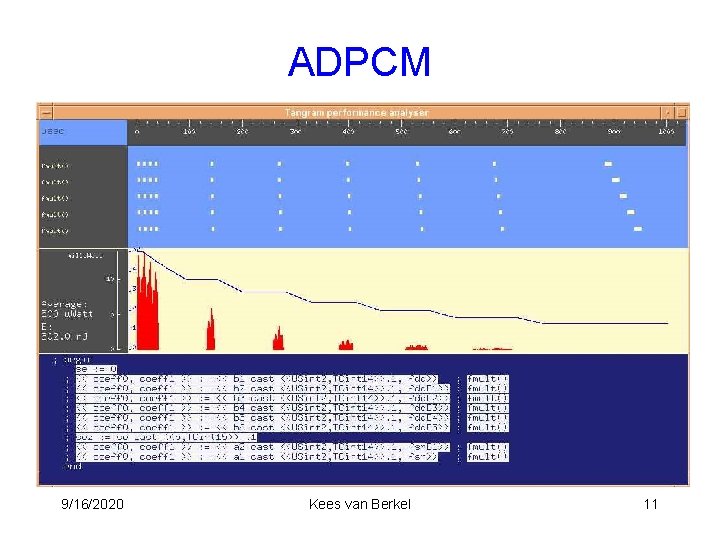

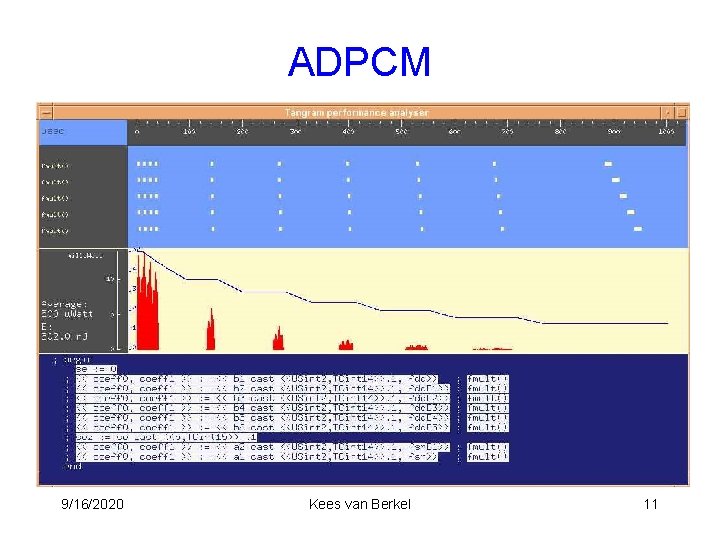

ADPCM 9/16/2020 Kees van Berkel 11

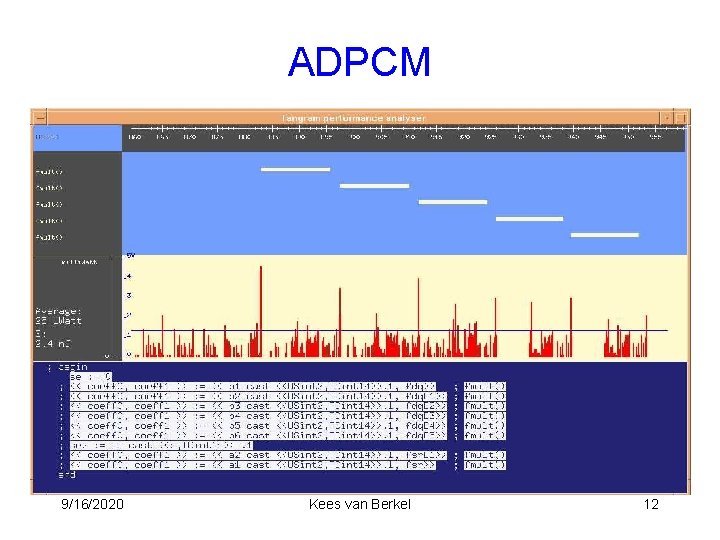

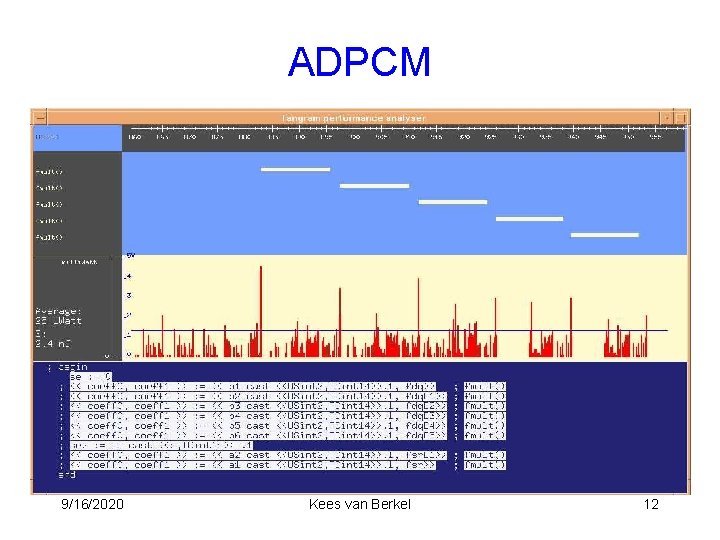

ADPCM 9/16/2020 Kees van Berkel 12

Industrialization of the Technology • Philips Semiconductors Zürich (1994 Dec): “We want to set a world record in low power, . . by using asynchronous technology. ” • Their choice for a vehicle: the 80 C 51 micro-controller (used in many consumer products). • Result: 4× less power, minimal EME. • Follow-up: pager baseband ICs, … In parallel: transfer and upgrade of tools + design flow 9/16/2020 Kees van Berkel 13

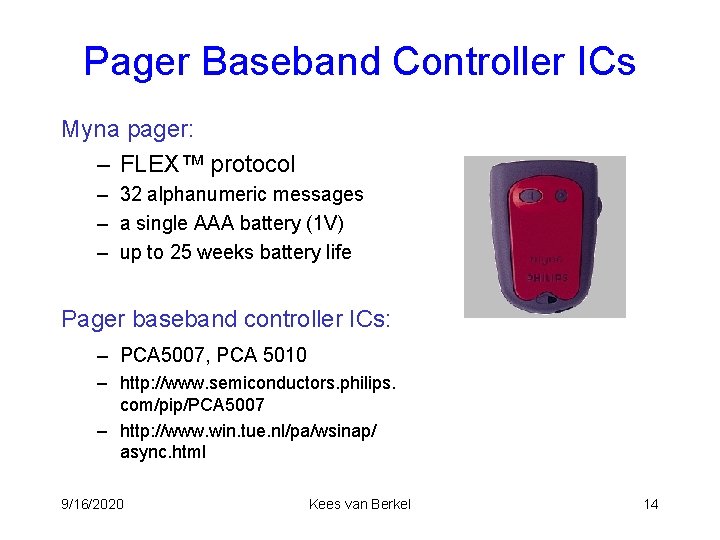

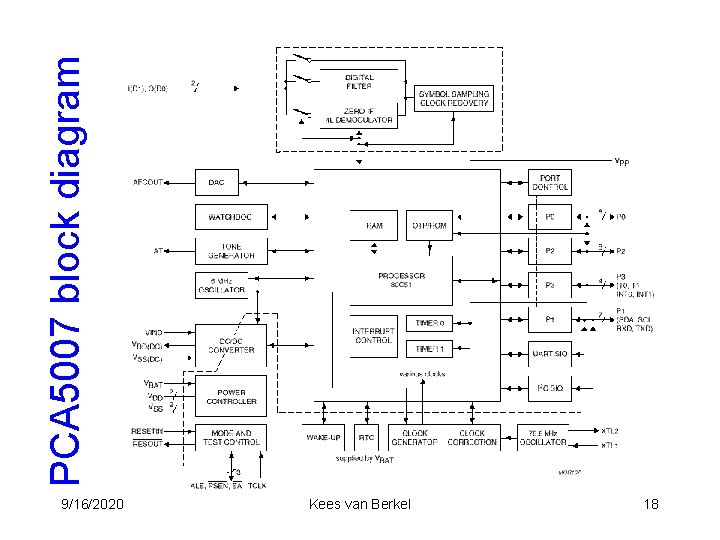

Pager Baseband Controller ICs Myna pager: – FLEX™ protocol – 32 alphanumeric messages – a single AAA battery (1 V) – up to 25 weeks battery life Pager baseband controller ICs: – PCA 5007, PCA 5010 – http: //www. semiconductors. philips. com/pip/PCA 5007 – http: //www. win. tue. nl/pa/wsinap/ async. html 9/16/2020 Kees van Berkel 14

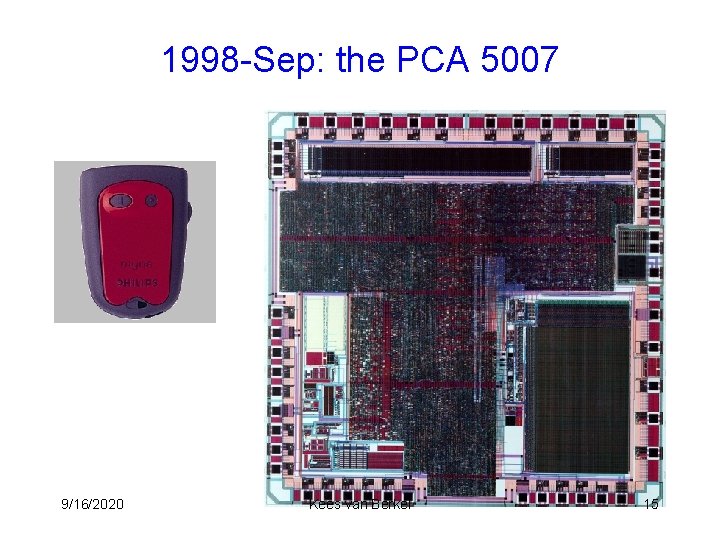

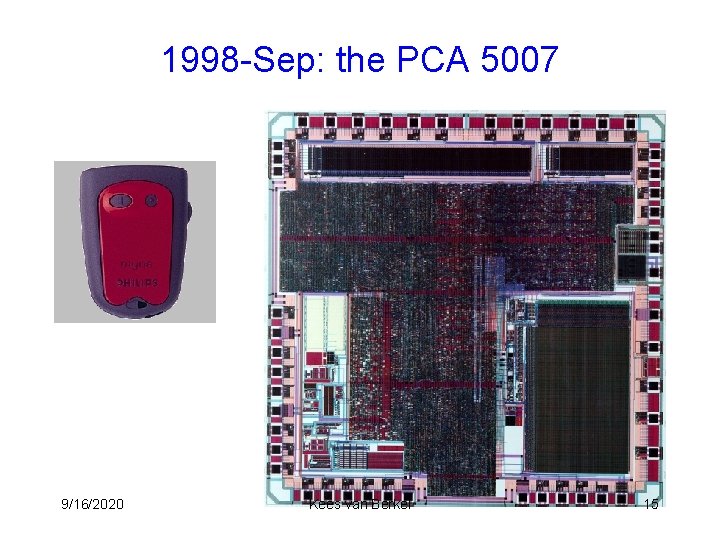

1998 -Sep: the PCA 5007 9/16/2020 Kees van Berkel 15

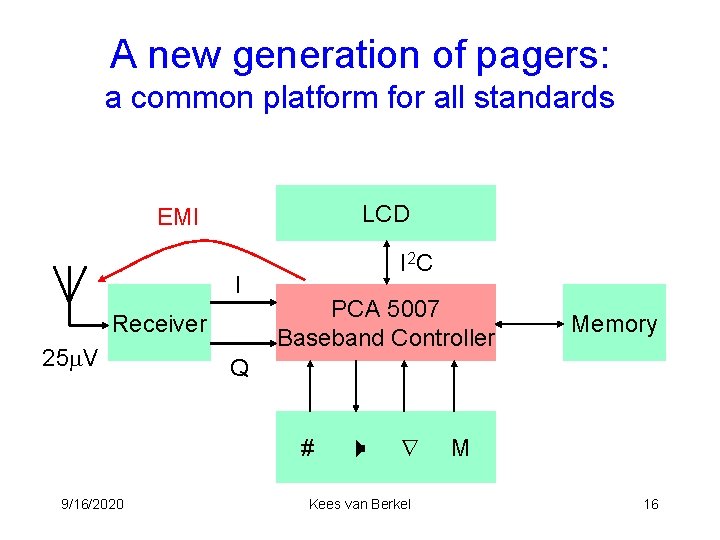

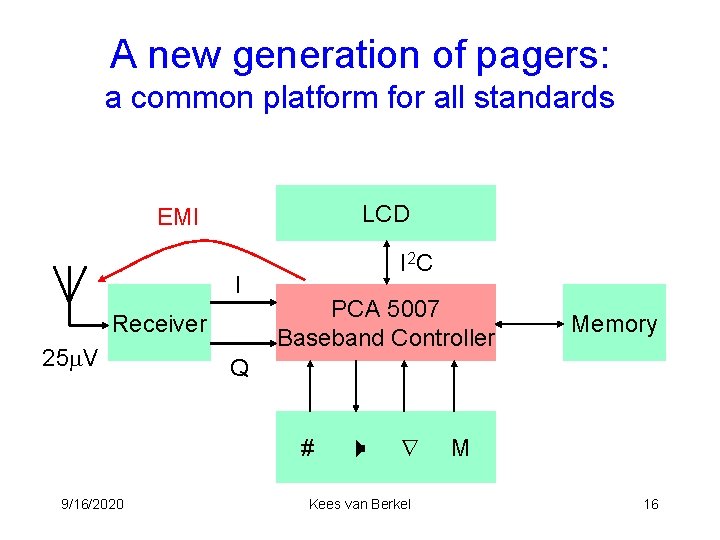

A new generation of pagers: a common platform for all standards LCD EMI I Receiver 25 V I 2 C PCA 5007 Baseband Controller Q # 9/16/2020 Memory Kees van Berkel M 16

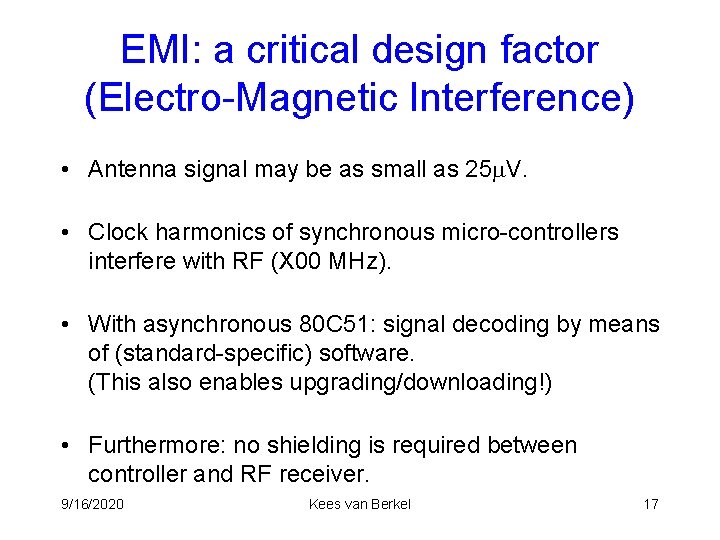

EMI: a critical design factor (Electro-Magnetic Interference) • Antenna signal may be as small as 25 V. • Clock harmonics of synchronous micro-controllers interfere with RF (X 00 MHz). • With asynchronous 80 C 51: signal decoding by means of (standard-specific) software. (This also enables upgrading/downloading!) • Furthermore: no shielding is required between controller and RF receiver. 9/16/2020 Kees van Berkel 17

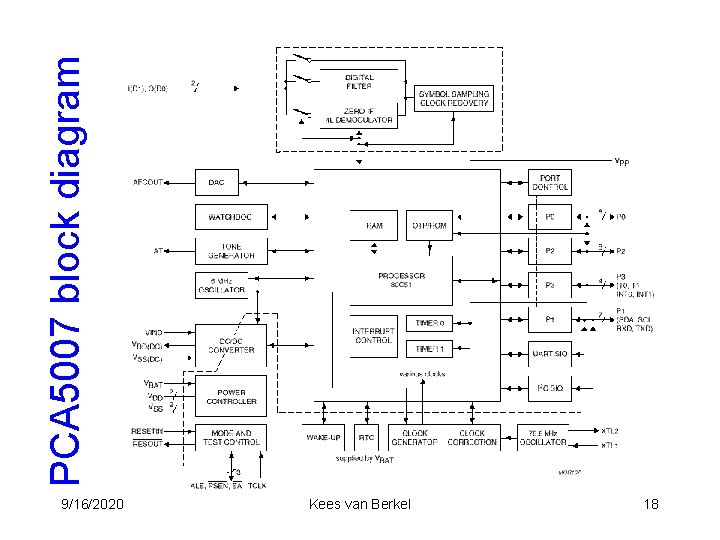

PCA 5007 block diagram 9/16/2020 Kees van Berkel 18

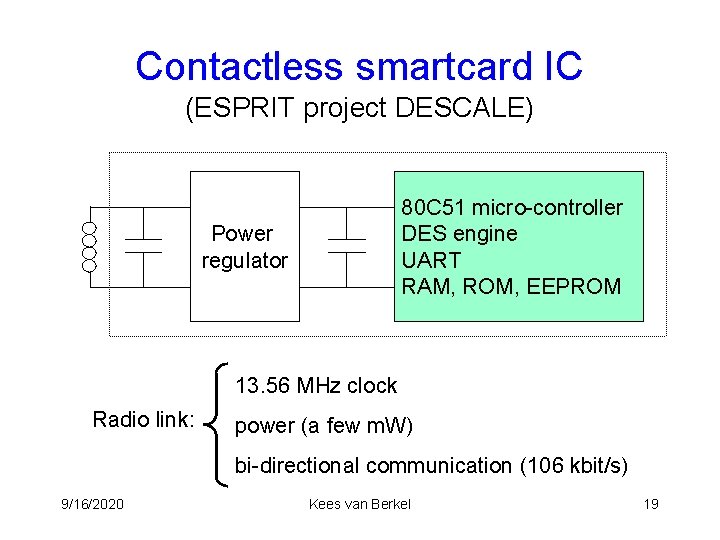

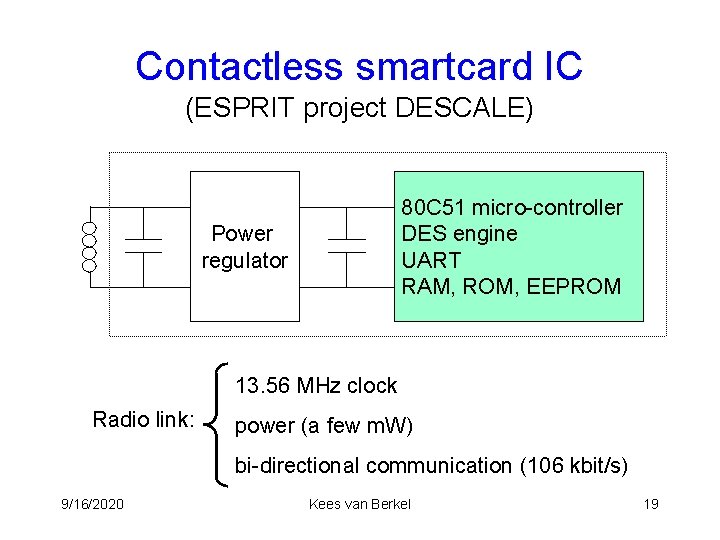

Contactless smartcard IC (ESPRIT project DESCALE) 80 C 51 micro-controller DES engine UART RAM, ROM, EEPROM Power regulator 13. 56 MHz clock Radio link: power (a few m. W) bi-directional communication (106 kbit/s) 9/16/2020 Kees van Berkel 19

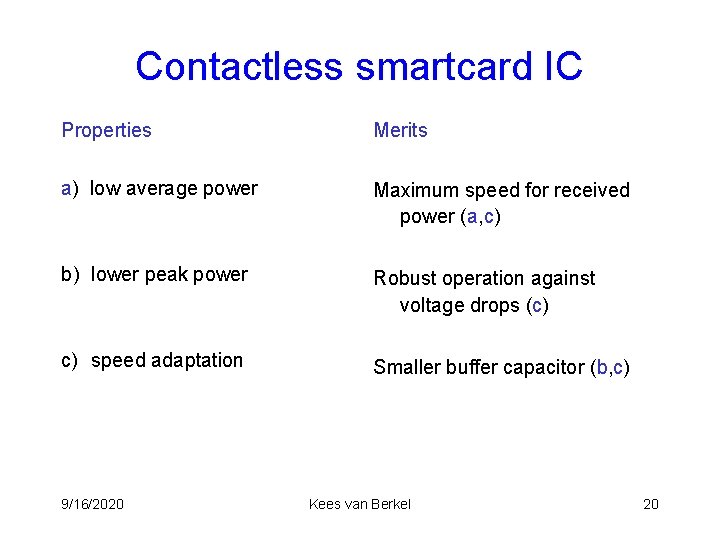

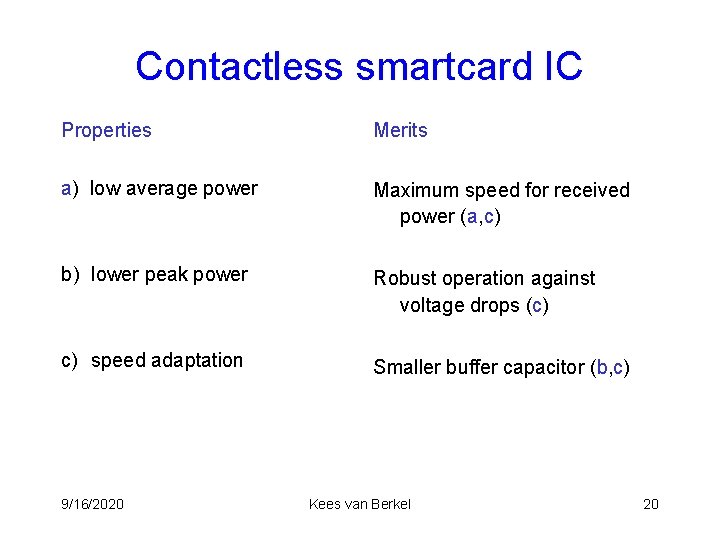

Contactless smartcard IC Properties Merits a) low average power Maximum speed for received power (a, c) b) lower peak power Robust operation against voltage drops (c) c) speed adaptation Smaller buffer capacitor (b, c) 9/16/2020 Kees van Berkel 20

Conclusion • First asynchronous VLSI circuits on the market (high volume sales). • Prospects for more async products look good. • Added value: low power, EME performance. • Added costs: test, IC area, being different. • Asynchronous VLSI technology: – there is room for it in market niches, – … but it may contribute to main-stream VLSI. 9/16/2020 Kees van Berkel 21

Bibliography • Computer Architecture; a Quantitative Approach (3 rd Ed. ); John L Hennessy & David A Patterson; Morgan Kaufmann Publishers Inc, 1996. • ARM System Architecture; Steve Furber; Addison Wesley, 1996. • DSP Processor Fundamentals, Architectures and Features; Phil Lapsey et al (Berkeley Design Technology Inc. ), IEEE, 1996. • www. handshakesolutions. com • www. arm. com/news/6936. html • www. research. philips. com/ newscenter/archive/2004/handshake. html 9/16/2020 Kees van Berkel 22

Lab-work and report You are allowed to team up with a colleague (Not mandatory. ) Report: more than listing of functional Tangram programs: • analyze the specifications and requirements; • present design options, alternatives, trade-offs; • motivate your design choices; • explain functional correctness of your Tangram programs; • analyze & explain {area, time, energy} of your programs. 9/16/2020 Kees van Berkel 23