Quad Core Team DLX ISA n n David

- Slides: 22

Quad. Core Team – DLX ISA n n David Bild Greg Bok Jake Czyz Brandon Keao

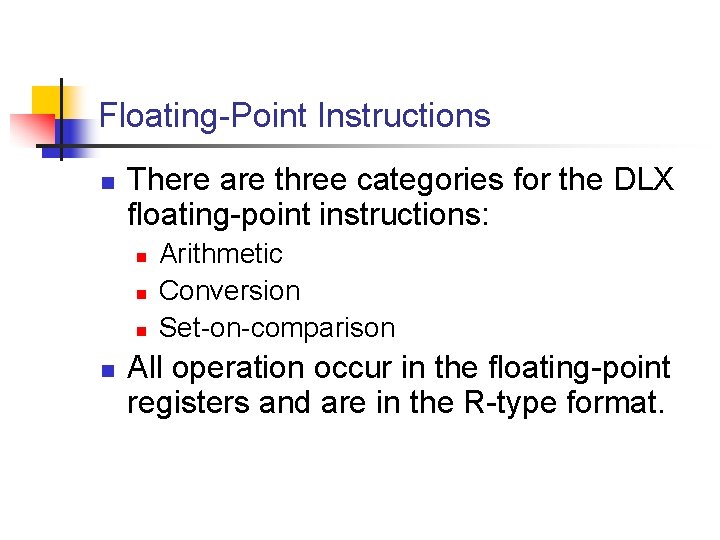

Floating-Point Instructions n There are three categories for the DLX floating-point instructions: n n Arithmetic Conversion Set-on-comparison All operation occur in the floating-point registers and are in the R-type format.

DLX ISA Floating-Point Instructions: Arithmetic Brandon Keao

Floating-Point Instructions: Arithmetic n n n These intructions preform arithmetic operations on two floating-point registers Always R-format There are 2 categories of floating-point arithmetic instructions: n n Single-precision Double-precision

Floating-Point Instructions: Arithmetic n n SP operations interpret the values in the two registers as SP FP values The result is rounded to a SP value and stored in a FP register n n ADDF- Adds two SP values SUBF - Subtracts two SP values MULTF - Multiplies two SP values DIVF - Divides two SP values

Floating-Point Instructions: Arithmetic n n DP operations interpret the values of two even/odd pairs of FP registers as DP FP values. The result if rounded to a DP value and stored in an even/odd pair of FP registers. n ADDD - Adds two DP values n SUBD - Subtracts two DP values n MULTD - Multiplies two DP values n DIVD - Divides two DP values

DLX ISA Floating-Point Instructions: Conversion And Special Instructions Greg Bok

Floating-Point Instructions: Conversion n n Sometimes need to convert between precisions or integer/floating-point The DLX ISA includes 6 such instructions R-format Double-precision FP register operands must be even-numbered FP registers 32 -bit integers used

Floating-Point Instructions: Conversion 1. 2. 3. 4. 5. 6. CVT 2 DF: double-precision to single-precision CVTD 2 I: double-precision to integer CVTF 2 D: single-precision to double-precision CVTF 2 I: single-precision to integer CVTI 2 D: integer to double-precision CVTI 2 F: integer to single-precision

Special Instructions: TRAP n n n J-type, unconditional branch 26 -bit name field zero-extended to 32 bits to obtain target address Moves PC + 8 to IAR (interrupt address register)

Special Instructions: RFE n n Return From Exception J-type, unconditional Returns to code that was executing before TRAP instruction Moves value in IAR register to PC

Special Instructions: NOP n n n R-type Performs no operation -- hardware state is unaffected Typically used to fill branch delay slots when no useful instruction will work

DLX ISA Floating-Point Instructions: Set-on-Comparison David Bild

Floating-Point Instructions: Set. On-Comparison n Compares two floating point numbers (SP or DP) Sets FPSR (Floating Point Status Register) to ‘ 1’ if comparison is true, ‘ 0’ if false 6 comparisons are provided: <, >, =. <=, >=, ~=

DLX ISA Load & Store Instructions Jake Czyz

Load and Store Instructions n n For loading/storing data from/to memory Handle data of size: n n Byte Halfword Word Double (for floating point only)

Load and Store Instructions n n Byte and Halfword instructions always load/store the least significant byte or halfword, respectively. Loads and Stores may be done with any of the general purpose registers, except that loading R 0 has no effect (it always stores the value 0 x 0000).

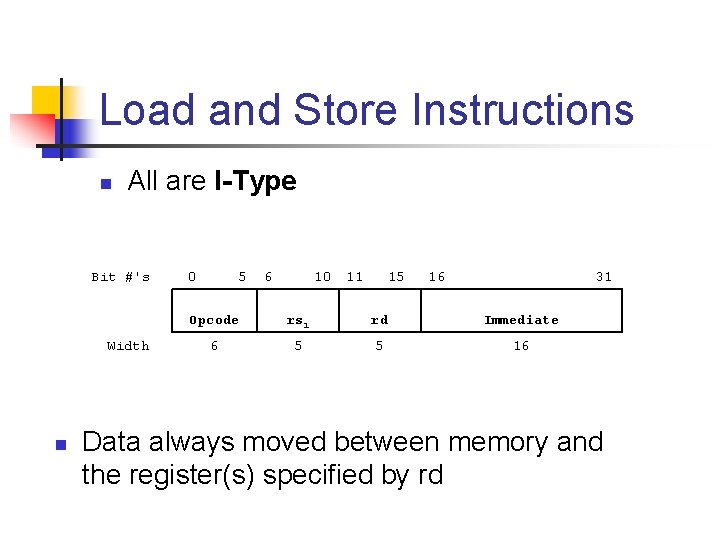

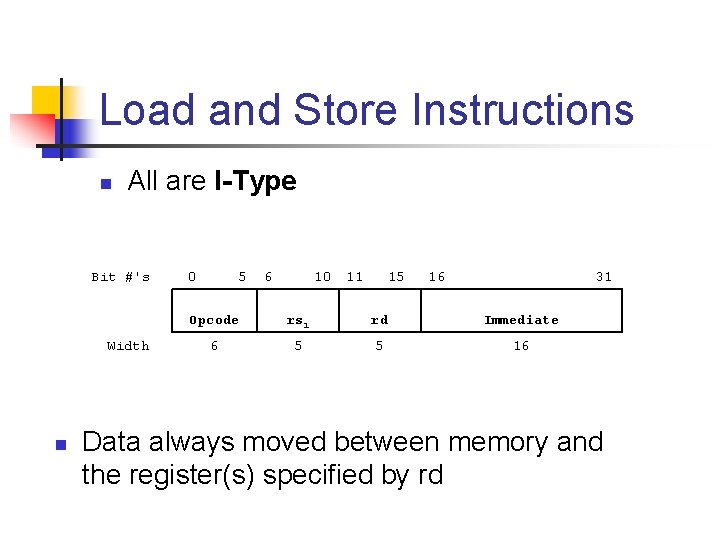

Load and Store Instructions n All are I-Type Bit #'s Width n 0 5 6 10 11 15 16 31 Opcode rs 1 rd Immediate 6 5 5 16 Data always moved between memory and the register(s) specified by rd

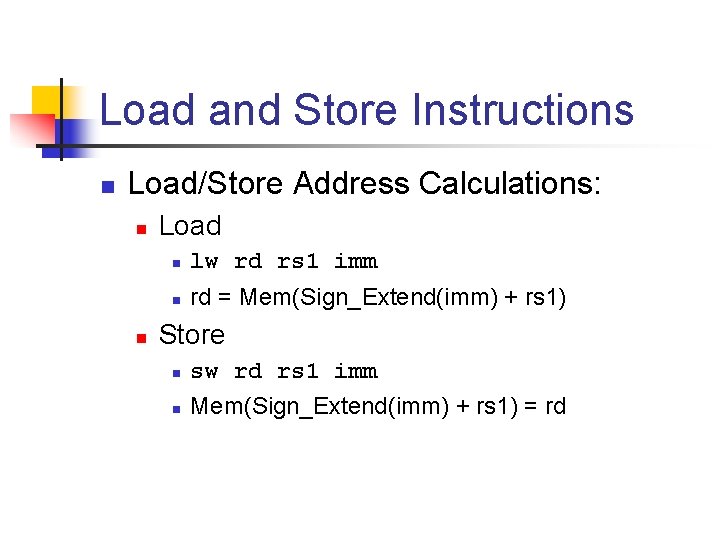

Load and Store Instructions n Load/Store Address Calculations: n n Load n lw rd rs 1 imm n rd = Mem(Sign_Extend(imm) + rs 1) Store n sw rd rs 1 imm n Mem(Sign_Extend(imm) + rs 1) = rd

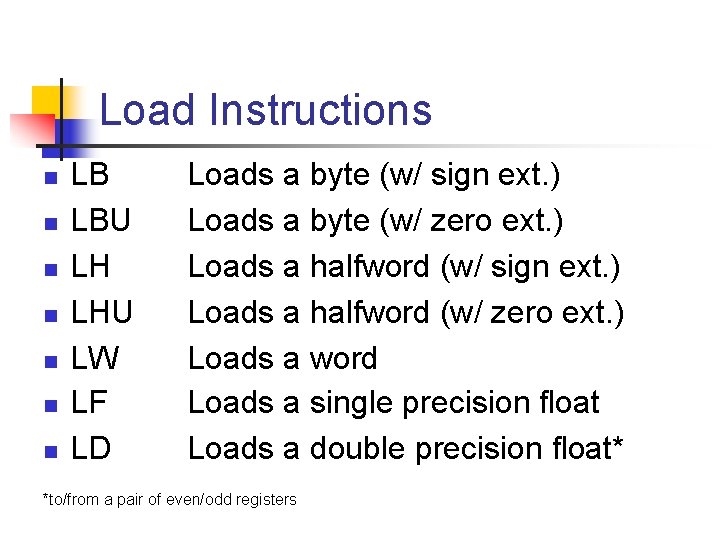

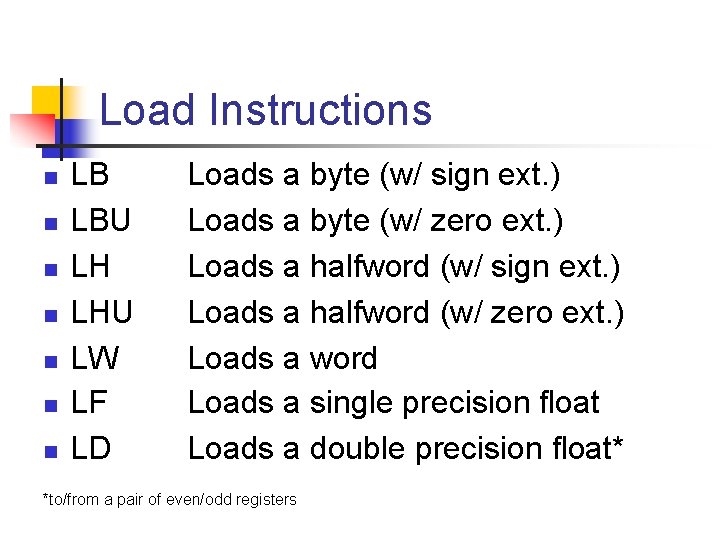

Load Instructions n n n n LB LBU LH LHU LW LF LD Loads a byte (w/ sign ext. ) Loads a byte (w/ zero ext. ) Loads a halfword (w/ sign ext. ) Loads a halfword (w/ zero ext. ) Loads a word Loads a single precision float Loads a double precision float* *to/from a pair of even/odd registers

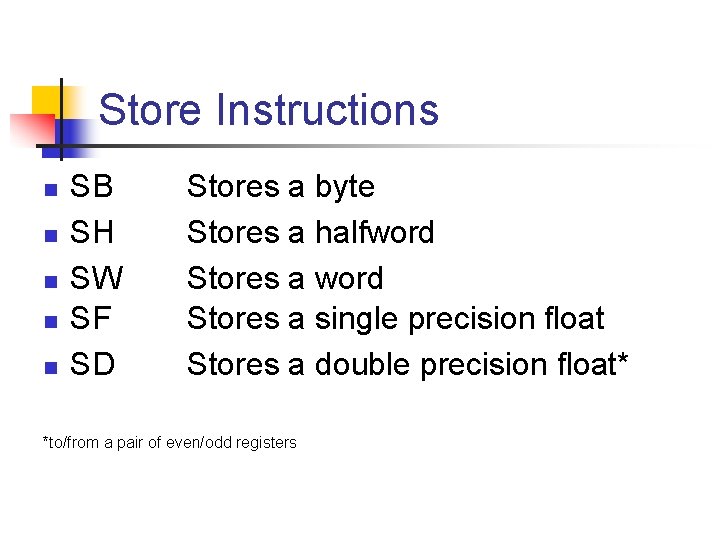

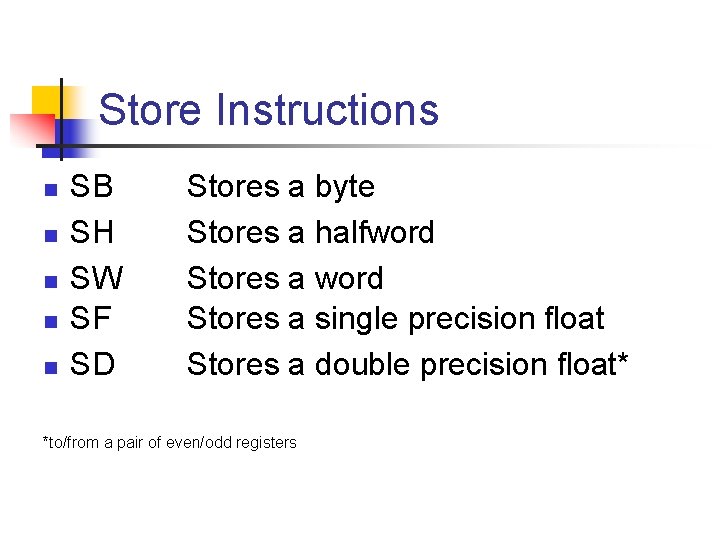

Store Instructions n n n SB SH SW SF SD Stores a byte Stores a halfword Stores a single precision float Stores a double precision float* *to/from a pair of even/odd registers

Thank You