Quad 2 to1 and Quad 4 to1 Multiplexers

- Slides: 10

Quad 2 -to-1 and Quad 4 -to-1 Multiplexers Discussion D 2. 4 Example 7

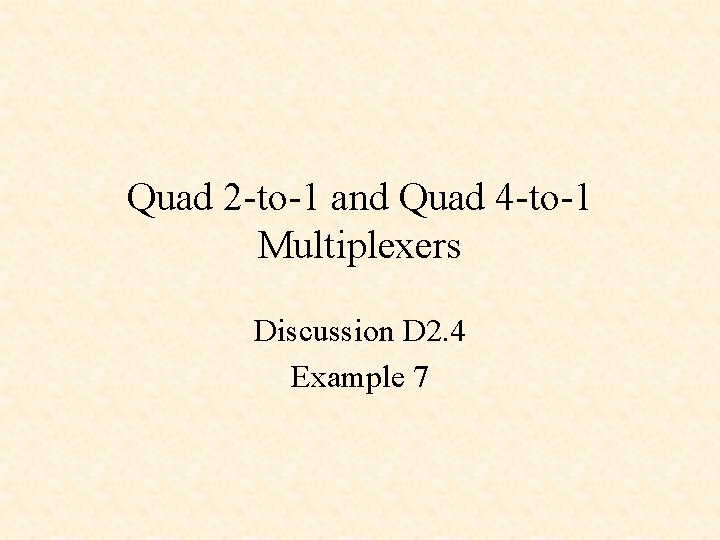

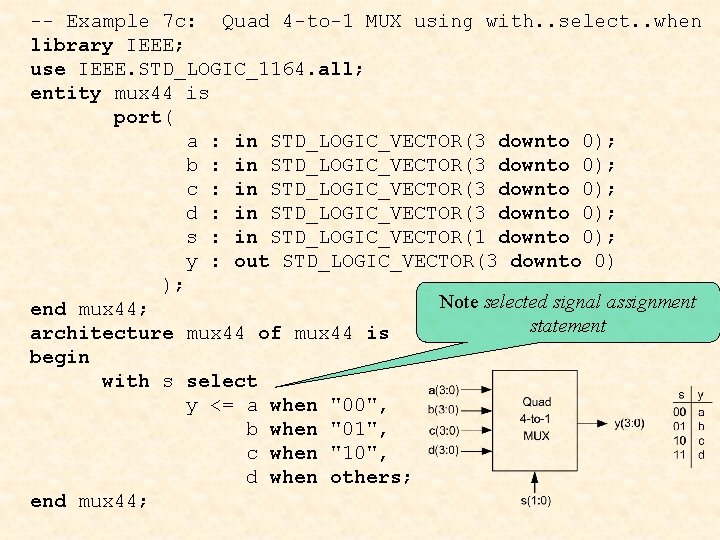

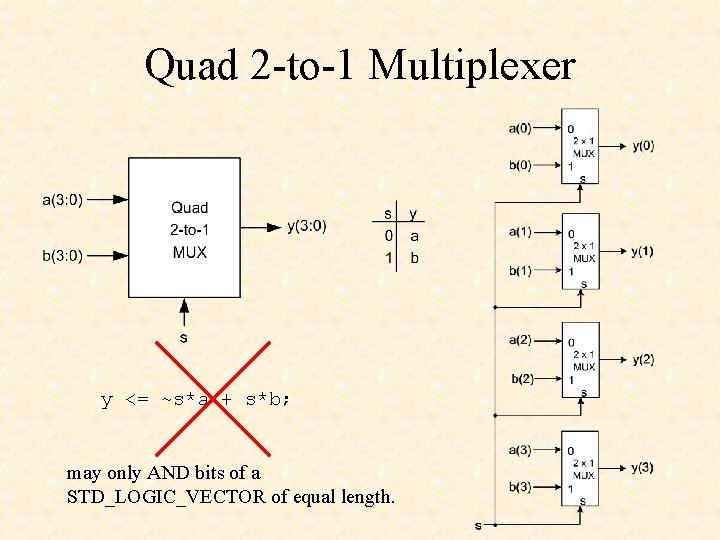

Quad 2 -to-1 Multiplexer

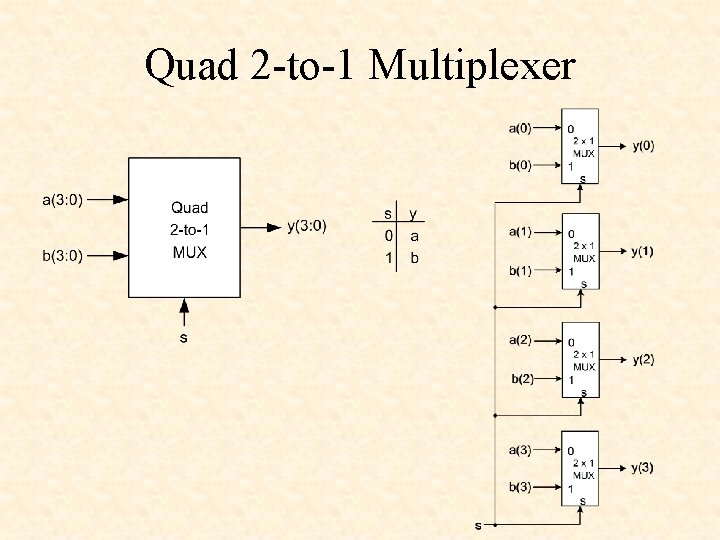

Quad 2 -to-1 Multiplexer y <= ~s*a + s*b; may only AND bits of a STD_LOGIC_VECTOR of equal length.

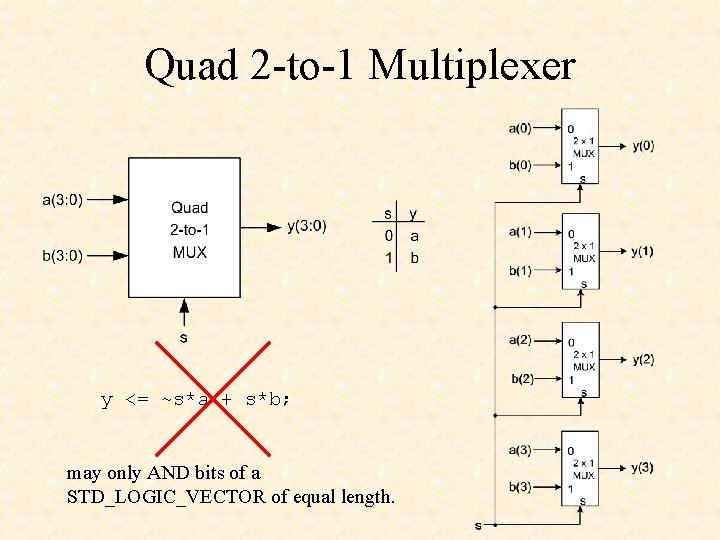

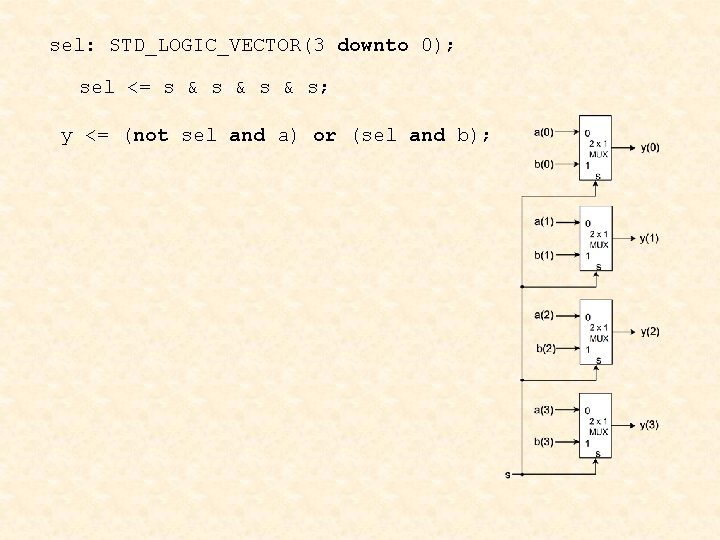

sel: STD_LOGIC_VECTOR(3 downto 0); sel <= s & s & s; y <= (not sel and a) or (sel and b);

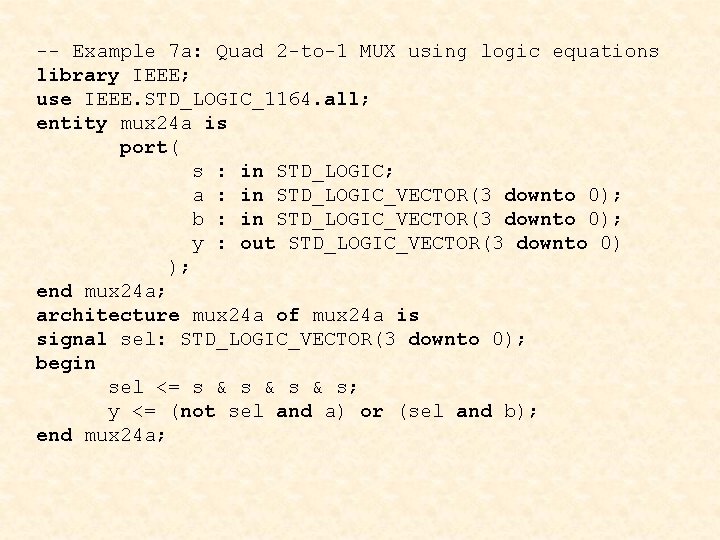

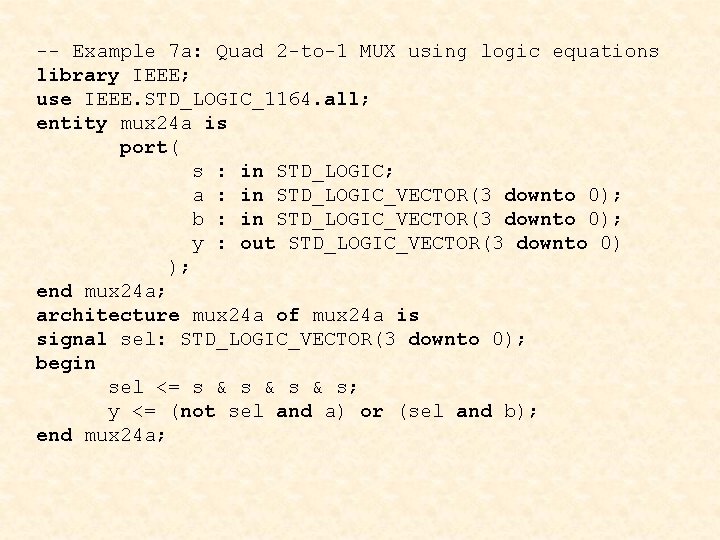

-- Example 7 a: Quad 2 -to-1 MUX using logic equations library IEEE; use IEEE. STD_LOGIC_1164. all; entity mux 24 a is port( s : in STD_LOGIC; a : in STD_LOGIC_VECTOR(3 downto 0); b : in STD_LOGIC_VECTOR(3 downto 0); y : out STD_LOGIC_VECTOR(3 downto 0) ); end mux 24 a; architecture mux 24 a of mux 24 a is signal sel: STD_LOGIC_VECTOR(3 downto 0); begin sel <= s & s & s; y <= (not sel and a) or (sel and b); end mux 24 a;

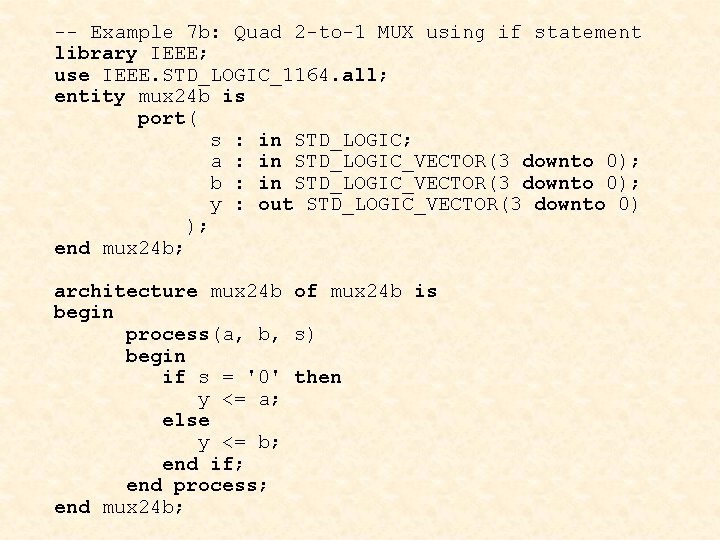

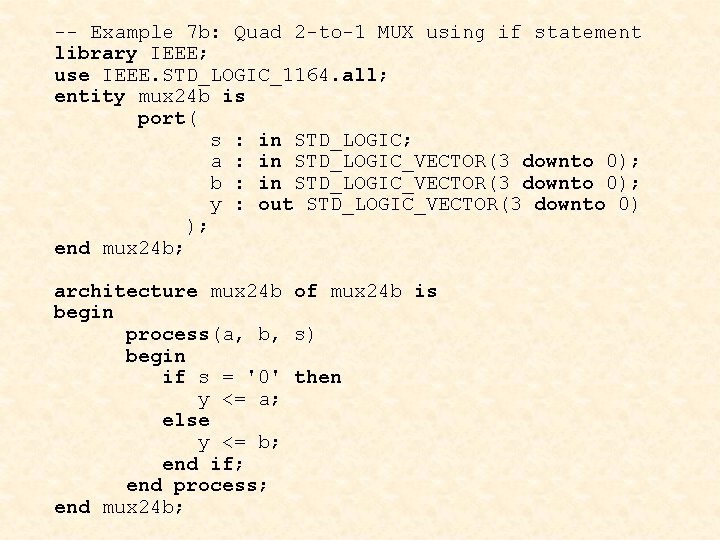

-- Example 7 b: Quad 2 -to-1 MUX using if statement library IEEE; use IEEE. STD_LOGIC_1164. all; entity mux 24 b is port( s : in STD_LOGIC; a : in STD_LOGIC_VECTOR(3 downto 0); b : in STD_LOGIC_VECTOR(3 downto 0); y : out STD_LOGIC_VECTOR(3 downto 0) ); end mux 24 b; architecture mux 24 b of mux 24 b is begin process(a, b, s) begin if s = '0' then y <= a; else y <= b; end if; end process; end mux 24 b;

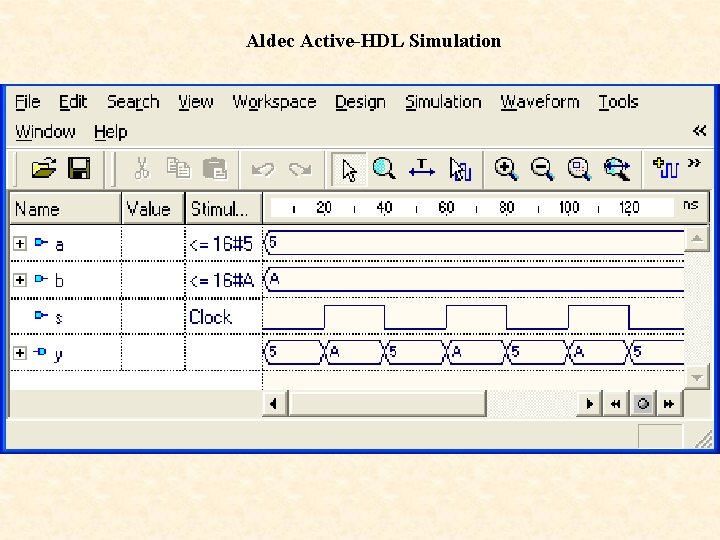

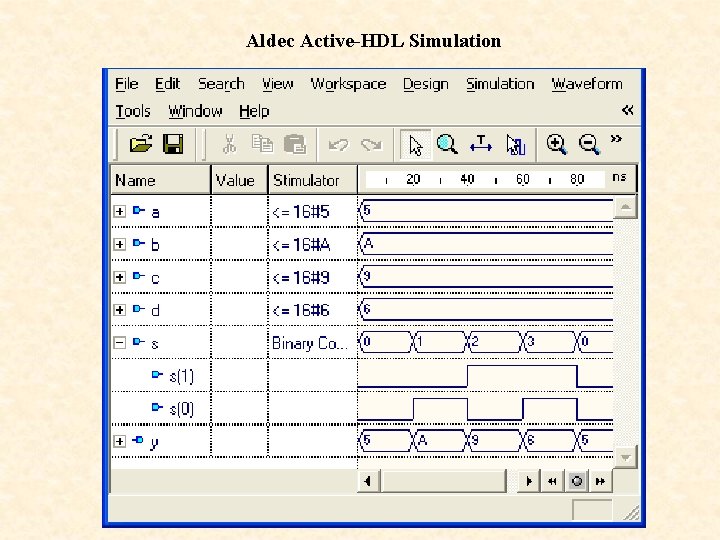

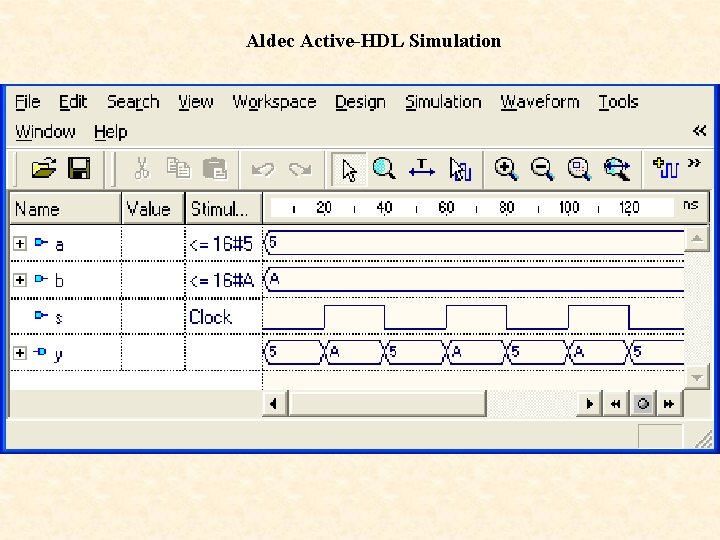

Aldec Active-HDL Simulation

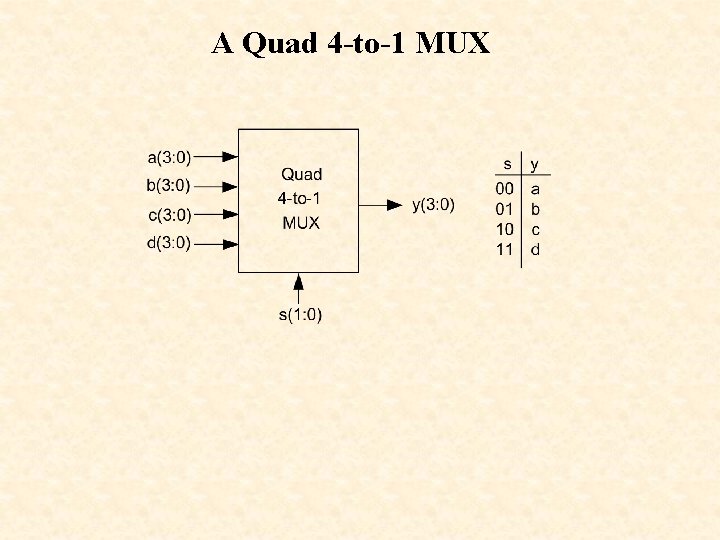

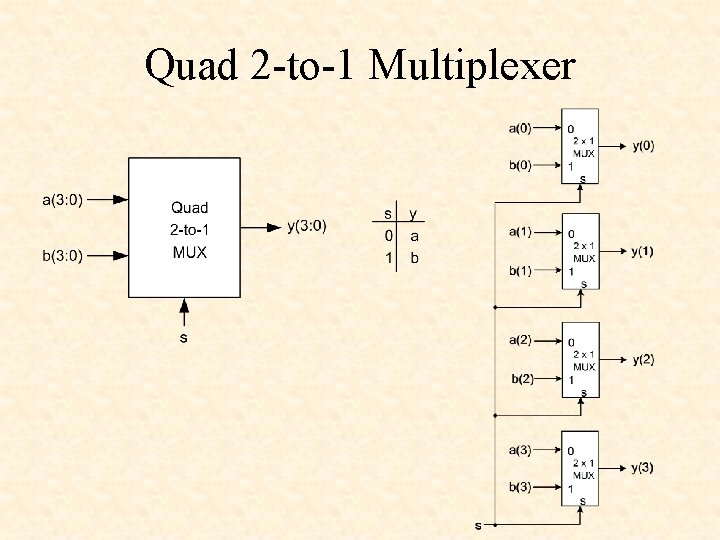

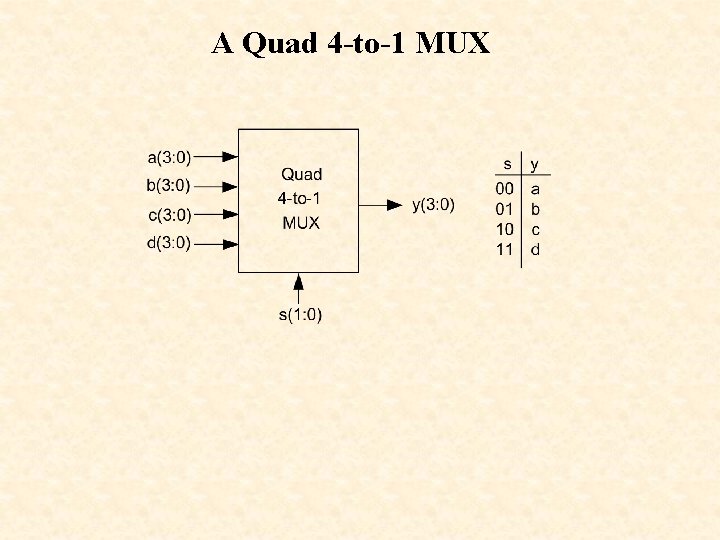

A Quad 4 -to-1 MUX

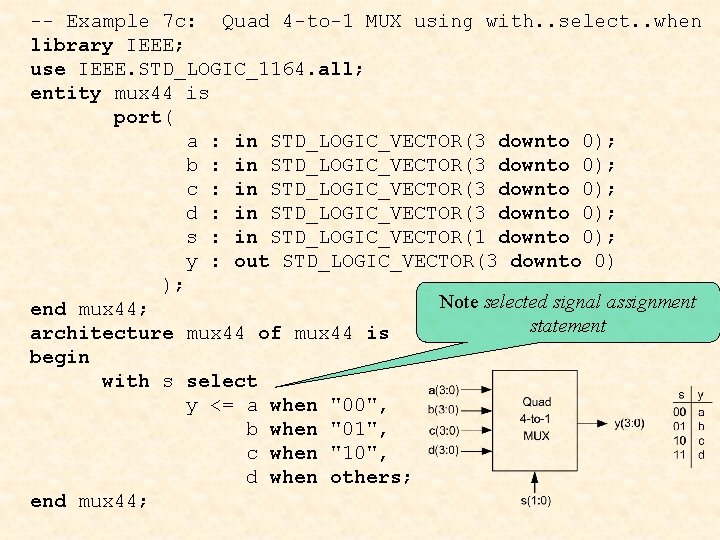

-- Example 7 c: Quad 4 -to-1 MUX using with. . select. . when library IEEE; use IEEE. STD_LOGIC_1164. all; entity mux 44 is port( a : in STD_LOGIC_VECTOR(3 downto 0); b : in STD_LOGIC_VECTOR(3 downto 0); c : in STD_LOGIC_VECTOR(3 downto 0); d : in STD_LOGIC_VECTOR(3 downto 0); s : in STD_LOGIC_VECTOR(1 downto 0); y : out STD_LOGIC_VECTOR(3 downto 0) ); Note selected signal assignment end mux 44; statement architecture mux 44 of mux 44 is begin with s select y <= a when "00", b when "01", c when "10", d when others; end mux 44;

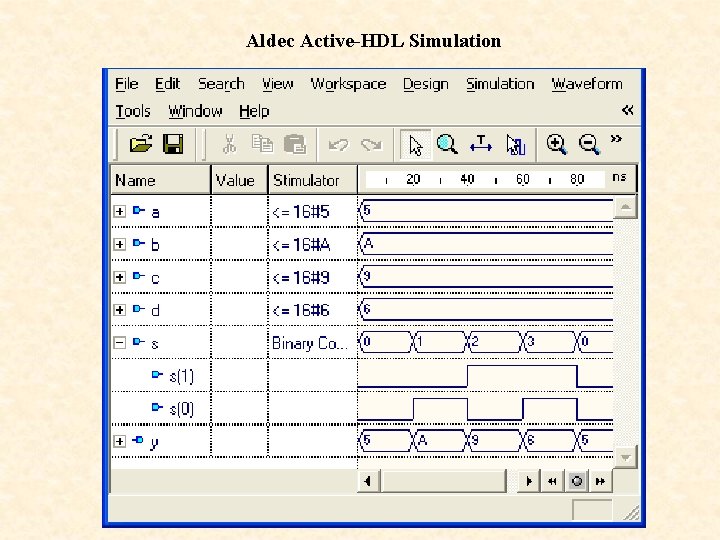

Aldec Active-HDL Simulation