DLX Register Ops Team Brian Leslie Stephen Brenner

DLX Register Ops Team Brian Leslie Stephen Brenner Brian Leslie Ben Whitcher

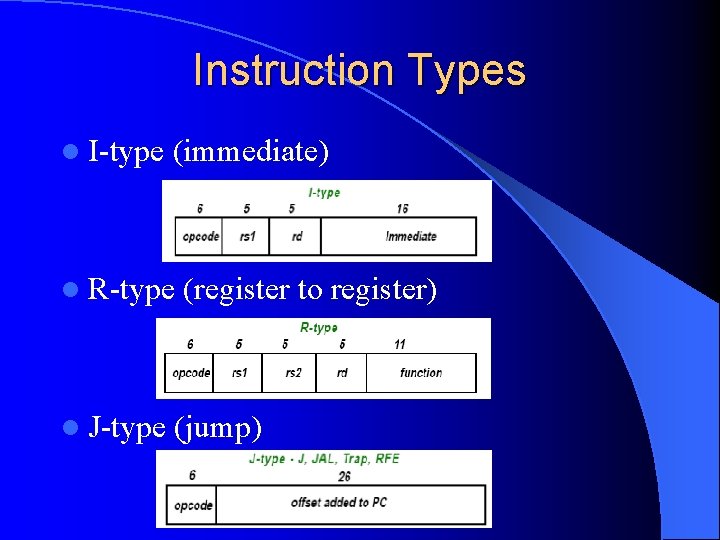

Instruction Types l I-type (immediate) l R-type l J-type (register to register) (jump)

Arithmetic & Logical Instructions l Arithmetic l Logical l Shift l Set-On-Comparison

Arithmetic l ADD, SUB, MULT, DIV – Two registers l ADDI, SUBI – Register & 16 -bit immediate l ADDU, SUBU, MULTU, DIVU – Treats source register as unsigned integer l ADDUI, SUBUI

![Arithmetic examples l ADD R 1, R 2, R 3 – Regs[R 1] <- Arithmetic examples l ADD R 1, R 2, R 3 – Regs[R 1] <-](http://slidetodoc.com/presentation_image/2b892806040cb3e6cf30711a8a0e2149/image-5.jpg)

Arithmetic examples l ADD R 1, R 2, R 3 – Regs[R 1] <- Regs[R 2] + Regs[R 3] l SUBI R 1, R 2, #2 – Regs[R 1] <- Regs[R 2] + 2

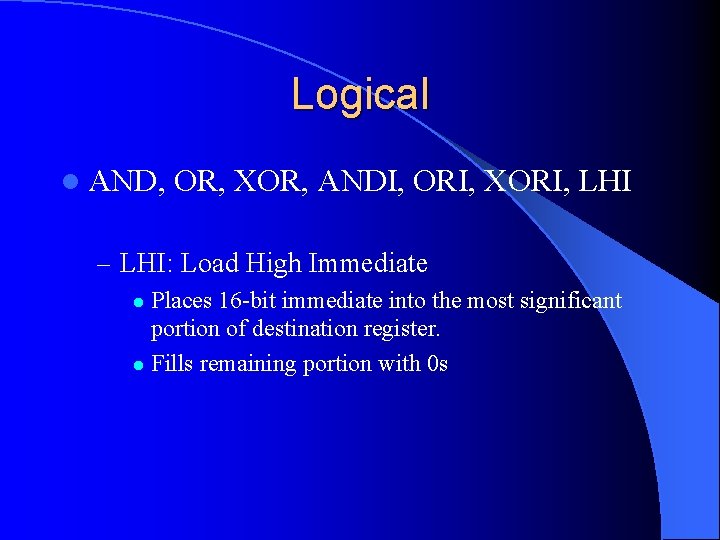

Logical l AND, OR, XOR, ANDI, ORI, XORI, LHI – LHI: Load High Immediate Places 16 -bit immediate into the most significant portion of destination register. l Fills remaining portion with 0 s l

![Logical examples l AND R 1, R 2, R 3 – Regs[R 1] <- Logical examples l AND R 1, R 2, R 3 – Regs[R 1] <-](http://slidetodoc.com/presentation_image/2b892806040cb3e6cf30711a8a0e2149/image-7.jpg)

Logical examples l AND R 1, R 2, R 3 – Regs[R 1] <- Regs[R 2] & Regs[R 3] l LHI R 1, 0 x 42 – Regs[R 1] <- 0 x 420000

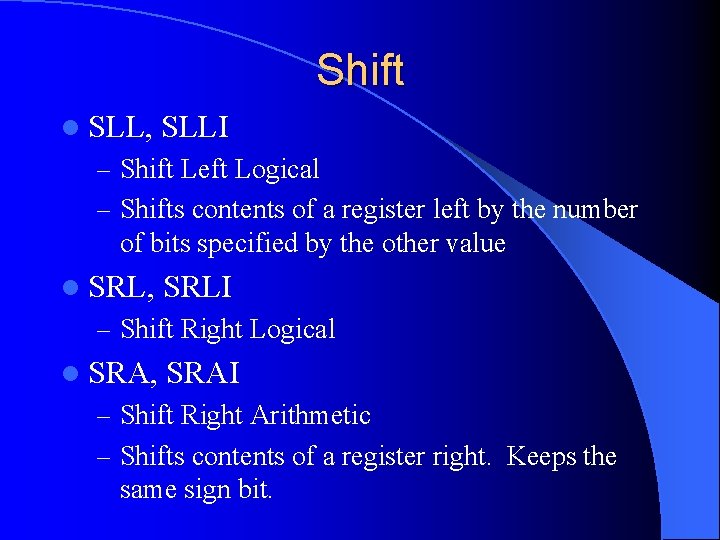

Shift l SLL, SLLI – Shift Left Logical – Shifts contents of a register left by the number of bits specified by the other value l SRL, SRLI – Shift Right Logical l SRA, SRAI – Shift Right Arithmetic – Shifts contents of a register right. Keeps the same sign bit.

![Shift examples l SLL R 1, R 2, R 3 – Regs[R 1] <- Shift examples l SLL R 1, R 2, R 3 – Regs[R 1] <-](http://slidetodoc.com/presentation_image/2b892806040cb3e6cf30711a8a0e2149/image-9.jpg)

Shift examples l SLL R 1, R 2, R 3 – Regs[R 1] <- Regs[R 2] << Regs[R 3] l SRAI R 1, R 2, 0 x 2 – Regs[R 1] <- Regs[R 2] >> 0 x 2 l Keep R 2’s sign

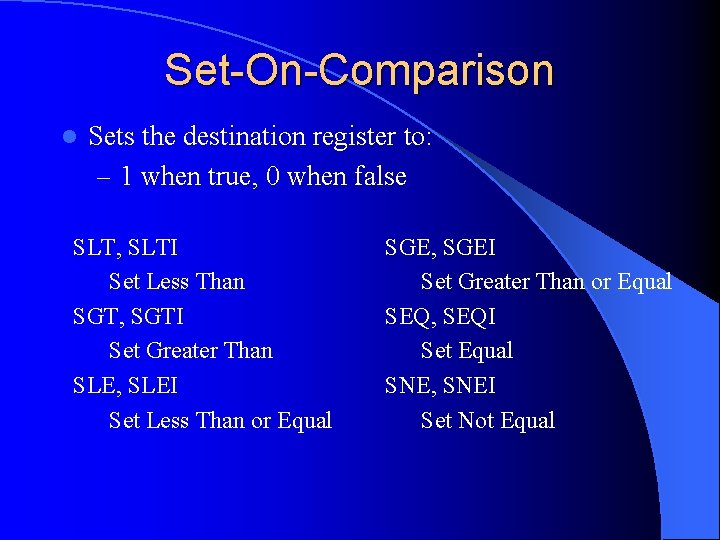

Set-On-Comparison l Sets the destination register to: – 1 when true, 0 when false SLT, SLTI Set Less Than SGT, SGTI Set Greater Than SLE, SLEI Set Less Than or Equal SGE, SGEI Set Greater Than or Equal SEQ, SEQI Set Equal SNE, SNEI Set Not Equal

![Set-On-Comparison examples l SLT R 1, R 2, R 3 – If (Regs[R 2] Set-On-Comparison examples l SLT R 1, R 2, R 3 – If (Regs[R 2]](http://slidetodoc.com/presentation_image/2b892806040cb3e6cf30711a8a0e2149/image-11.jpg)

Set-On-Comparison examples l SLT R 1, R 2, R 3 – If (Regs[R 2] < Regs[R 3]) Regs[R 1] <- 1 else Regs[R 1] <- 0 l SNEI R 1, R 2, 0 x 7 – If (Regs[R 2] != 0 x 7) Regs[R 1] <- 1 else Regs[R 1] <- 0

- Slides: 11