EE 5780 Advanced VLSI Computer Aided Design VLSI

- Slides: 37

EE 5780 Advanced VLSI Computer. Aided Design VLSI Placement Prof. Shiyan Hu shiyan@mtu. edu Office: EERC 518 9/25/2020 1

Objectives • Placement Problem Formulation – Motivation – Definition • Placement Technique – General flow – Quadratic program based wirelength optimization – FM Partitioning 9/25/2020 2

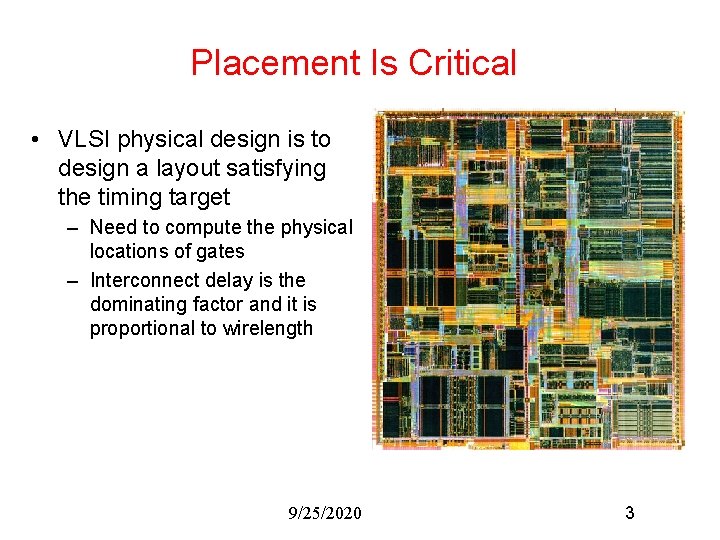

Placement Is Critical • VLSI physical design is to design a layout satisfying the timing target – Need to compute the physical locations of gates – Interconnect delay is the dominating factor and it is proportional to wirelength 9/25/2020 3

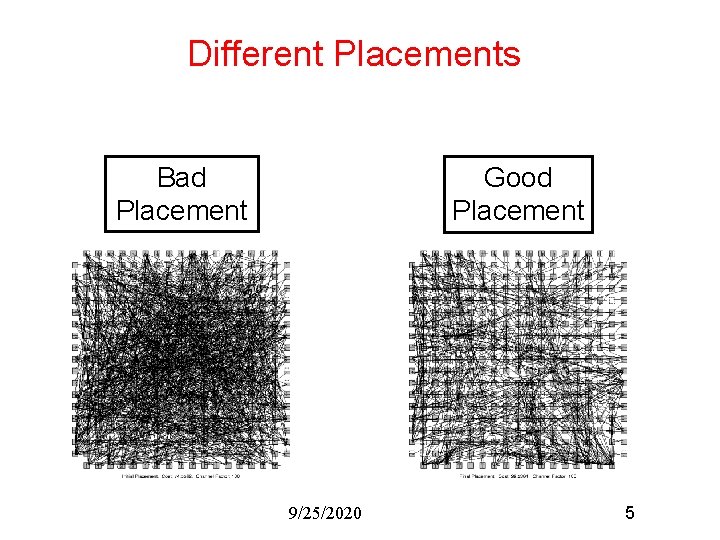

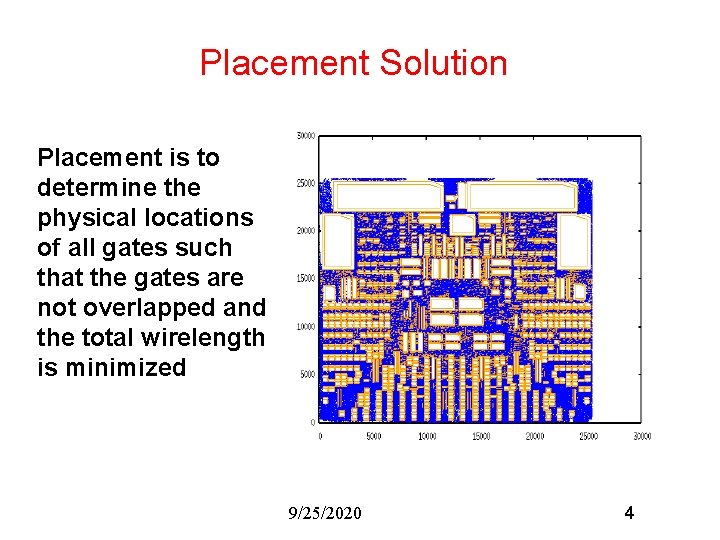

Placement Solution Placement is to determine the physical locations of all gates such that the gates are not overlapped and the total wirelength is minimized 9/25/2020 4

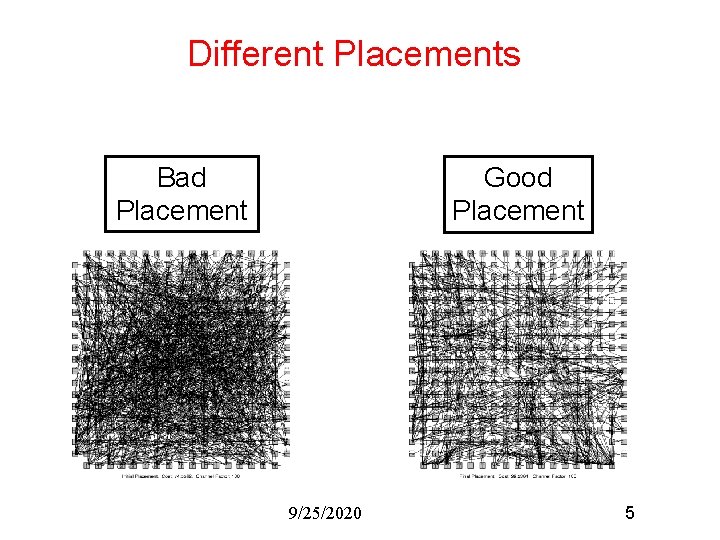

Different Placements Bad Placement Good Placement 9/25/2020 5

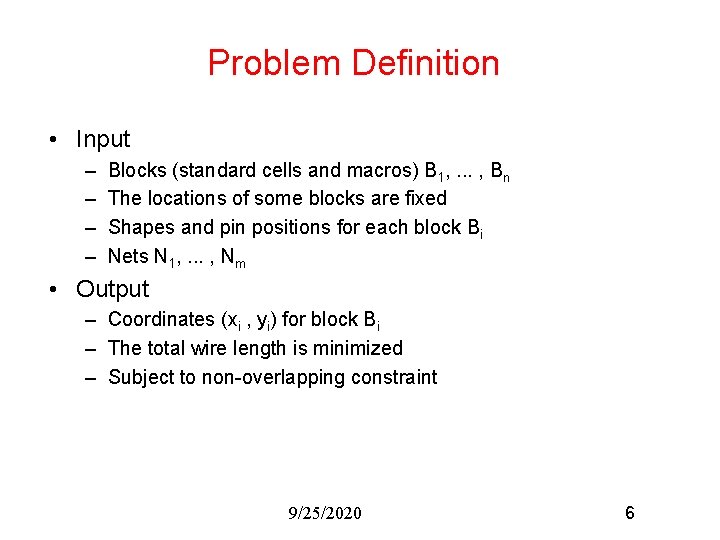

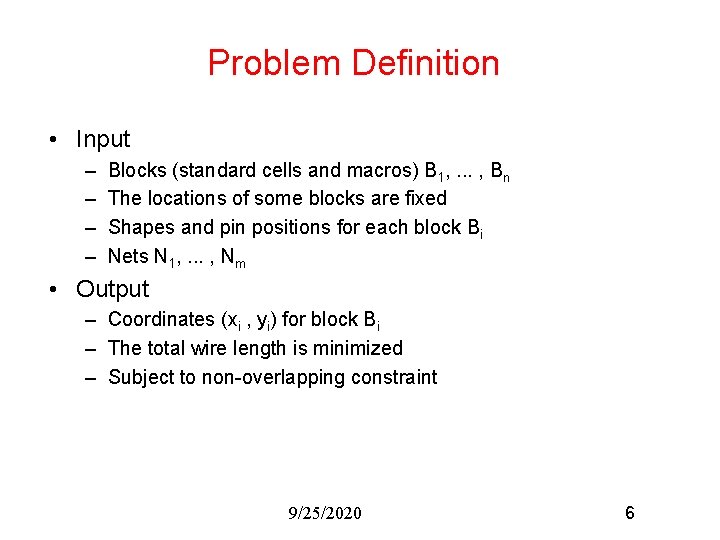

Problem Definition • Input – – Blocks (standard cells and macros) B 1, . . . , Bn The locations of some blocks are fixed Shapes and pin positions for each block Bi Nets N 1, . . . , Nm • Output – Coordinates (xi , yi) for block Bi – The total wire length is minimized – Subject to non-overlapping constraint 9/25/2020 6

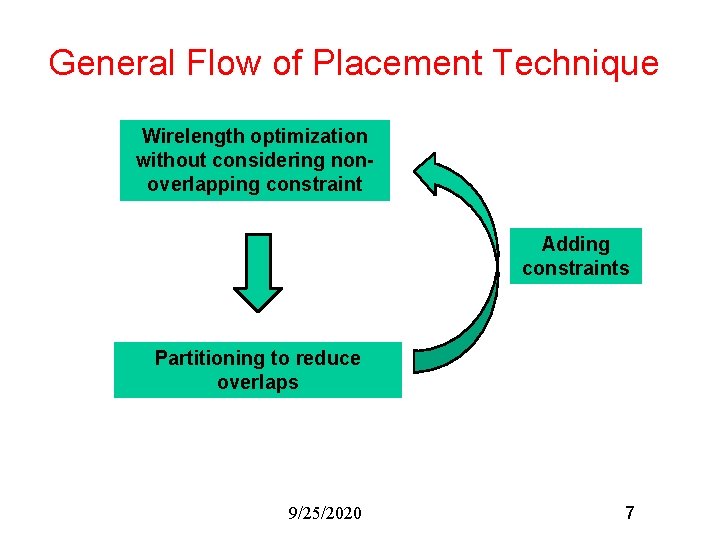

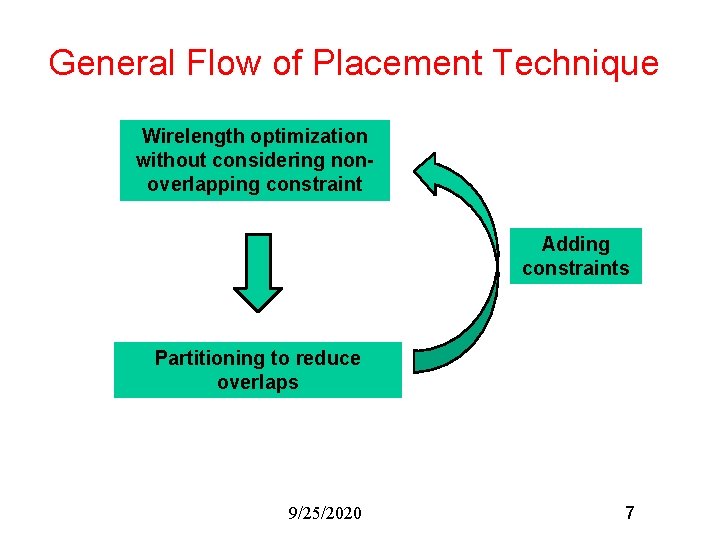

General Flow of Placement Technique Wirelength optimization without considering nonoverlapping constraint Adding constraints Partitioning to reduce overlaps 9/25/2020 7

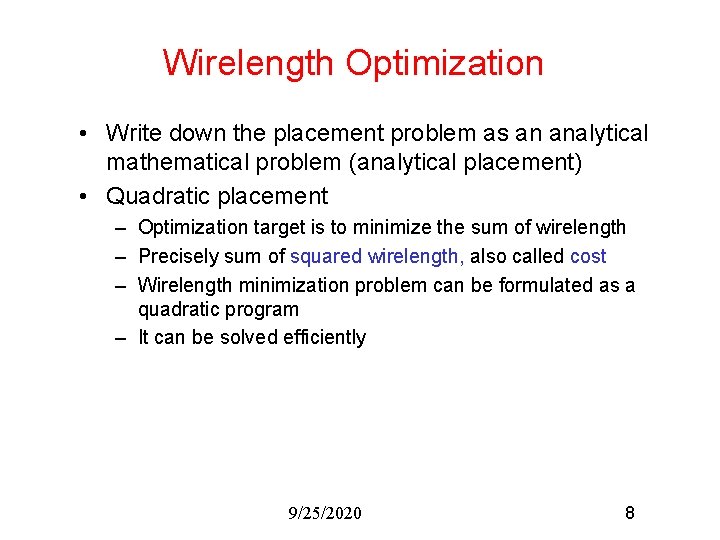

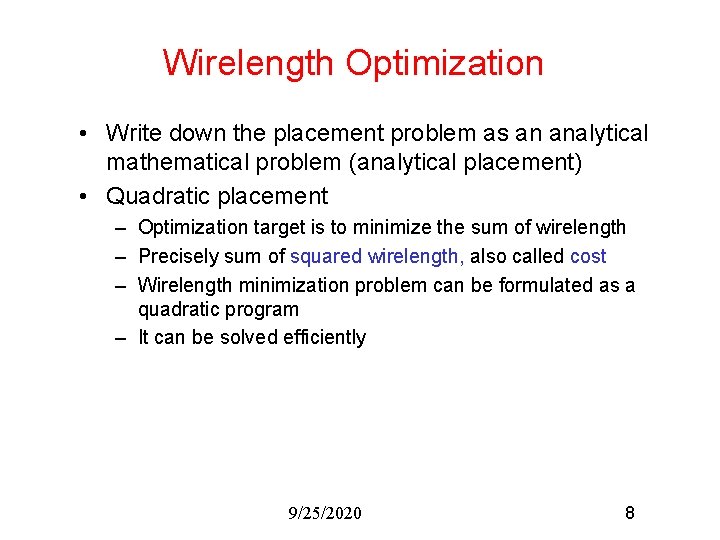

Wirelength Optimization • Write down the placement problem as an analytical mathematical problem (analytical placement) • Quadratic placement – Optimization target is to minimize the sum of wirelength – Precisely sum of squared wirelength, also called cost – Wirelength minimization problem can be formulated as a quadratic program – It can be solved efficiently 9/25/2020 8

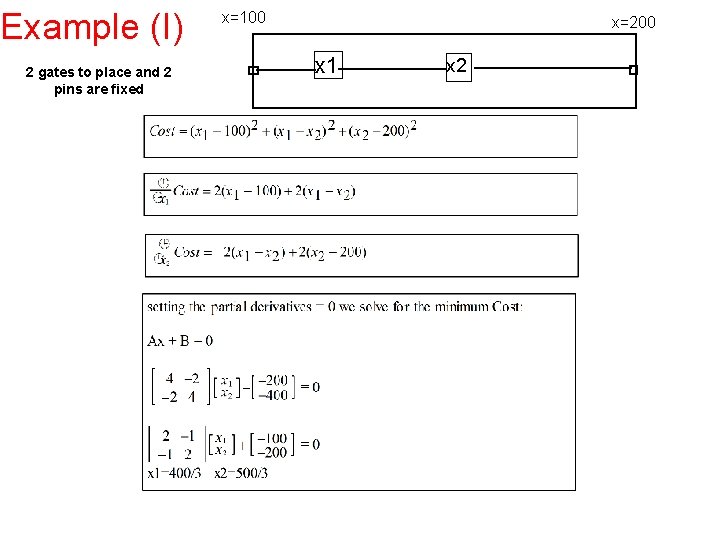

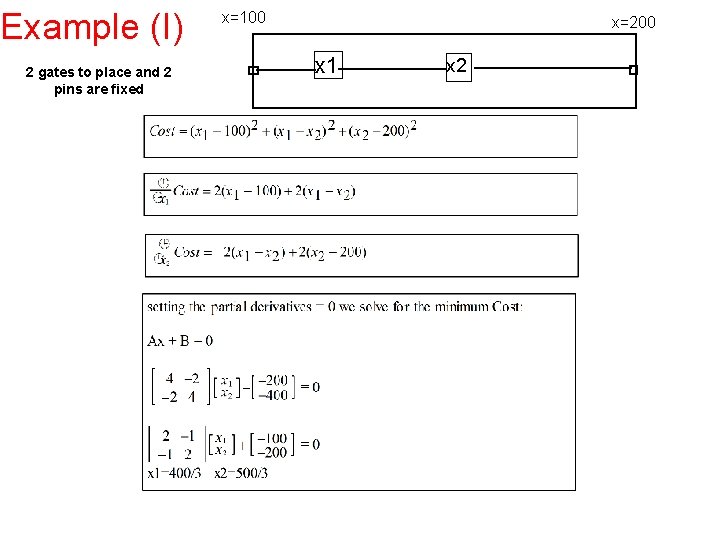

Example (I) 2 gates to place and 2 pins are fixed x=100 x=200 x 1 9/25/2020 x 2 9

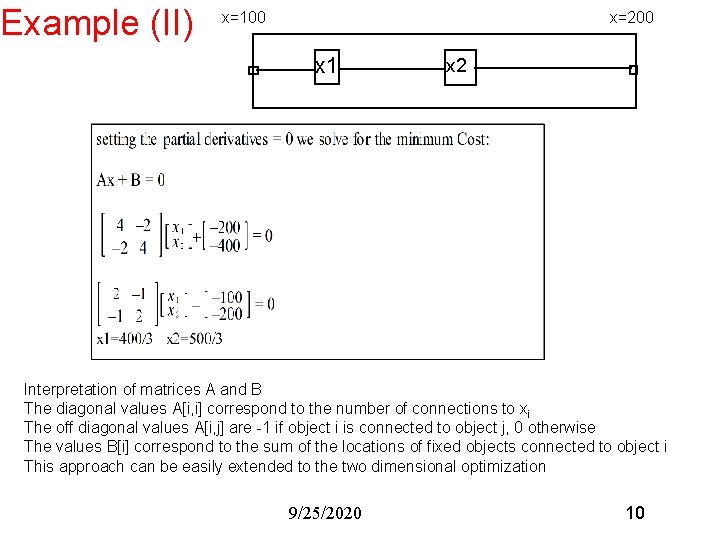

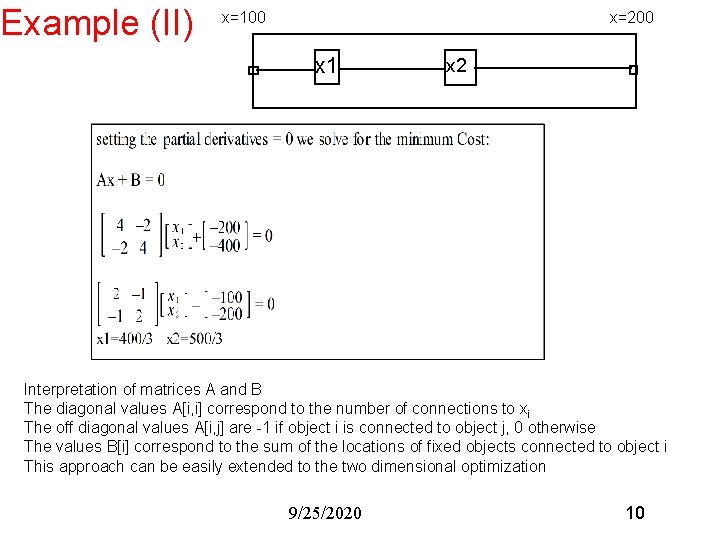

Example (II) x=100 x=200 x 1 x 2 Interpretation of matrices A and B The diagonal values A[i, i] correspond to the number of connections to xi The off diagonal values A[i, j] are -1 if object i is connected to object j, 0 otherwise The values B[i] correspond to the sum of the locations of fixed objects connected to object i This approach can be easily extended to the two dimensional optimization 9/25/2020 10

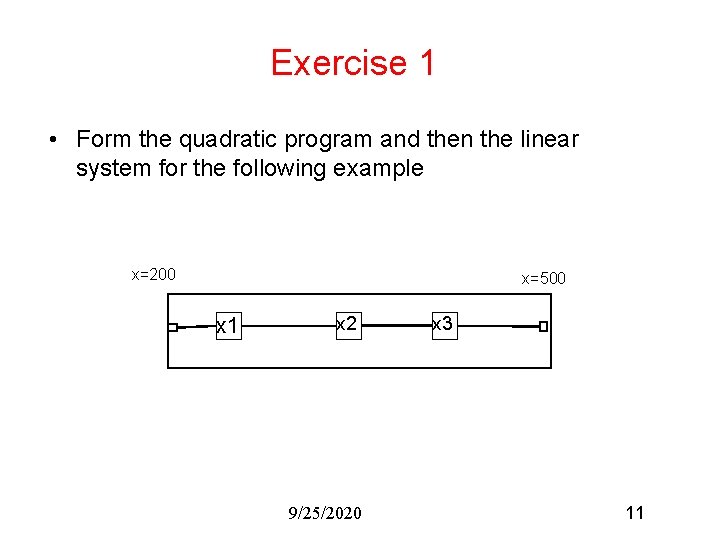

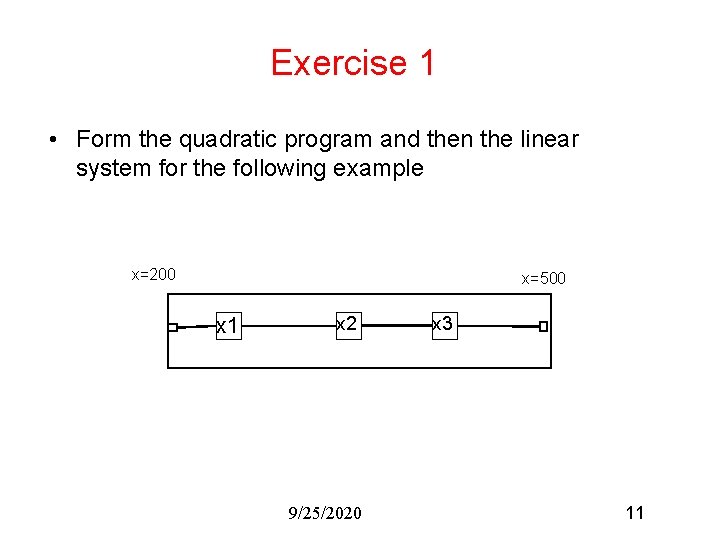

Exercise 1 • Form the quadratic program and then the linear system for the following example x=200 x=500 x 1 x 2 9/25/2020 x 3 11

Exercise 2 • How do we solve the linear system? How large is it? • It is a sparse linear system which can be efficiently solved using standard linear system solver such as the iterative conjugate gradient based approach. 9/25/2020 12

Exercise 3 • We choose to use square of wirelength in optimization target since the delay is a quadratic function of wirelength, but is it right target? 9/25/2020 13

Exercise 4 • When there are no fixed pins, what would the solution be? • Even with the fixed pins, there are still a lot of overlaps since in the quadratic program, non-overlapping constraint is not considered. 9/25/2020 14

The Placement Technique a Quadratic program minimize the squared wirelength a Partitioning reduce the overlap among gates 9/25/2020 15

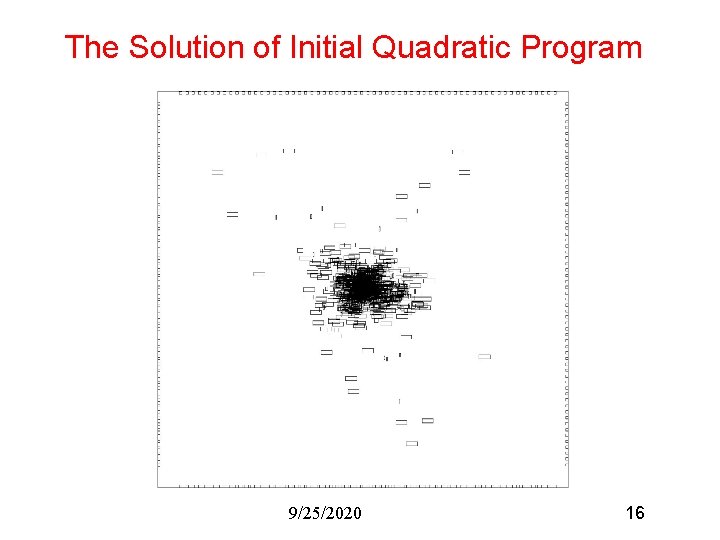

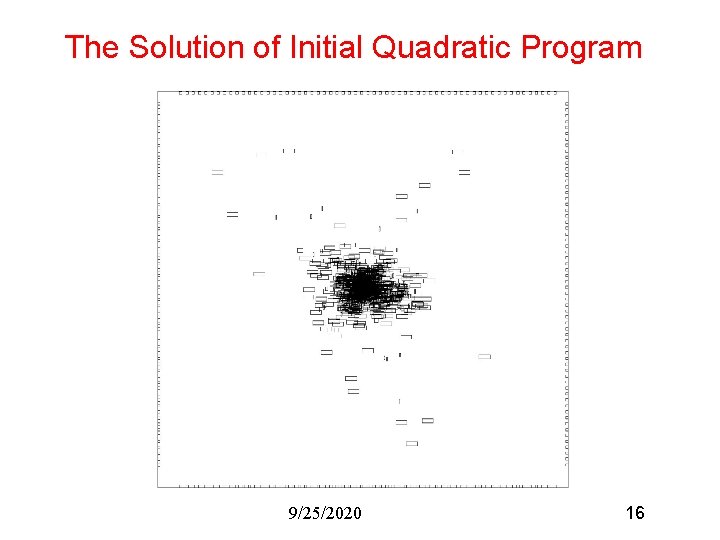

The Solution of Initial Quadratic Program 9/25/2020 16

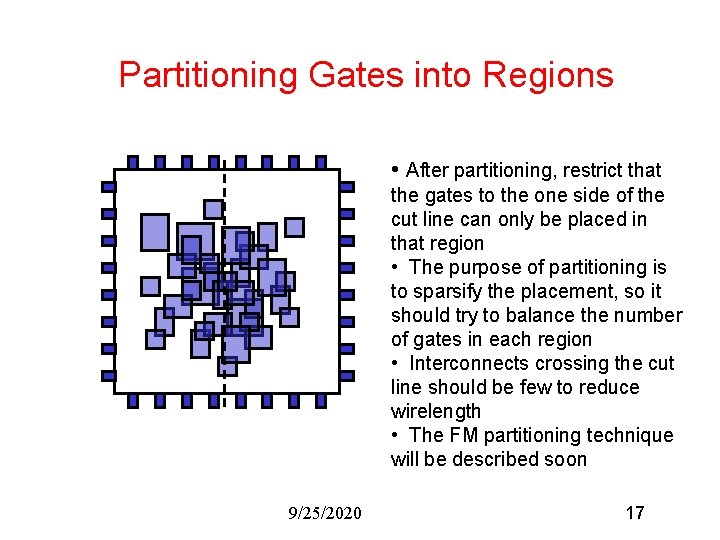

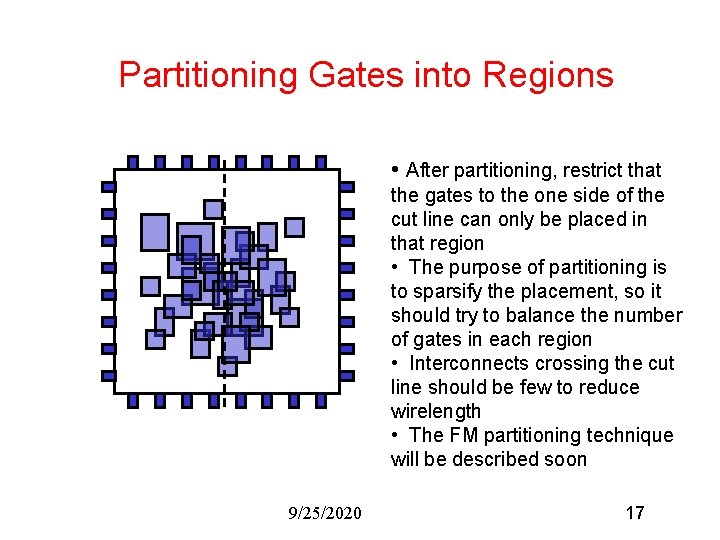

Partitioning Gates into Regions • After partitioning, restrict that the gates to the one side of the cut line can only be placed in that region • The purpose of partitioning is to sparsify the placement, so it should try to balance the number of gates in each region • Interconnects crossing the cut line should be few to reduce wirelength • The FM partitioning technique will be described soon 9/25/2020 17

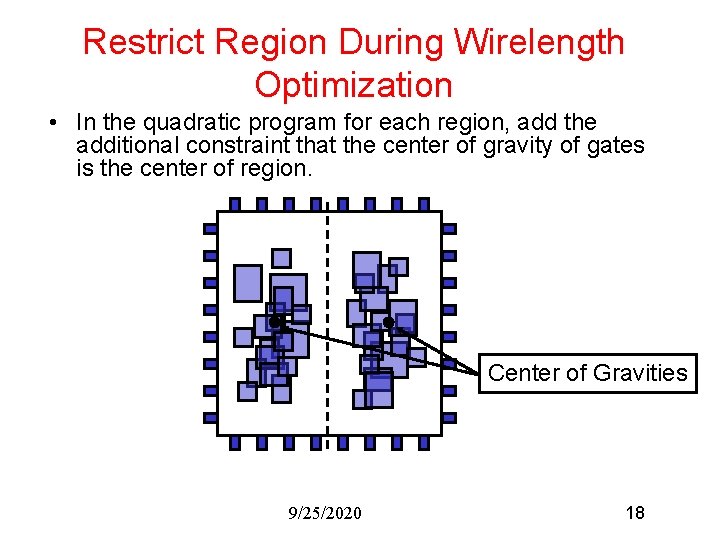

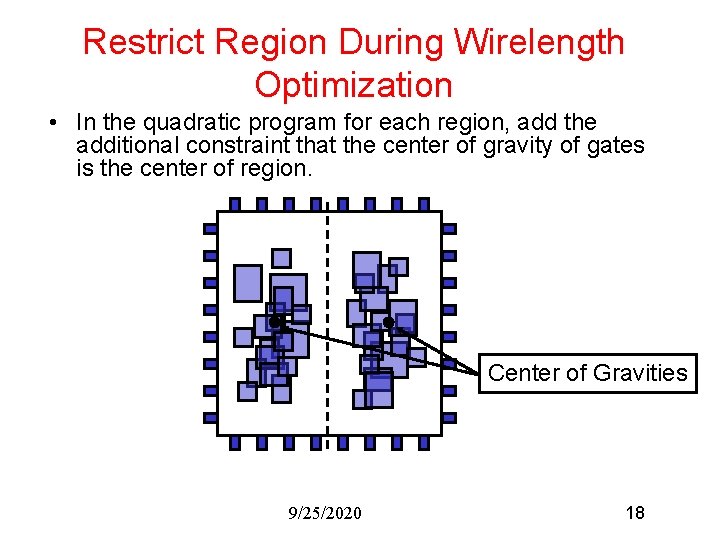

Restrict Region During Wirelength Optimization • In the quadratic program for each region, add the additional constraint that the center of gravity of gates is the center of region. Center of Gravities 9/25/2020 18

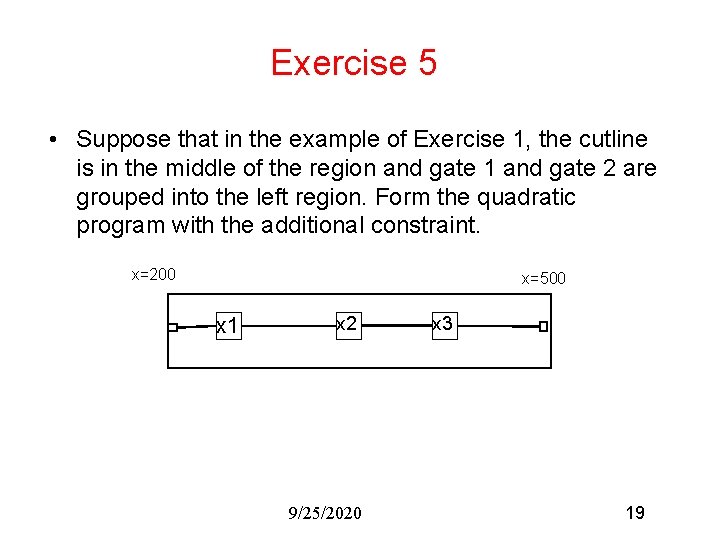

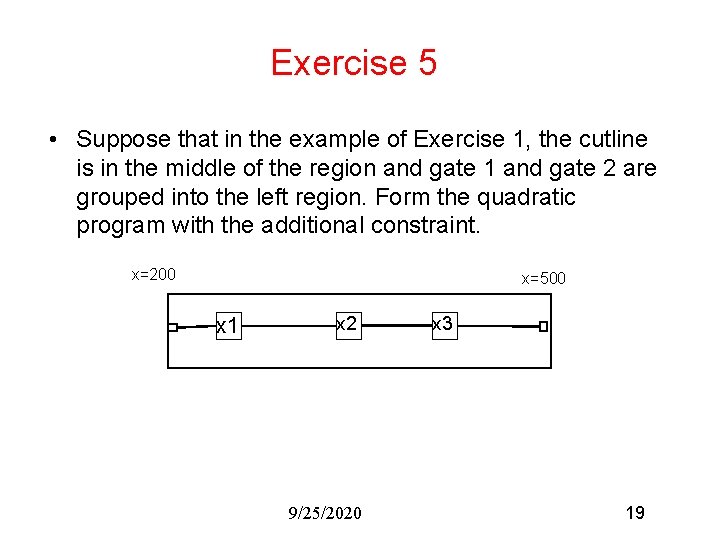

Exercise 5 • Suppose that in the example of Exercise 1, the cutline is in the middle of the region and gate 1 and gate 2 are grouped into the left region. Form the quadratic program with the additional constraint. x=200 x=500 x 1 x 2 9/25/2020 x 3 19

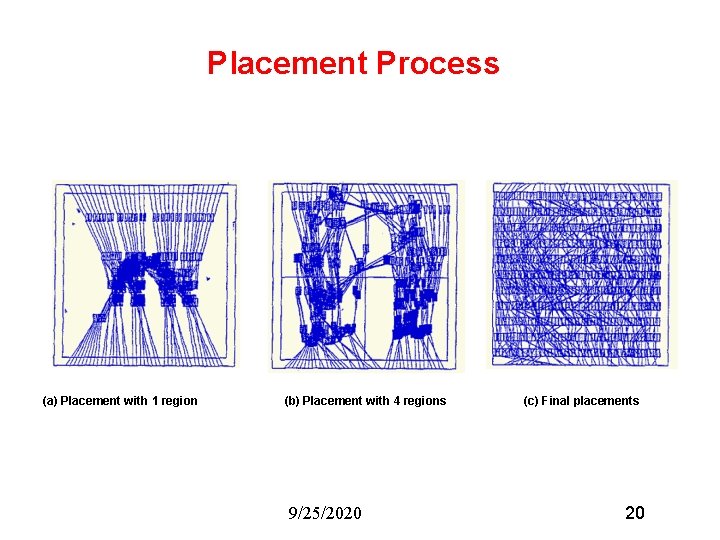

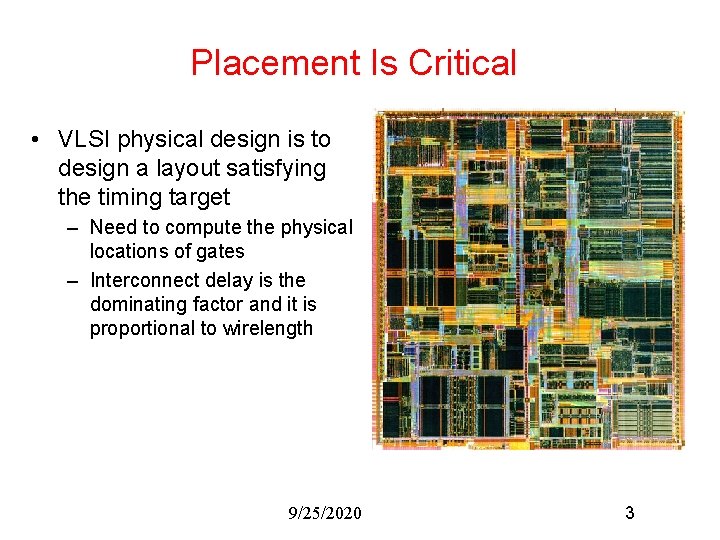

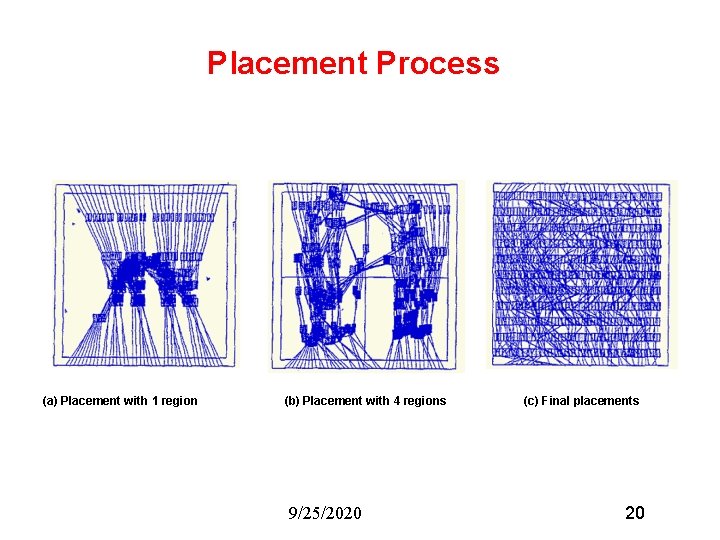

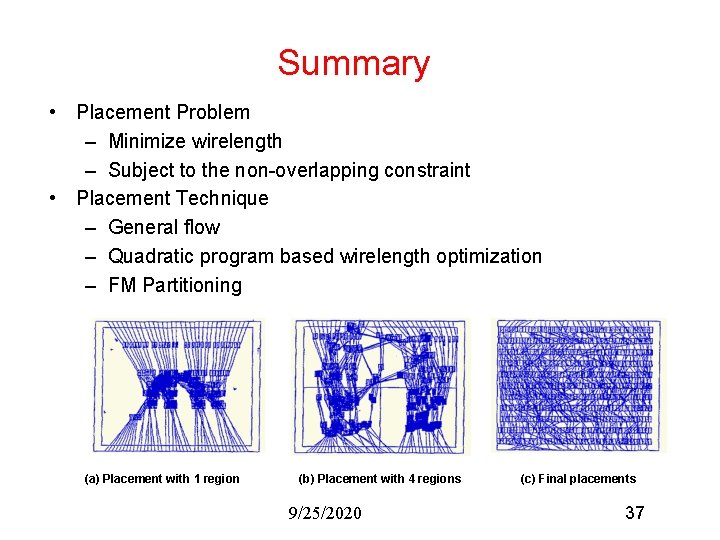

Placement Process (a) Placement with 1 region (b) Placement with 4 regions 9/25/2020 (c) Final placements 20

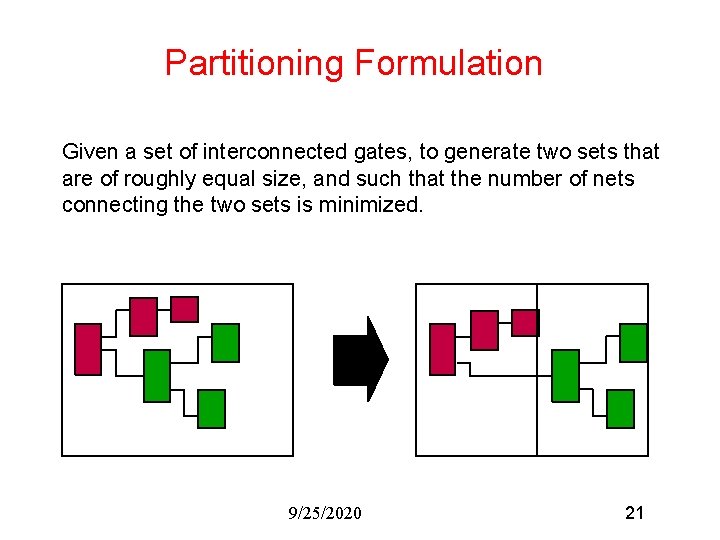

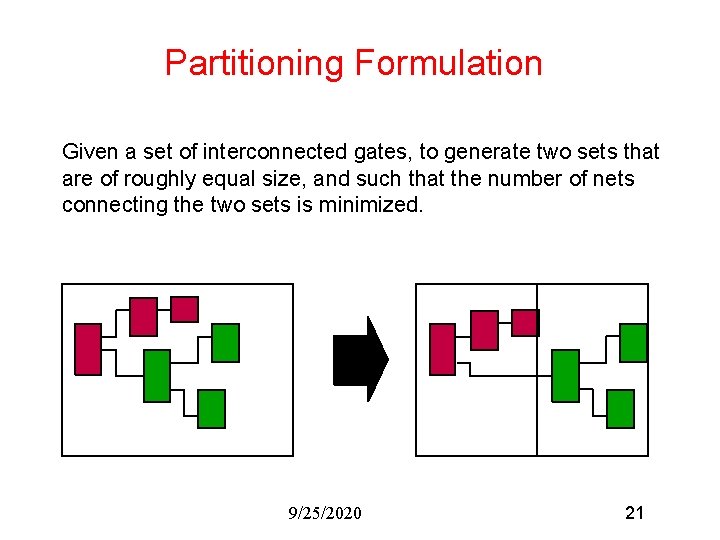

Partitioning Formulation Given a set of interconnected gates, to generate two sets that are of roughly equal size, and such that the number of nets connecting the two sets is minimized. 9/25/2020 21

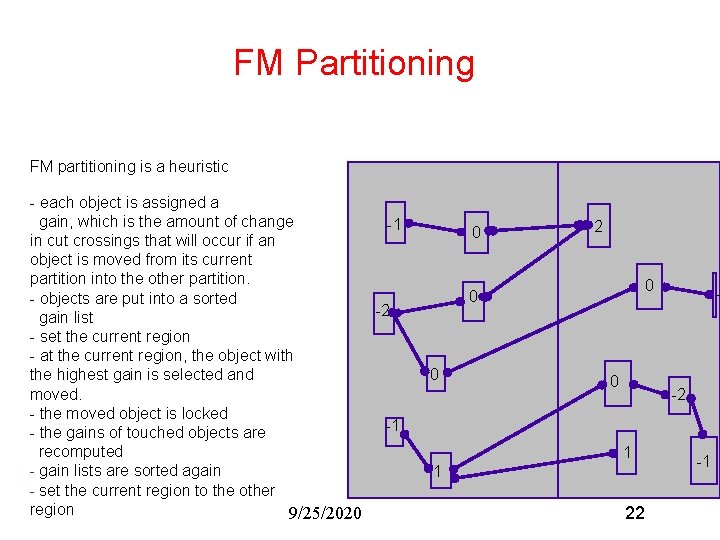

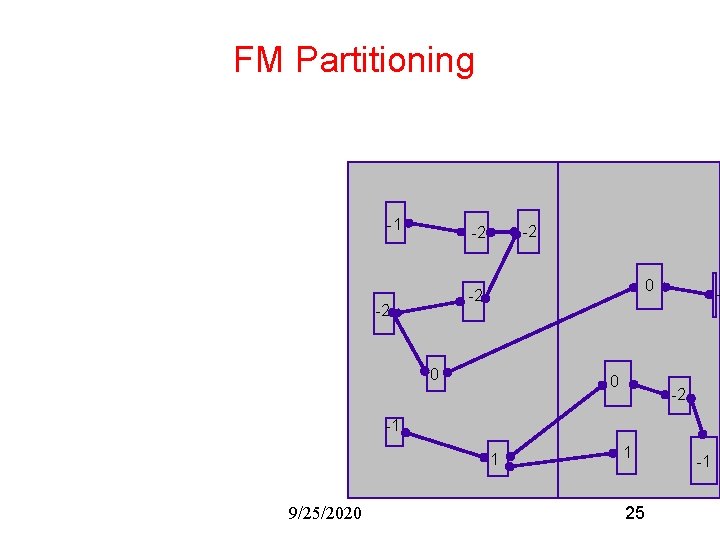

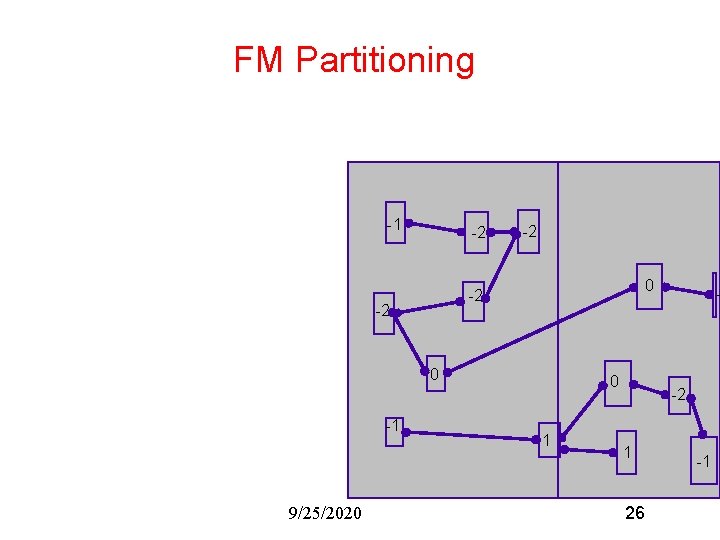

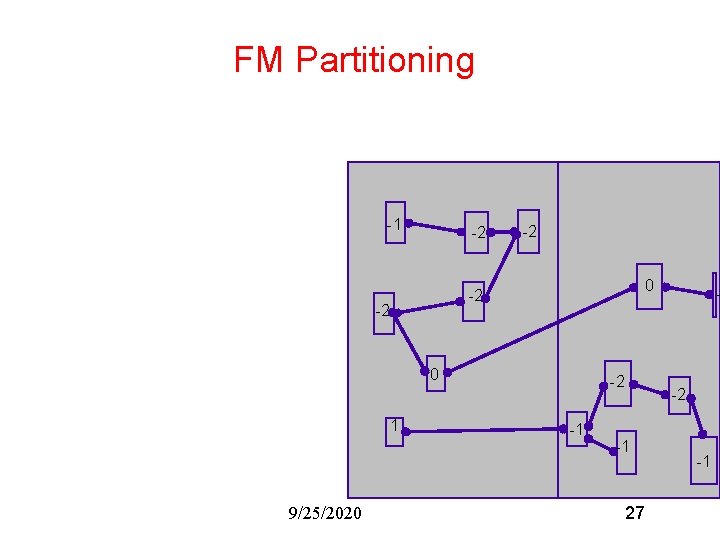

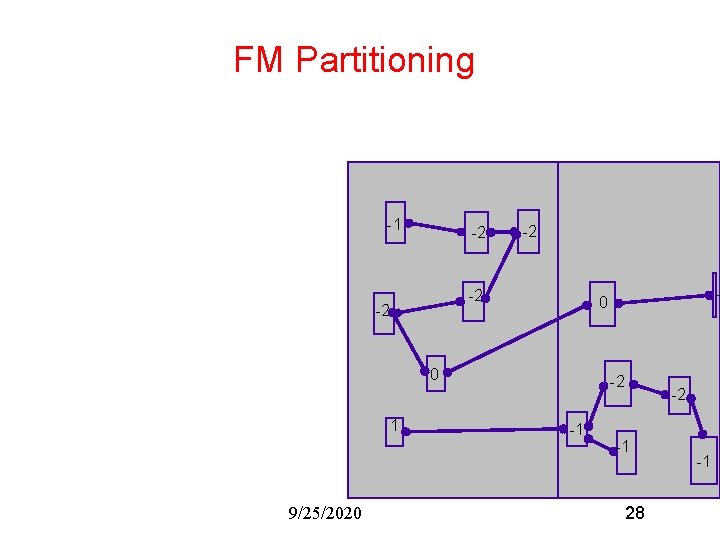

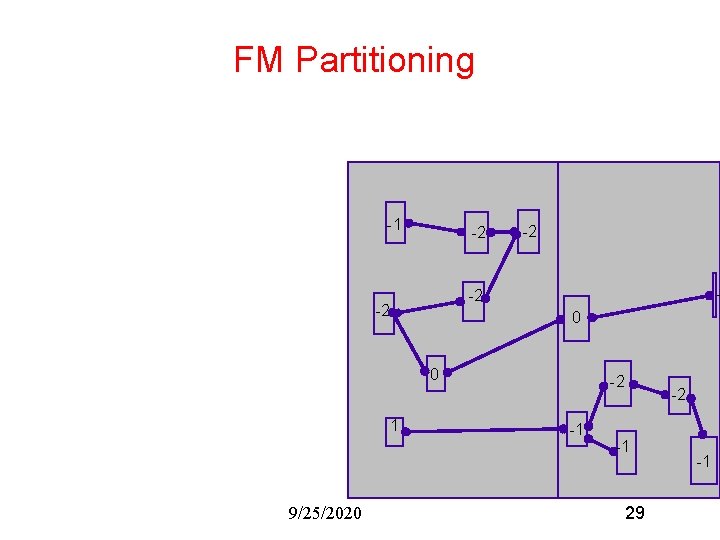

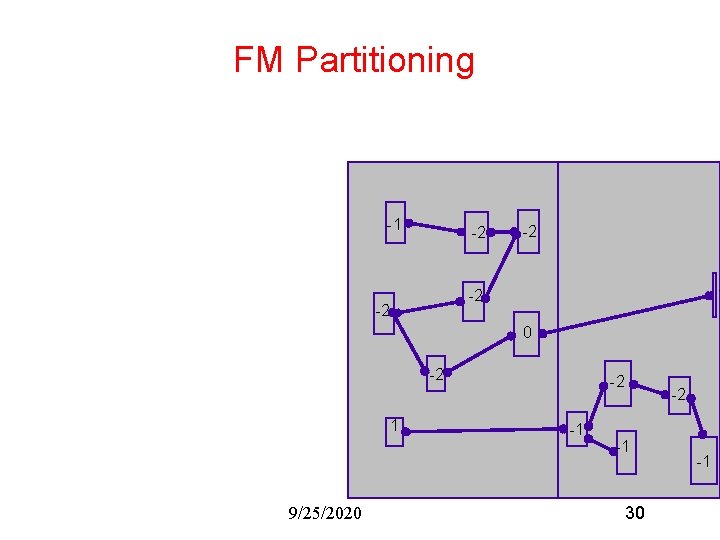

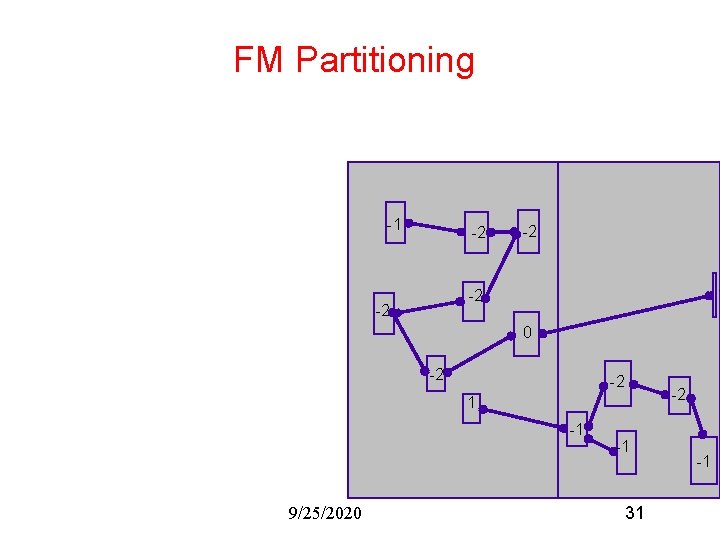

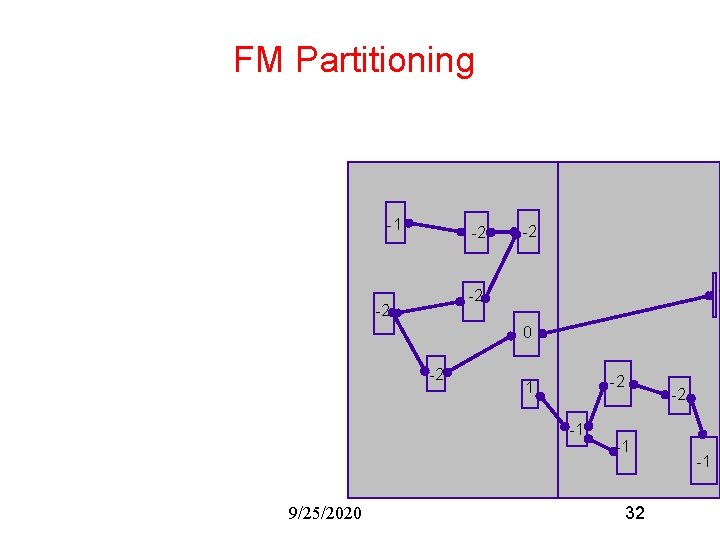

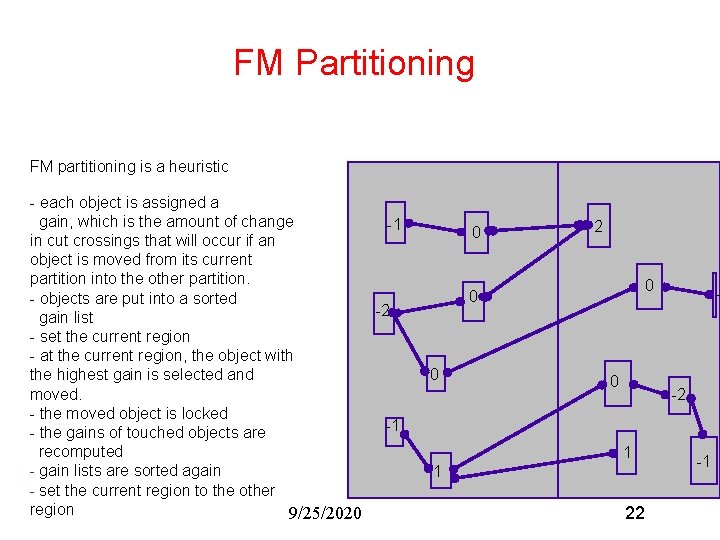

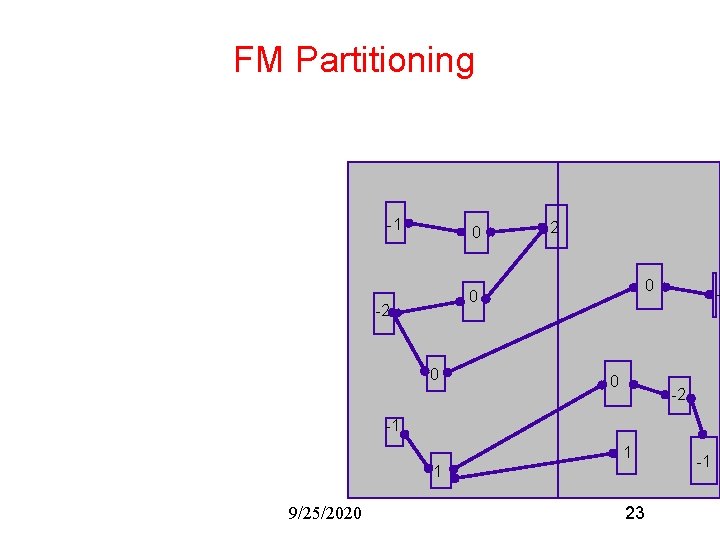

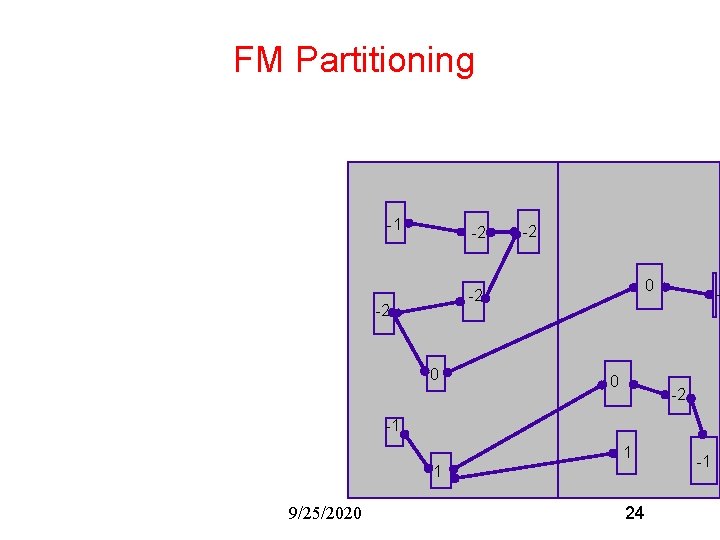

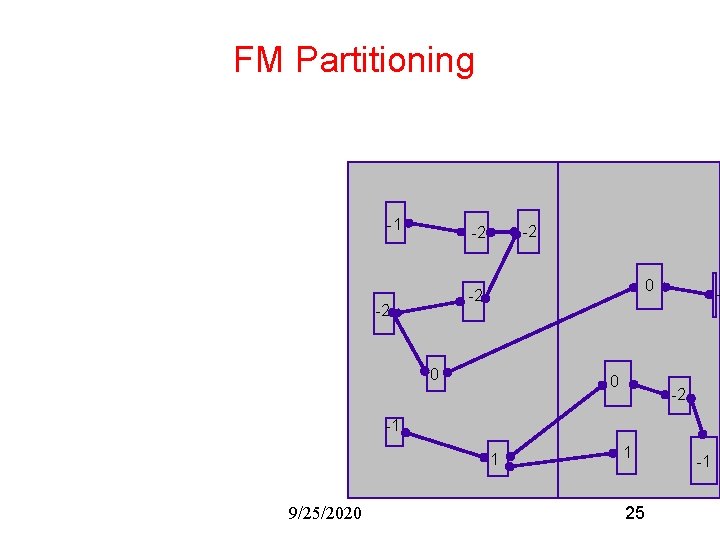

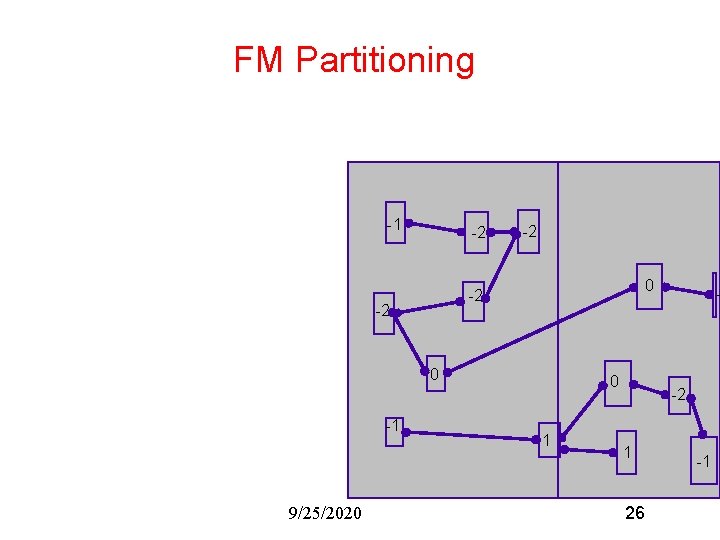

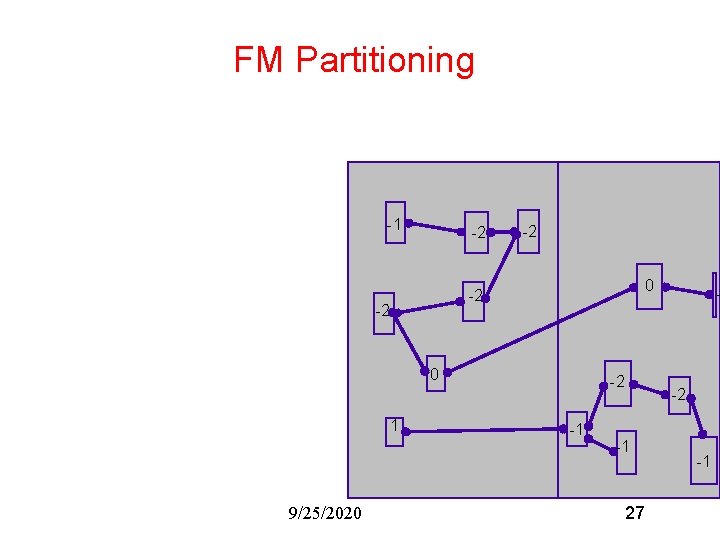

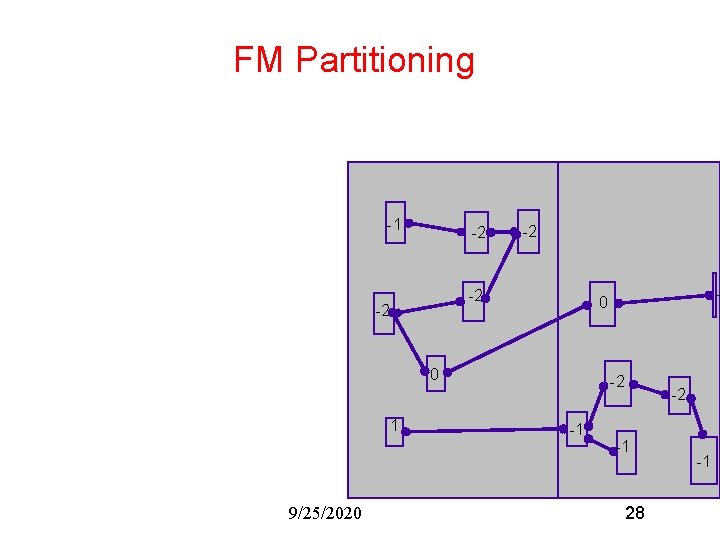

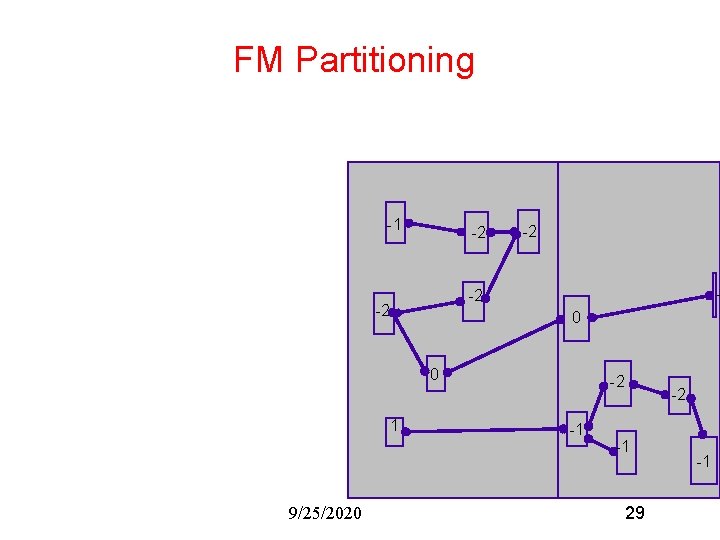

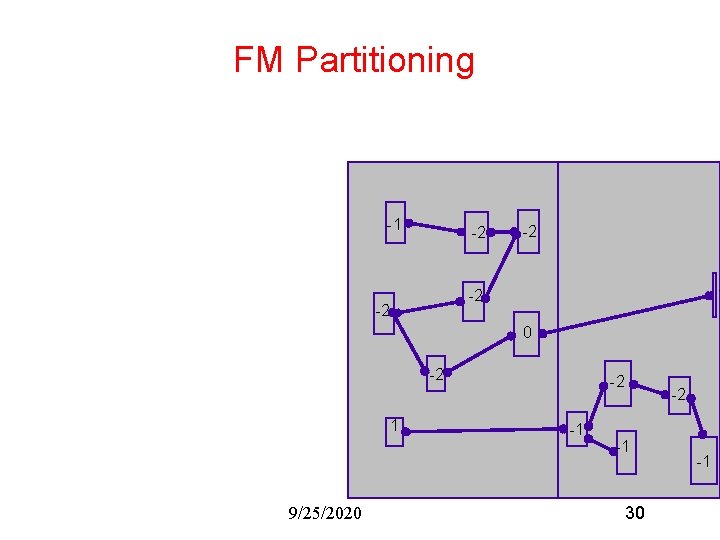

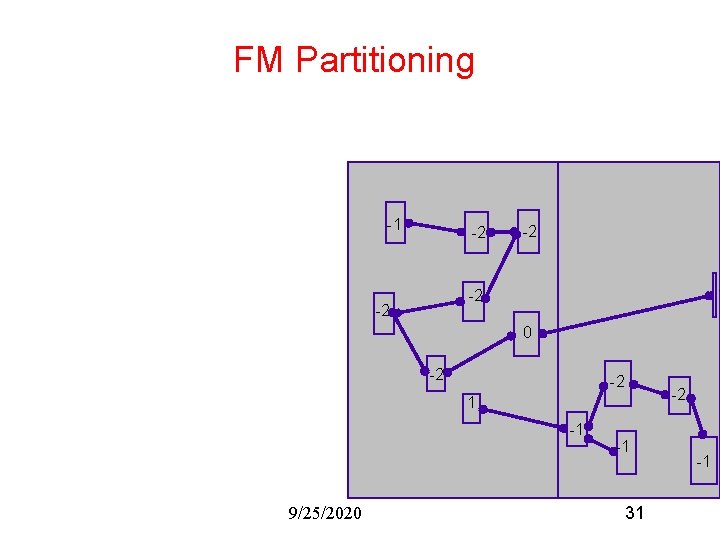

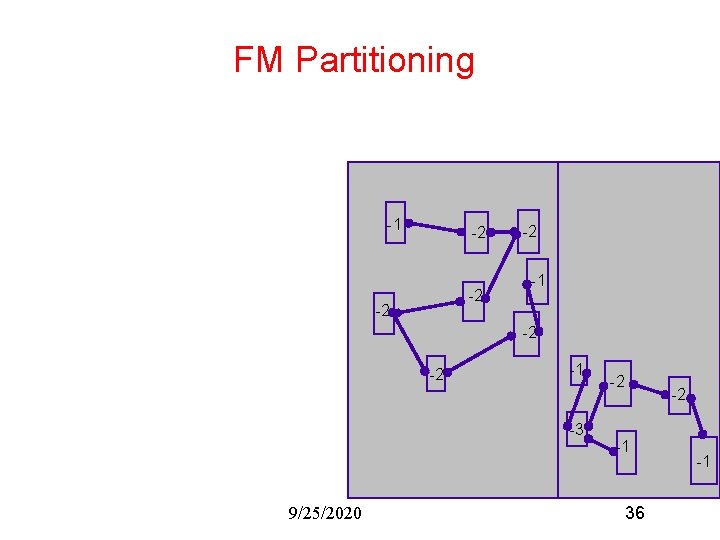

FM Partitioning FM partitioning is a heuristic - each object is assigned a gain, which is the amount of change -1 in cut crossings that will occur if an object is moved from its current partition into the other partition. - objects are put into a sorted -2 gain list - set the current region - at the current region, the object with the highest gain is selected and moved. - the moved object is locked -1 - the gains of touched objects are recomputed - gain lists are sorted again - set the current region to the other region 9/25/2020 0 2 0 0 - -2 1 1 22 -1

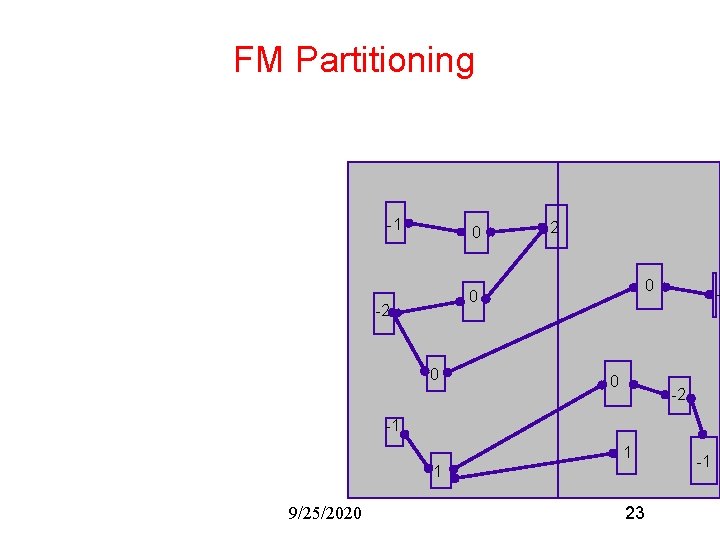

FM Partitioning -1 0 2 0 0 - -2 -1 1 1 9/25/2020 23 -1

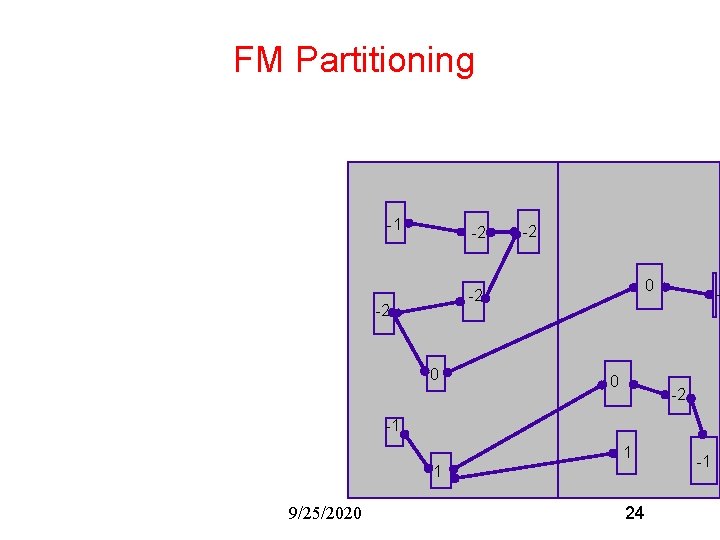

FM Partitioning -1 -2 -2 0 0 - -2 -1 1 1 9/25/2020 24 -1

FM Partitioning -1 -2 -2 0 0 - -2 -1 1 9/25/2020 1 25 -1

FM Partitioning -1 -2 -2 0 -1 9/25/2020 0 1 - -2 1 26 -1

FM Partitioning -1 -2 -2 0 1 9/25/2020 -2 -1 - -2 -1 27 -1

FM Partitioning -1 -2 -2 0 1 9/25/2020 - 0 -2 -1 28 -1

FM Partitioning -1 -2 -2 -2 0 0 1 9/25/2020 -2 -1 29 -1

FM Partitioning -1 -2 -2 0 -2 1 9/25/2020 -2 -1 30 -1

FM Partitioning -1 -2 -2 0 -2 -2 -2 1 -1 9/25/2020 -1 31 -1

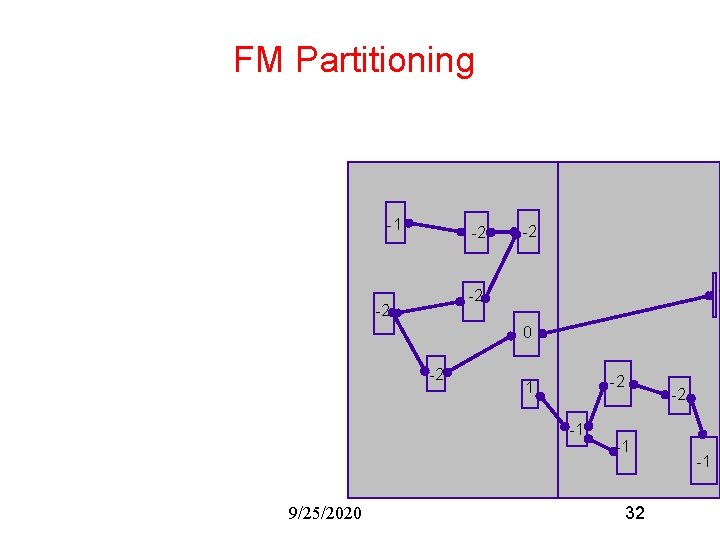

FM Partitioning -1 -2 -2 0 -2 -2 1 -1 9/25/2020 -2 -1 32 -1

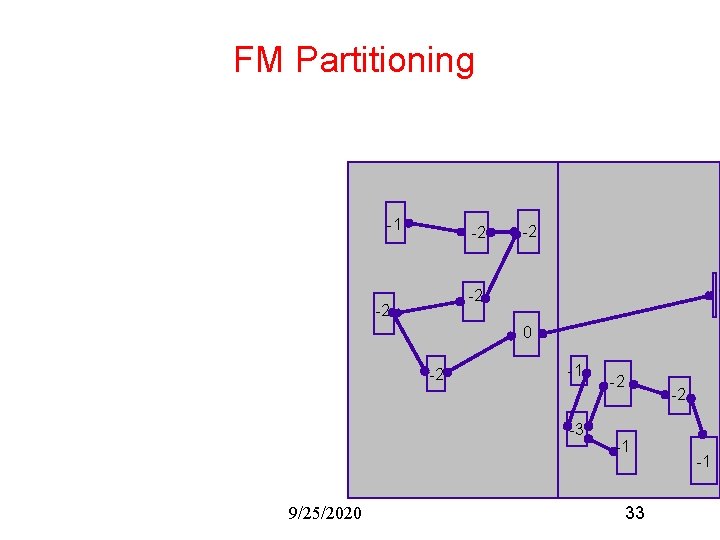

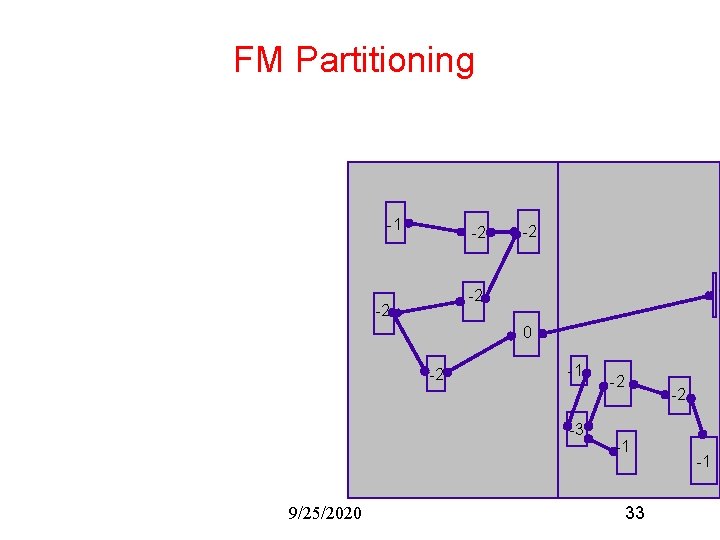

FM Partitioning -1 -2 -2 0 -2 -1 -3 9/25/2020 -2 -2 -1 33 -1

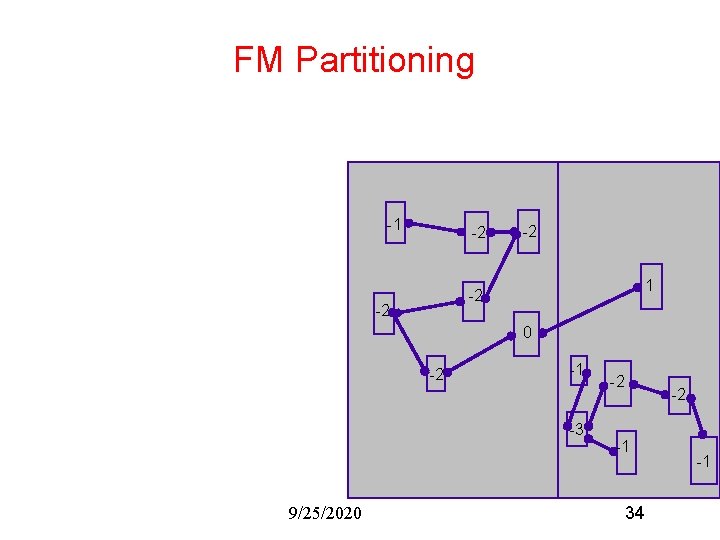

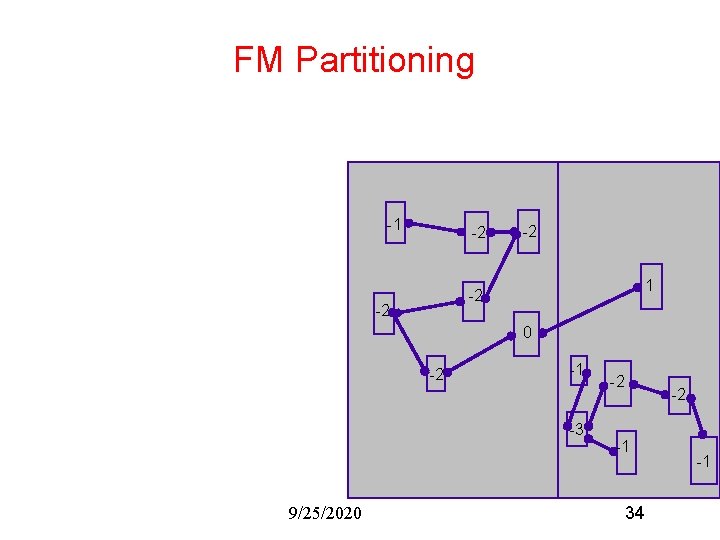

FM Partitioning -1 -2 -2 0 -2 -1 -3 9/25/2020 -2 -2 -1 34 -1

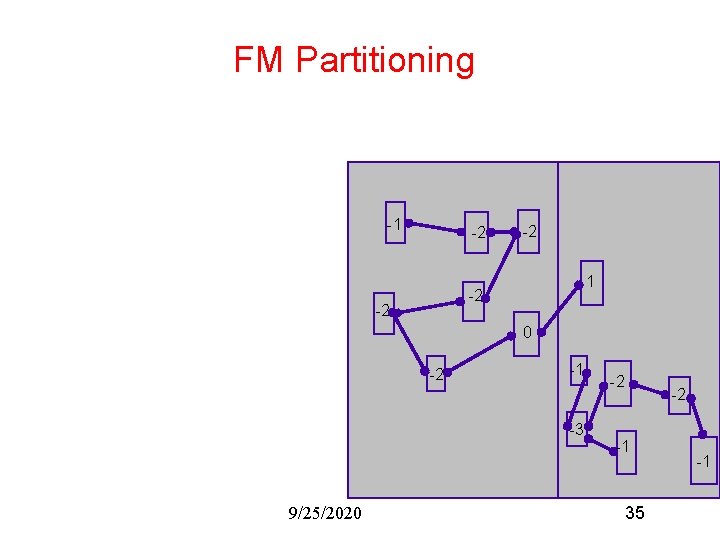

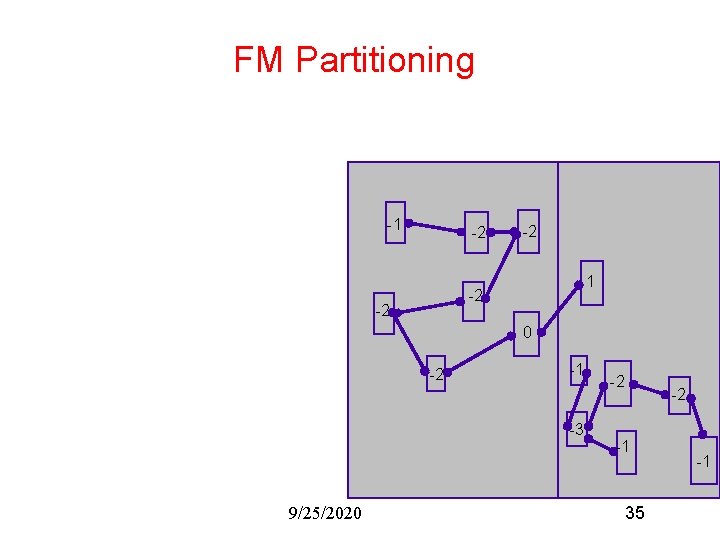

FM Partitioning -1 -2 -2 0 -2 -1 -3 9/25/2020 -2 -2 -1 35 -1

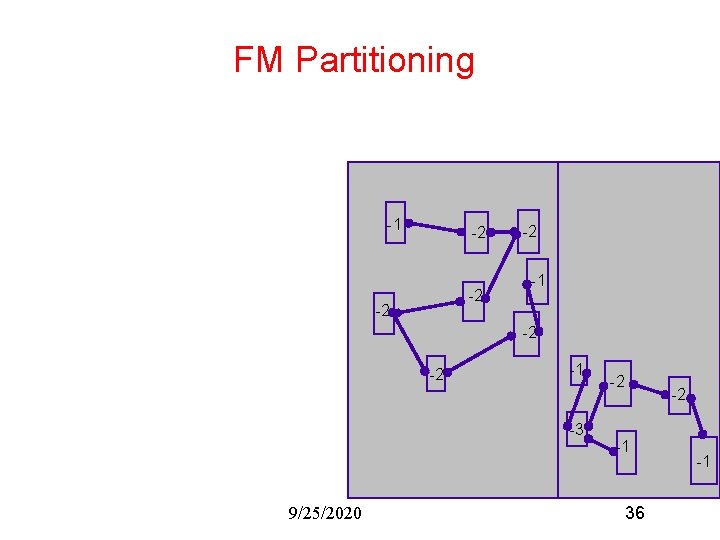

FM Partitioning -1 -2 -2 -1 -3 9/25/2020 -2 -2 -1 36 -1

Summary • Placement Problem – Minimize wirelength – Subject to the non-overlapping constraint • Placement Technique – General flow – Quadratic program based wirelength optimization – FM Partitioning (a) Placement with 1 region (b) Placement with 4 regions 9/25/2020 (c) Final placements 37