ETE 204 Digital Electronics NAND and NOR Circuits

- Slides: 30

ETE 204 – Digital Electronics NAND and NOR Circuits, Multi-level Logic Circuits, and Multiple-output Logic Circuits [Lecture: 8] Instructor: Sajib Roy Lecturer, ETE, ULAB

NAND and NOR Circuits Summer 2012 ETE 204 - Digital Electronics 2

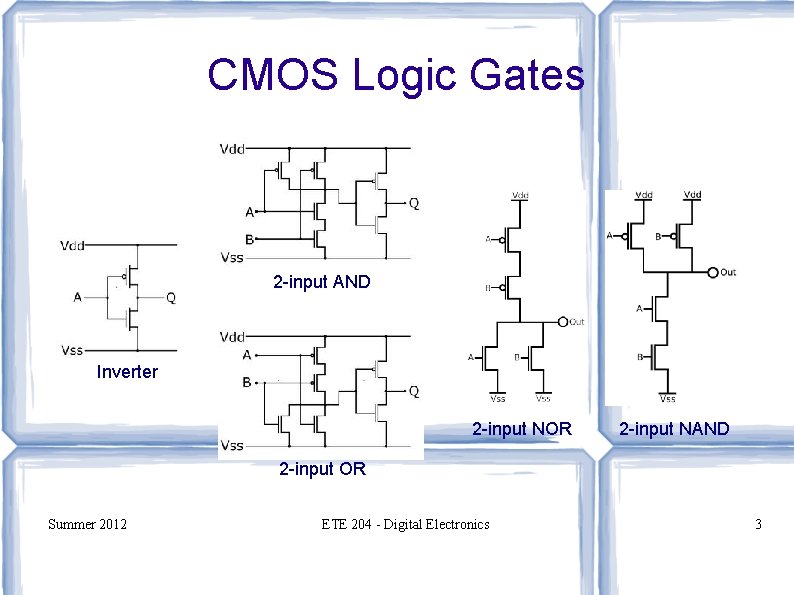

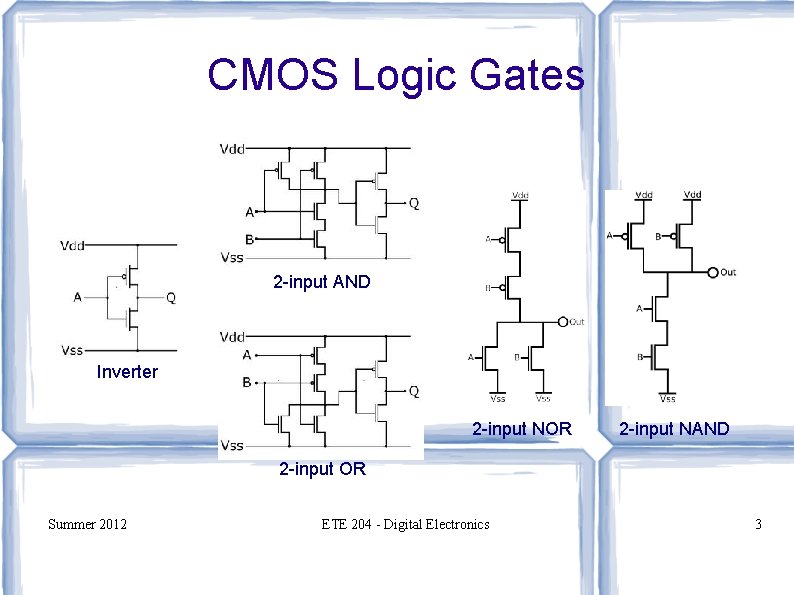

CMOS Logic Gates 2 -input AND Inverter 2 -input NOR 2 -input NAND 2 -input OR Summer 2012 ETE 204 - Digital Electronics 3

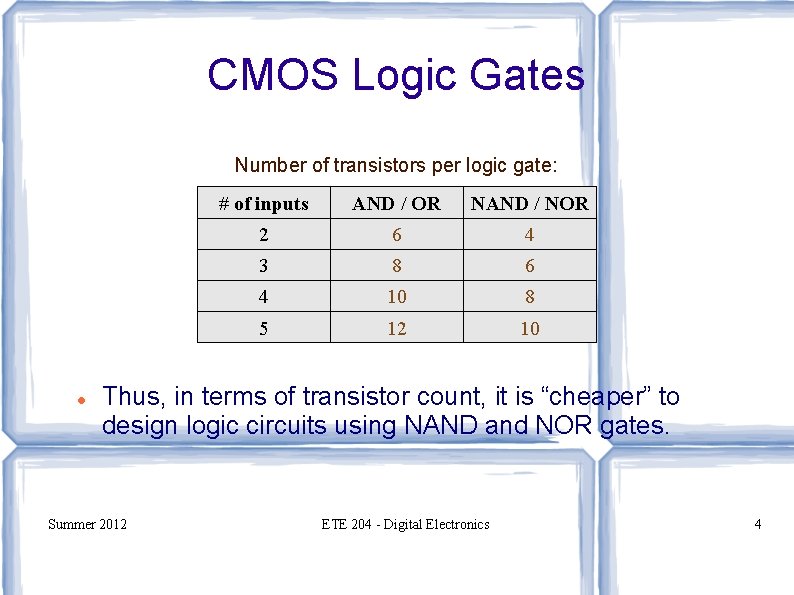

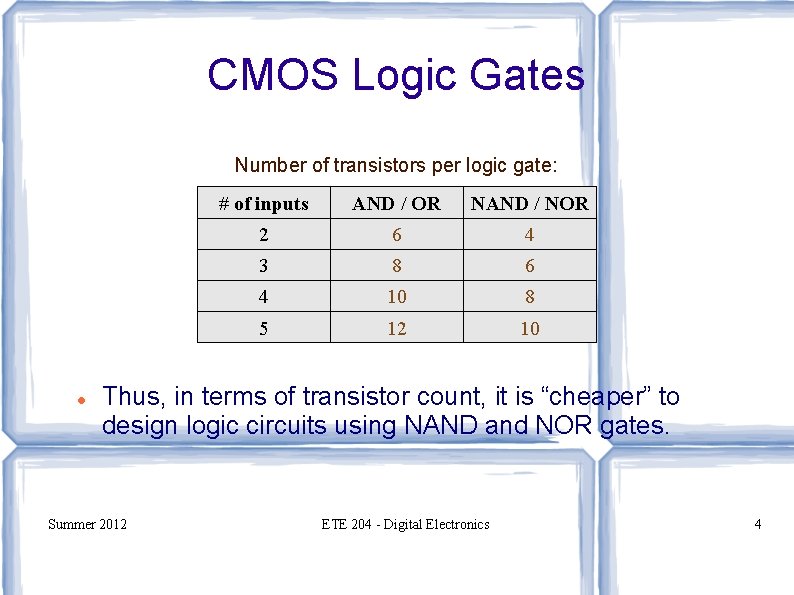

CMOS Logic Gates Number of transistors per logic gate: # of inputs AND / OR NAND / NOR 2 6 4 3 8 6 4 10 8 5 12 10 Thus, in terms of transistor count, it is “cheaper” to design logic circuits using NAND and NOR gates. Summer 2012 ETE 204 - Digital Electronics 4

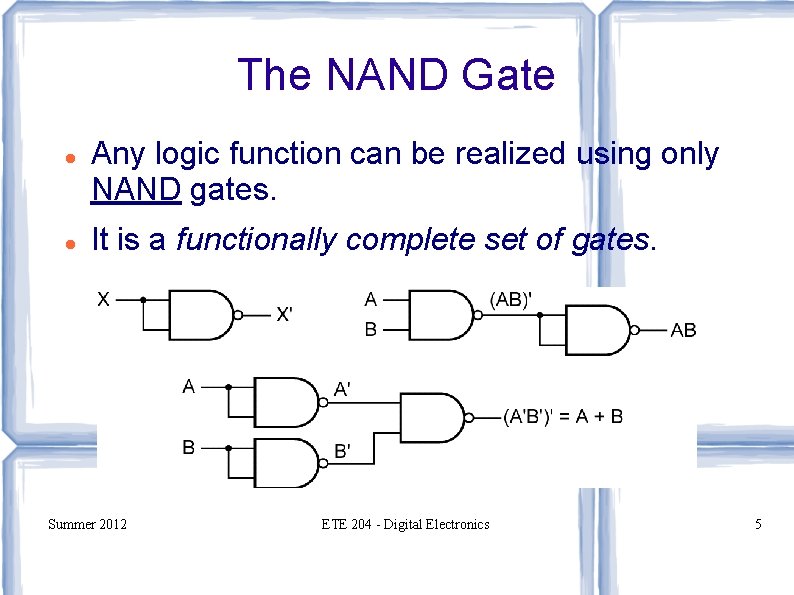

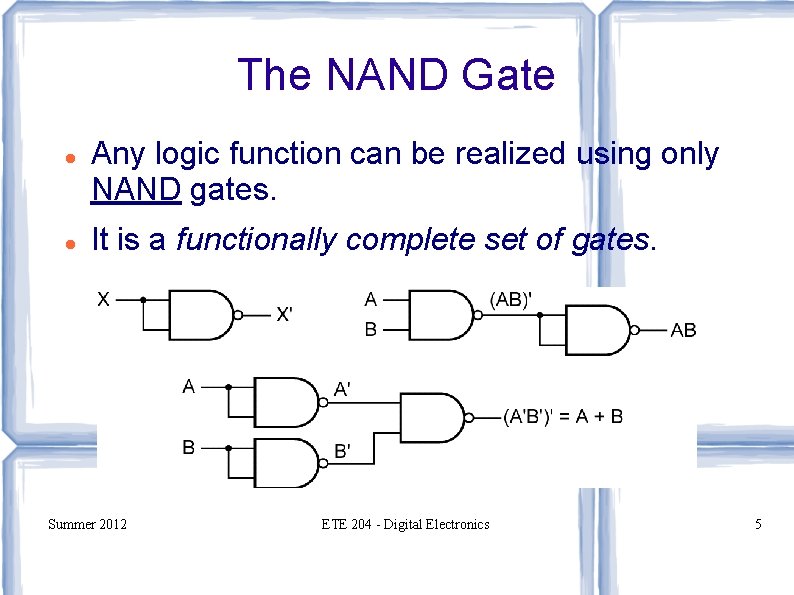

The NAND Gate Any logic function can be realized using only NAND gates. It is a functionally complete set of gates. Summer 2012 ETE 204 - Digital Electronics 5

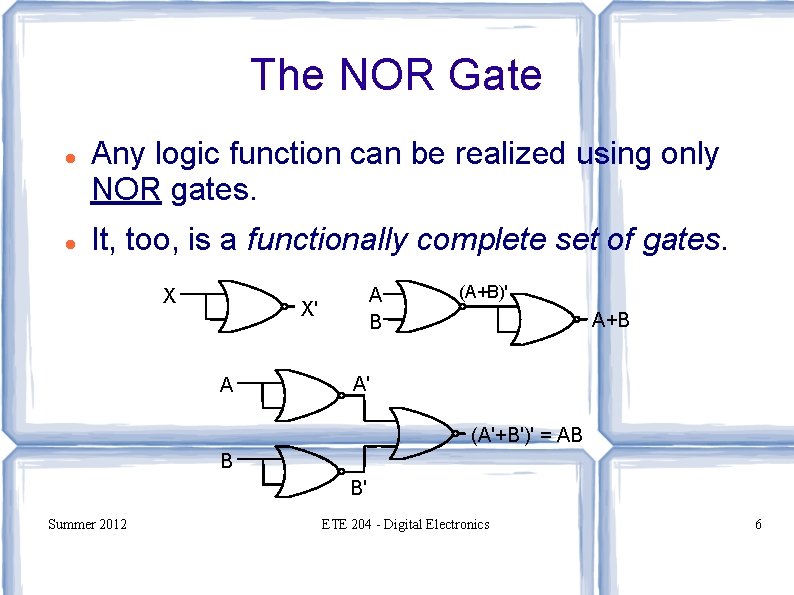

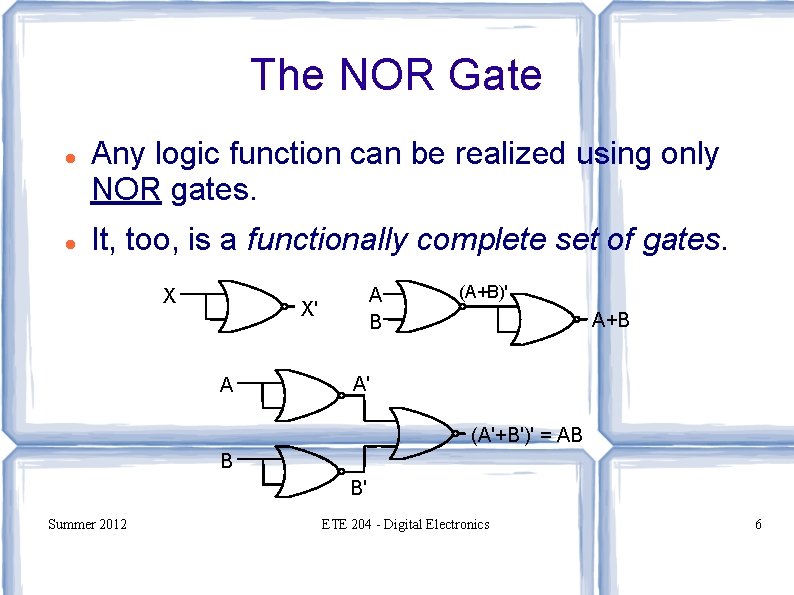

The NOR Gate Any logic function can be realized using only NOR gates. It, too, is a functionally complete set of gates. X A B X' A (A+B)' A+B A' (A'+B')' = AB B B' Summer 2012 ETE 204 - Digital Electronics 6

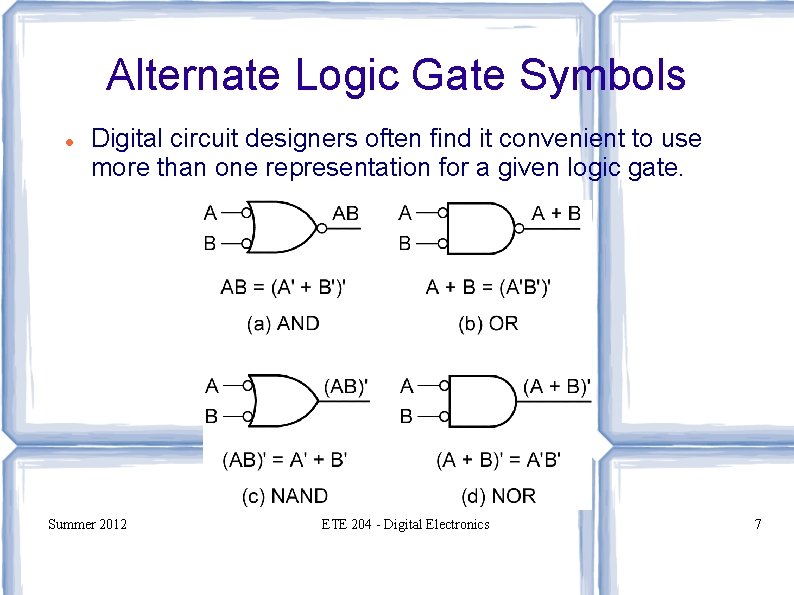

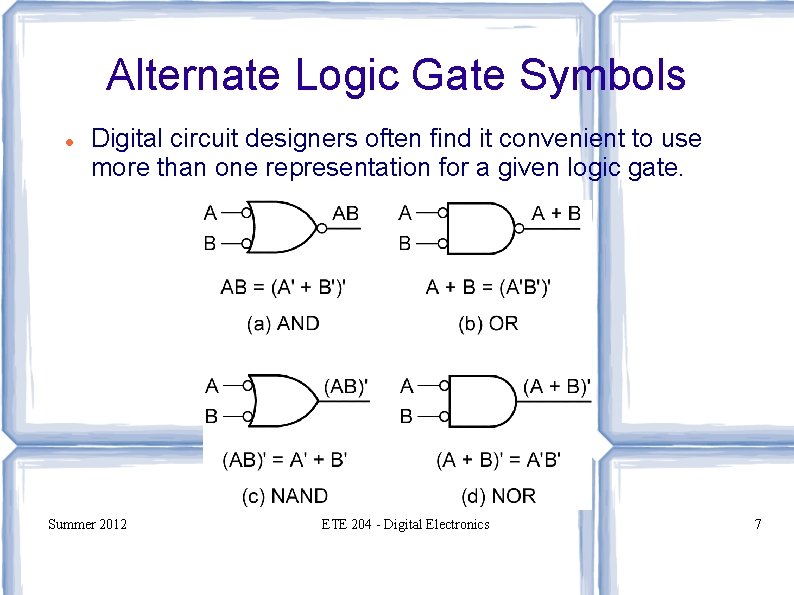

Alternate Logic Gate Symbols Digital circuit designers often find it convenient to use more than one representation for a given logic gate. Summer 2012 ETE 204 - Digital Electronics 7

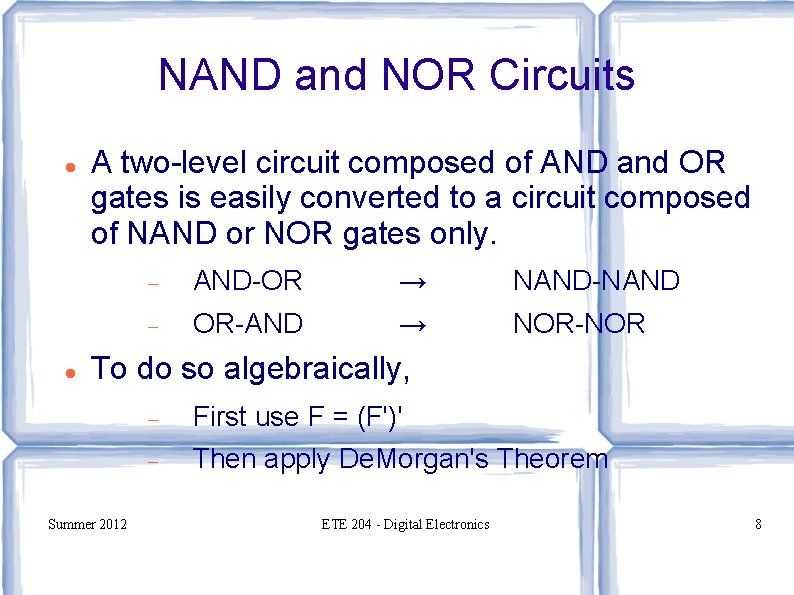

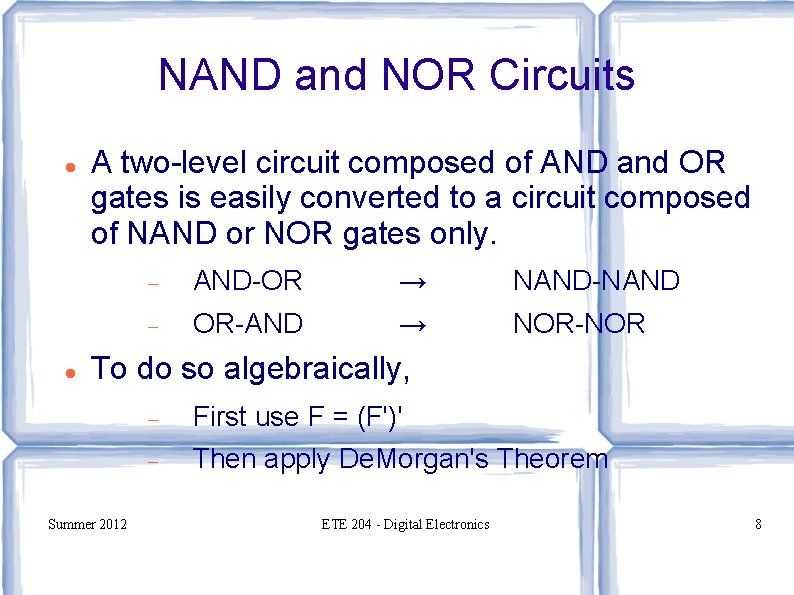

NAND and NOR Circuits A two-level circuit composed of AND and OR gates is easily converted to a circuit composed of NAND or NOR gates only. AND-OR → NAND-NAND OR-AND → NOR-NOR To do so algebraically, Summer 2012 First use F = (F')' Then apply De. Morgan's Theorem ETE 204 - Digital Electronics 8

NAND Circuit: Example Convert the following SOP expression from the AND-OR form to the NAND-NAND form: F(A, B, C) = A. B' + A'. C' + B. C Summer 2012 ETE 204 - Digital Electronics 9

NOR Circuit: Example Convert the following POS expression from the OR-AND form to the NOR-NOR form: F(A, B, C) = (A'+B'). (A'+C). (B+C') Summer 2012 ETE 204 - Digital Electronics 10

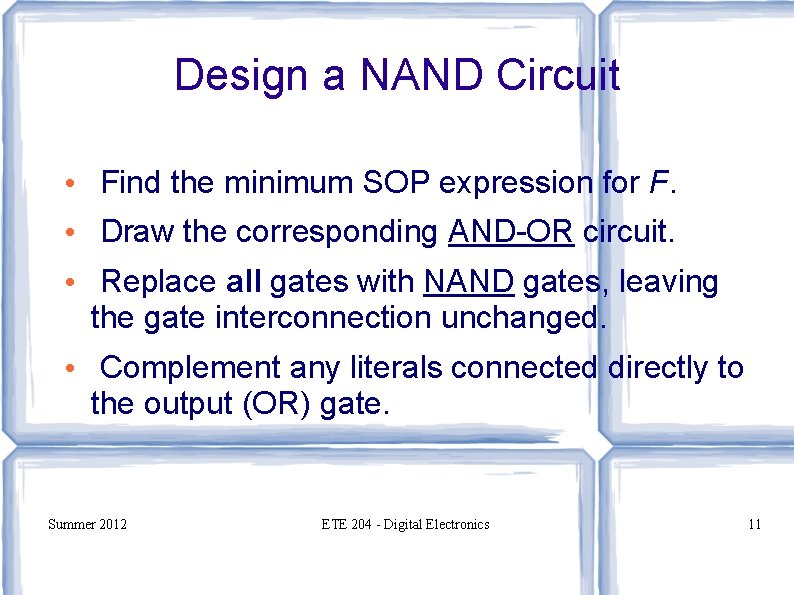

Design a NAND Circuit • Find the minimum SOP expression for F. • Draw the corresponding AND-OR circuit. • Replace all gates with NAND gates, leaving the gate interconnection unchanged. • Complement any literals connected directly to the output (OR) gate. Summer 2012 ETE 204 - Digital Electronics 11

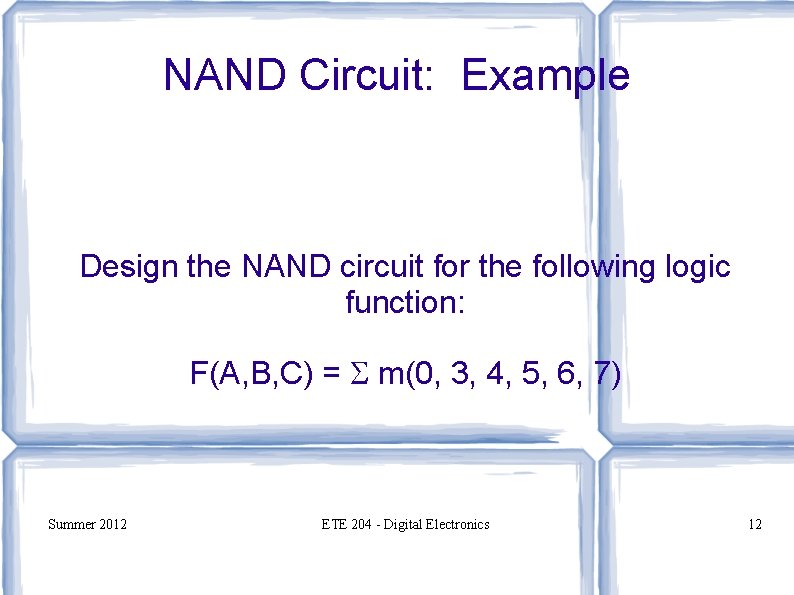

NAND Circuit: Example Design the NAND circuit for the following logic function: F(A, B, C) = S m(0, 3, 4, 5, 6, 7) Summer 2012 ETE 204 - Digital Electronics 12

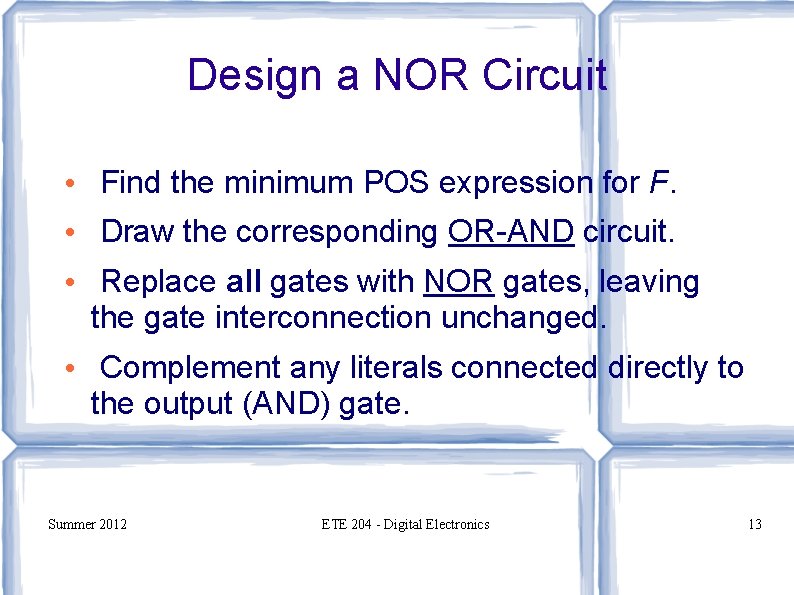

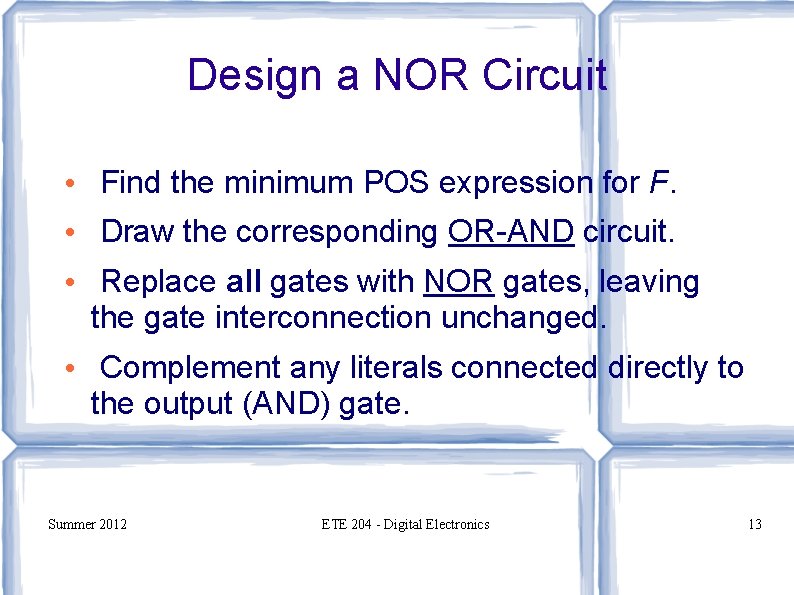

Design a NOR Circuit • Find the minimum POS expression for F. • Draw the corresponding OR-AND circuit. • Replace all gates with NOR gates, leaving the gate interconnection unchanged. • Complement any literals connected directly to the output (AND) gate. Summer 2012 ETE 204 - Digital Electronics 13

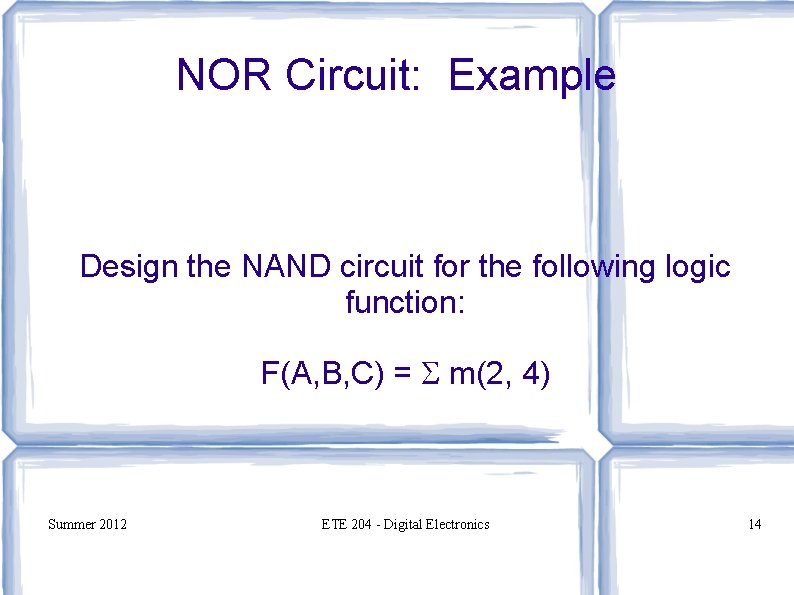

NOR Circuit: Example Design the NAND circuit for the following logic function: F(A, B, C) = S m(2, 4) Summer 2012 ETE 204 - Digital Electronics 14

Multi-level Logic Circuits Summer 2012 ETE 204 - Digital Electronics 15

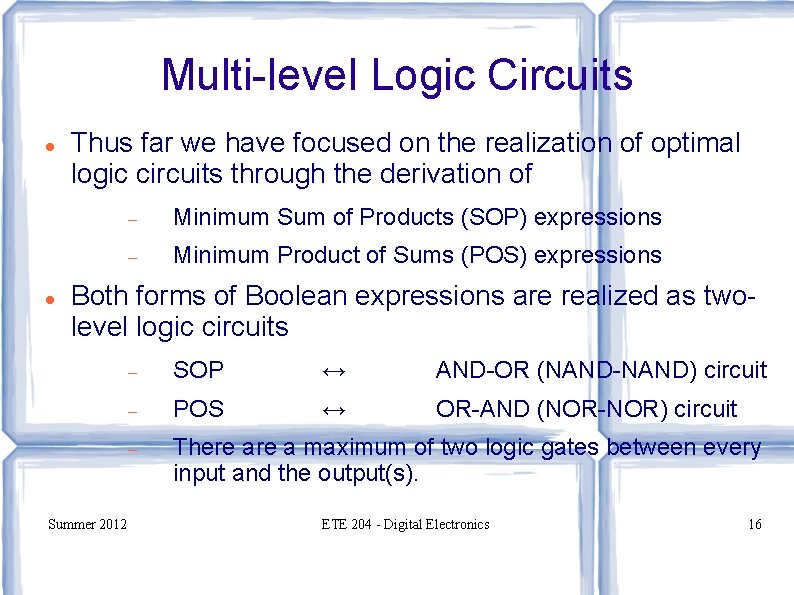

Multi-level Logic Circuits Thus far we have focused on the realization of optimal logic circuits through the derivation of Minimum Sum of Products (SOP) expressions Minimum Product of Sums (POS) expressions Both forms of Boolean expressions are realized as twolevel logic circuits Summer 2012 SOP ↔ AND-OR (NAND-NAND) circuit POS ↔ OR-AND (NOR-NOR) circuit There a maximum of two logic gates between every input and the output(s). ETE 204 - Digital Electronics 16

Multi-level Logic Circuits A two-level logic circuit is usually efficient for Boolean expressions of a few variables (i. e. inputs). However, as the number of inputs increases, a twolevel logic circuit may encounter fan-in problems. Fan-in refers to the number of inputs to a logic gate Whether fan-in is an issue is dependent upon the technology used to implement the logic circuit. Summer 2012 Standard TTL and CMOS chips Complex Programmable Logic Device (CPLD) Field Programmable Gate Array (FPGA) ETE 204 - Digital Electronics 17

Multi-level Logic Circuits A multi-level logic circuit may require fewer logic gates than the logically equivalent two-level logic circuit. Reduced (silicon) area Decreased cost It may require less complex wiring between logic gates Fewer literals results in fewer interconnecting wires It will have a greater propagation delay than the logically equivalent two-level logic circuit. Summer 2012 Each additional level adds to the propagation delay Decreased speed ETE 204 - Digital Electronics 18

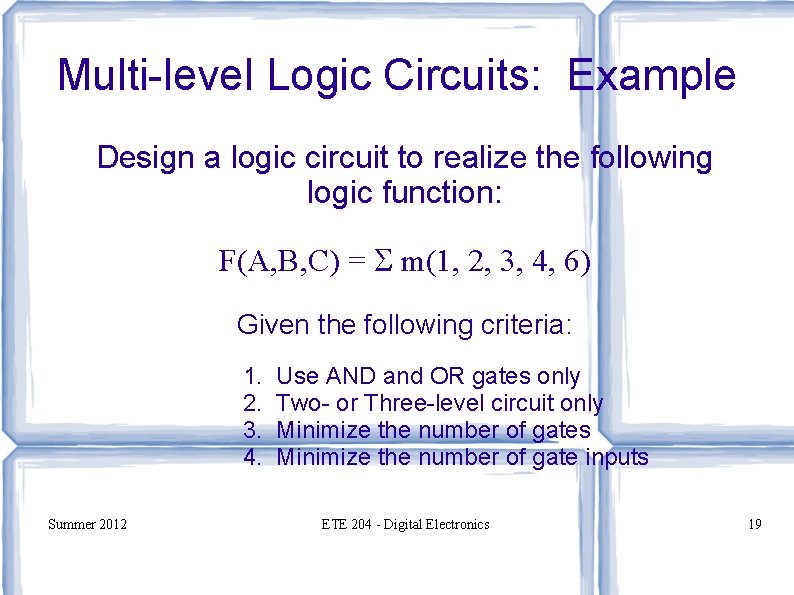

Multi-level Logic Circuits: Example Design a logic circuit to realize the following logic function: F(A, B, C) = S m(1, 2, 3, 4, 6) Given the following criteria: 1. 2. 3. 4. Summer 2012 Use AND and OR gates only Two- or Three-level circuit only Minimize the number of gates Minimize the number of gate inputs ETE 204 - Digital Electronics 19

Multi-level Logic Circuits: Example Which design would be possible if the following additional criteria was imposed: 5. Two-input logic gates only Summer 2012 ETE 204 - Digital Electronics 20

Multi-level Logic Circuits using NAND and NOR gates Summer 2012 ETE 204 - Digital Electronics 21

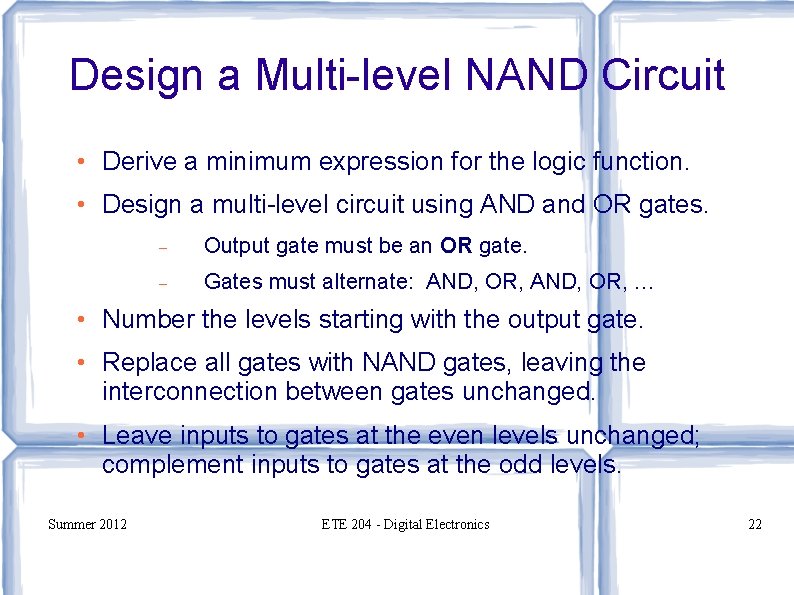

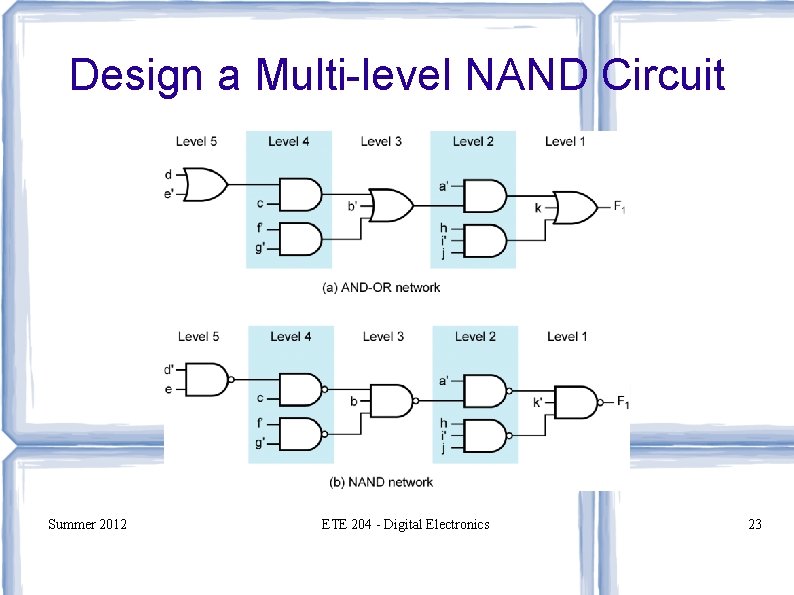

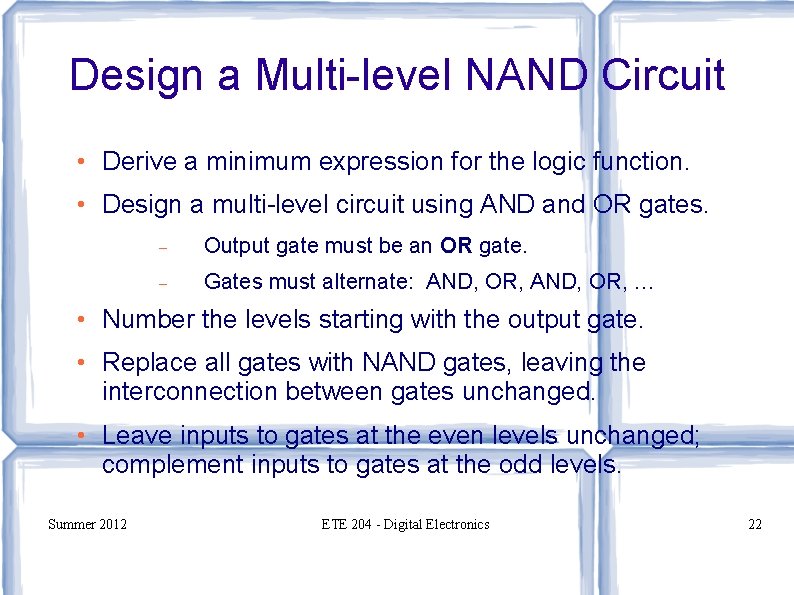

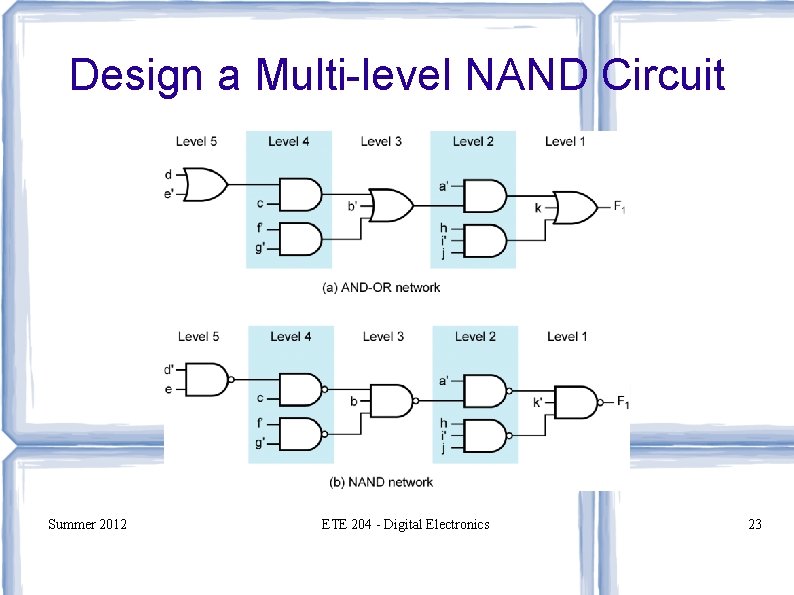

Design a Multi-level NAND Circuit • Derive a minimum expression for the logic function. • Design a multi-level circuit using AND and OR gates. Output gate must be an OR gate. Gates must alternate: AND, OR, … • Number the levels starting with the output gate. • Replace all gates with NAND gates, leaving the interconnection between gates unchanged. • Leave inputs to gates at the even levels unchanged; complement inputs to gates at the odd levels. Summer 2012 ETE 204 - Digital Electronics 22

Design a Multi-level NAND Circuit Summer 2012 ETE 204 - Digital Electronics 23

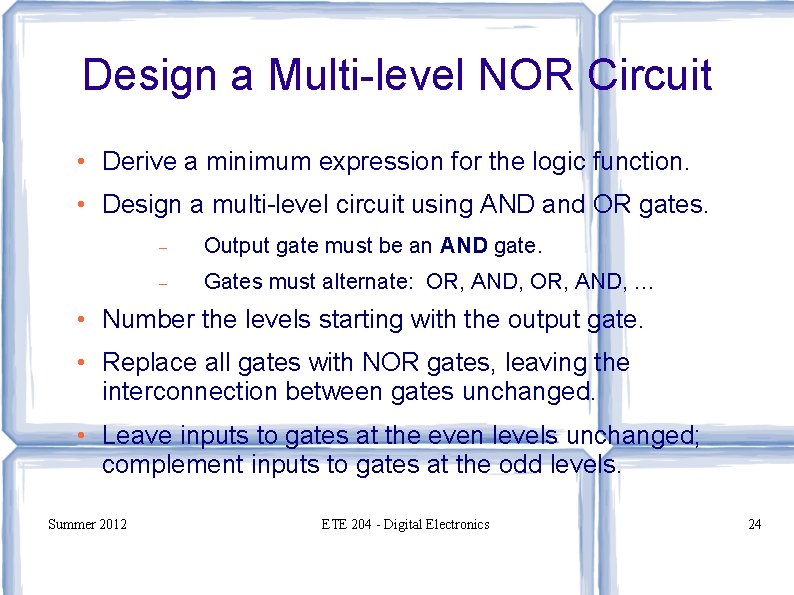

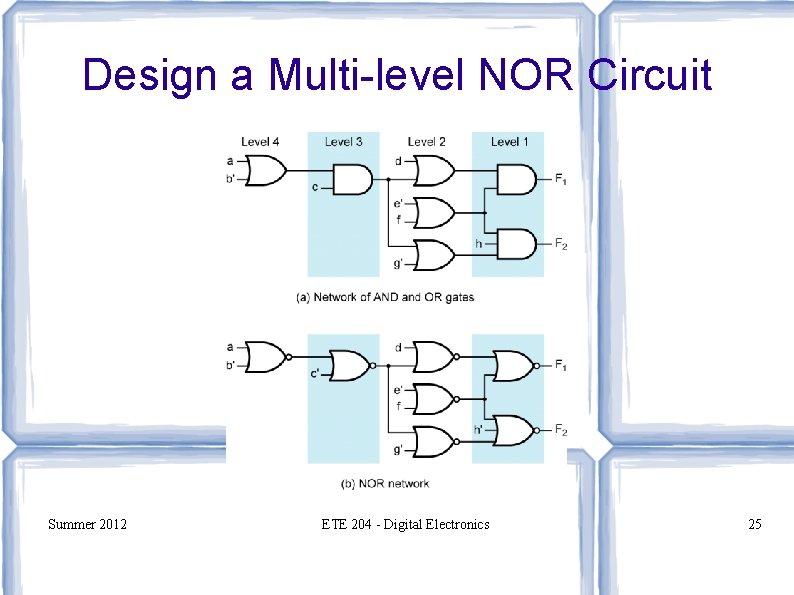

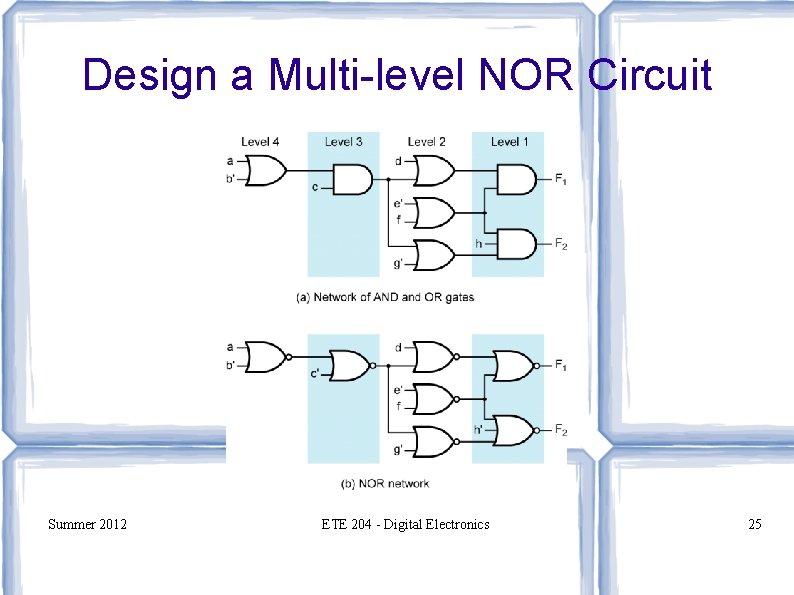

Design a Multi-level NOR Circuit • Derive a minimum expression for the logic function. • Design a multi-level circuit using AND and OR gates. Output gate must be an AND gate. Gates must alternate: OR, AND, … • Number the levels starting with the output gate. • Replace all gates with NOR gates, leaving the interconnection between gates unchanged. • Leave inputs to gates at the even levels unchanged; complement inputs to gates at the odd levels. Summer 2012 ETE 204 - Digital Electronics 24

Design a Multi-level NOR Circuit Summer 2012 ETE 204 - Digital Electronics 25

Multiple-output Logic Circuits Summer 2012 ETE 204 - Digital Electronics 26

Multiple-output Logic Circuits Thus far, we have focused on designing logic circuits to realize a single logic function. A logic circuit with a single output. However, many logic circuits have multiple outputs. Summer 2012 Corresponding to multiple logic functions of the same input variables. ETE 204 - Digital Electronics 27

Multiple-output Logic Circuits An optimal logic circuit may not be realized by simply minimizing each of the logic functions independently. Rather, it may be necessary to consider which terms (i. e. logic gates), if any, are common to the logic functions to be realized. Summer 2012 Share those logic gates that are in common. ETE 204 - Digital Electronics 28

Multiple-output Circuits: Example Design an optimal logic circuit to realize the following logic functions: F(A, B, C) = S m(0, 4, 5) G(A, B, C) = S m(0, 2, 6) Cost = # of logic gates + # of gate inputs Summer 2012 ETE 204 - Digital Electronics 29

Questions? Summer 2012 ETE 204 - Digital Electronics 30