Arithmetic Building Blocks Digital Integrated Circuits Arithmetic Prentice

Arithmetic Building Blocks Digital Integrated Circuits Arithmetic © Prentice Hall 1995

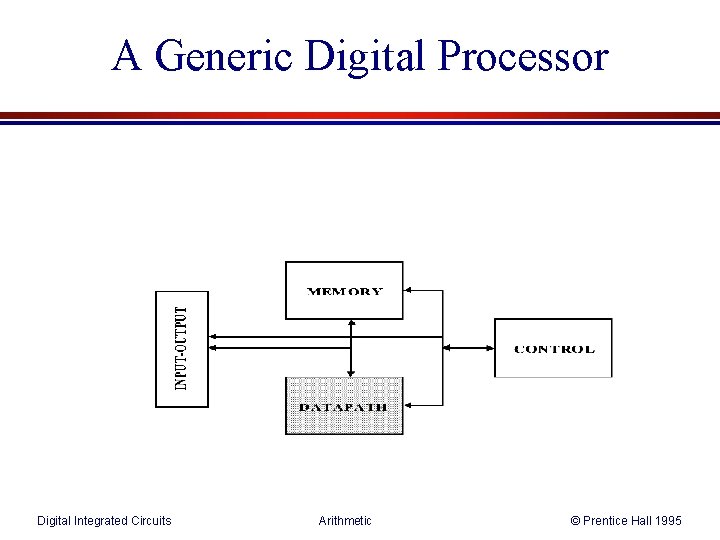

A Generic Digital Processor Digital Integrated Circuits Arithmetic © Prentice Hall 1995

Building Blocks for Digital Architectures Arithmetic unit - Bit-sliced datapath (adder , multiplier, shifter, comparator, etc. ) Memory - RAM, ROM, Buffers, Shift registers Control - Finite state machine (PLA, random logic. ) - Counters Interconnect - Switches - Arbiters - Bus Digital Integrated Circuits Arithmetic © Prentice Hall 1995

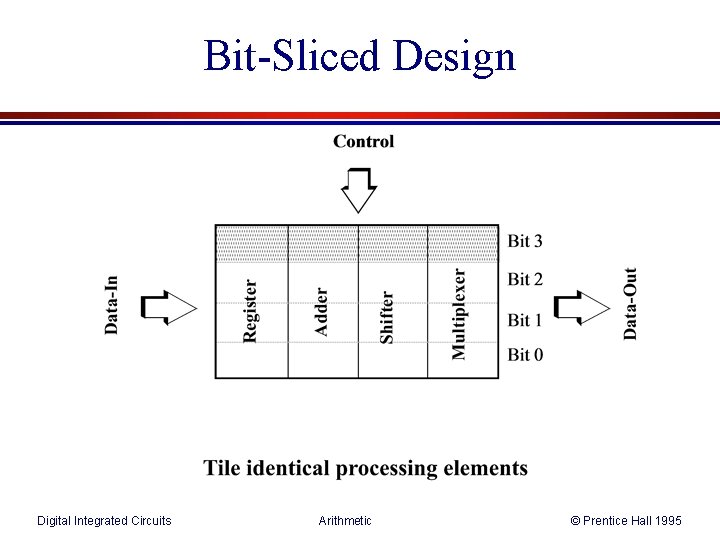

Bit-Sliced Design Digital Integrated Circuits Arithmetic © Prentice Hall 1995

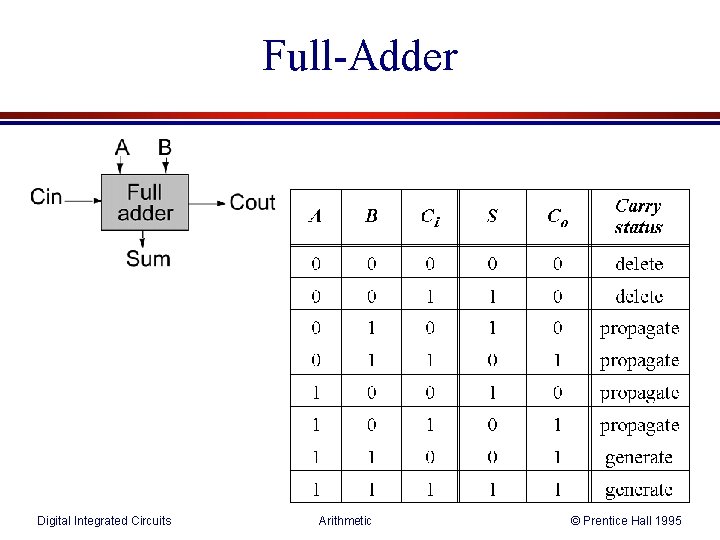

Full-Adder Digital Integrated Circuits Arithmetic © Prentice Hall 1995

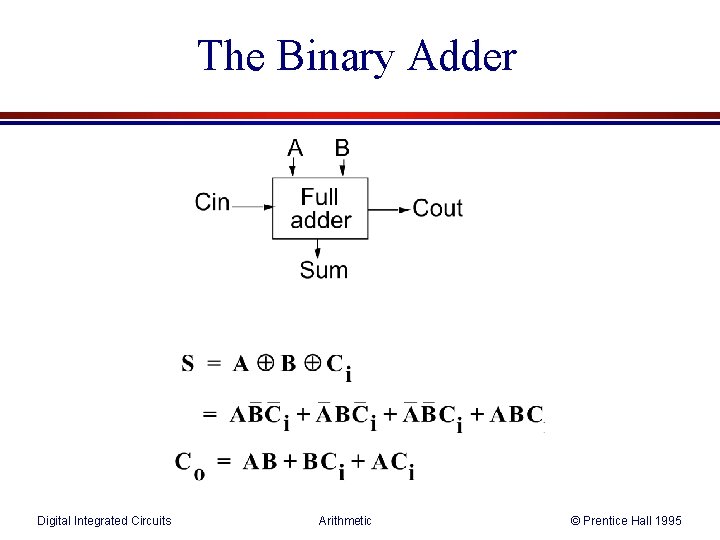

The Binary Adder Digital Integrated Circuits Arithmetic © Prentice Hall 1995

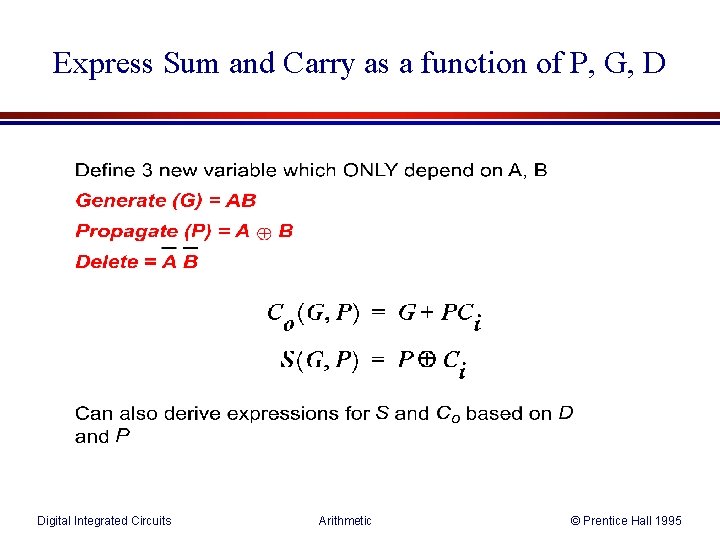

Express Sum and Carry as a function of P, G, D Digital Integrated Circuits Arithmetic © Prentice Hall 1995

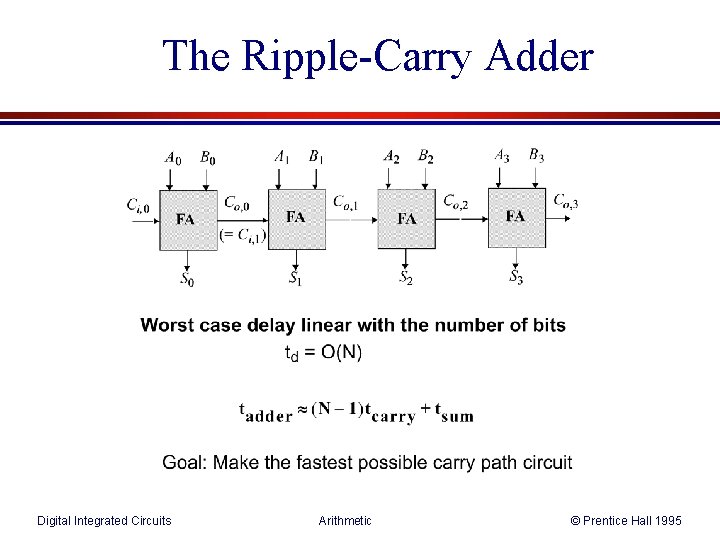

The Ripple-Carry Adder Digital Integrated Circuits Arithmetic © Prentice Hall 1995

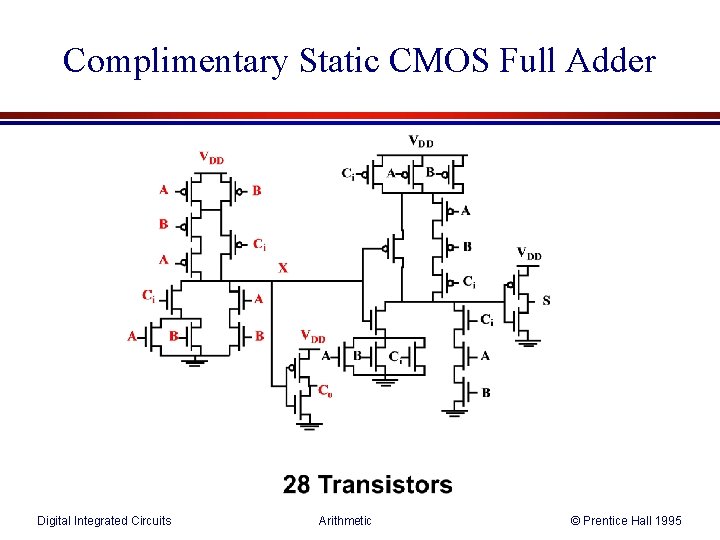

Complimentary Static CMOS Full Adder Digital Integrated Circuits Arithmetic © Prentice Hall 1995

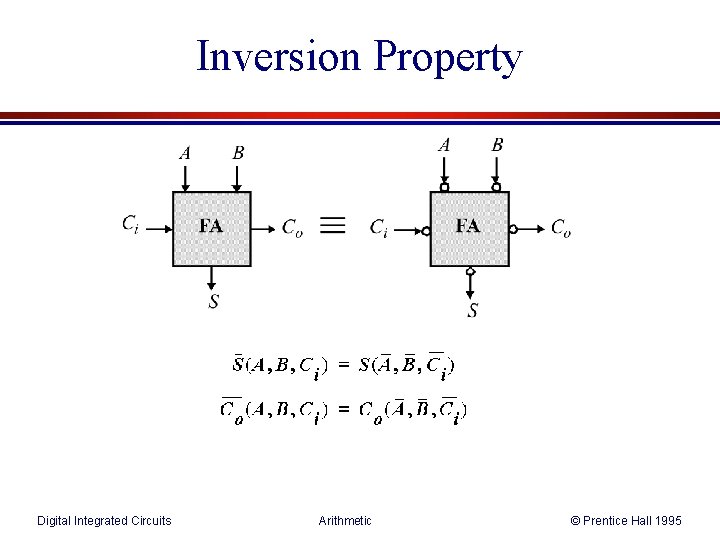

Inversion Property Digital Integrated Circuits Arithmetic © Prentice Hall 1995

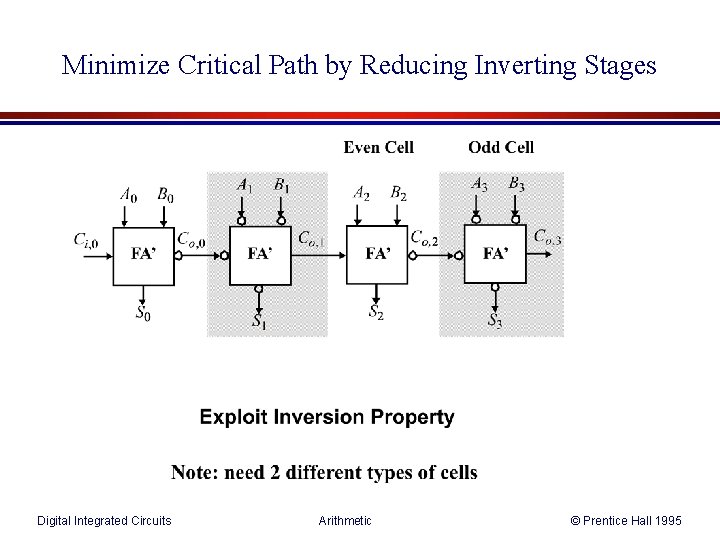

Minimize Critical Path by Reducing Inverting Stages Digital Integrated Circuits Arithmetic © Prentice Hall 1995

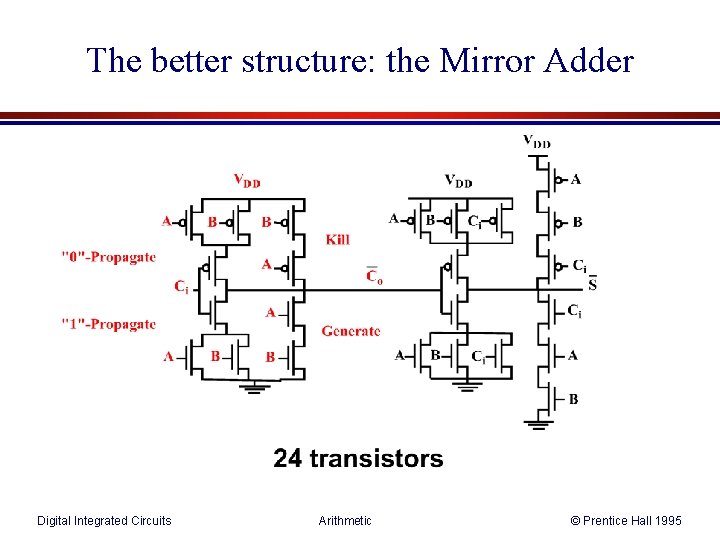

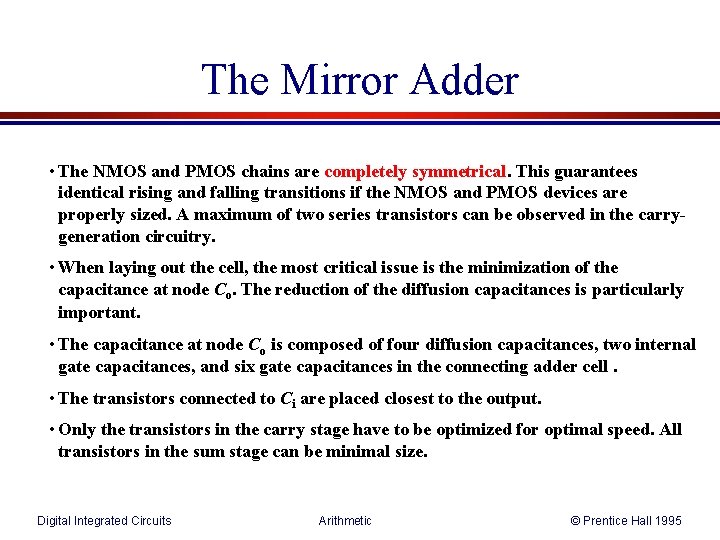

The better structure: the Mirror Adder Digital Integrated Circuits Arithmetic © Prentice Hall 1995

The Mirror Adder • The NMOS and PMOS chains are completely symmetrical. This guarantees identical rising and falling transitions if the NMOS and PMOS devices are properly sized. A maximum of two series transistors can be observed in the carrygeneration circuitry. • When laying out the cell, the most critical issue is the minimization of the capacitance at node Co. The reduction of the diffusion capacitances is particularly important. • The capacitance at node Co is composed of four diffusion capacitances, two internal gate capacitances, and six gate capacitances in the connecting adder cell. • The transistors connected to Ci are placed closest to the output. • Only the transistors in the carry stage have to be optimized for optimal speed. All transistors in the sum stage can be minimal size. Digital Integrated Circuits Arithmetic © Prentice Hall 1995

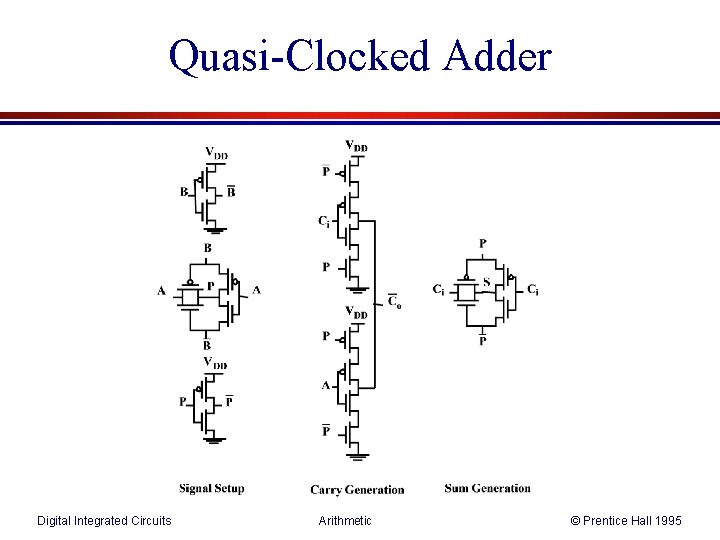

Quasi-Clocked Adder Digital Integrated Circuits Arithmetic © Prentice Hall 1995

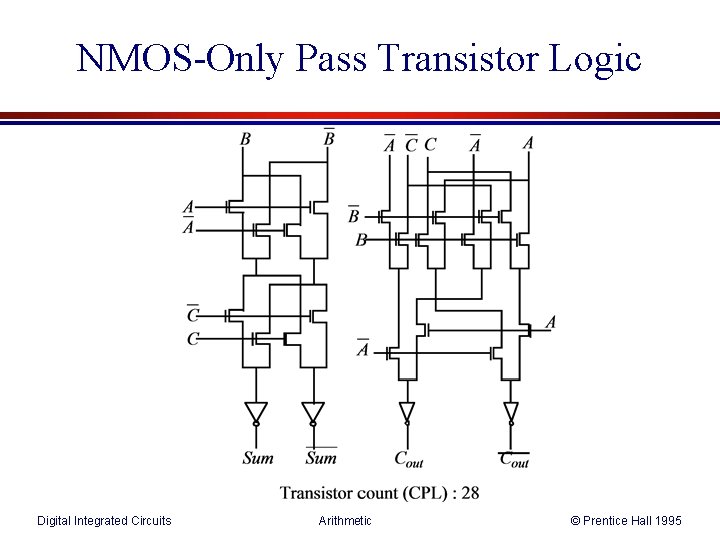

NMOS-Only Pass Transistor Logic Digital Integrated Circuits Arithmetic © Prentice Hall 1995

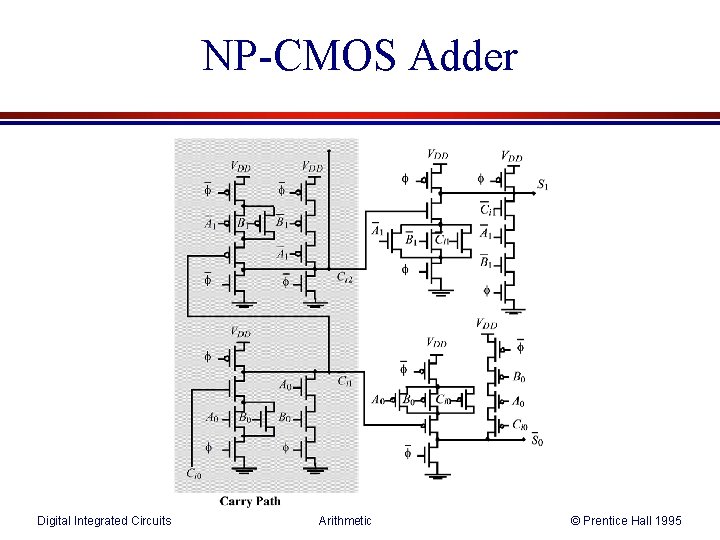

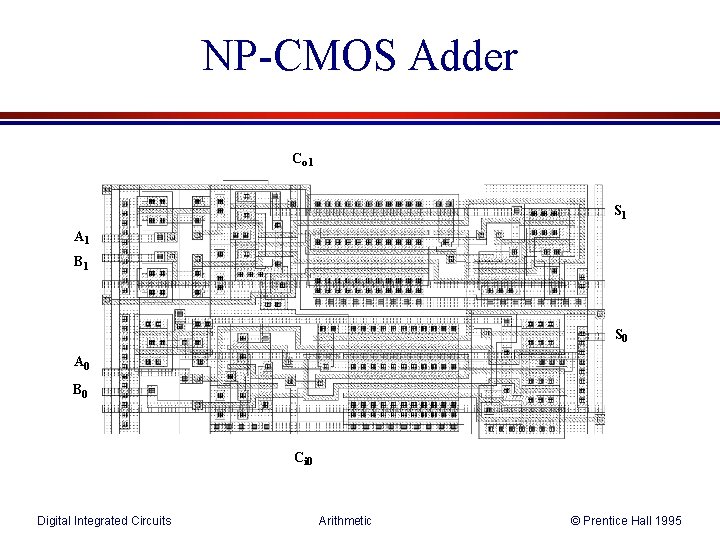

NP-CMOS Adder Digital Integrated Circuits Arithmetic © Prentice Hall 1995

NP-CMOS Adder Co 1 S 1 A 1 B 1 S 0 A 0 B 0 Ci 0 Digital Integrated Circuits Arithmetic © Prentice Hall 1995

Manchester Carry Chain Digital Integrated Circuits Arithmetic © Prentice Hall 1995

Sizing Manchester Carry Chain Digital Integrated Circuits Arithmetic © Prentice Hall 1995

Carry-Bypass Adder Digital Integrated Circuits Arithmetic © Prentice Hall 1995

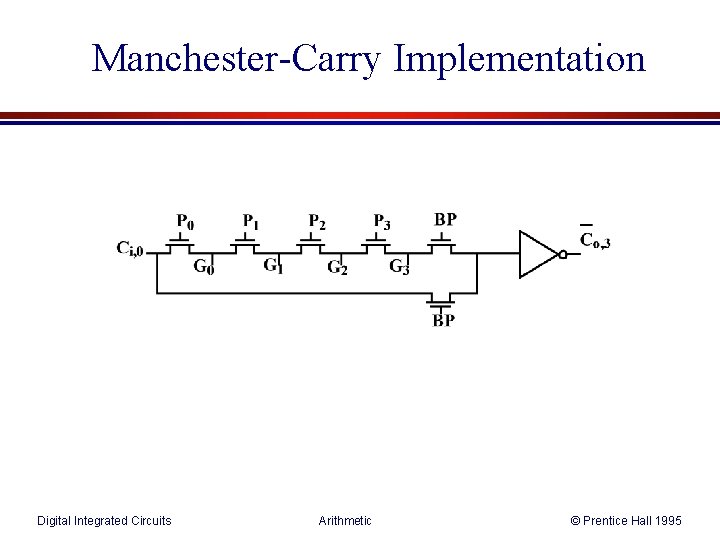

Manchester-Carry Implementation Digital Integrated Circuits Arithmetic © Prentice Hall 1995

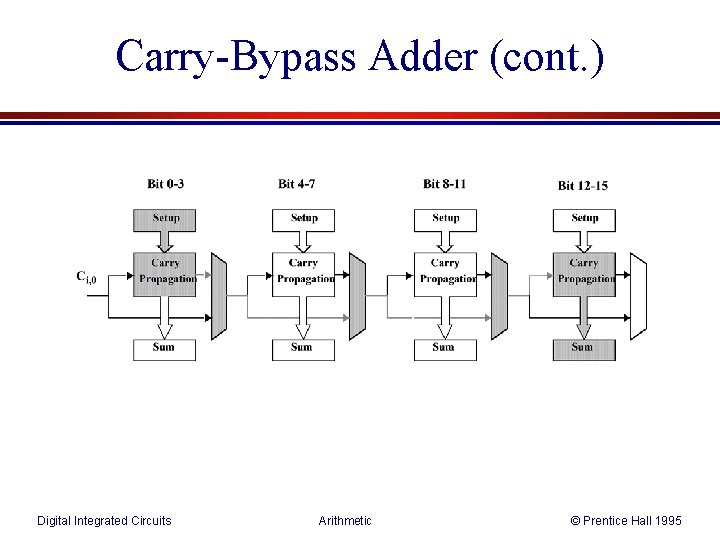

Carry-Bypass Adder (cont. ) Digital Integrated Circuits Arithmetic © Prentice Hall 1995

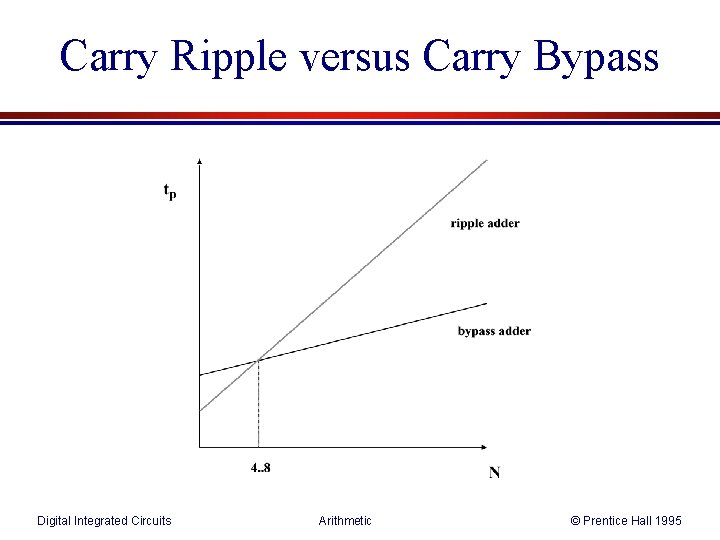

Carry Ripple versus Carry Bypass Digital Integrated Circuits Arithmetic © Prentice Hall 1995

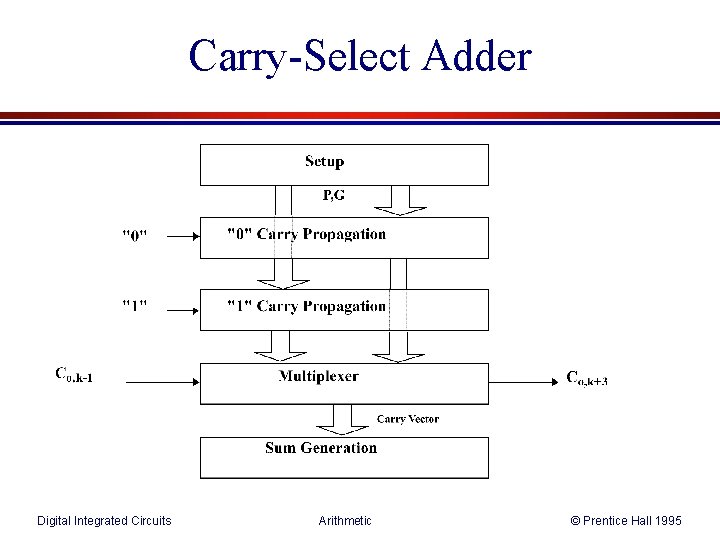

Carry-Select Adder Digital Integrated Circuits Arithmetic © Prentice Hall 1995

Carry Select Adder: Critical Path Digital Integrated Circuits Arithmetic © Prentice Hall 1995

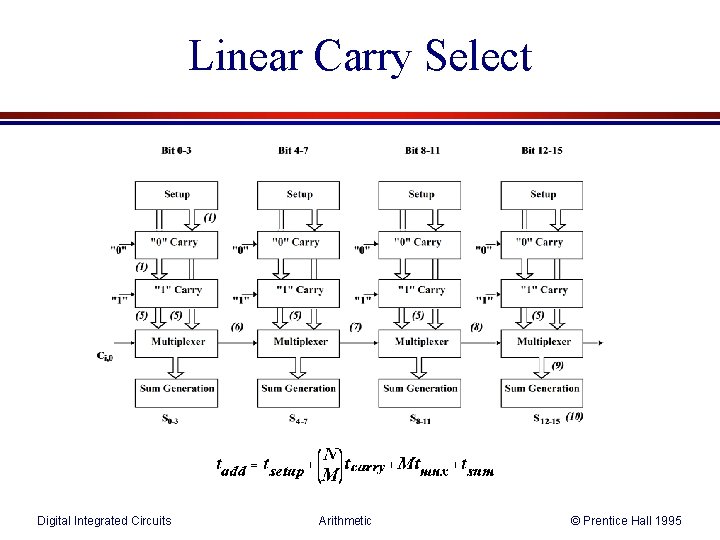

Linear Carry Select Digital Integrated Circuits Arithmetic © Prentice Hall 1995

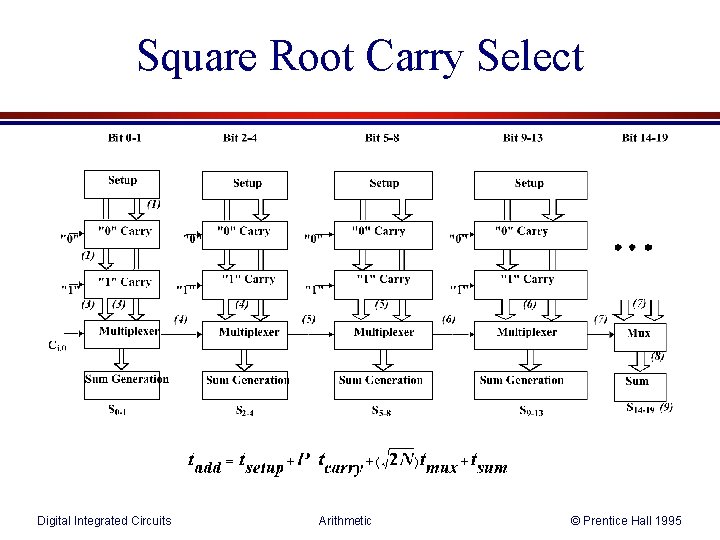

Square Root Carry Select Digital Integrated Circuits Arithmetic © Prentice Hall 1995

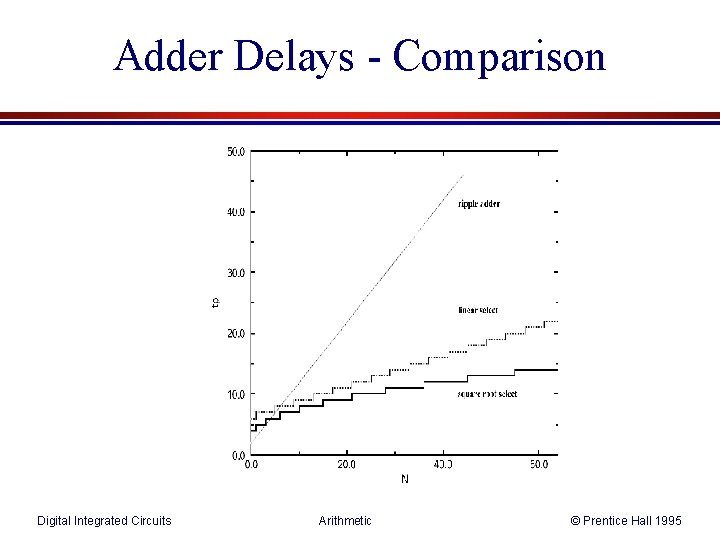

Adder Delays - Comparison Digital Integrated Circuits Arithmetic © Prentice Hall 1995

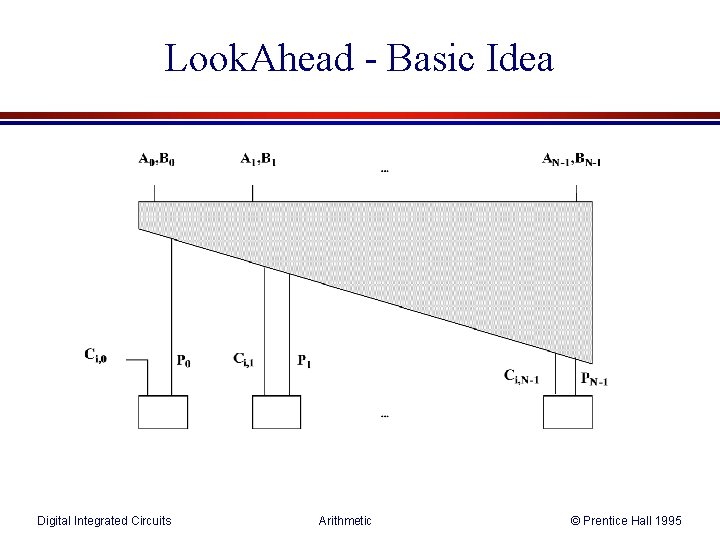

Look. Ahead - Basic Idea Digital Integrated Circuits Arithmetic © Prentice Hall 1995

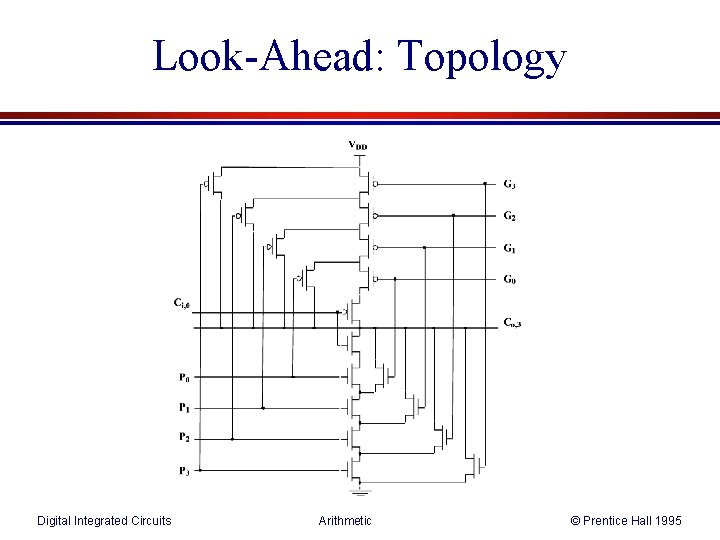

Look-Ahead: Topology Digital Integrated Circuits Arithmetic © Prentice Hall 1995

Logarithmic Look-Ahead Adder Digital Integrated Circuits Arithmetic © Prentice Hall 1995

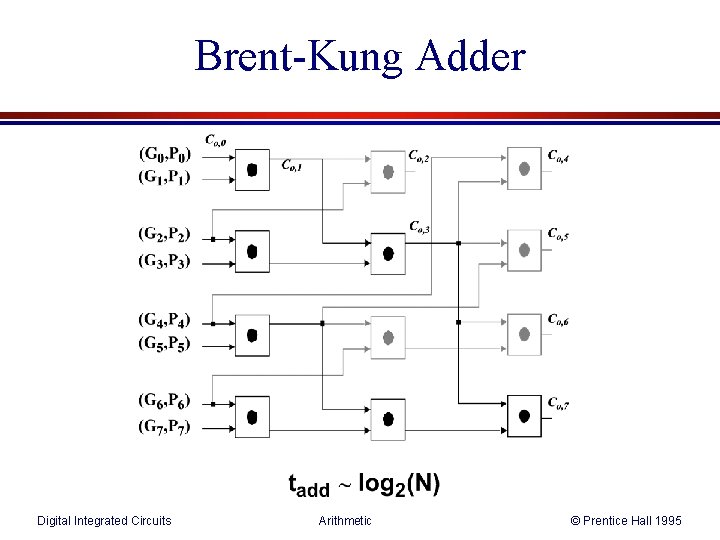

Brent-Kung Adder Digital Integrated Circuits Arithmetic © Prentice Hall 1995

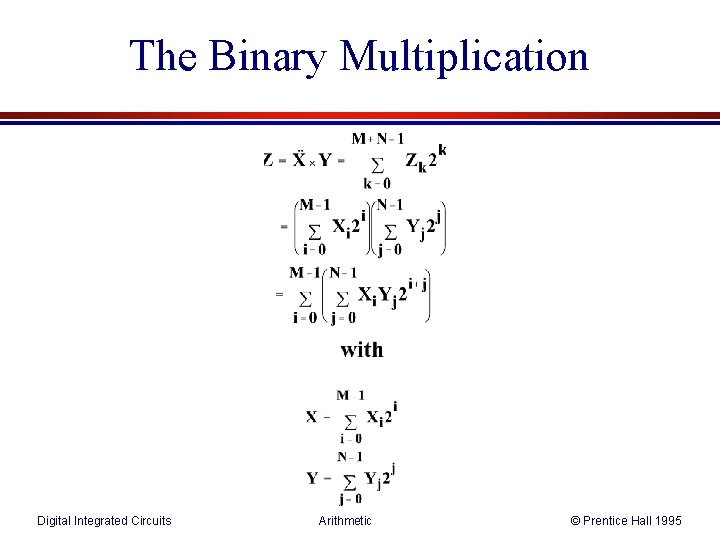

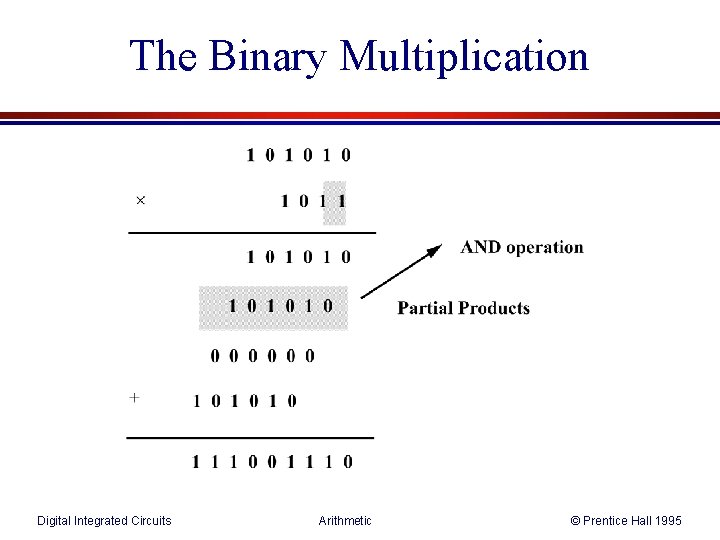

The Binary Multiplication Digital Integrated Circuits Arithmetic © Prentice Hall 1995

The Binary Multiplication Digital Integrated Circuits Arithmetic © Prentice Hall 1995

The Array Multiplier Digital Integrated Circuits Arithmetic © Prentice Hall 1995

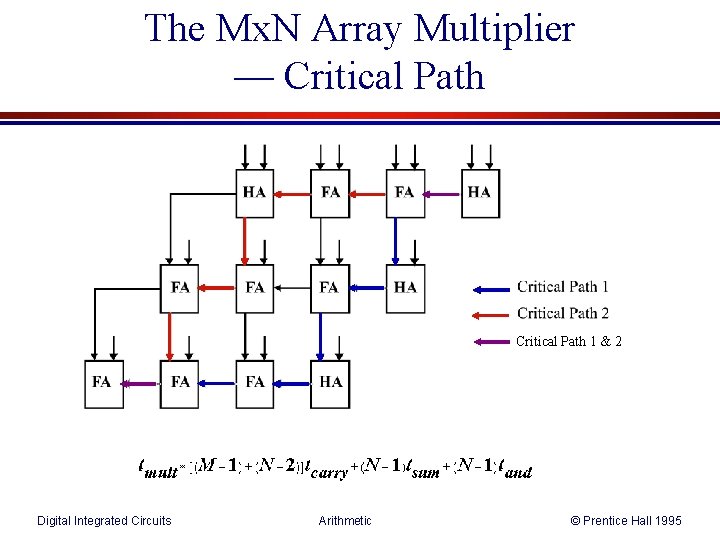

The Mx. N Array Multiplier — Critical Path 1 & 2 Digital Integrated Circuits Arithmetic © Prentice Hall 1995

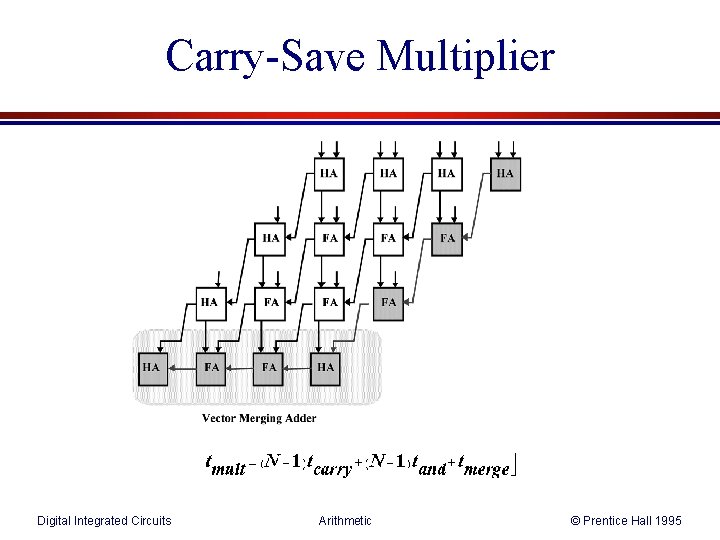

Carry-Save Multiplier Digital Integrated Circuits Arithmetic © Prentice Hall 1995

Adder Cells in Array Multiplier Digital Integrated Circuits Arithmetic © Prentice Hall 1995

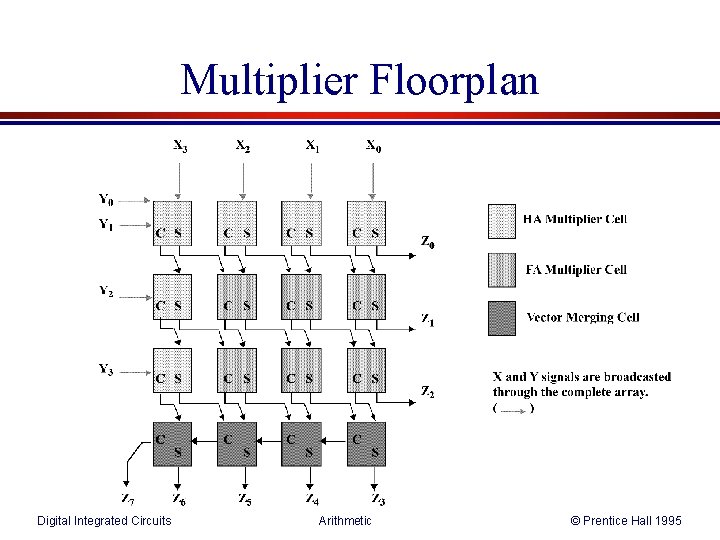

Multiplier Floorplan Digital Integrated Circuits Arithmetic © Prentice Hall 1995

Wallace-Tree Multiplier Digital Integrated Circuits Arithmetic © Prentice Hall 1995

Multipliers —Summary Digital Integrated Circuits Arithmetic © Prentice Hall 1995

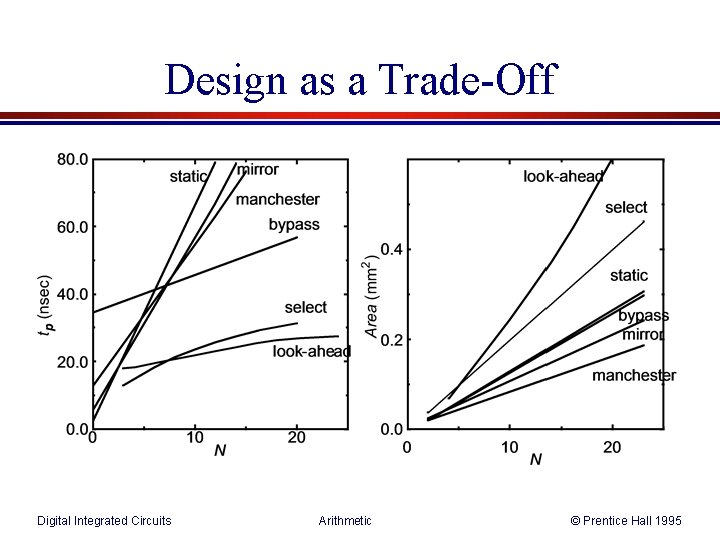

Design as a Trade-Off Digital Integrated Circuits Arithmetic © Prentice Hall 1995

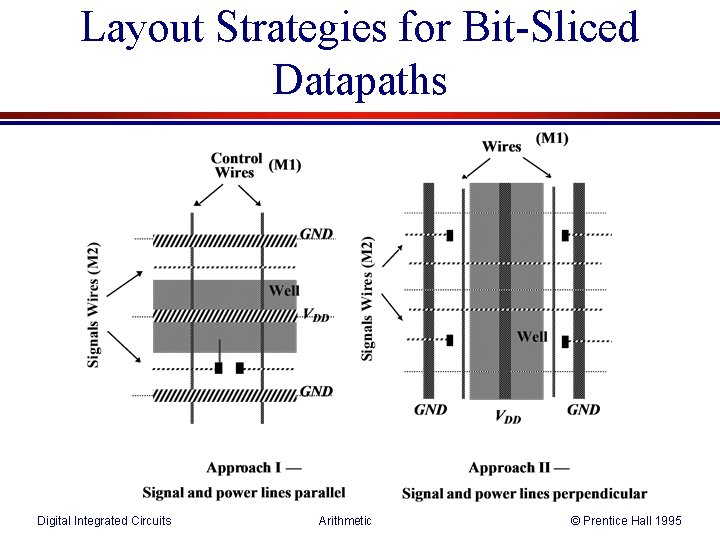

Layout Strategies for Bit-Sliced Datapaths Digital Integrated Circuits Arithmetic © Prentice Hall 1995

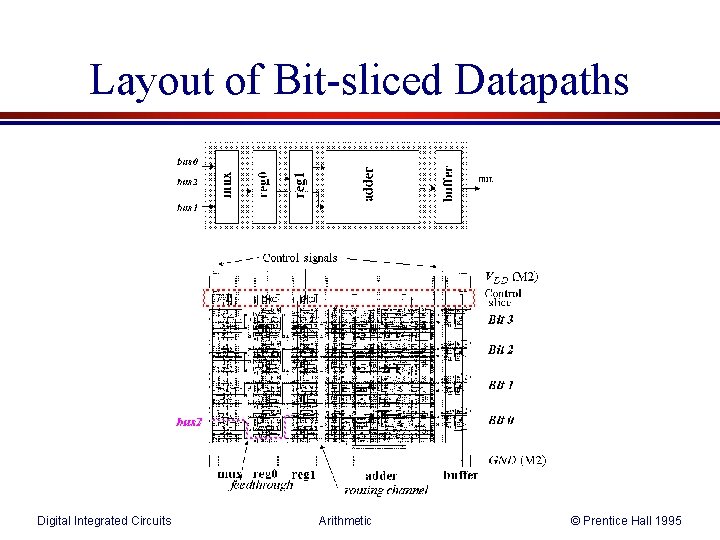

Layout of Bit-sliced Datapaths Digital Integrated Circuits Arithmetic © Prentice Hall 1995

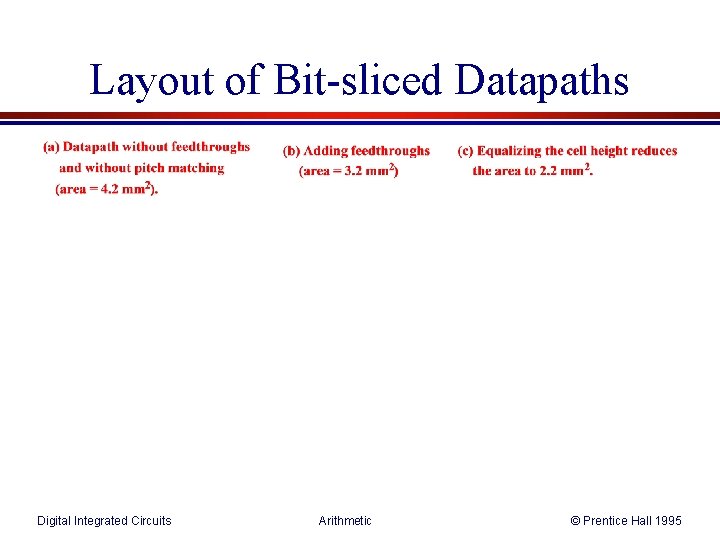

Layout of Bit-sliced Datapaths Digital Integrated Circuits Arithmetic © Prentice Hall 1995

- Slides: 45