Descrevendo Circuitos Lgicos Captulo 3 Parte II Prof

- Slides: 33

Descrevendo Circuitos Lógicos Capítulo 3 Parte II Prof. Gustavo Fernandes de Lima <gustavo. lima@ifrn. edu. br>

Os temas abordados nesse capítulo são: Usar a álgebra booleana para simplificar circuitos lógicos complexos. n Usar os teoremas de De. Morgan para simplificar expressões lógicas. n Usar uma das portas lógicas universais (NAND ou NOR) na implementação de circuitos representados por expressões booleanas. n slide 2 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

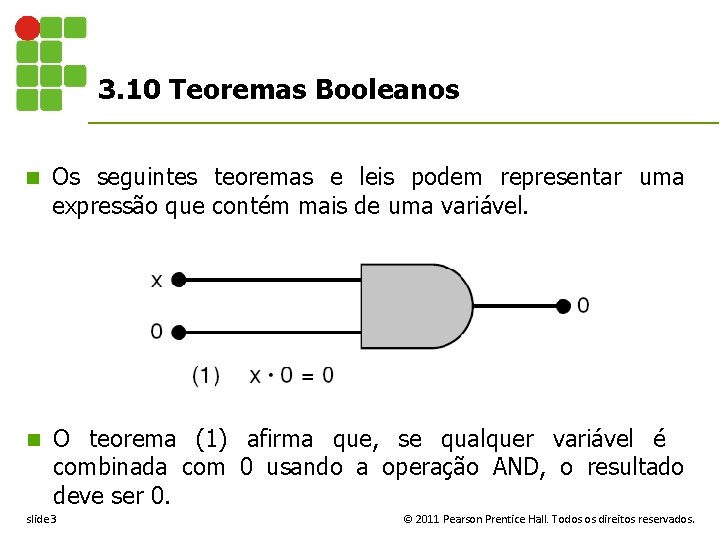

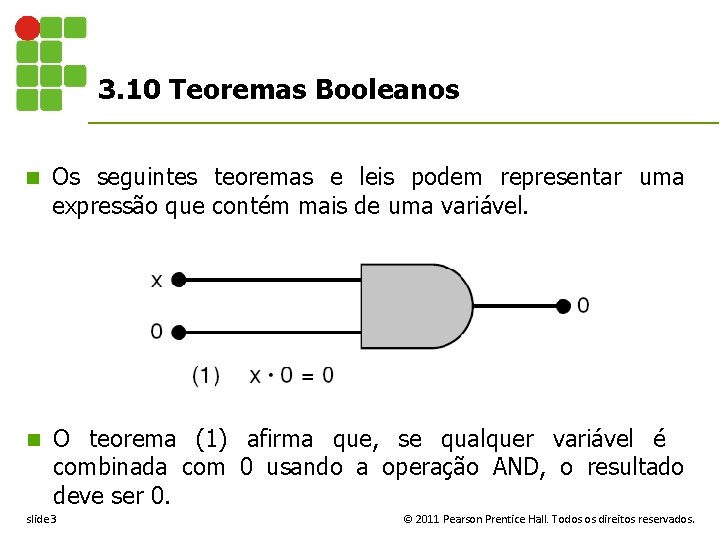

3. 10 Teoremas Booleanos n Os seguintes teoremas e leis podem representar uma expressão que contém mais de uma variável. n O teorema (1) afirma que, se qualquer variável é combinada com 0 usando a operação AND, o resultado deve ser 0. slide 3 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

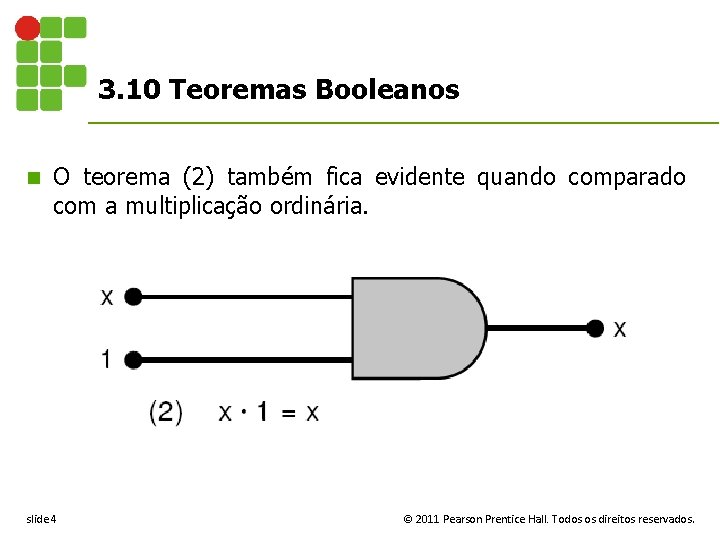

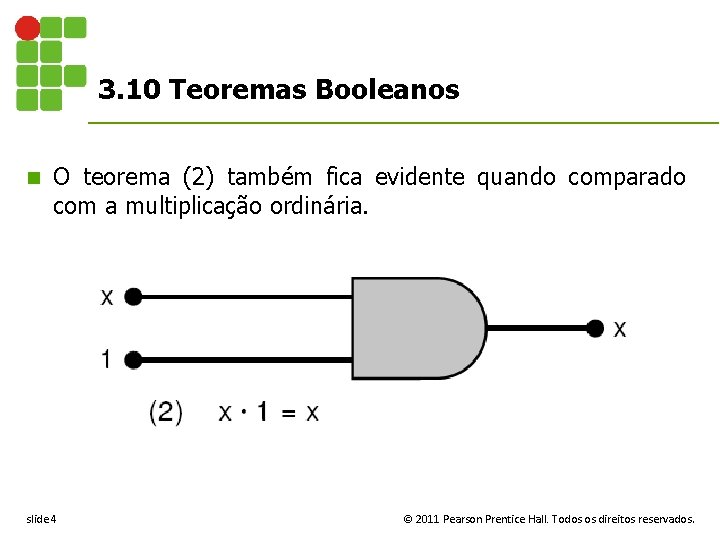

3. 10 Teoremas Booleanos n O teorema (2) também fica evidente quando comparado com a multiplicação ordinária. slide 4 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

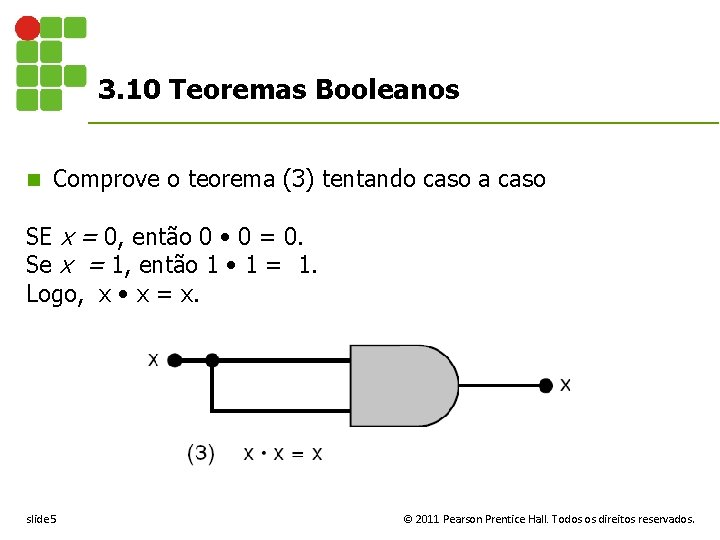

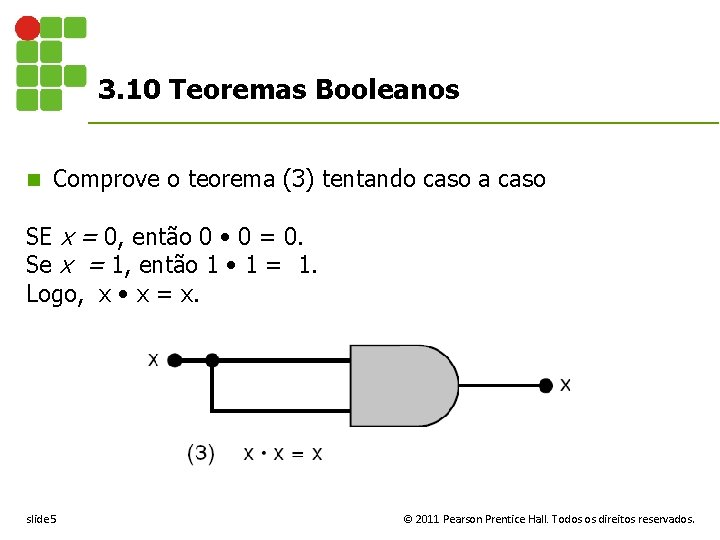

3. 10 Teoremas Booleanos n Comprove o teorema (3) tentando caso a caso SE x = 0, então 0 • 0 = 0. Se x = 1, então 1 • 1 = 1. Logo, x • x = x. slide 5 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

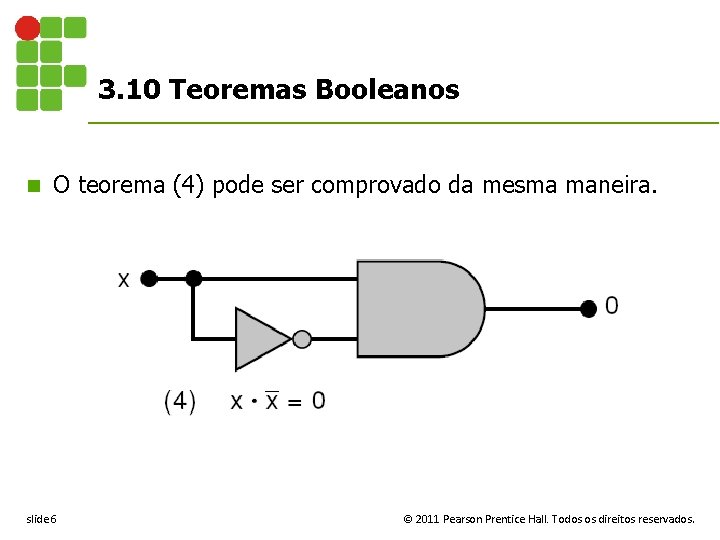

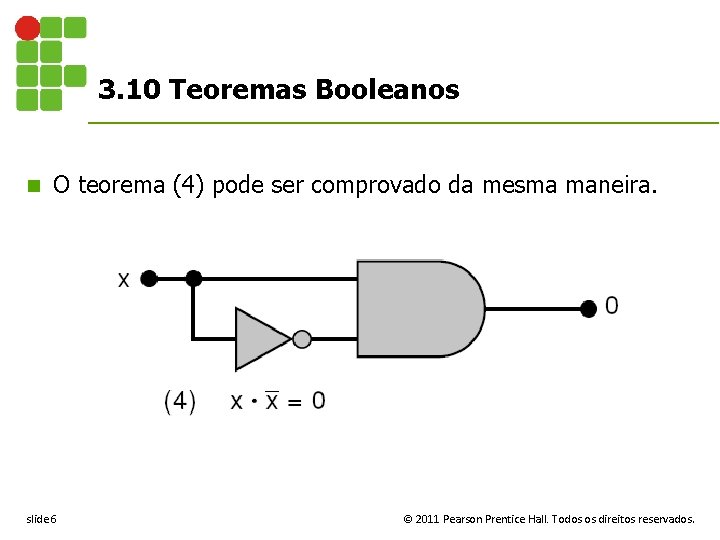

3. 10 Teoremas Booleanos n O teorema (4) pode ser comprovado da mesma maneira. slide 6 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

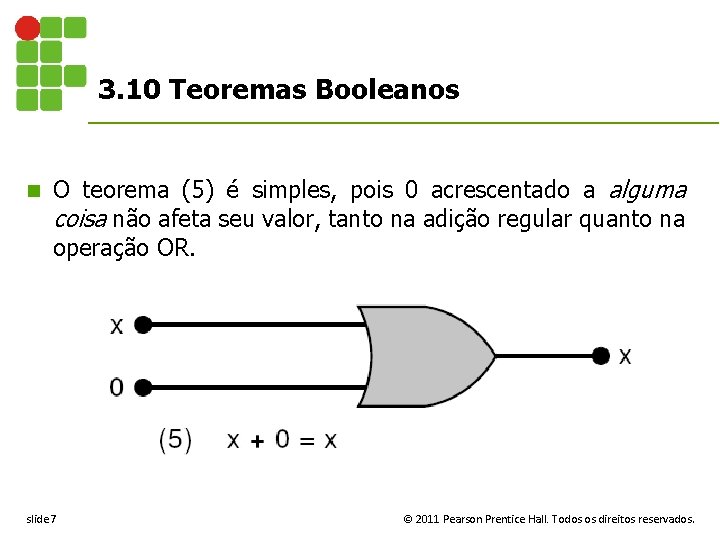

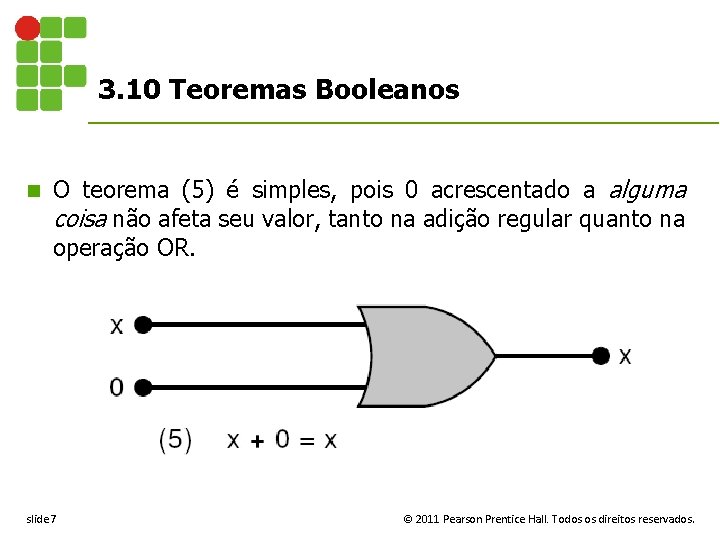

3. 10 Teoremas Booleanos n O teorema (5) é simples, pois 0 acrescentado a alguma coisa não afeta seu valor, tanto na adição regular quanto na operação OR. slide 7 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

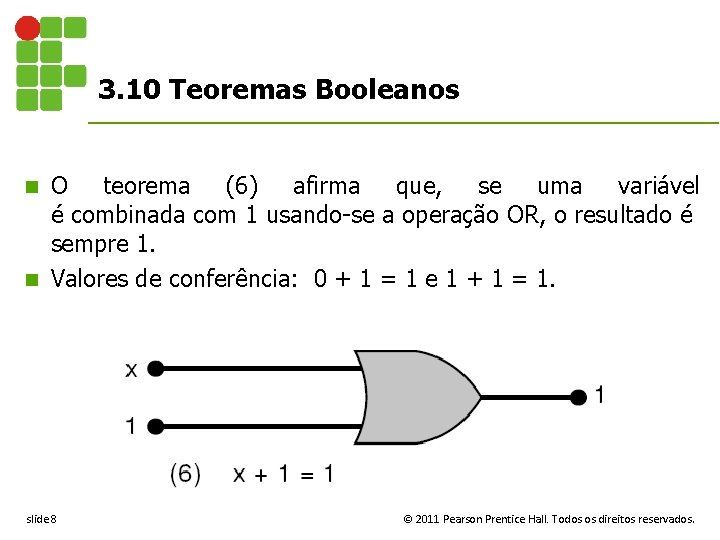

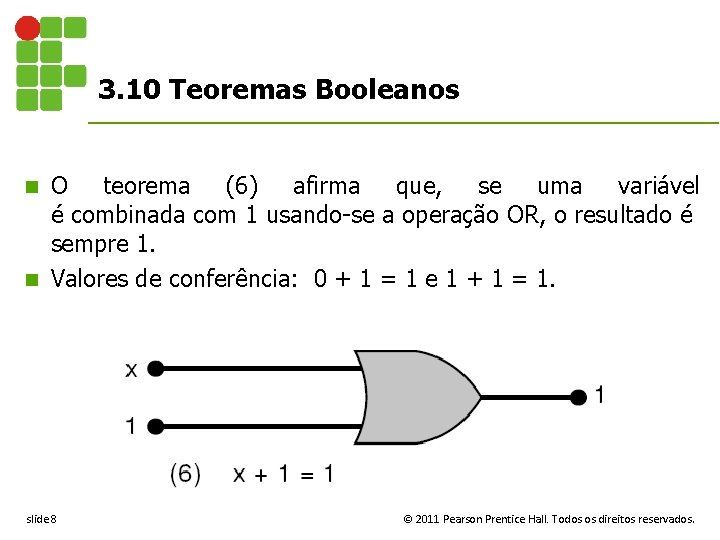

3. 10 Teoremas Booleanos O teorema (6) afirma que, se uma variável é combinada com 1 usando-se a operação OR, o resultado é sempre 1. n Valores de conferência: 0 + 1 = 1 e 1 + 1 = 1. n slide 8 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

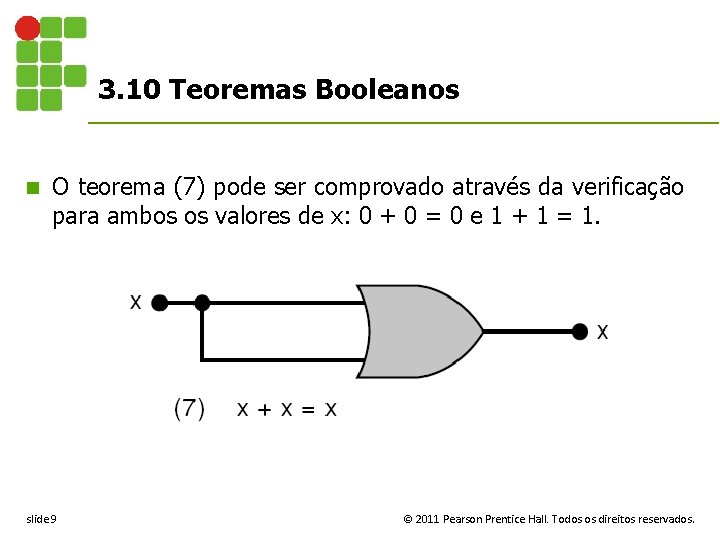

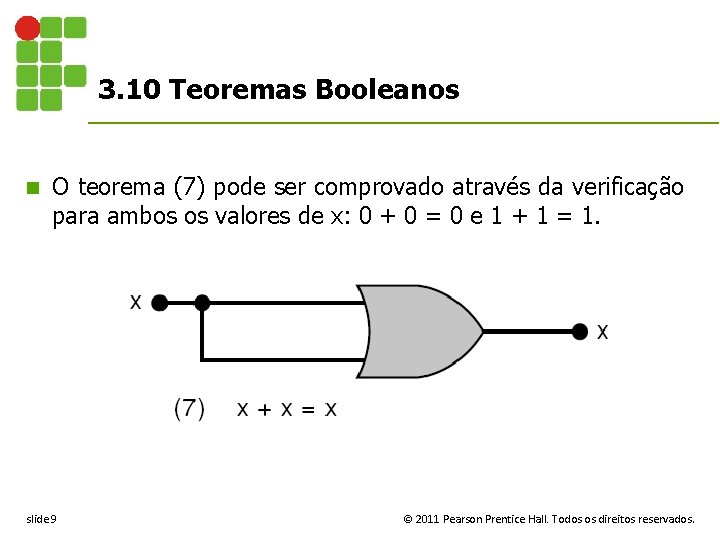

3. 10 Teoremas Booleanos n O teorema (7) pode ser comprovado através da verificação para ambos os valores de x: 0 + 0 = 0 e 1 + 1 = 1. slide 9 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

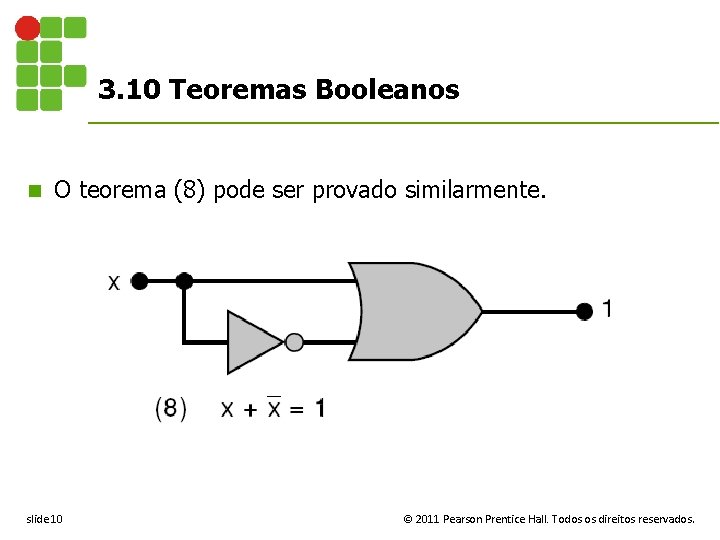

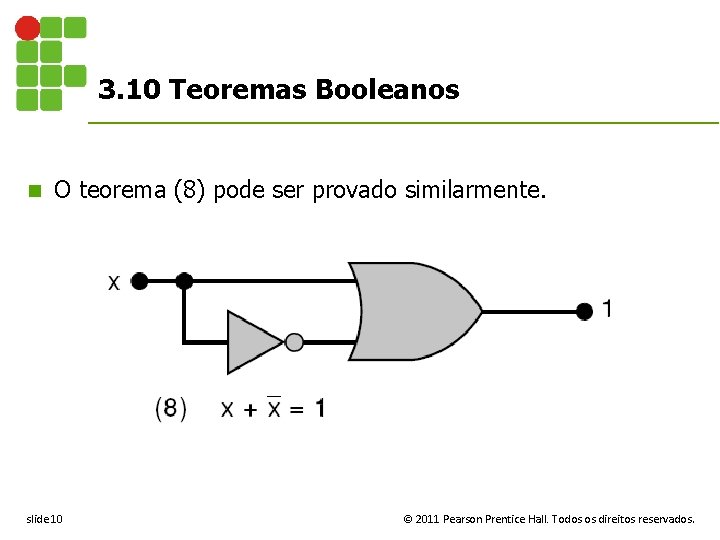

3. 10 Teoremas Booleanos n O teorema (8) pode ser provado similarmente. slide 10 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

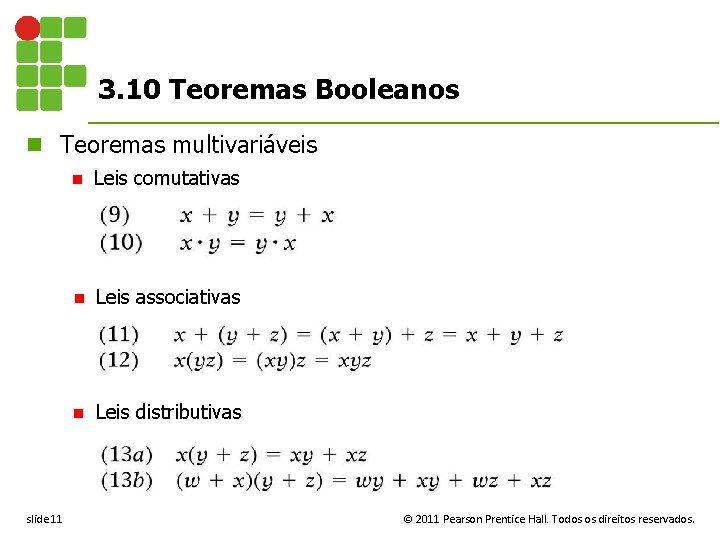

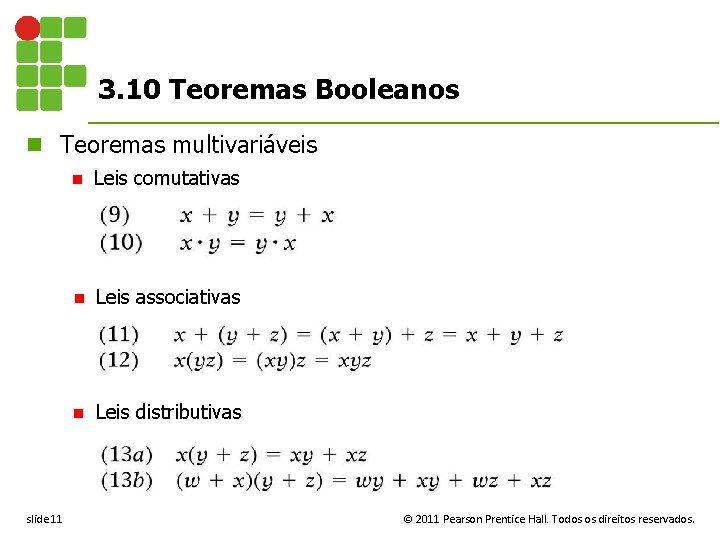

3. 10 Teoremas Booleanos n Teoremas multivariáveis slide 11 n Leis comutativas n Leis associativas n Leis distributivas © 2011 Pearson Prentice Hall. Todos os direitos reservados.

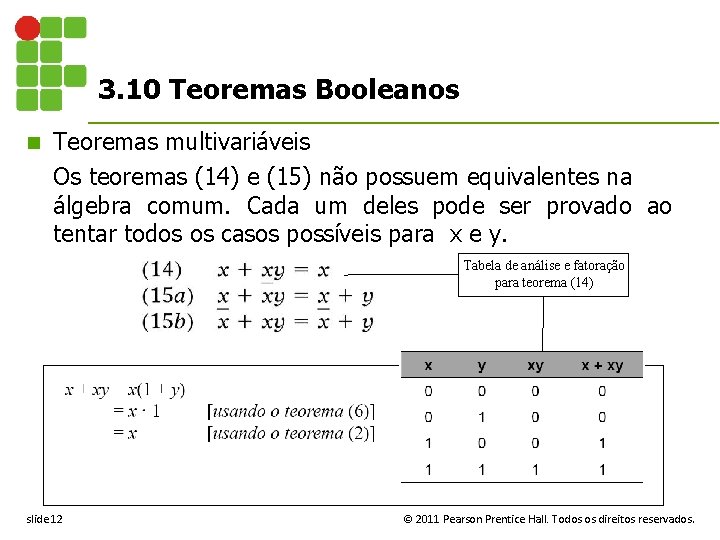

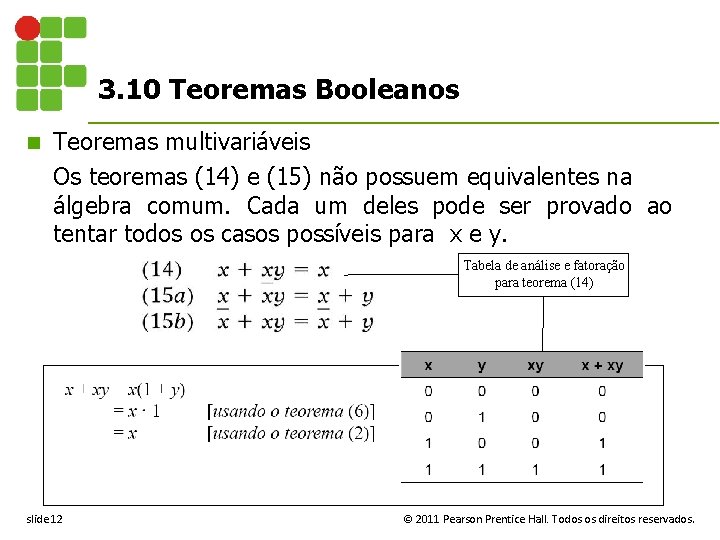

3. 10 Teoremas Booleanos n Teoremas multivariáveis Os teoremas (14) e (15) não possuem equivalentes na álgebra comum. Cada um deles pode ser provado ao tentar todos os casos possíveis para x e y. Tabela de análise e fatoração para teorema (14) slide 12 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

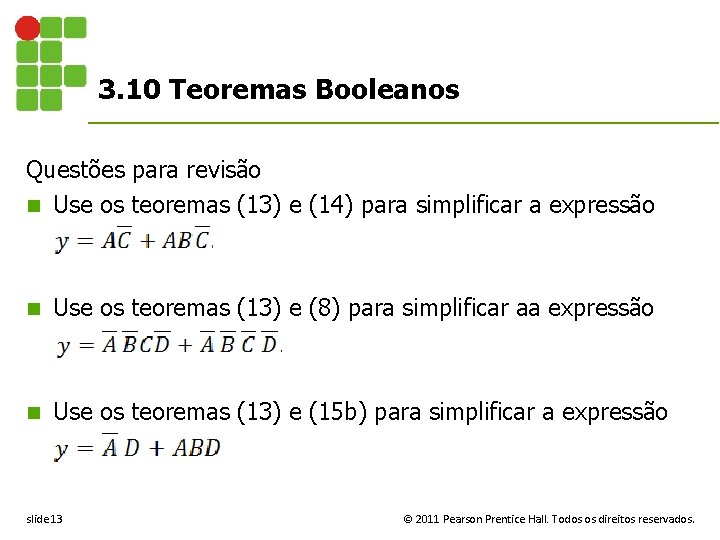

3. 10 Teoremas Booleanos Questões para revisão n Use os teoremas (13) e (14) para simplificar a expressão n Use os teoremas (13) e (8) para simplificar aa expressão n Use os teoremas (13) e (15 b) para simplificar a expressão slide 13 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

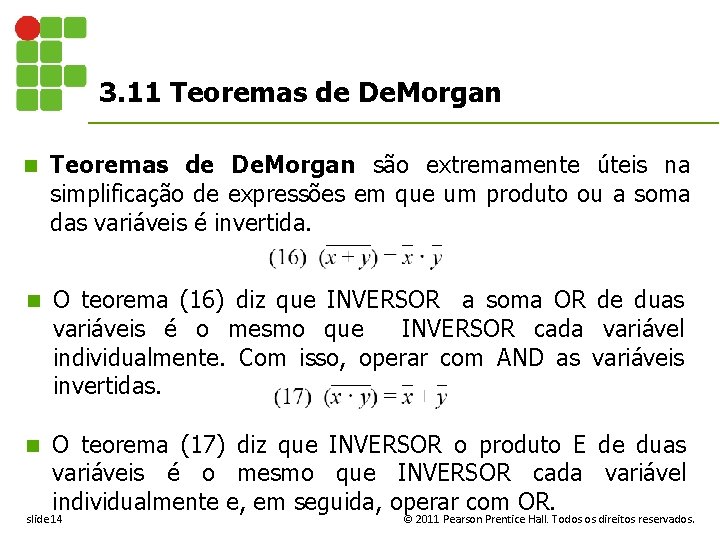

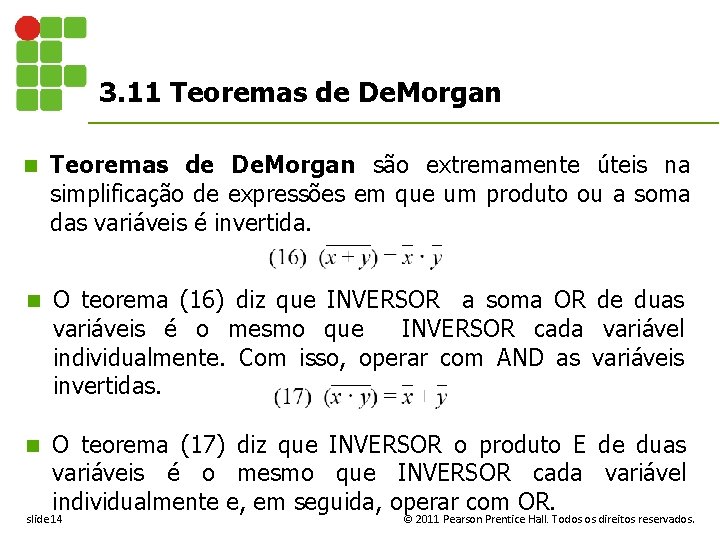

3. 11 Teoremas de De. Morgan n Teoremas de De. Morgan são extremamente úteis na simplificação de expressões em que um produto ou a soma das variáveis é invertida. n O teorema (16) diz que INVERSOR a soma OR de duas variáveis é o mesmo que INVERSOR cada variável individualmente. Com isso, operar com AND as variáveis invertidas. n O teorema (17) diz que INVERSOR o produto E de duas variáveis é o mesmo que INVERSOR cada variável individualmente e, em seguida, operar com OR. slide 14 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

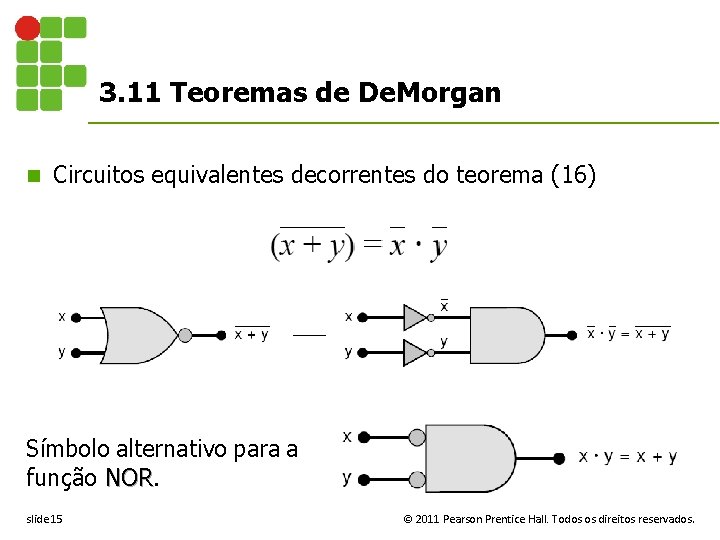

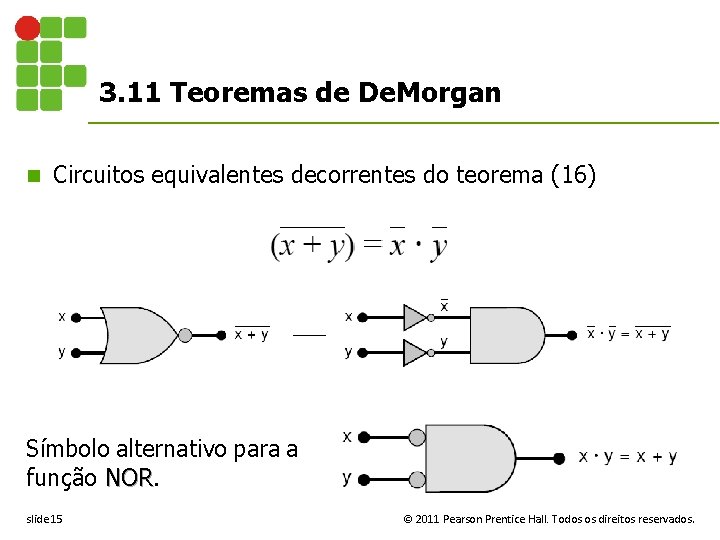

3. 11 Teoremas de De. Morgan n Circuitos equivalentes decorrentes do teorema (16) Símbolo alternativo para a função NOR slide 15 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

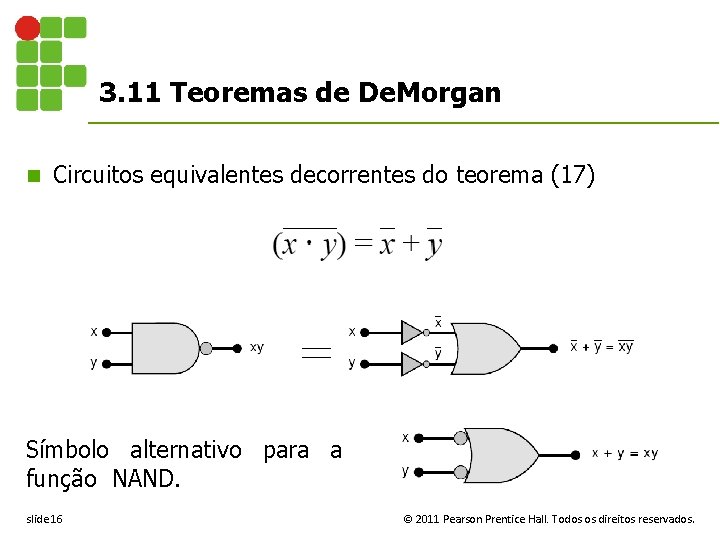

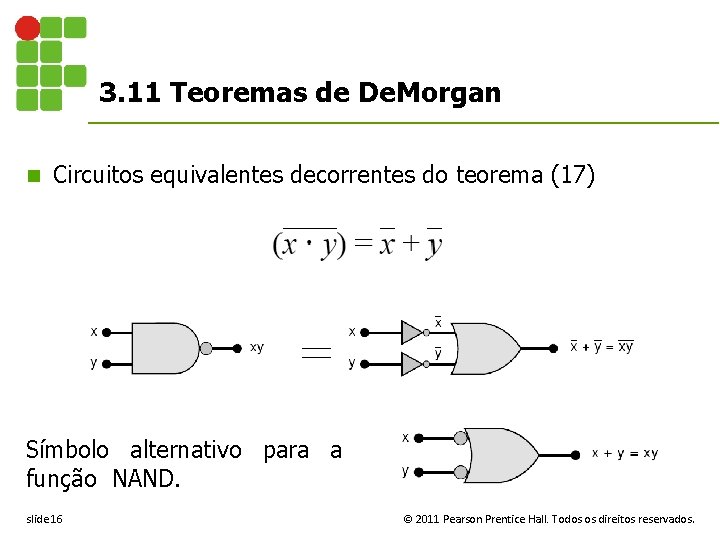

3. 11 Teoremas de De. Morgan n Circuitos equivalentes decorrentes do teorema (17) Símbolo alternativo para a função NAND. slide 16 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

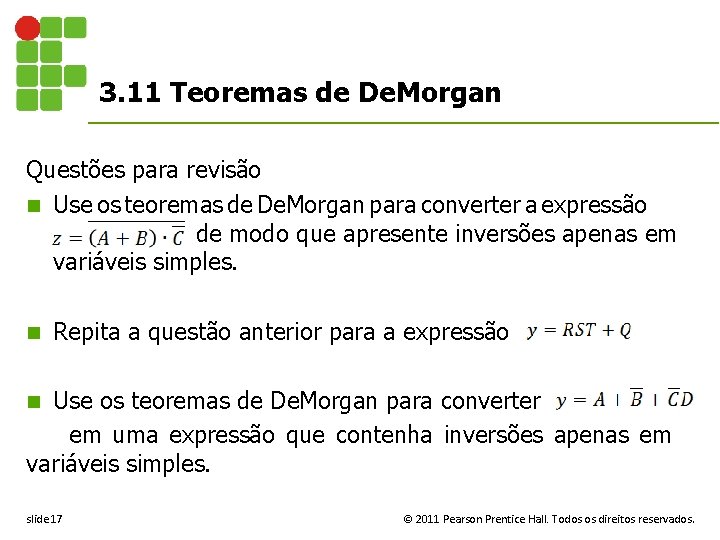

3. 11 Teoremas de De. Morgan Questões para revisão n Use os teoremas de De. Morgan para converter a expressão de modo que apresente inversões apenas em variáveis simples. n Repita a questão anterior para a expressão . Use os teoremas de De. Morgan para converter em uma expressão que contenha inversões apenas em variáveis simples. n slide 17 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

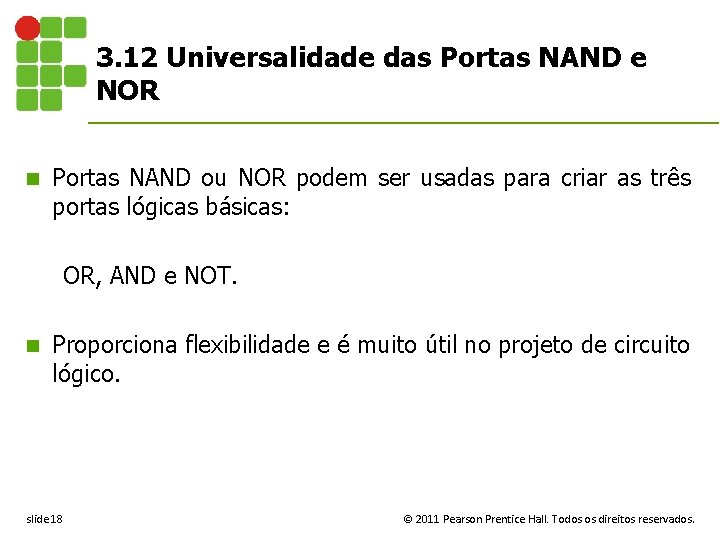

3. 12 Universalidade das Portas NAND e NOR n Portas NAND ou NOR podem ser usadas para criar as três portas lógicas básicas: OR, AND e NOT. n Proporciona flexibilidade e é muito útil no projeto de circuito lógico. slide 18 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

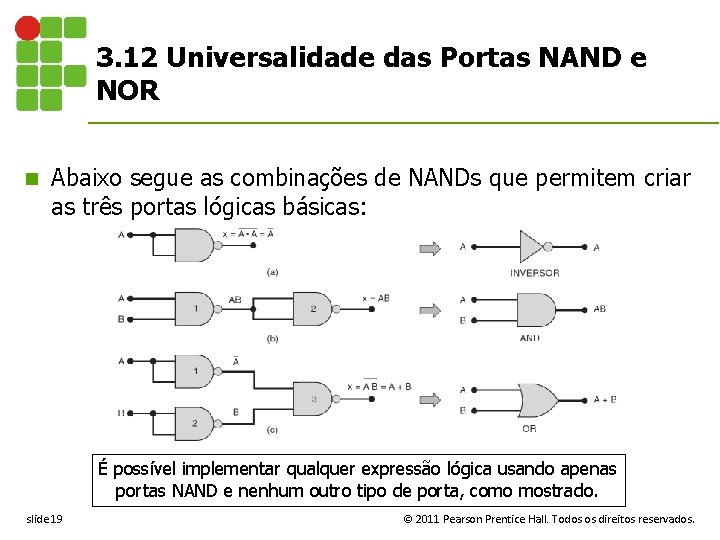

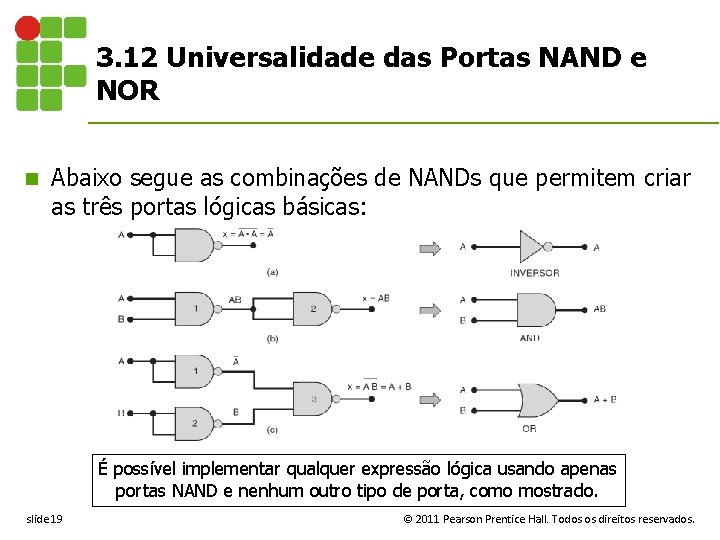

3. 12 Universalidade das Portas NAND e NOR n Abaixo segue as combinações de NANDs que permitem criar as três portas lógicas básicas: É possível implementar qualquer expressão lógica usando apenas portas NAND e nenhum outro tipo de porta, como mostrado. slide 19 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

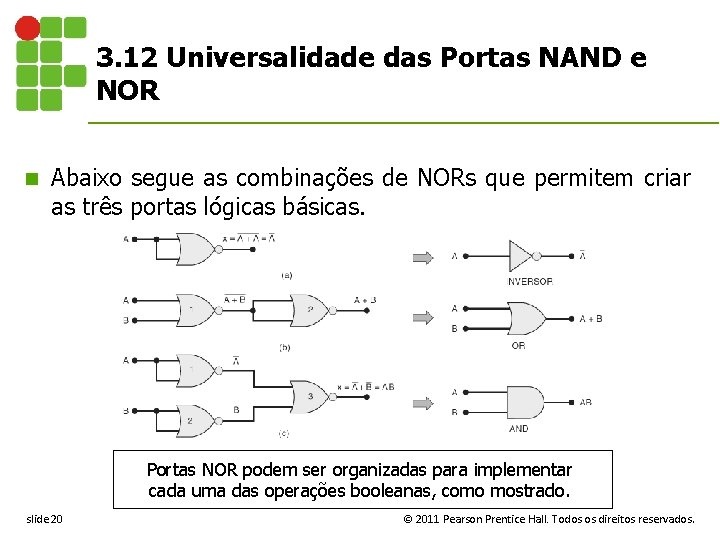

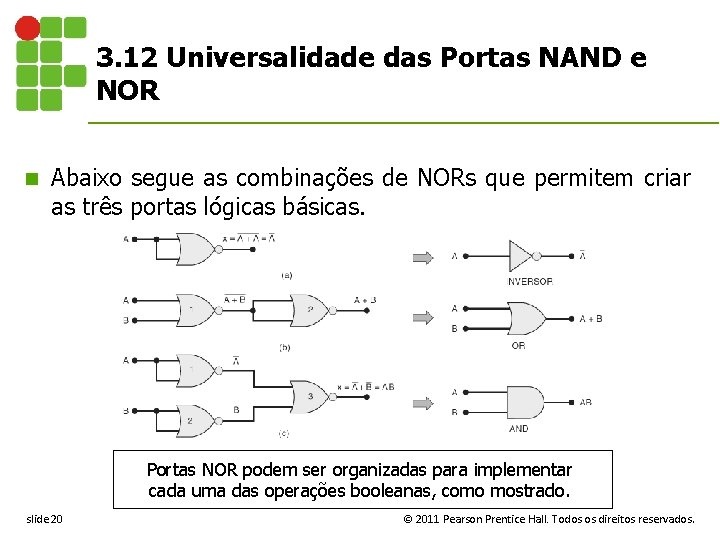

3. 12 Universalidade das Portas NAND e NOR n Abaixo segue as combinações de NORs que permitem criar as três portas lógicas básicas. Portas NOR podem ser organizadas para implementar cada uma das operações booleanas, como mostrado. slide 20 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

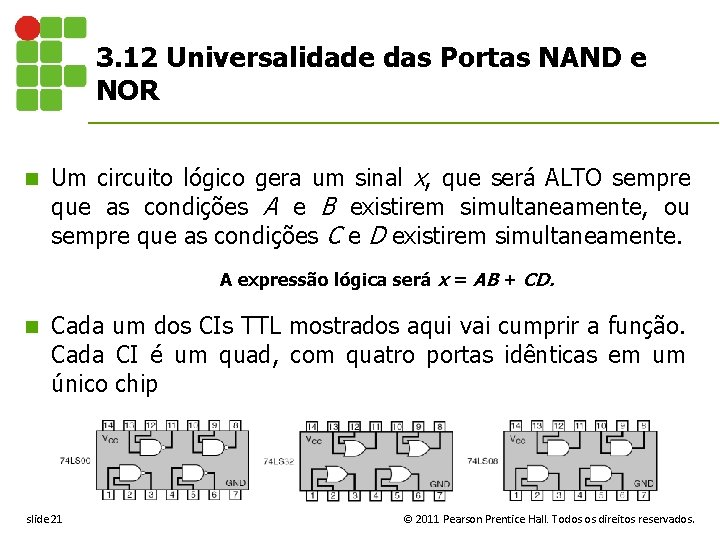

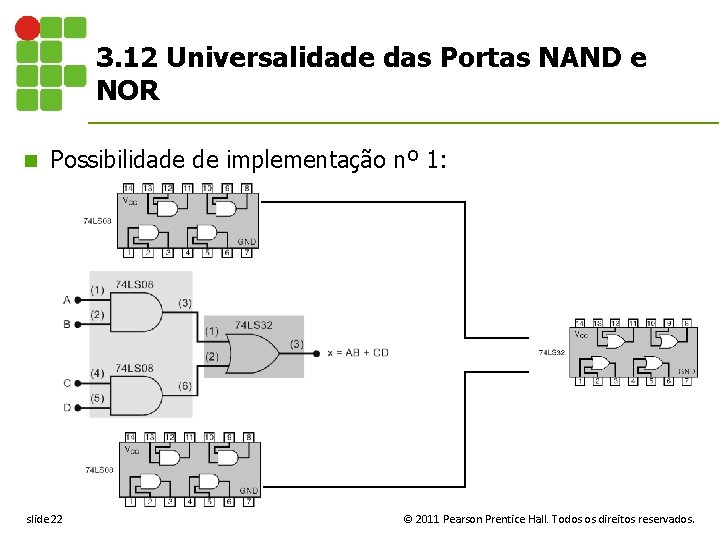

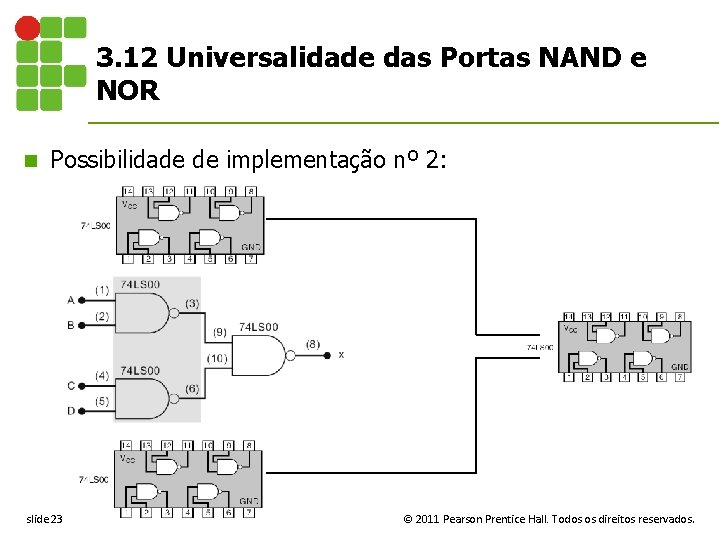

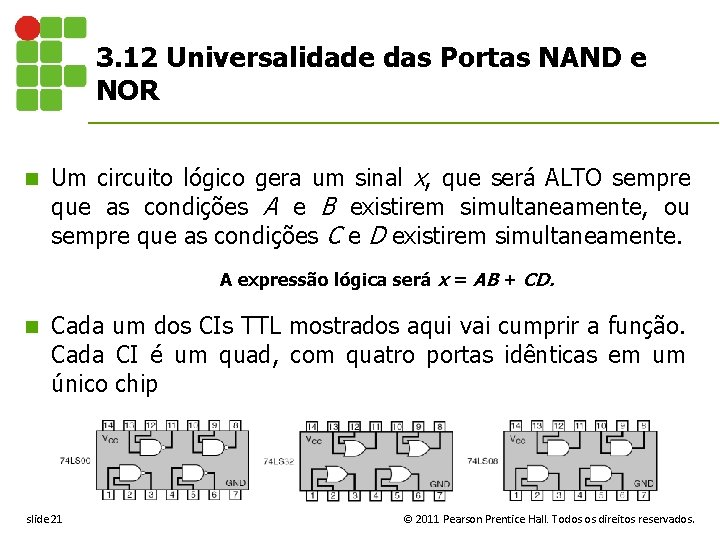

3. 12 Universalidade das Portas NAND e NOR n Um circuito lógico gera um sinal x, que será ALTO sempre que as condições A e B existirem simultaneamente, ou sempre que as condições C e D existirem simultaneamente. A expressão lógica será x = AB + CD. n Cada um dos CIs TTL mostrados aqui vai cumprir a função. Cada CI é um quad, com quatro portas idênticas em um único chip slide 21 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

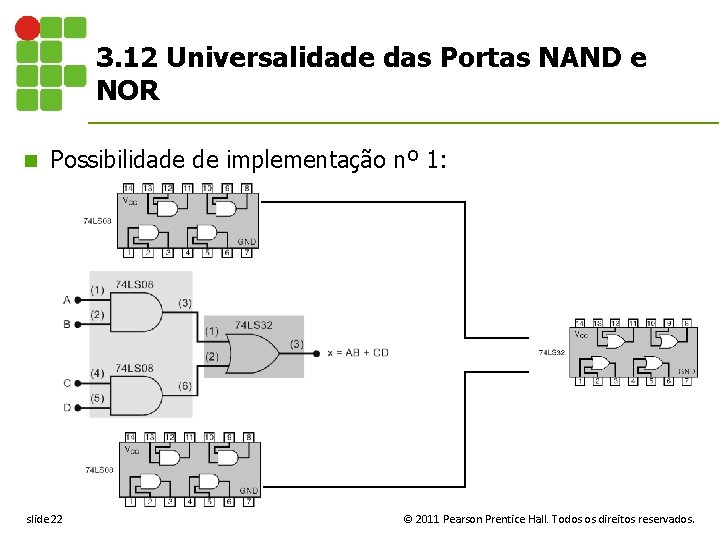

3. 12 Universalidade das Portas NAND e NOR n Possibilidade de implementação nº 1: slide 22 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

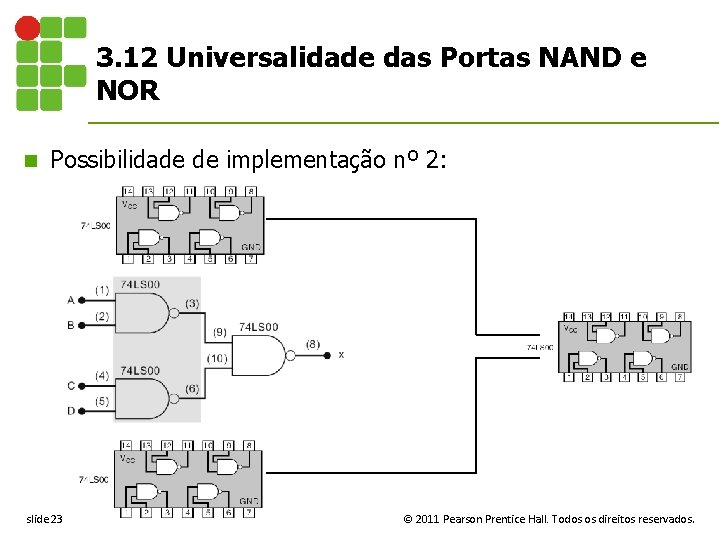

3. 12 Universalidade das Portas NAND e NOR n Possibilidade de implementação nº 2: slide 23 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

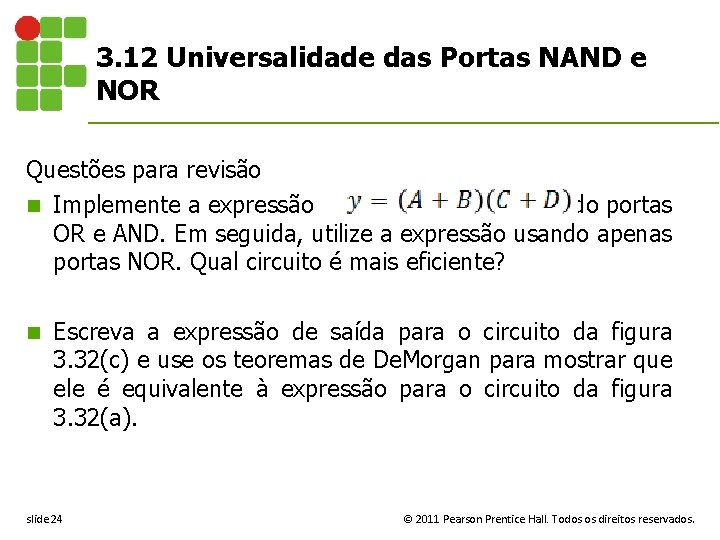

3. 12 Universalidade das Portas NAND e NOR Questões para revisão n Implemente a expressão usando portas OR e AND. Em seguida, utilize a expressão usando apenas portas NOR. Qual circuito é mais eficiente? n Escreva a expressão de saída para o circuito da figura 3. 32(c) e use os teoremas de De. Morgan para mostrar que ele é equivalente à expressão para o circuito da figura 3. 32(a). slide 24 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

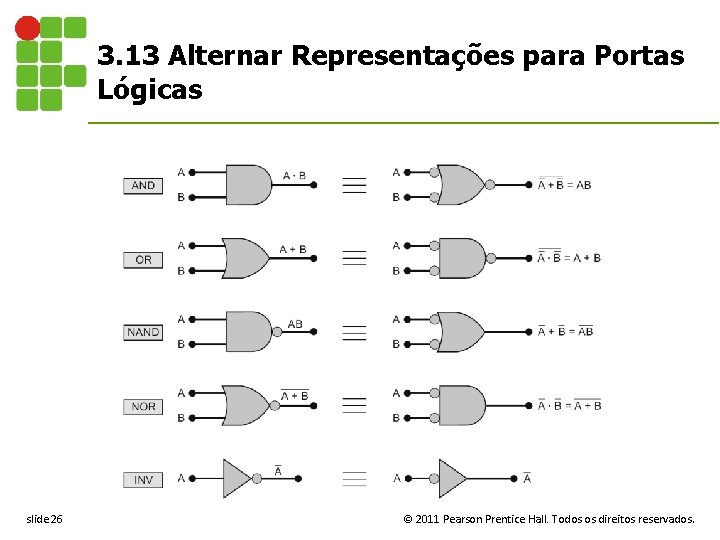

3. 13 Alternar Representações para Portas Lógicas n Para converter um símbolo-padrão em um suplente, siga os seguintes passos: n inverta cada entrada e saída de símbolos-padrão; n adicione uma bolha de inversão, onde não exista alguma; n remova as bolhas, caso existam. slide 25 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

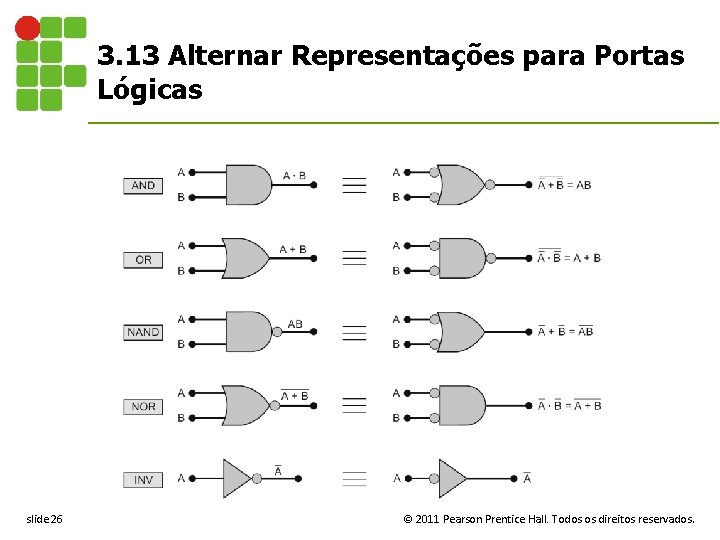

3. 13 Alternar Representações para Portas Lógicas slide 26 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

3. 13 Alternar Representações para Portas Lógicas n Aspectos sobre as equivalências de símbolos lógicos: n n n slide 27 As equivalências podem ser estendidas para portas com qualquer número de entradas. Nenhum dos símbolos-padrão tem bolhas em suas entradas, e todos os símbolos alternativos os têm. NAND e NOR são portas inversoras. O padrão e os símbolos alternativos para cada um terão uma bolha sobre a entrada ou a saída. Portas AND e OR são portas não inversoras. Os símbolos alternativos para cada um terá bolhas em ambas as entradas e as saídas. © 2011 Pearson Prentice Hall. Todos os direitos reservados.

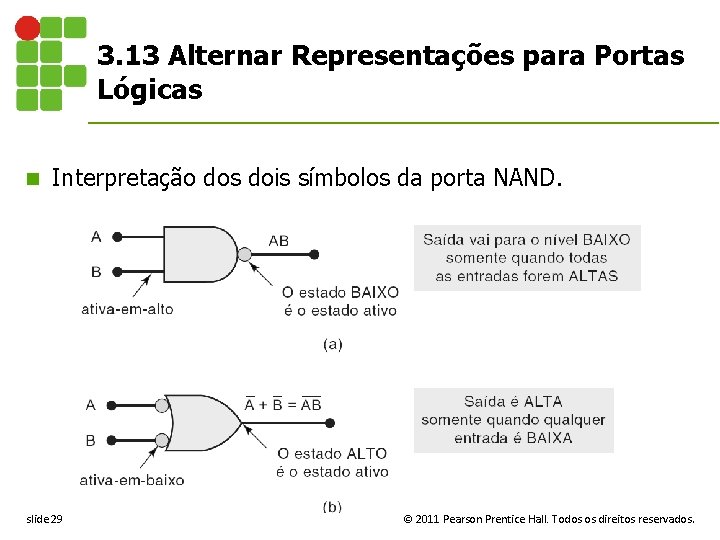

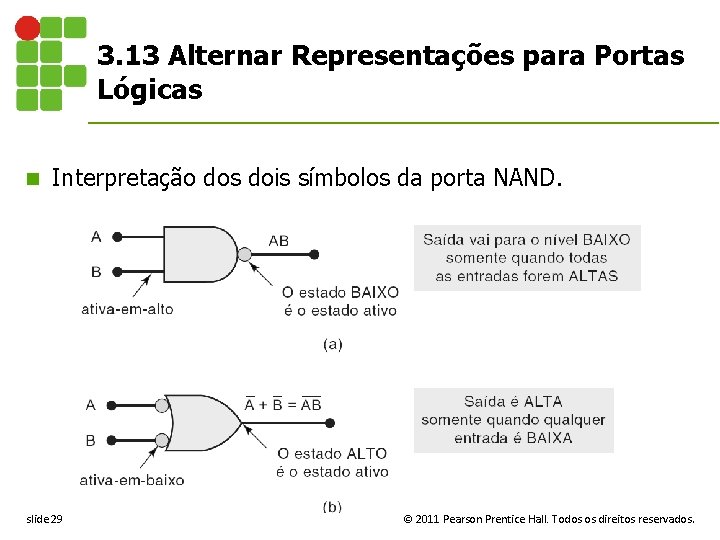

3. 13 Alternar Representações para Portas Lógicas n Ativa-em-ALTO – entrada ou saída não tem uma bolha de inversão. n Ativa-em-BAIXO – entrada ou saída tem uma bolha de inversão. slide 28 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

3. 13 Alternar Representações para Portas Lógicas n Interpretação dos dois símbolos da porta NAND. slide 29 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

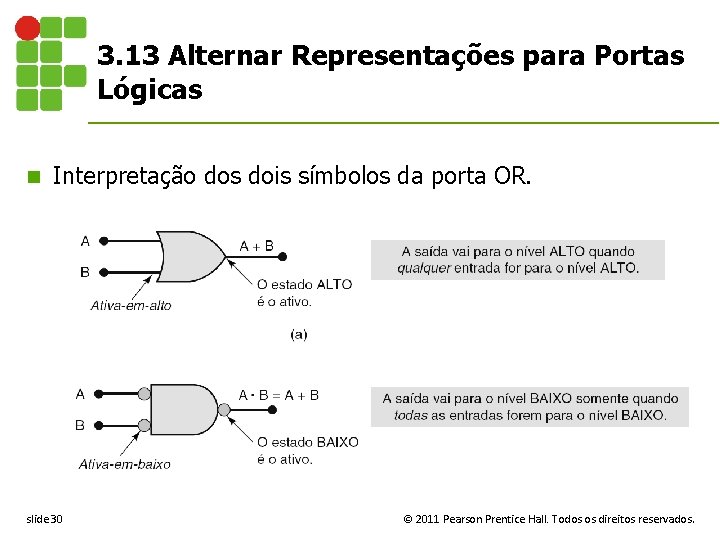

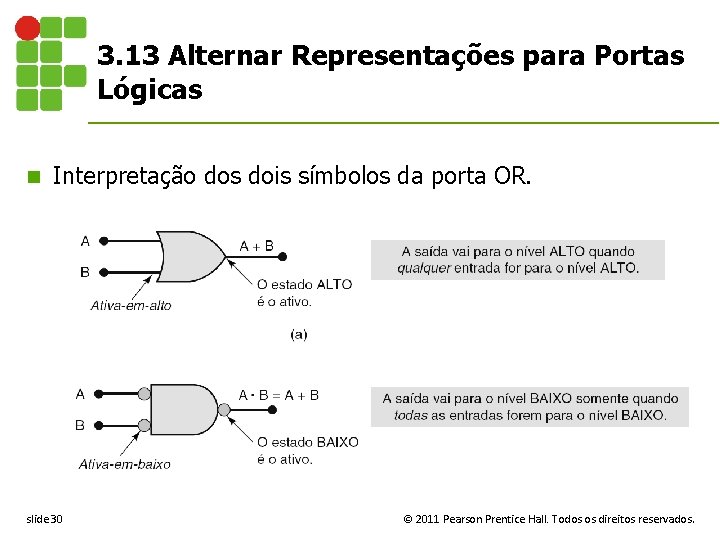

3. 13 Alternar Representações para Portas Lógicas n Interpretação dos dois símbolos da porta OR. slide 30 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

3. 13 Alternar Representações para Portas Lógicas Questões para revisão n Descreva a operação realizada pelo símbolo-padrão da porta NOR na figura 3. 33. n Repita a questão para o símbolo alternativo da porta NOR. n Repita a questão para o símbolo alternativo da porta AND. n Repita a questão para o símbolo-padrão da porta AND. slide 31 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

Bibliografia n TOCCI, Ronald J. ; WIDMER, Neal S. ; MOSS, Gregory L. . Sistemas digitais: princípios e aplicações. 11. ed. São Paulo : Pearson Prentice Hall, 2011. slide 32 © 2011 Pearson Prentice Hall. Todos os direitos reservados.

Fim O B R I G A D O <gustavo. lima@ifrn. edu. br> http: //tiny. cc/profgustavo slide 33 © 2011 Pearson Prentice Hall. Todos os direitos reservados.