Electrical Engineering 348 ELECTRONIC CIRCUITS I Dr John

![Lowpass Step Response • Input Is Unit Step [X(s) = 1/s] • Overdamped ( Lowpass Step Response • Input Is Unit Step [X(s) = 1/s] • Overdamped (](https://slidetodoc.com/presentation_image/0f67ecaecbb9b3aed8973585b6405379/image-34.jpg)

![Underdamped Step Analysis • Input Is Unit Step [X(s) = 1/s] • Underdamped ( Underdamped Step Analysis • Input Is Unit Step [X(s) = 1/s] • Underdamped (](https://slidetodoc.com/presentation_image/0f67ecaecbb9b3aed8973585b6405379/image-41.jpg)

- Slides: 42

Electrical Engineering 348: ELECTRONIC CIRCUITS I Dr. John Choma, Jr. Professor of Electrical Engineering University of Southern California Department of Electrical Engineering– Electrophysics University Park; Mail Code: 0271 Los Angeles, California 90089 -0271 213 -740 -4692 [Office] 626 -715 -0944 [Fax] 818 -384 -1552 [Cell] johnc@almaak. usc. edu Spring Semester 2001 EE 348 - Spring 2001 J. Choma, Jr.

EE 348: Lecture Supplement Notes SN 1 Review of Basic Circuit Theory and Introduction To Fundamental Electronic System Concepts 01 January 2001 EE 348 – Spring 2001 J. Choma, Jr. 2

Outline Of Lecture • Thévenin’s & Norton’s Theorems • Basic Electronic System Concepts • Steady State Sinusoidal Response • Transient Response EE 348 – Spring 2001 J. Choma, Jr. 3

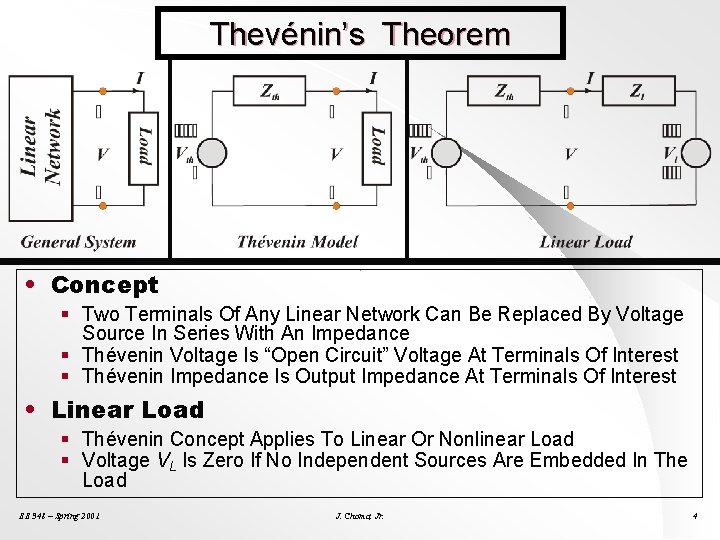

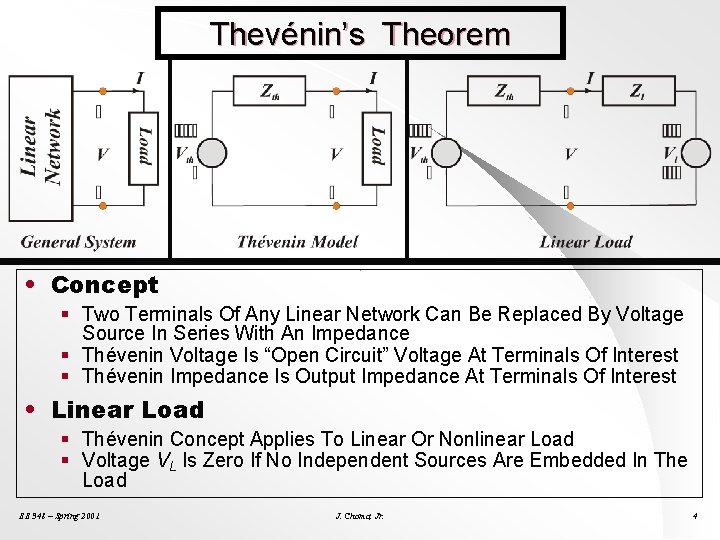

Thevénin’s Theorem • Concept § Two Terminals Of Any Linear Network Can Be Replaced By Voltage Source In Series With An Impedance § Thévenin Voltage Is “Open Circuit” Voltage At Terminals Of Interest § Thévenin Impedance Is Output Impedance At Terminals Of Interest • Linear Load § Thévenin Concept Applies To Linear Or Nonlinear Load § Voltage VL Is Zero If No Independent Sources Are Embedded In The Load EE 348 – Spring 2001 J. Choma, Jr. 4

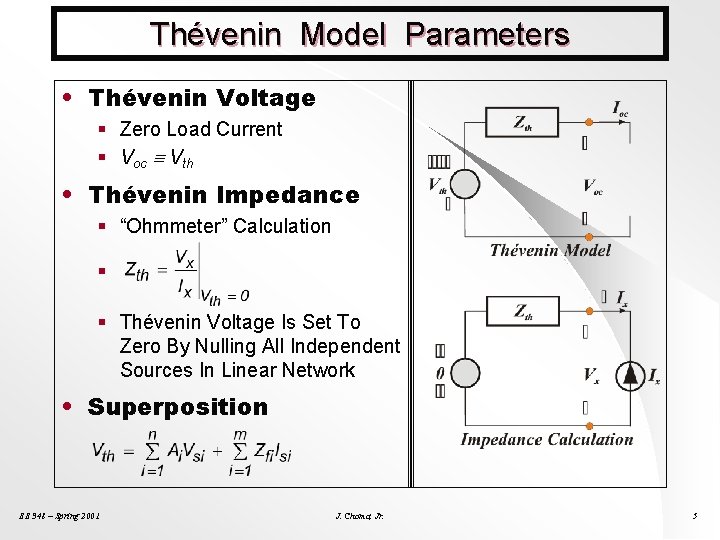

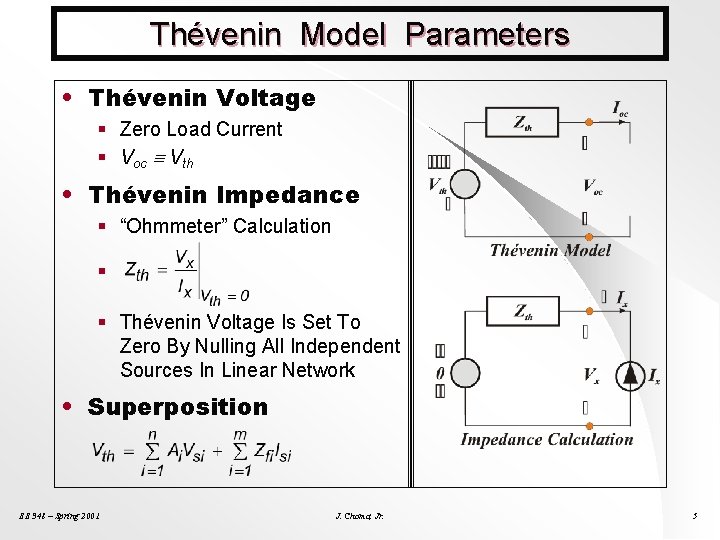

Thévenin Model Parameters • Thévenin Voltage § Zero Load Current § Voc Vth • Thévenin Impedance § “Ohmmeter” Calculation § § Thévenin Voltage Is Set To Zero By Nulling All Independent Sources In Linear Network • Superposition EE 348 – Spring 2001 J. Choma, Jr. 5

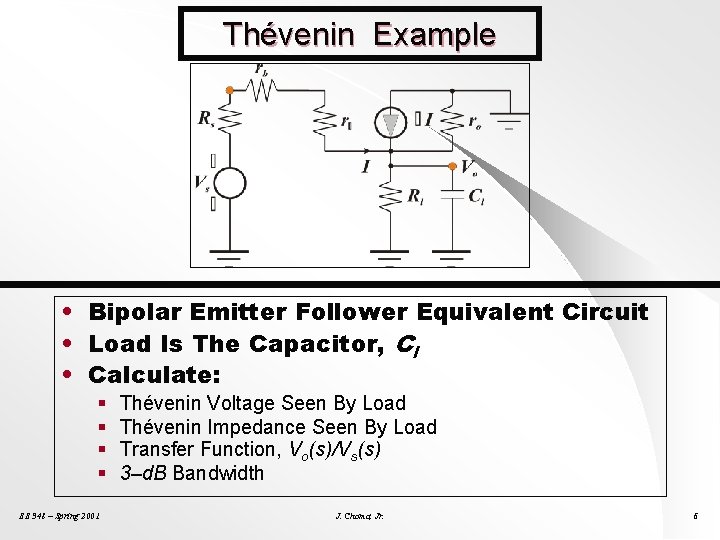

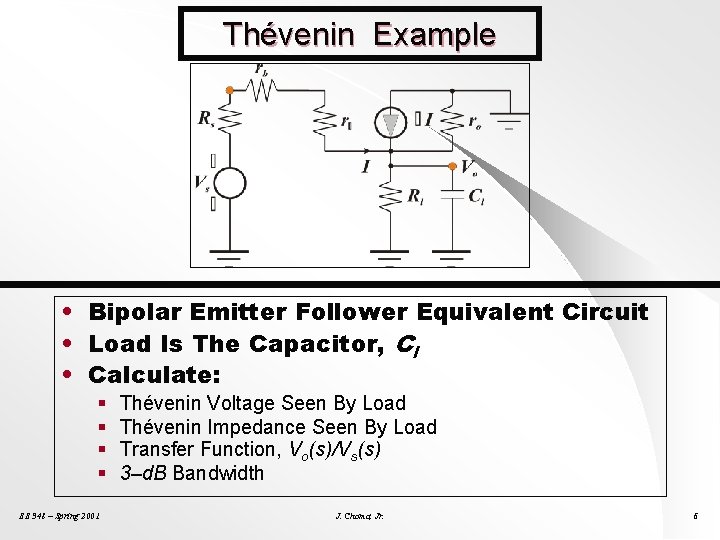

Thévenin Example • Bipolar Emitter Follower Equivalent Circuit • Load Is The Capacitor, Cl • Calculate: § § EE 348 – Spring 2001 Thévenin Voltage Seen By Load Thévenin Impedance Seen By Load Transfer Function, Vo(s)/Vs(s) 3–d. B Bandwidth J. Choma, Jr. 6

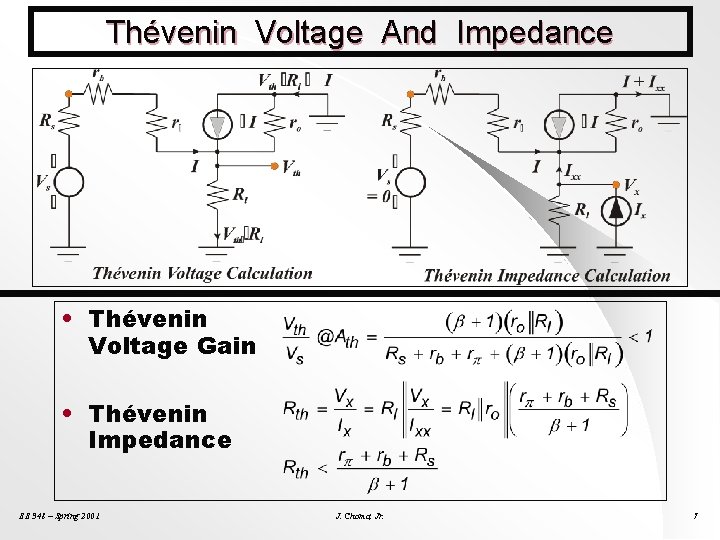

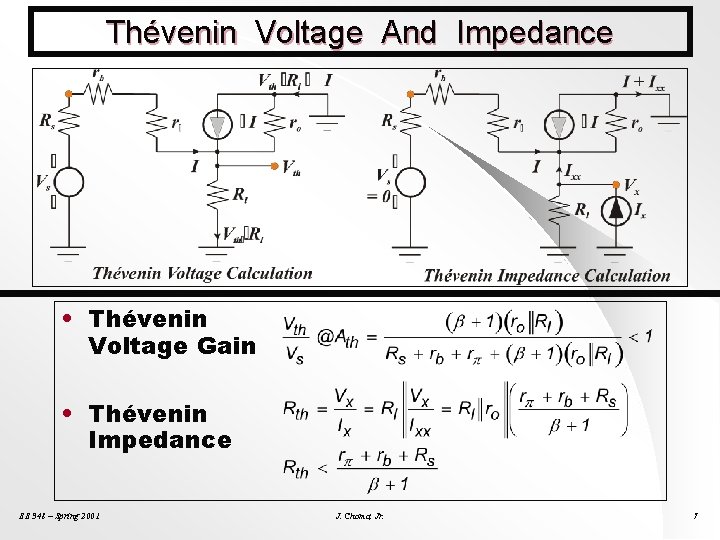

Thévenin Voltage And Impedance • Thévenin Voltage Gain • Thévenin Impedance EE 348 – Spring 2001 J. Choma, Jr. 7

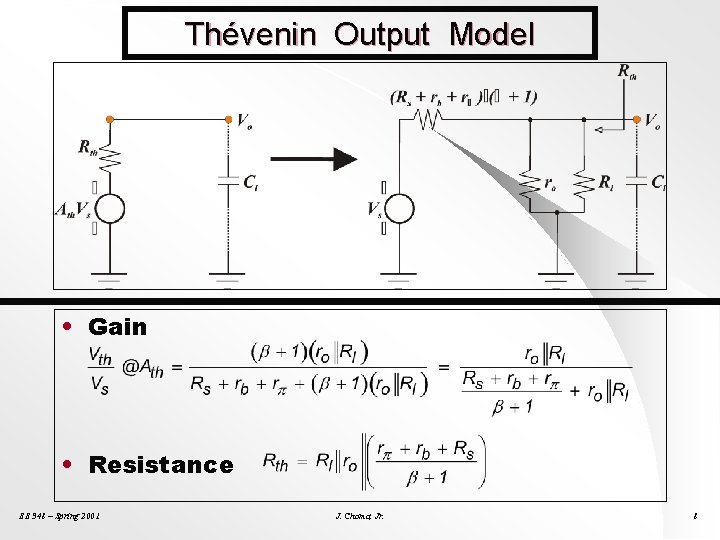

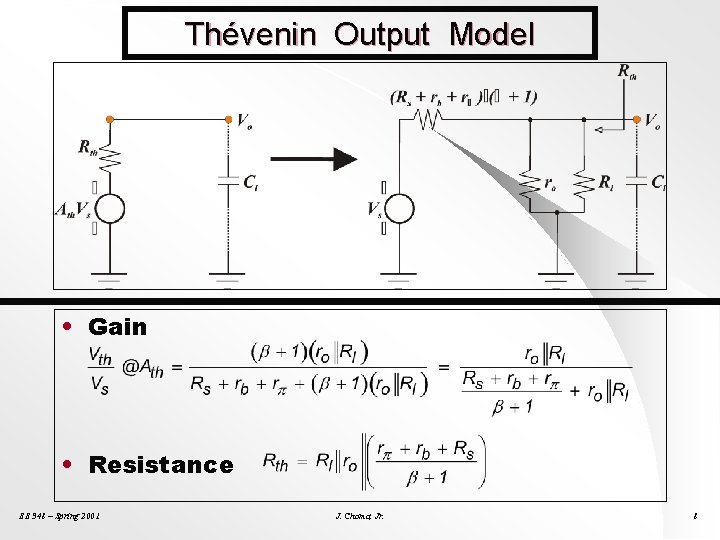

Thévenin Output Model • Gain • Resistance EE 348 – Spring 2001 J. Choma, Jr. 8

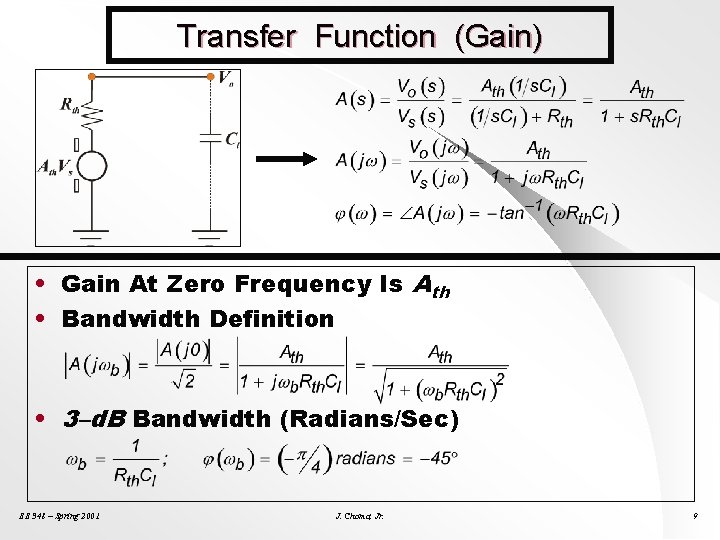

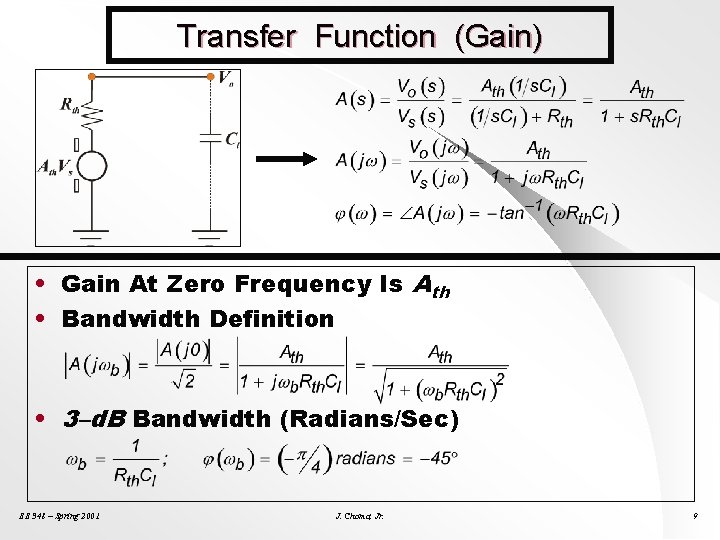

Transfer Function (Gain) • Gain At Zero Frequency Is Ath • Bandwidth Definition • 3–d. B Bandwidth (Radians/Sec) EE 348 – Spring 2001 J. Choma, Jr. 9

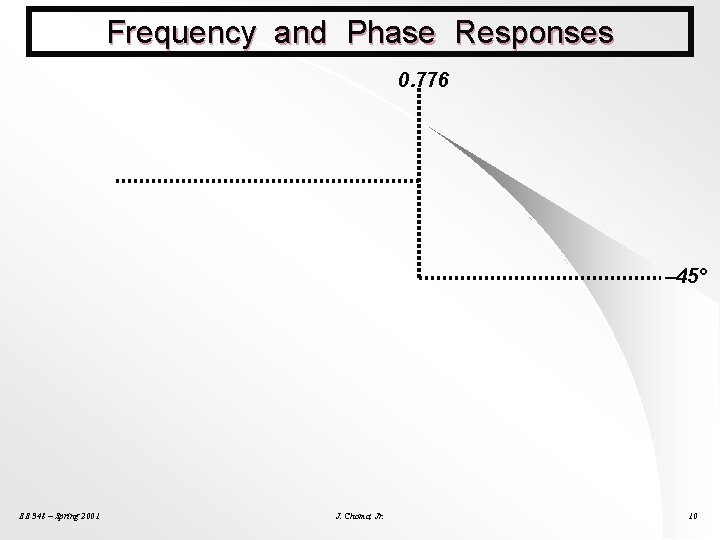

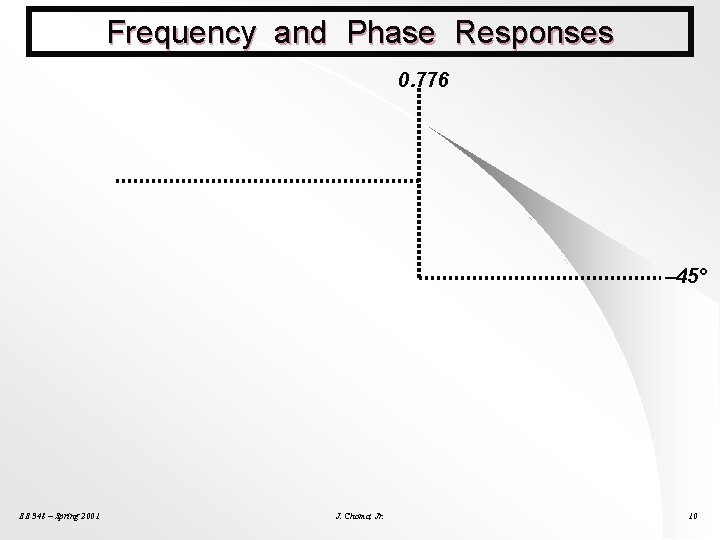

Frequency and Phase Responses 0. 776 – 45° EE 348 – Spring 2001 J. Choma, Jr. 10

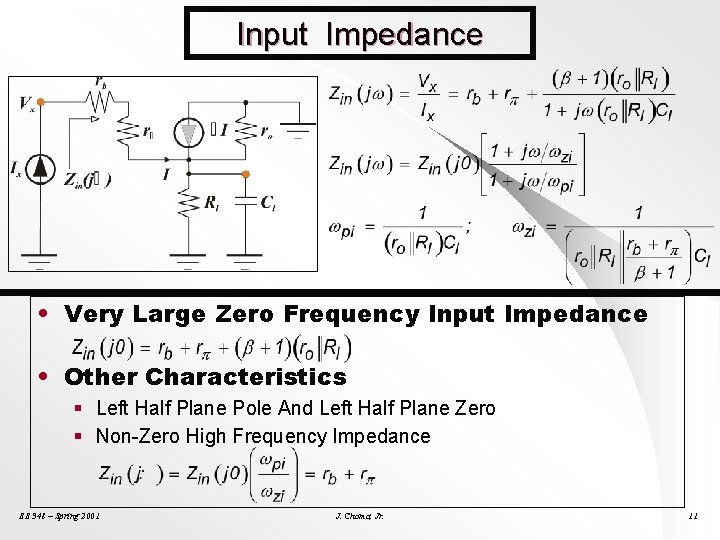

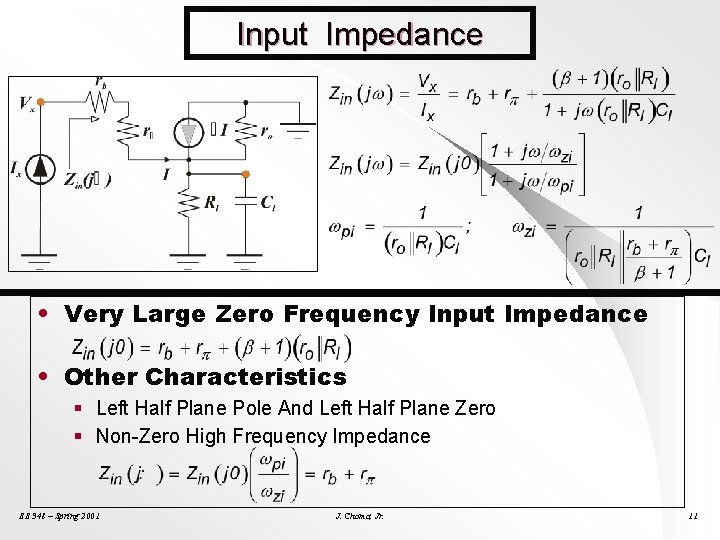

Input Impedance • Very Large Zero Frequency Input Impedance • Other Characteristics § Left Half Plane Pole And Left Half Plane Zero § Non-Zero High Frequency Impedance EE 348 – Spring 2001 J. Choma, Jr. 11

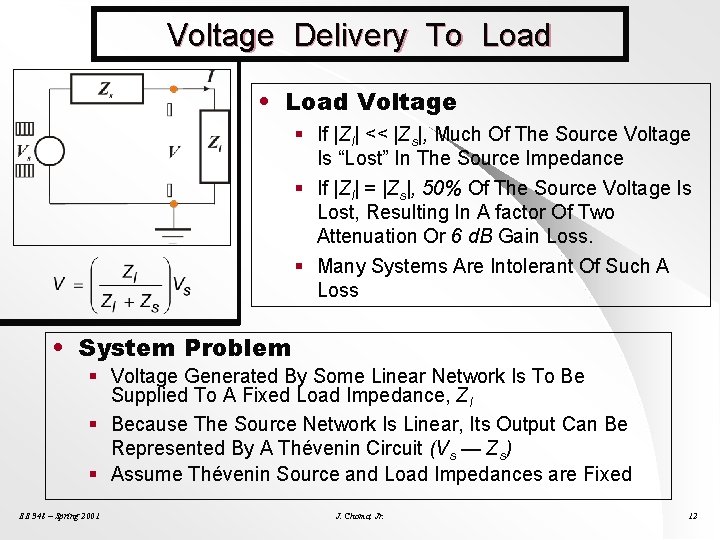

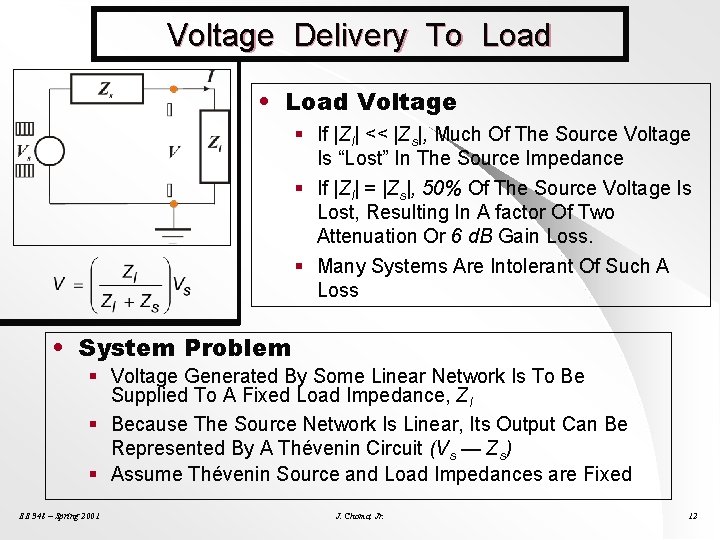

Voltage Delivery To Load • Load Voltage § If |Zl| << |Zs|, Much Of The Source Voltage Is “Lost” In The Source Impedance § If |Zl| = |Zs|, 50% Of The Source Voltage Is Lost, Resulting In A factor Of Two Attenuation Or 6 d. B Gain Loss. § Many Systems Are Intolerant Of Such A Loss • System Problem § Voltage Generated By Some Linear Network Is To Be Supplied To A Fixed Load Impedance, Zl § Because The Source Network Is Linear, Its Output Can Be Represented By A Thévenin Circuit (Vs — Zs) § Assume Thévenin Source and Load Impedances are Fixed EE 348 – Spring 2001 J. Choma, Jr. 12

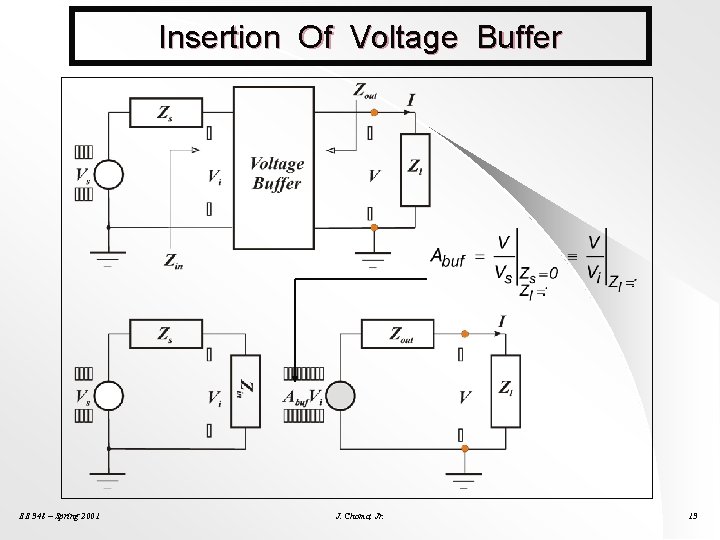

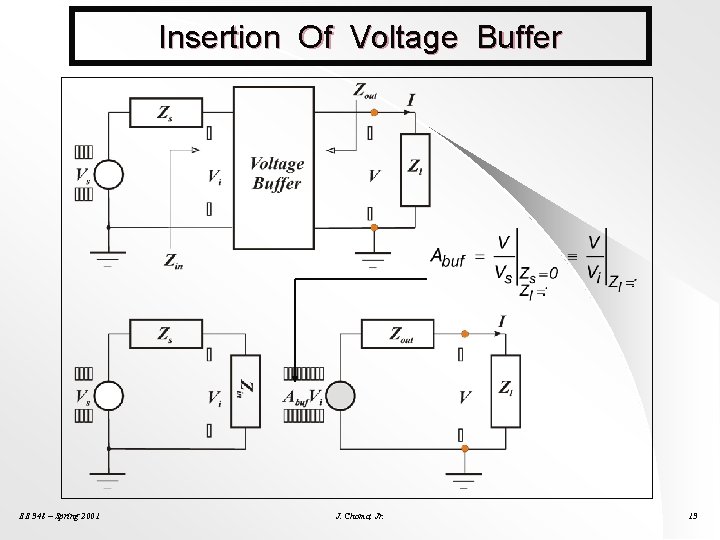

Insertion Of Voltage Buffer EE 348 – Spring 2001 J. Choma, Jr. 13

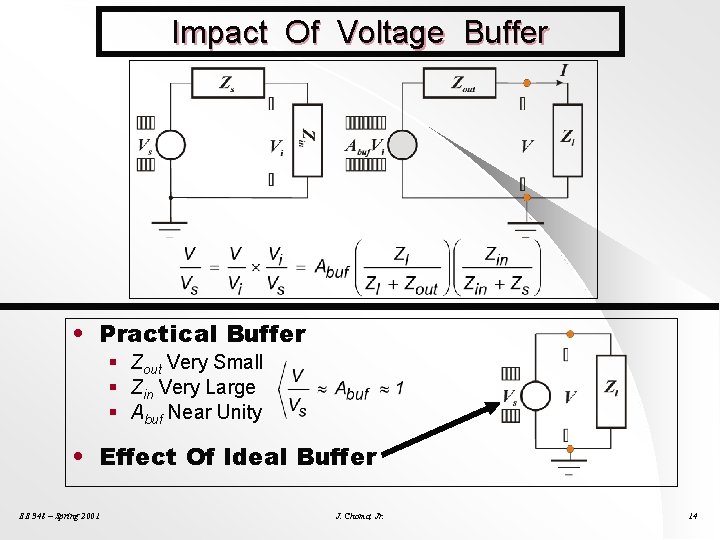

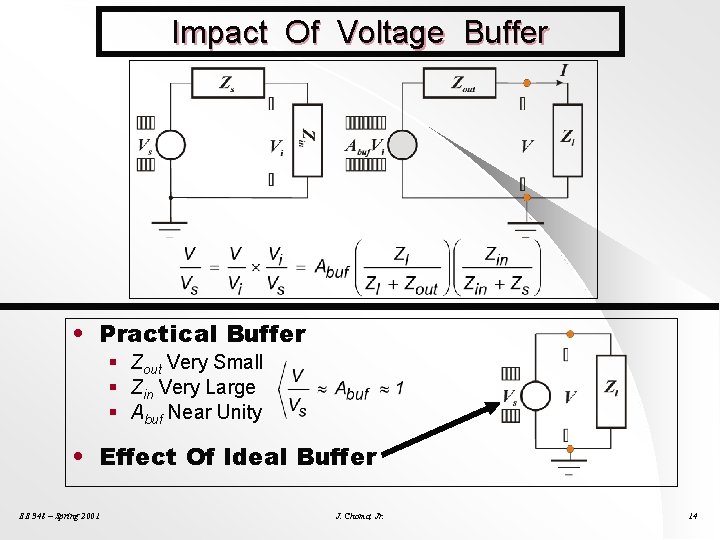

Impact Of Voltage Buffer • Practical Buffer § Zout Very Small § Zin Very Large § Abuf Near Unity • Effect Of Ideal Buffer EE 348 – Spring 2001 J. Choma, Jr. 14

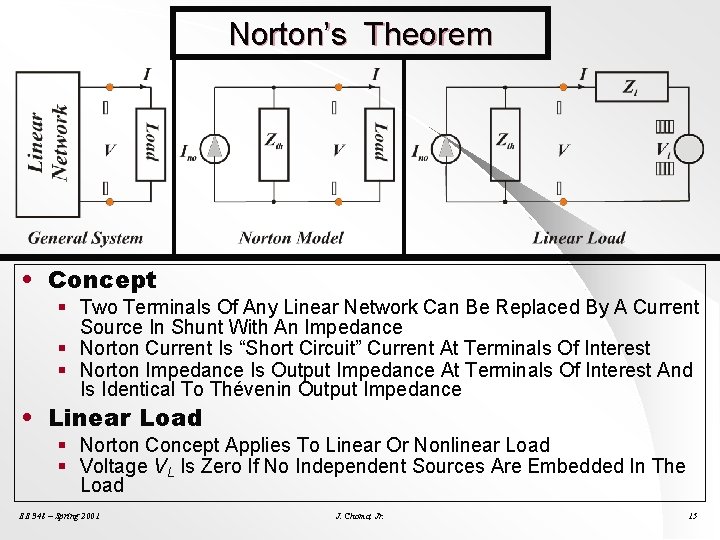

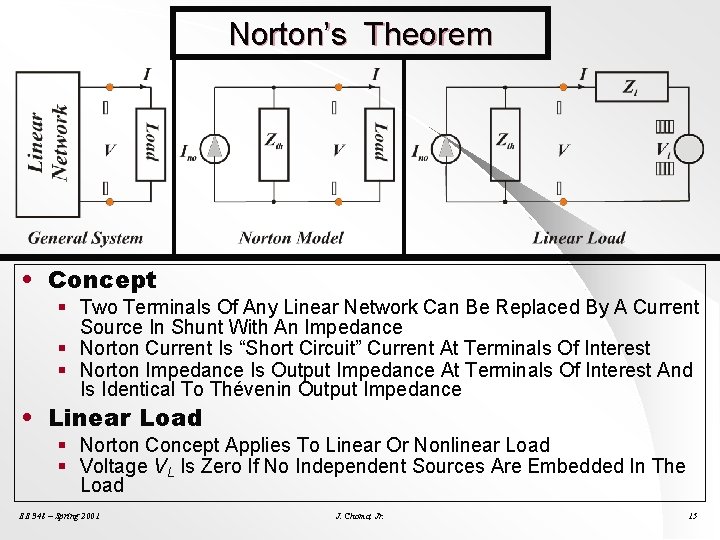

Norton’s Theorem • Concept § Two Terminals Of Any Linear Network Can Be Replaced By A Current Source In Shunt With An Impedance § Norton Current Is “Short Circuit” Current At Terminals Of Interest § Norton Impedance Is Output Impedance At Terminals Of Interest And Is Identical To Thévenin Output Impedance • Linear Load § Norton Concept Applies To Linear Or Nonlinear Load § Voltage VL Is Zero If No Independent Sources Are Embedded In The Load EE 348 – Spring 2001 J. Choma, Jr. 15

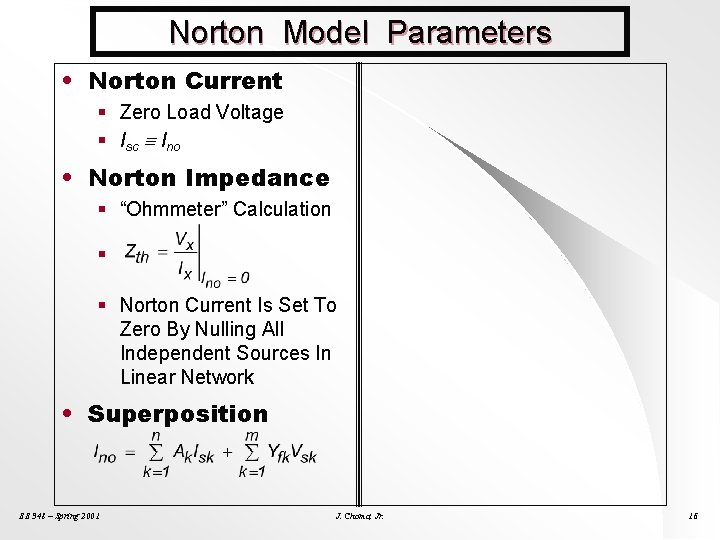

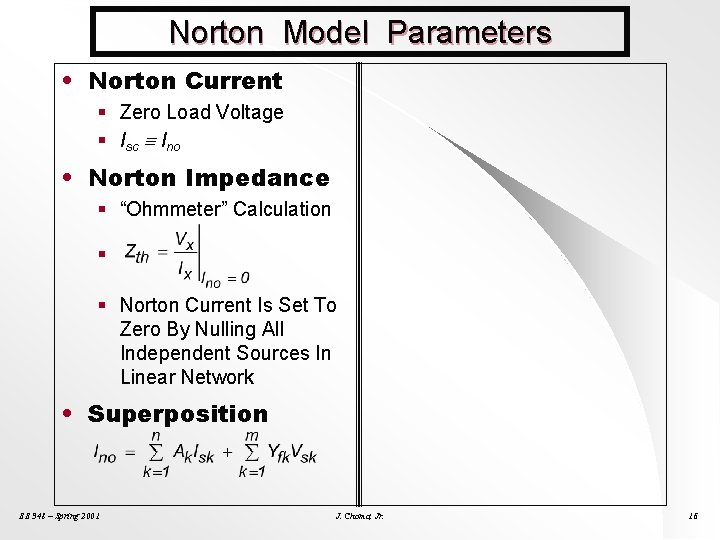

Norton Model Parameters • Norton Current § Zero Load Voltage § Isc Ino • Norton Impedance § “Ohmmeter” Calculation § § Norton Current Is Set To Zero By Nulling All Independent Sources In Linear Network • Superposition EE 348 – Spring 2001 J. Choma, Jr. 16

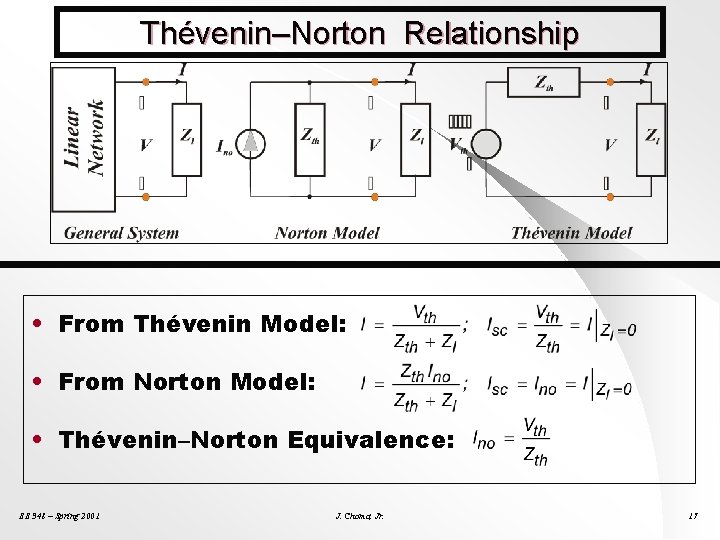

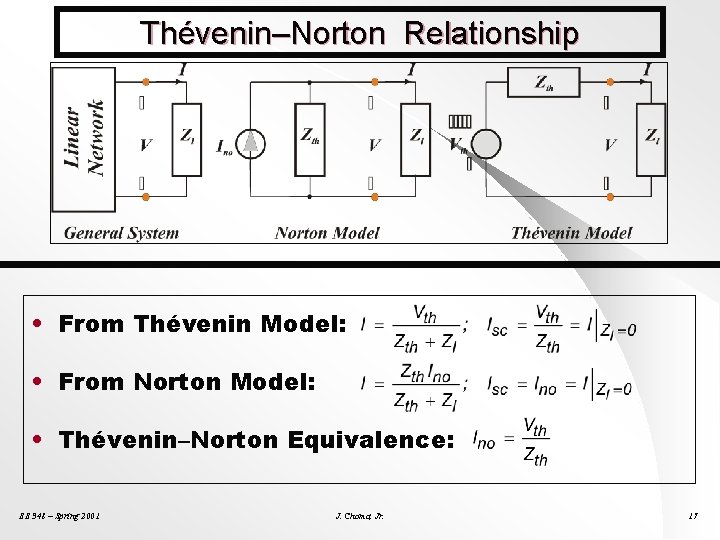

Thévenin–Norton Relationship • From Thévenin Model: • From Norton Model: • Thévenin–Norton Equivalence: EE 348 – Spring 2001 J. Choma, Jr. 17

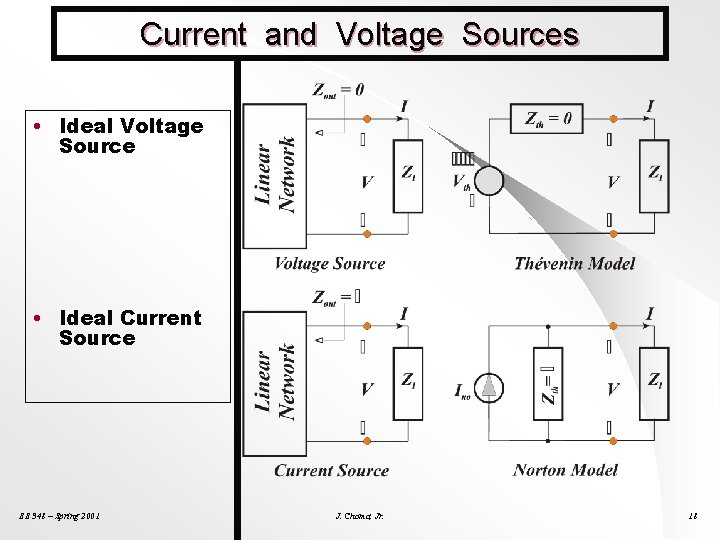

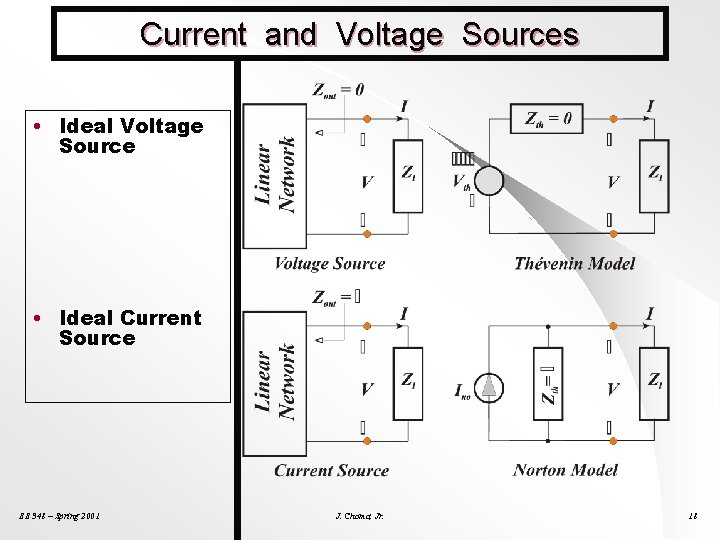

Current and Voltage Sources • Ideal Voltage Source • Ideal Current Source EE 348 – Spring 2001 J. Choma, Jr. 18

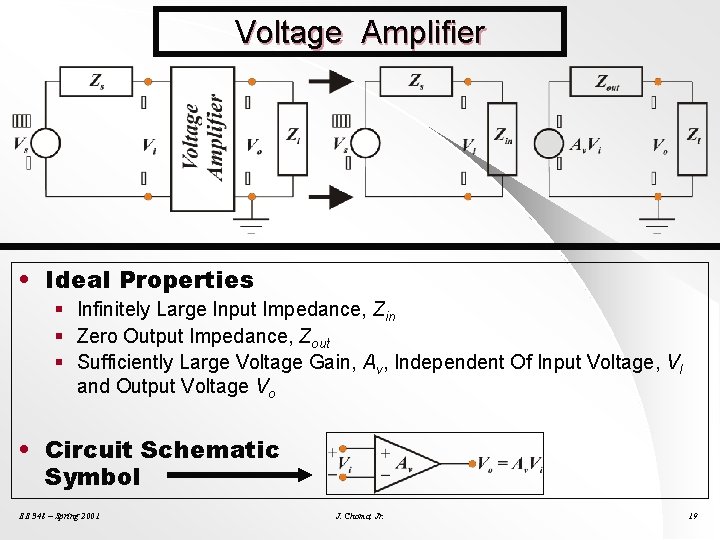

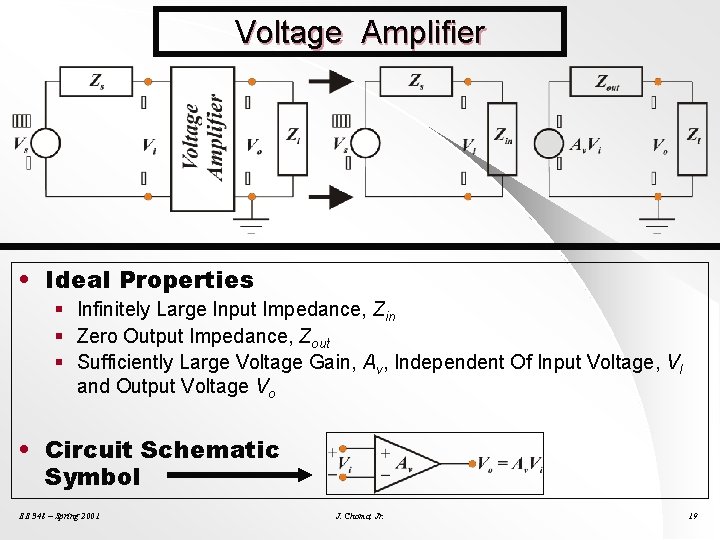

Voltage Amplifier • Ideal Properties § Infinitely Large Input Impedance, Zin § Zero Output Impedance, Zout § Sufficiently Large Voltage Gain, Av, Independent Of Input Voltage, VI and Output Voltage Vo • Circuit Schematic Symbol EE 348 – Spring 2001 J. Choma, Jr. 19

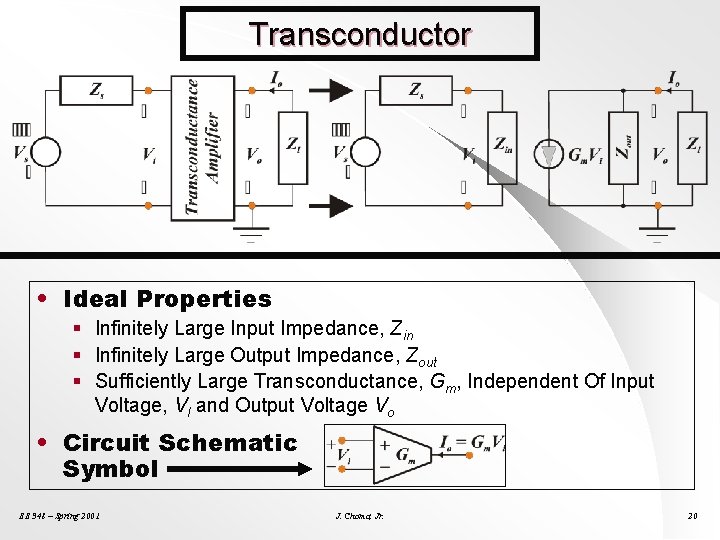

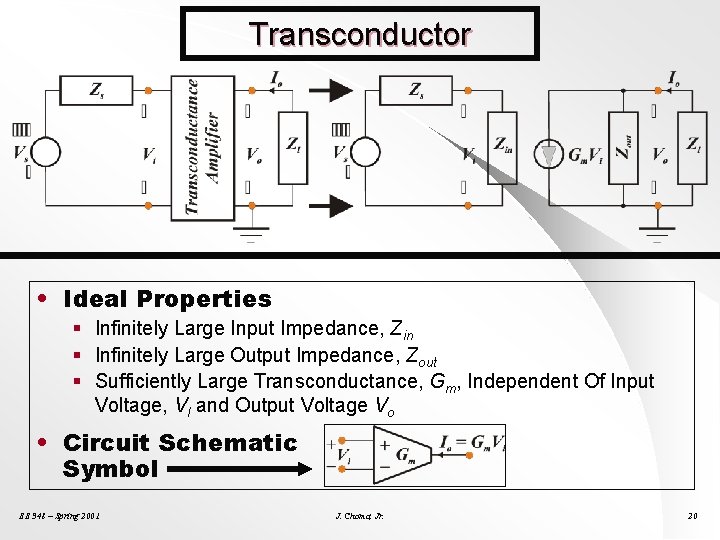

Transconductor • Ideal Properties § Infinitely Large Input Impedance, Zin § Infinitely Large Output Impedance, Zout § Sufficiently Large Transconductance, Gm, Independent Of Input Voltage, VI and Output Voltage Vo • Circuit Schematic Symbol EE 348 – Spring 2001 J. Choma, Jr. 20

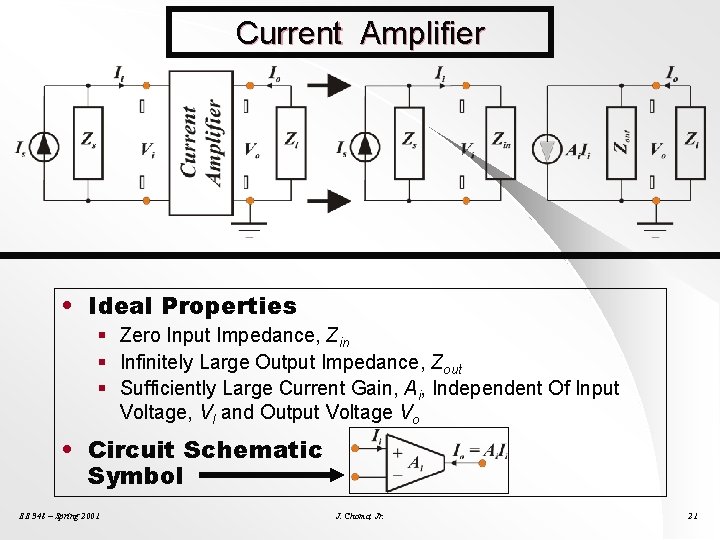

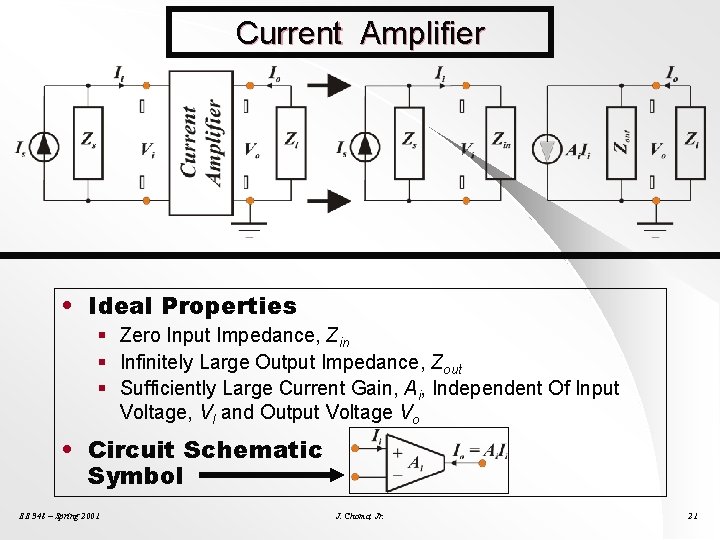

Current Amplifier • Ideal Properties § Zero Input Impedance, Zin § Infinitely Large Output Impedance, Zout § Sufficiently Large Current Gain, Ai, Independent Of Input Voltage, VI and Output Voltage Vo • Circuit Schematic Symbol EE 348 – Spring 2001 J. Choma, Jr. 21

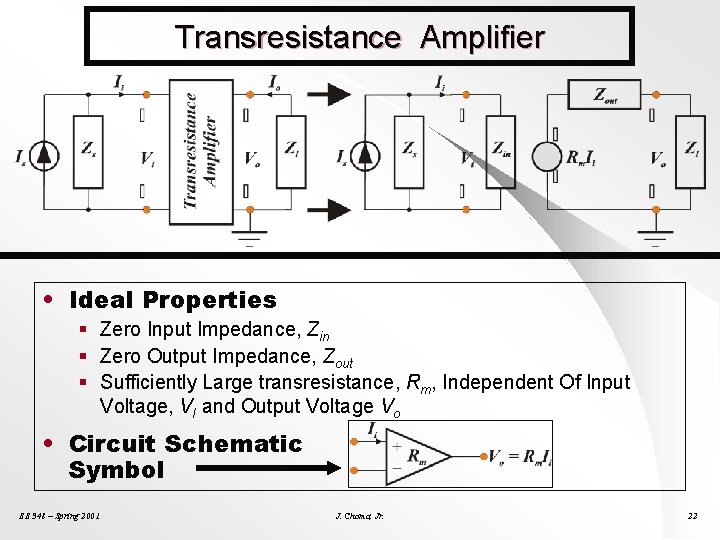

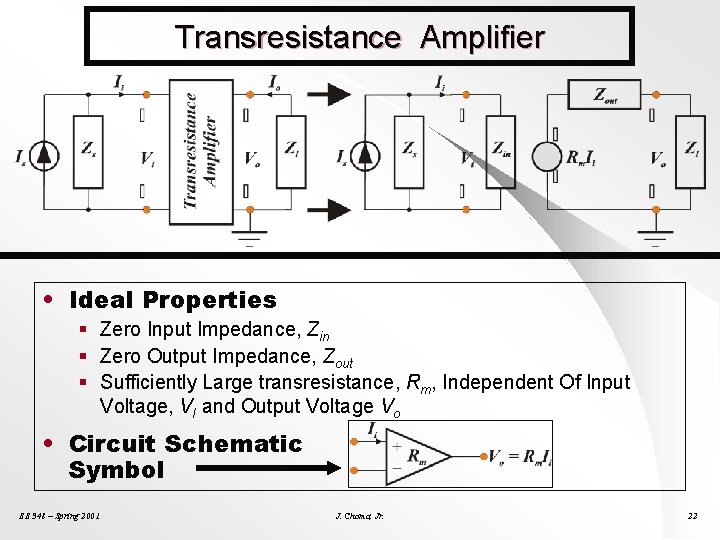

Transresistance Amplifier • Ideal Properties § Zero Input Impedance, Zin § Zero Output Impedance, Zout § Sufficiently Large transresistance, Rm, Independent Of Input Voltage, VI and Output Voltage Vo • Circuit Schematic Symbol EE 348 – Spring 2001 J. Choma, Jr. 22

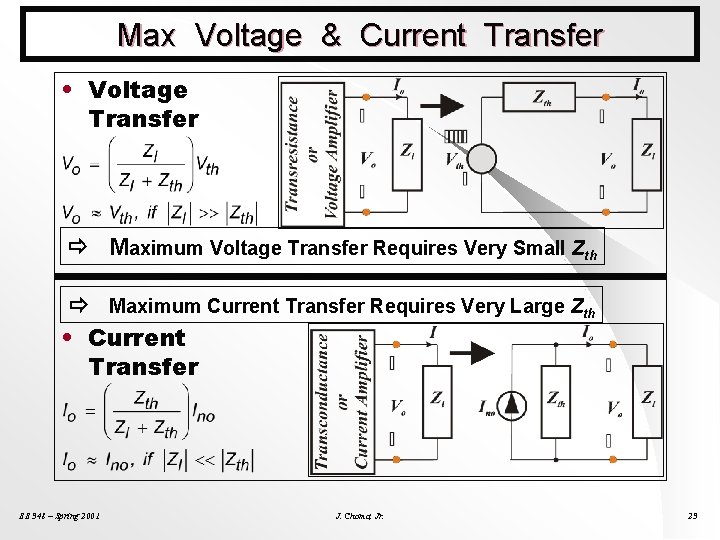

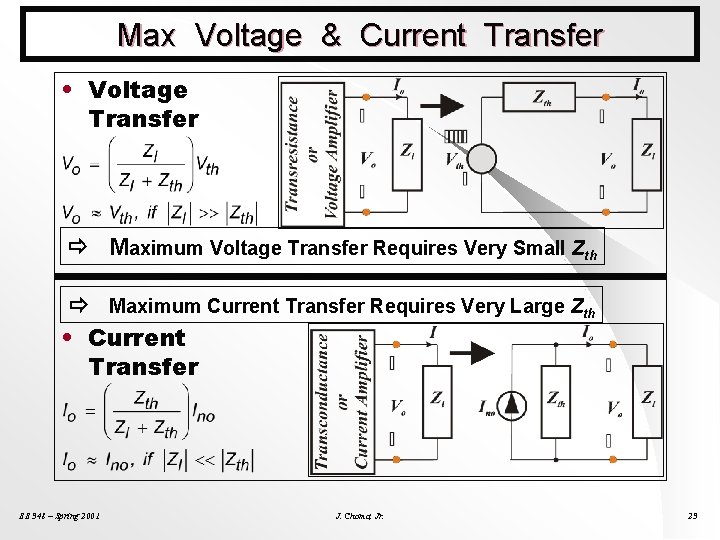

Max Voltage & Current Transfer • Voltage Transfer Maximum Voltage Transfer Requires Very Small Zth Maximum Current Transfer Requires Very Large Zth • Current Transfer EE 348 – Spring 2001 J. Choma, Jr. 23

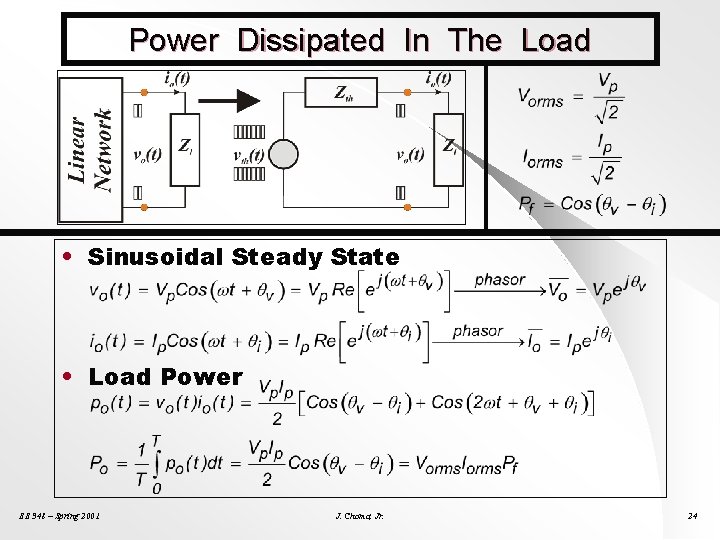

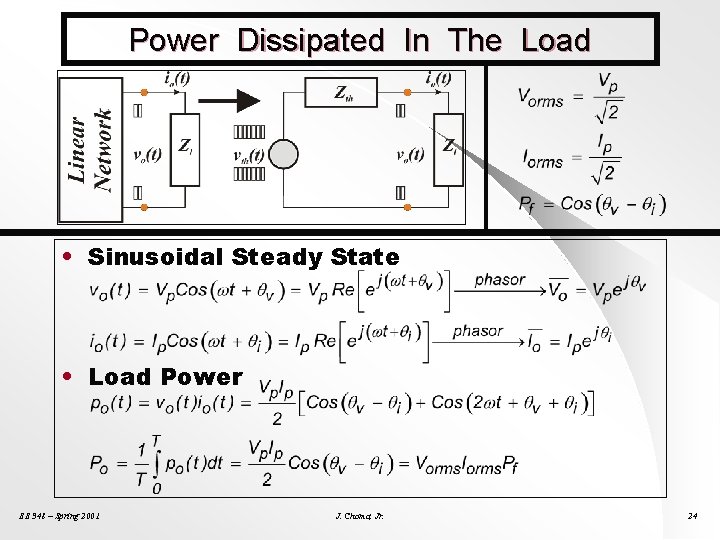

Power Dissipated In The Load • Sinusoidal Steady State • Load Power EE 348 – Spring 2001 J. Choma, Jr. 24

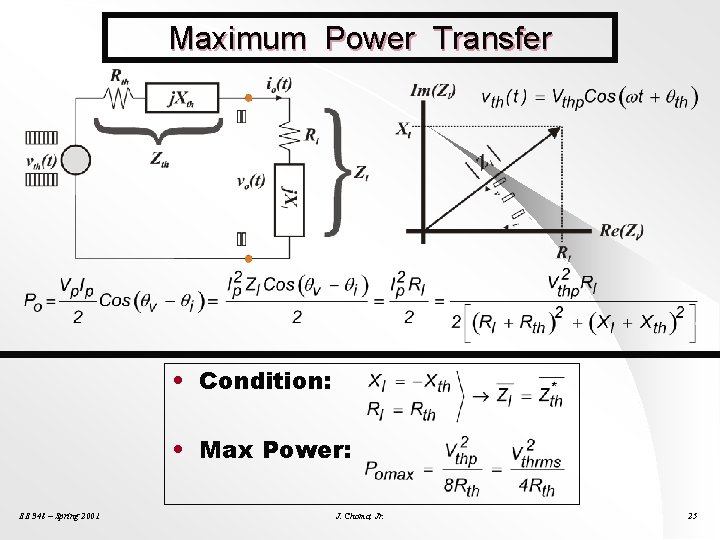

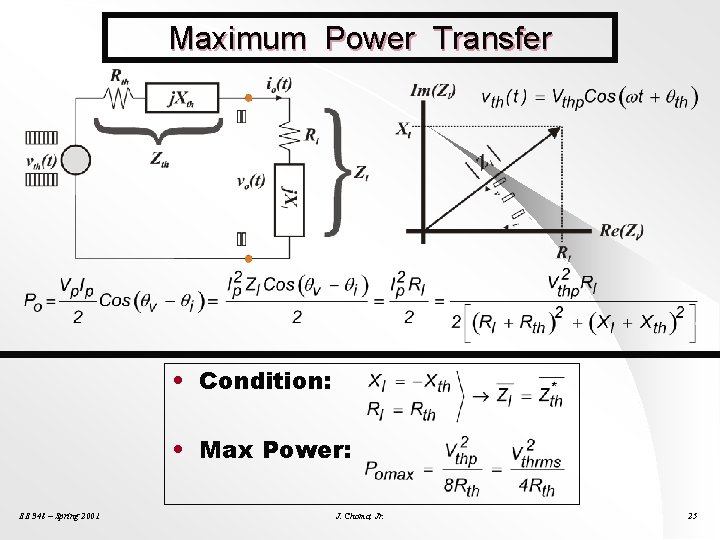

Maximum Power Transfer • Condition: • Max Power: EE 348 – Spring 2001 J. Choma, Jr. 25

Example– 50 Transmission Line • Parameters § Antenna RMS Voltage Signal Is 10 V § Transmission Line Coupling To RF Stage Behaves Electrically As A 50 Ohm Resistance • Power To RF Input Port § Maximized When RF Input Impedance Is 50 Ohms § • d. Bm Value: EE 348 – Spring 2001 J. Choma, Jr. 26

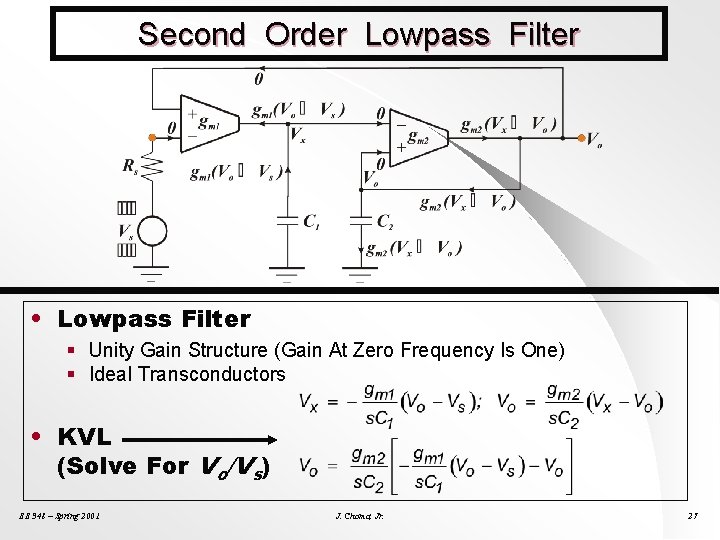

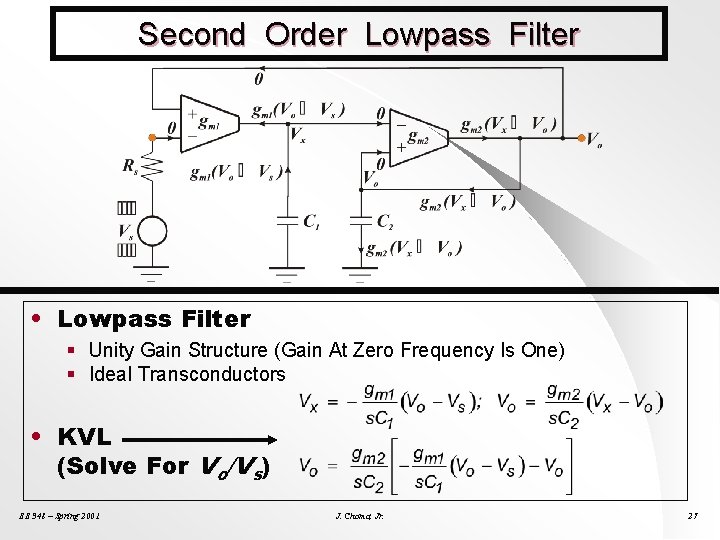

Second Order Lowpass Filter • Lowpass Filter § Unity Gain Structure (Gain At Zero Frequency Is One) § Ideal Transconductors • KVL (Solve For Vo/Vs) EE 348 – Spring 2001 J. Choma, Jr. 27

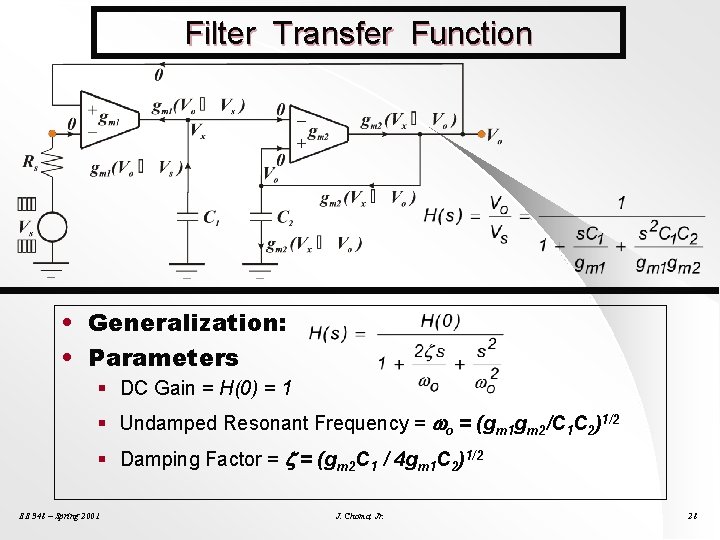

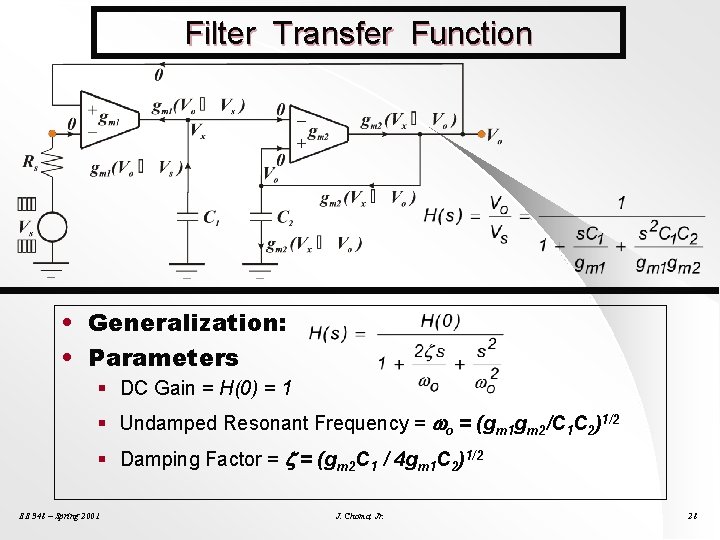

Filter Transfer Function • Generalization: • Parameters § DC Gain = H(0) = 1 § Undamped Resonant Frequency = o = (gm 1 gm 2/C 1 C 2)1/2 § Damping Factor = = (gm 2 C 1 / 4 gm 1 C 2)1/2 EE 348 – Spring 2001 J. Choma, Jr. 28

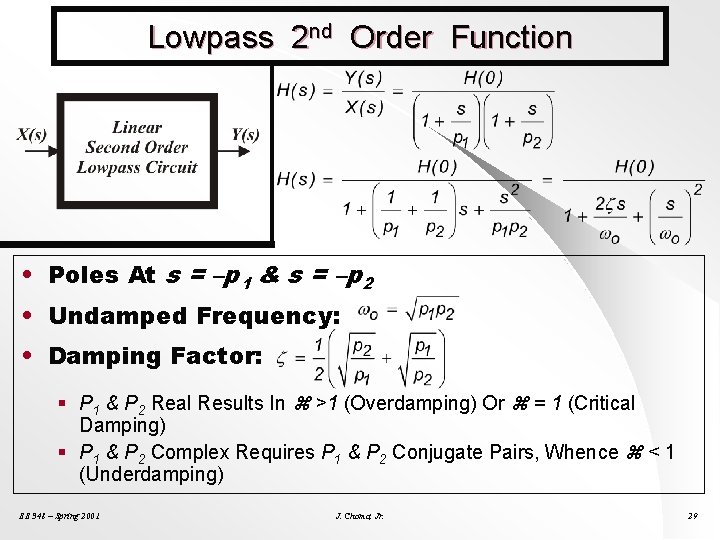

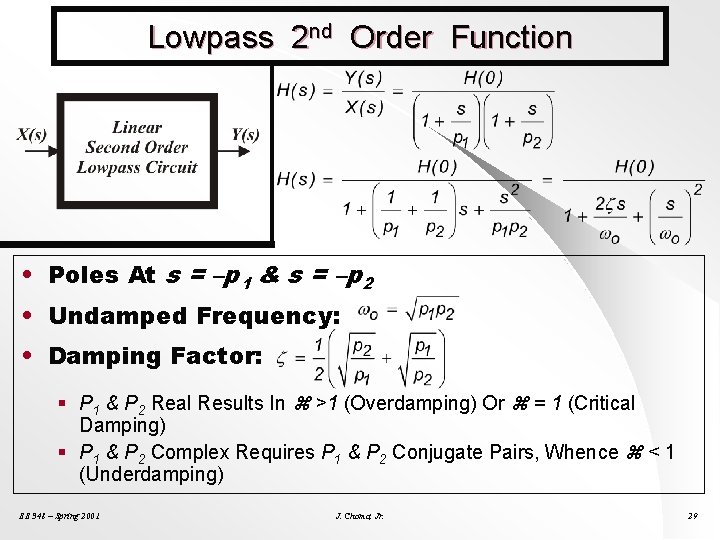

Lowpass 2 nd Order Function • Poles At s = –p 1 & s = –p 2 • Undamped Frequency: • Damping Factor: § P 1 & P 2 Real Results In >1 (Overdamping) Or = 1 (Critical Damping) § P 1 & P 2 Complex Requires P 1 & P 2 Conjugate Pairs, Whence < 1 (Underdamping) EE 348 – Spring 2001 J. Choma, Jr. 29

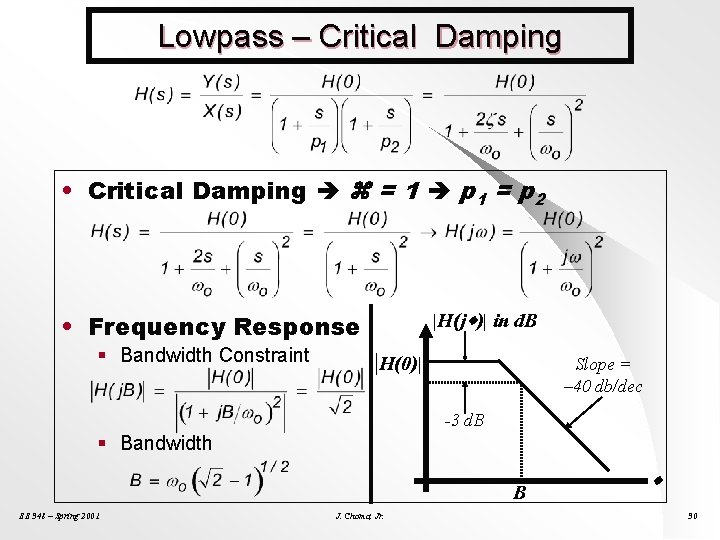

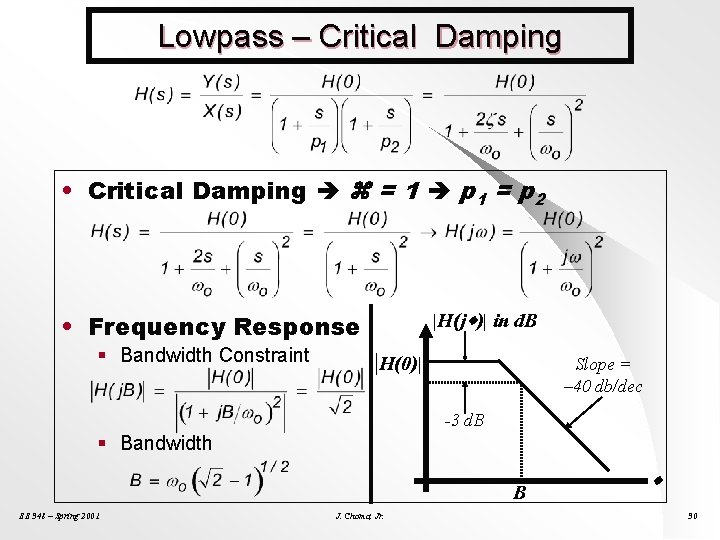

Lowpass – Critical Damping • Critical Damping = 1 p 1 = p 2 • Frequency Response § Bandwidth Constraint |H(j )| in d. B |H(0)| Slope = – 40 db/dec -3 d. B § Bandwidth B EE 348 – Spring 2001 J. Choma, Jr. 30

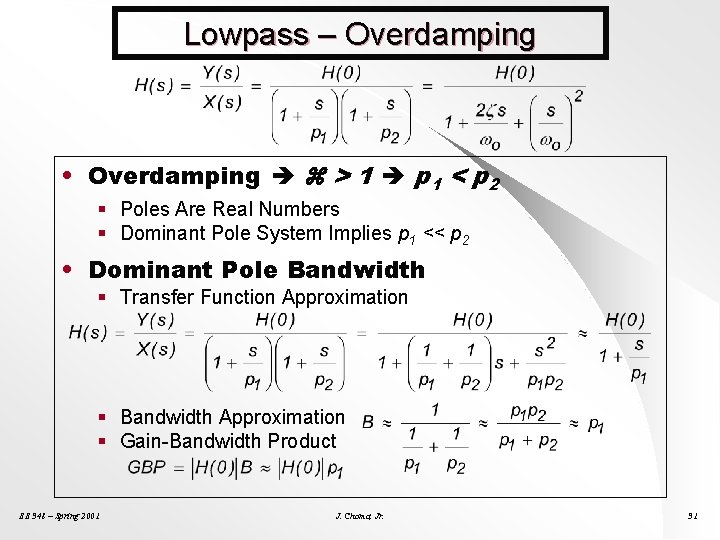

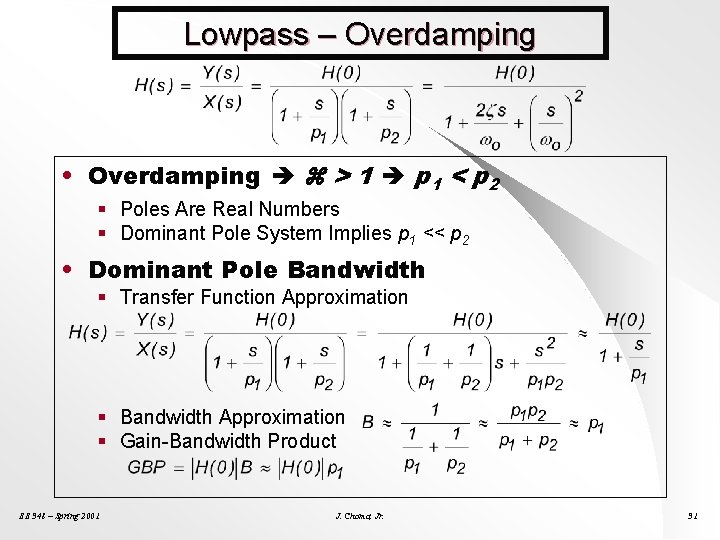

Lowpass – Overdamping • Overdamping > 1 p 1 < p 2 § Poles Are Real Numbers § Dominant Pole System Implies p 1 << p 2 • Dominant Pole Bandwidth § Transfer Function Approximation § Bandwidth Approximation § Gain-Bandwidth Product EE 348 – Spring 2001 J. Choma, Jr. 31

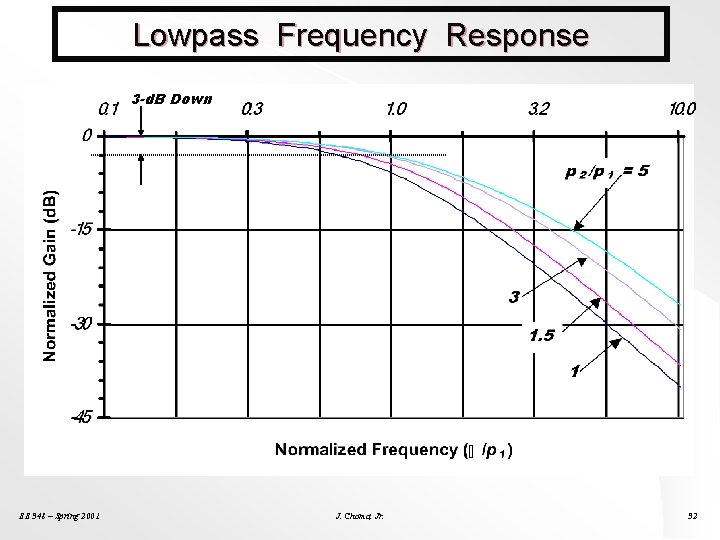

Lowpass Frequency Response 3 -d. B Down EE 348 – Spring 2001 J. Choma, Jr. 32

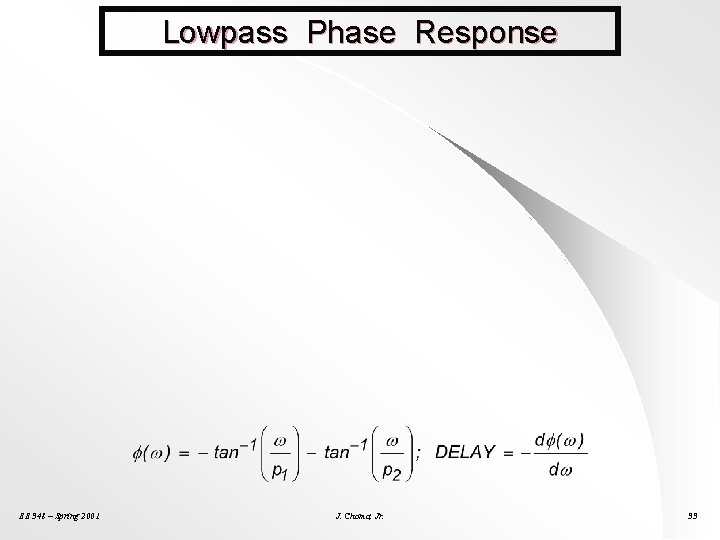

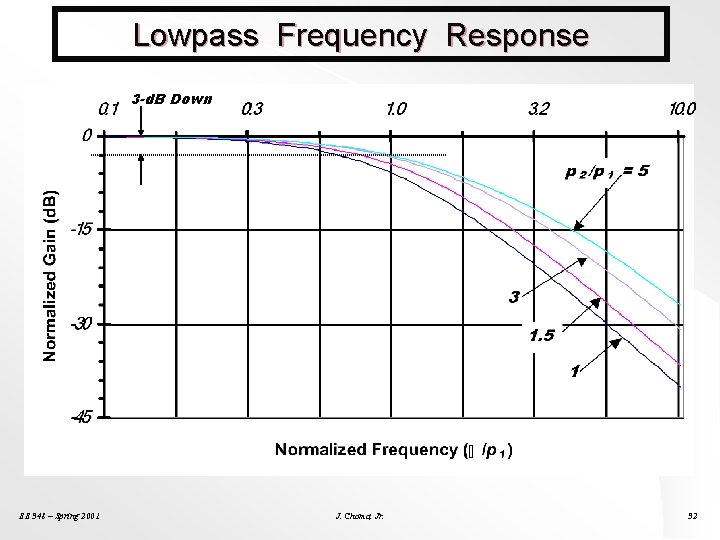

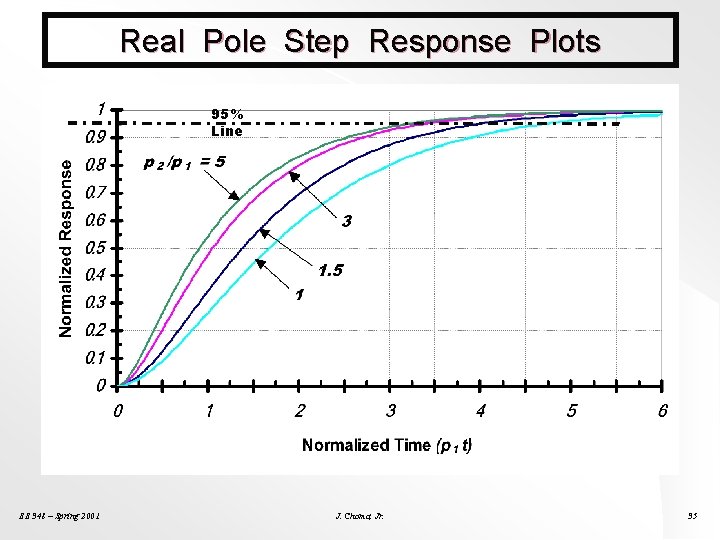

Lowpass Phase Response EE 348 – Spring 2001 J. Choma, Jr. 33

![Lowpass Step Response Input Is Unit Step Xs 1s Overdamped Lowpass Step Response • Input Is Unit Step [X(s) = 1/s] • Overdamped (](https://slidetodoc.com/presentation_image/0f67ecaecbb9b3aed8973585b6405379/image-34.jpg)

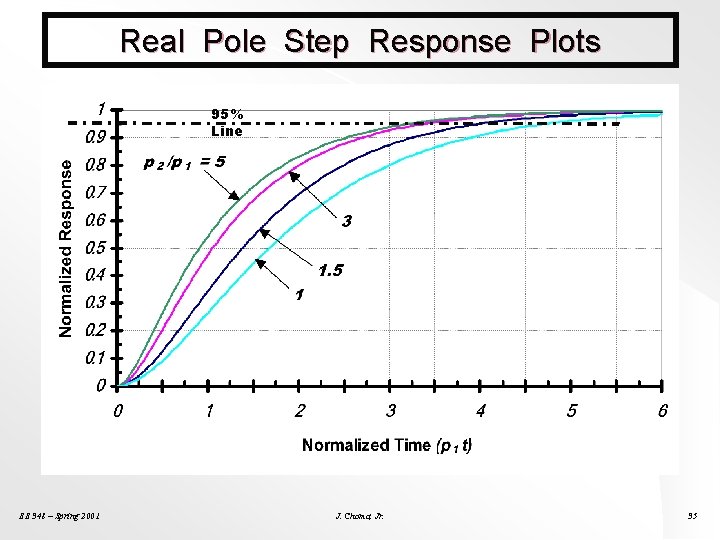

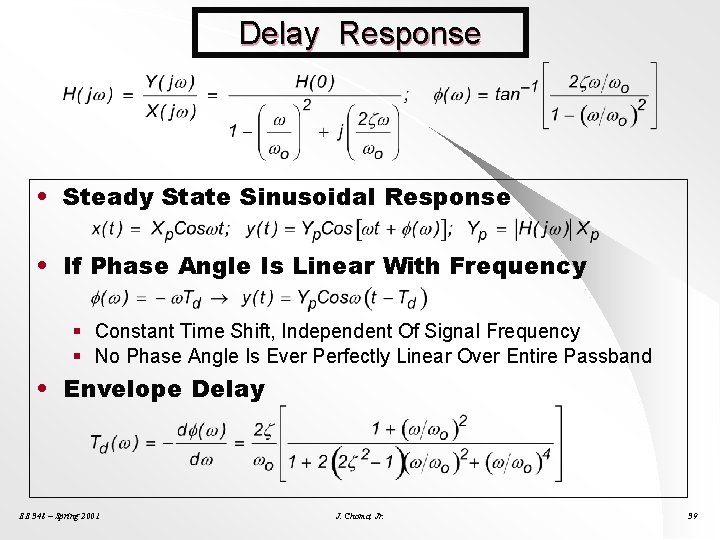

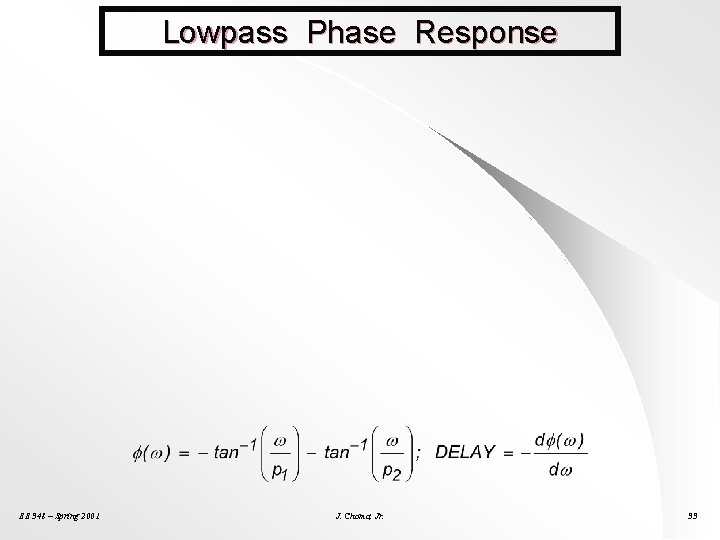

Lowpass Step Response • Input Is Unit Step [X(s) = 1/s] • Overdamped ( > 1) • Critical Damping ( = 1 o = p 1 = p 2) EE 348 – Spring 2001 J. Choma, Jr. 34

Real Pole Step Response Plots 95% Line EE 348 – Spring 2001 J. Choma, Jr. 35

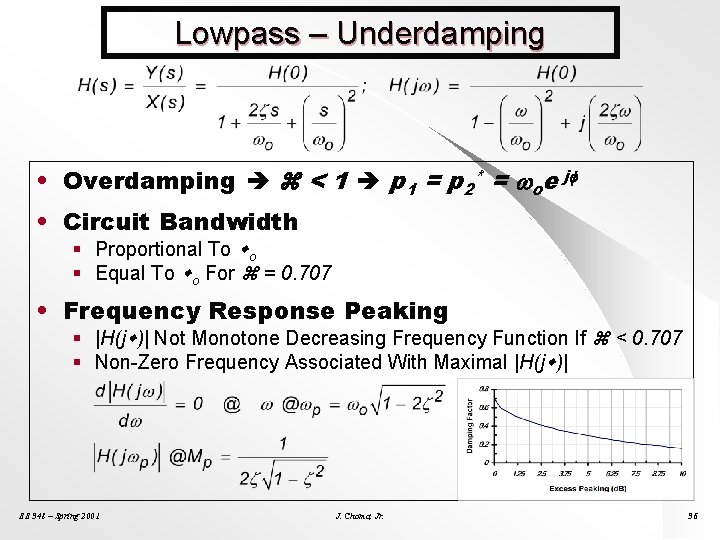

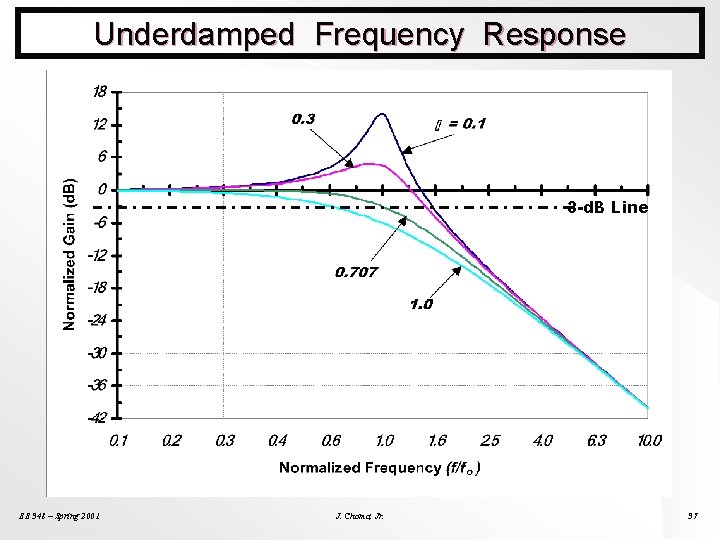

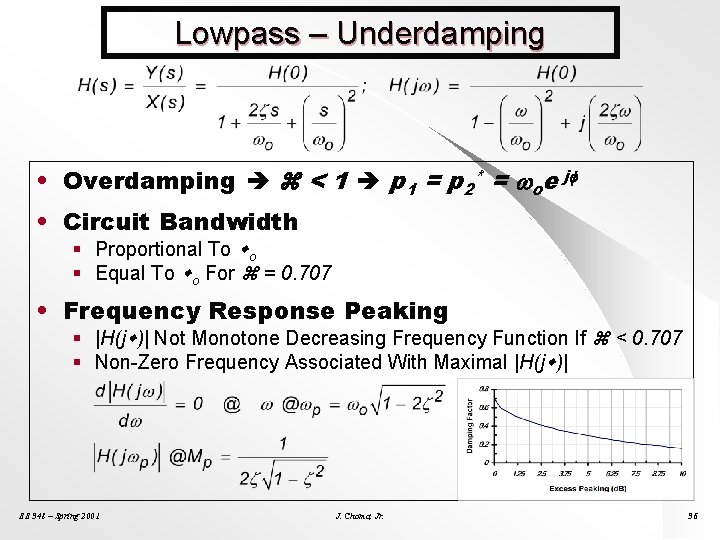

Lowpass – Underdamping • Overdamping < 1 p 1 = p 2* = oe j • Circuit Bandwidth § Proportional To o § Equal To o For = 0. 707 • Frequency Response Peaking § |H(j )| Not Monotone Decreasing Frequency Function If < 0. 707 § Non-Zero Frequency Associated With Maximal |H(j )| EE 348 – Spring 2001 J. Choma, Jr. 36

Underdamped Frequency Response 3 -d. B Line EE 348 – Spring 2001 J. Choma, Jr. 37

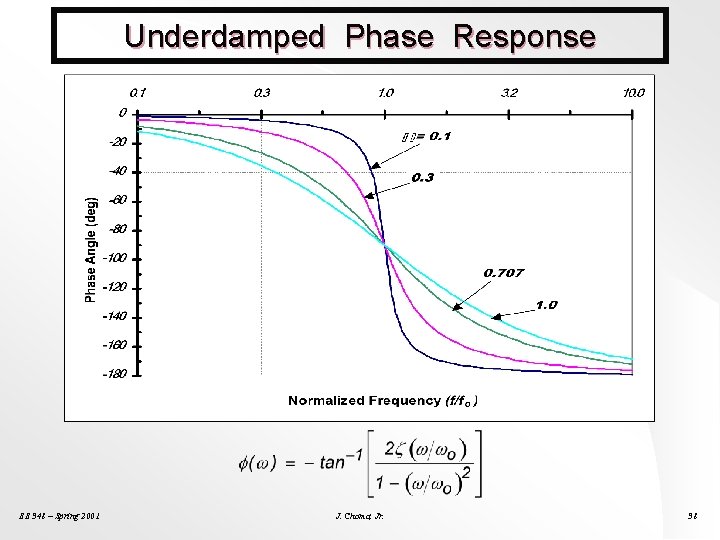

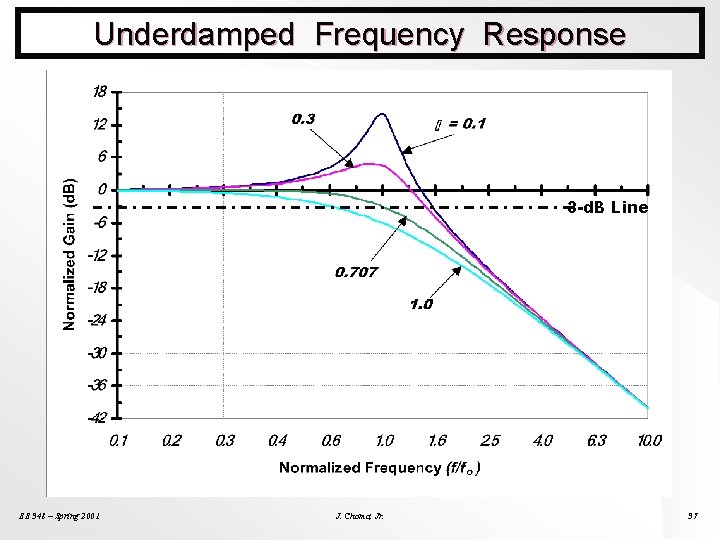

Underdamped Phase Response EE 348 – Spring 2001 J. Choma, Jr. 38

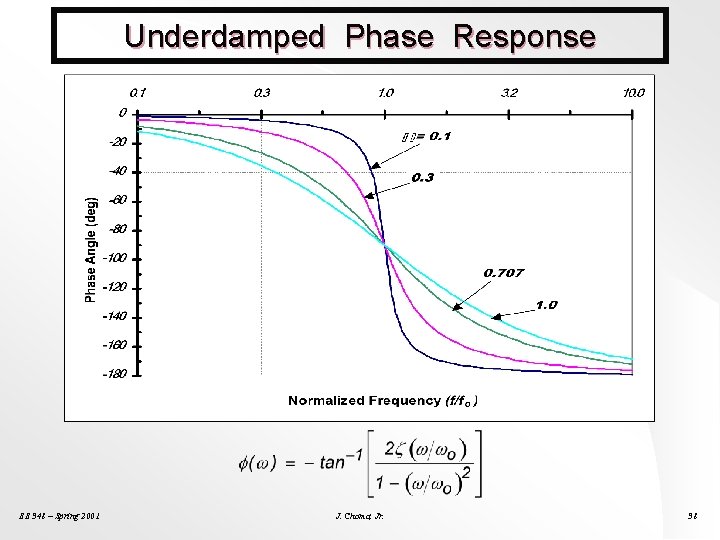

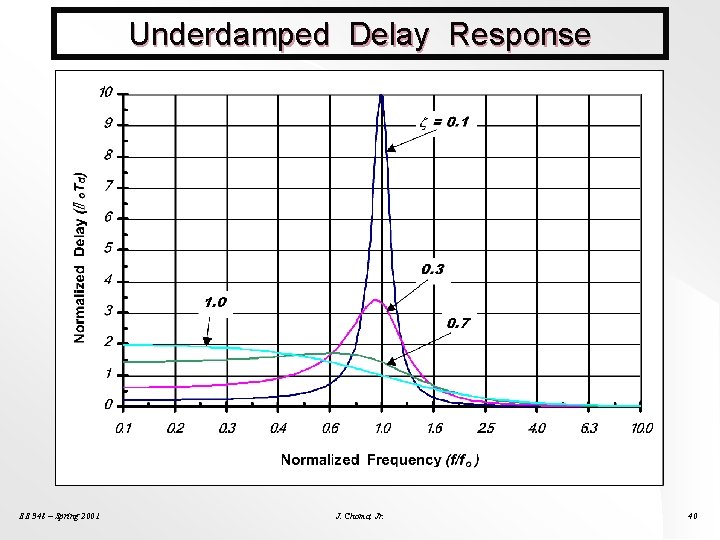

Delay Response • Steady State Sinusoidal Response • If Phase Angle Is Linear With Frequency § Constant Time Shift, Independent Of Signal Frequency § No Phase Angle Is Ever Perfectly Linear Over Entire Passband • Envelope Delay EE 348 – Spring 2001 J. Choma, Jr. 39

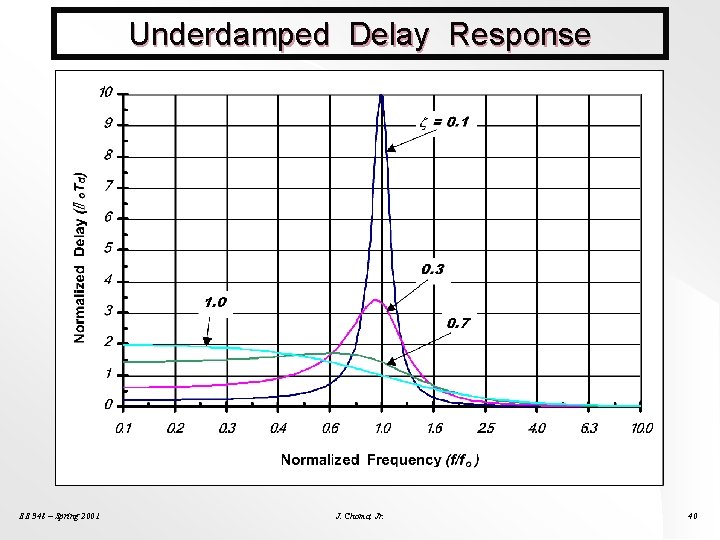

Underdamped Delay Response EE 348 – Spring 2001 J. Choma, Jr. 40

![Underdamped Step Analysis Input Is Unit Step Xs 1s Underdamped Underdamped Step Analysis • Input Is Unit Step [X(s) = 1/s] • Underdamped (](https://slidetodoc.com/presentation_image/0f67ecaecbb9b3aed8973585b6405379/image-41.jpg)

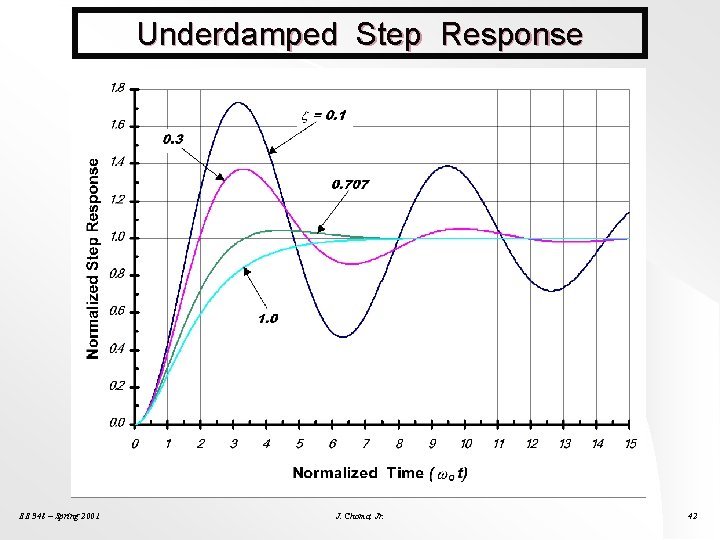

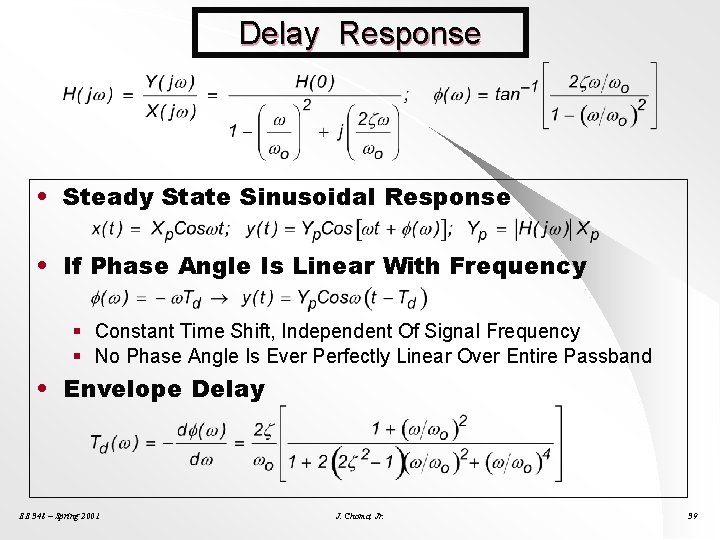

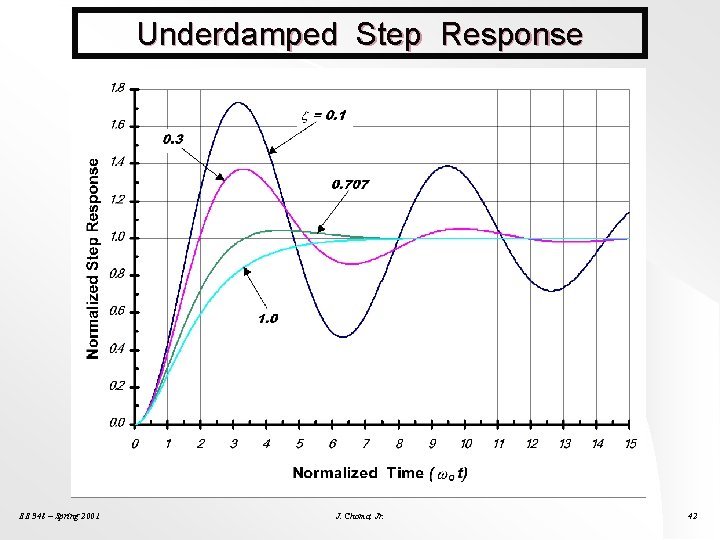

Underdamped Step Analysis • Input Is Unit Step [X(s) = 1/s] • Underdamped ( < 1) • Characteristics § Damped Oscillations § Oscillation For Zero Damping ( = 0) § Undamped Frequency Is Oscillatory Frequency For Zero Damping EE 348 – Spring 2001 J. Choma, Jr. 41

Underdamped Step Response EE 348 – Spring 2001 J. Choma, Jr. 42