ELEC 52706270 Spring 2013 LowPower Design of Electronic

- Slides: 36

ELEC 5270/6270 Spring 2013 Low-Power Design of Electronic Circuits Energy Source Design Vishwani D. Agrawal James J. Danaher Professor Dept. of Electrical and Computer Engineering Auburn University, Auburn, AL 36849 vagrawal@eng. auburn. edu http: //www. eng. auburn. edu/~vagrawal/COURSE/E 6270_Spr 13/course. html Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 1

Outline l Energy source optimization methods l l l Voltage and Clock Management Functional Management Voltage and Clock Management (DVFS) l l Background l A typical system powered with battery l Battery Simulation Model l DC to DC converter Problem statement l Case I : System is Performance bound l Case II : A higher battery lifetime is required l Case III : Battery weight or size is constrained Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 2

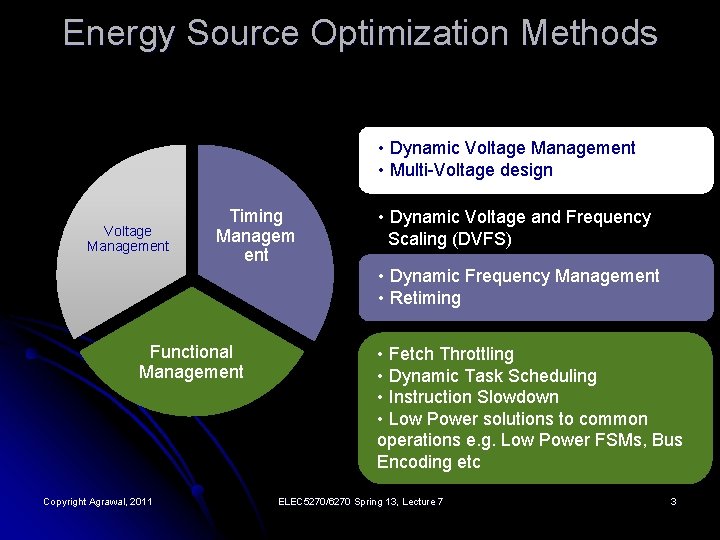

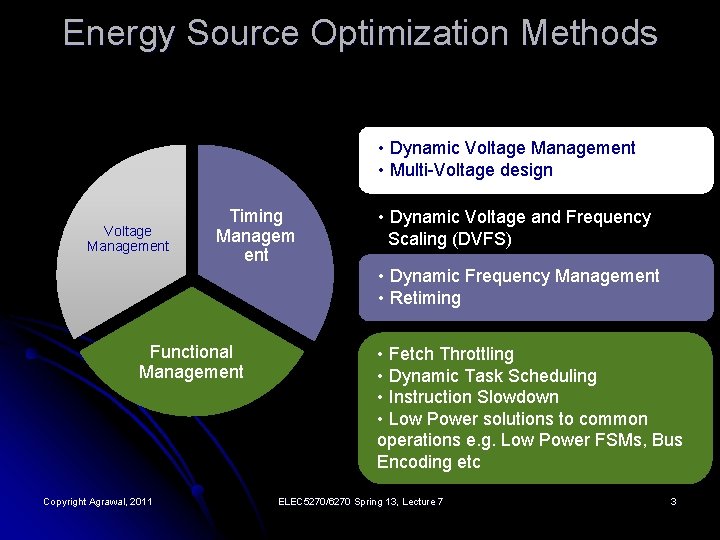

Energy Source Optimization Methods • Dynamic Voltage Management • Multi-Voltage design Voltage Management Timing Managem ent • Dynamic Voltage and Frequency Scaling (DVFS) • Dynamic Frequency Management • Retiming Functional Management Copyright Agrawal, 2011 • Fetch Throttling • Dynamic Task Scheduling • Instruction Slowdown • Low Power solutions to common operations e. g. Low Power FSMs, Bus Encoding etc ELEC 5270/6270 Spring 13, Lecture 7 3

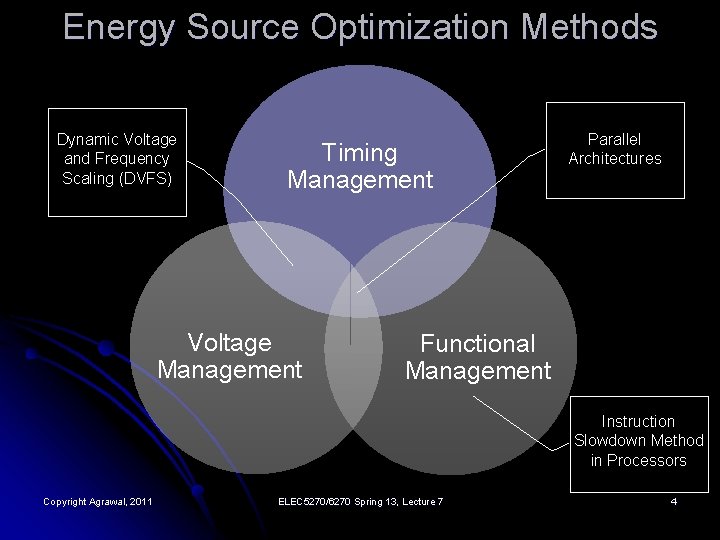

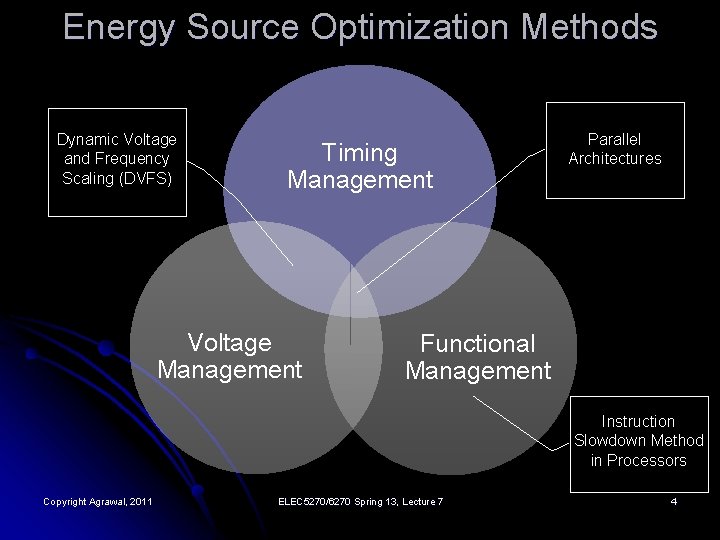

Energy Source Optimization Methods Dynamic Voltage and Frequency Scaling (DVFS) Timing Management Voltage Management Parallel Architectures Functional Management Instruction Slowdown Method in Processors Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 4

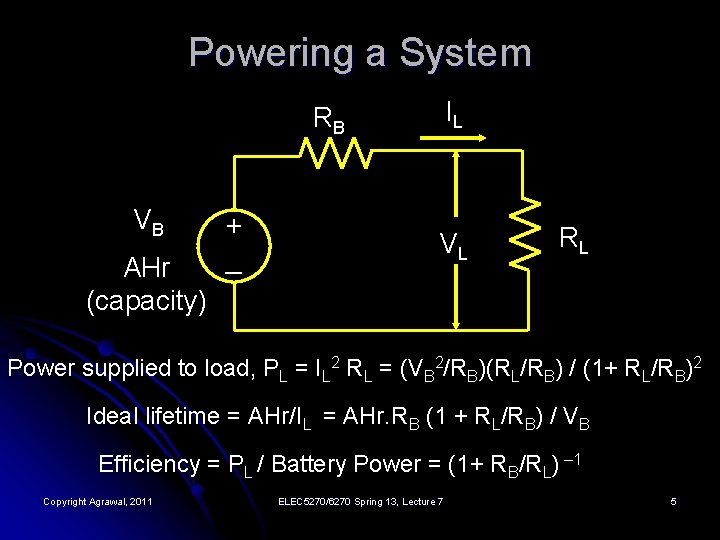

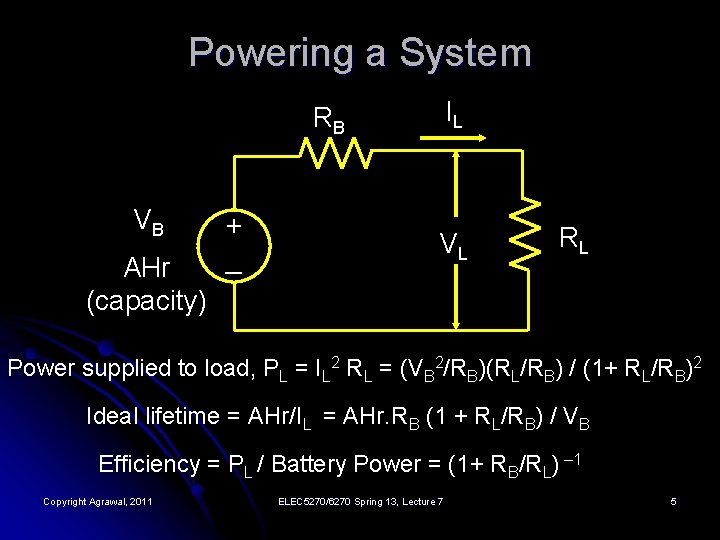

Powering a System IL RB VB AHr (capacity) + _ VL RL Power supplied to load, PL = IL 2 RL = (VB 2/RB)(RL/RB) / (1+ RL/RB)2 Ideal lifetime = AHr/IL = AHr. RB (1 + RL/RB) / VB Efficiency = PL / Battery Power = (1+ RB/RL) – 1 Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 5

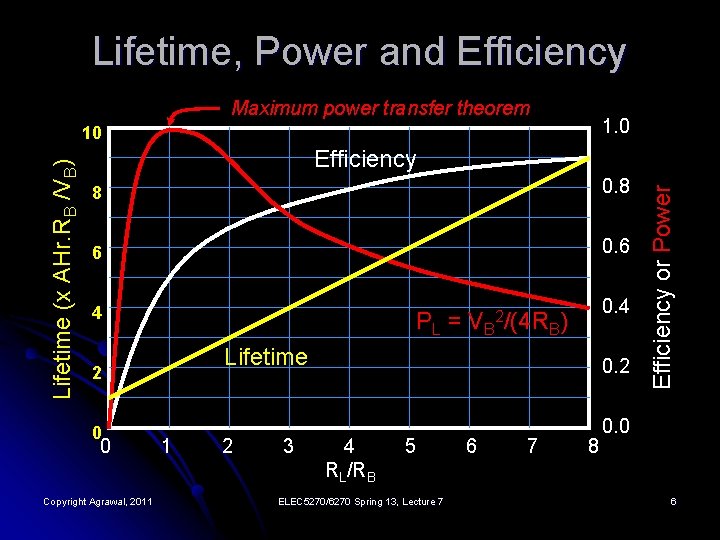

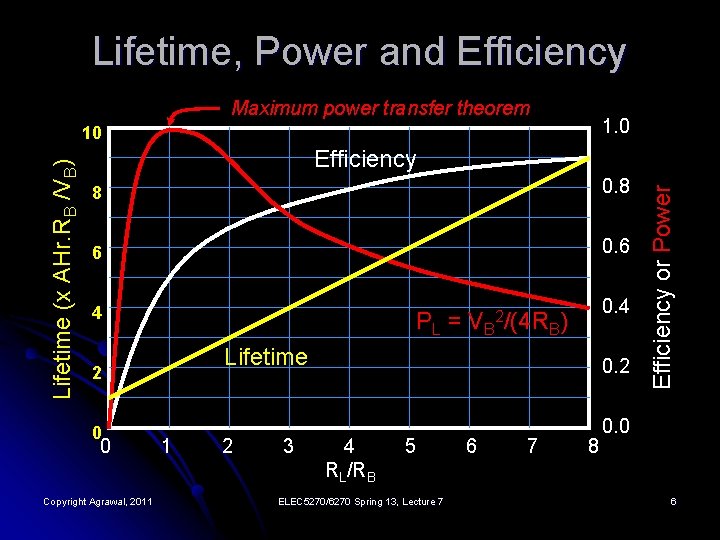

Lifetime, Power and Efficiency Maximum power transfer theorem 1. 0 Efficiency 8 0. 8 6 0. 6 4 PL = V B 0 Copyright Agrawal, 2011 0. 4 B) Lifetime 2 0 2/(4 R 1 2 3 0. 2 4 RL/RB 5 ELEC 5270/6270 Spring 13, Lecture 7 6 7 8 Efficiency or Power Lifetime (x AHr. RB /VB) 10 0. 0 6

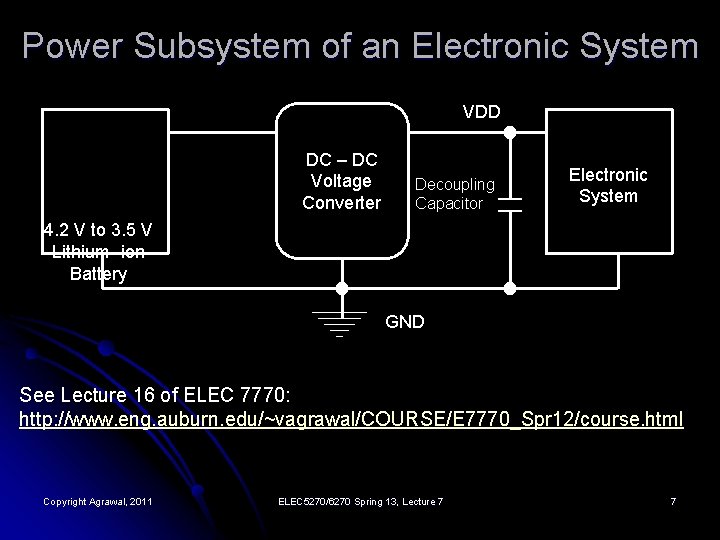

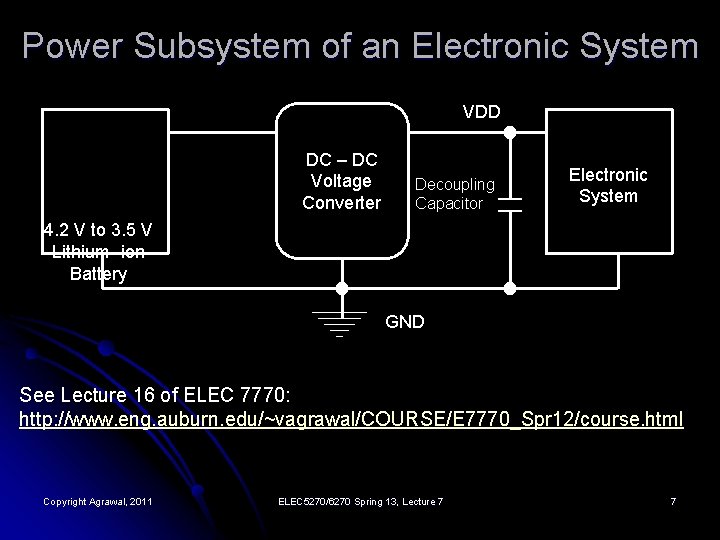

Power Subsystem of an Electronic System VDD DC – DC Voltage Converter Decoupling Capacitor Electronic System 4. 2 V to 3. 5 V Lithium- ion Battery GND See Lecture 16 of ELEC 7770: http: //www. eng. auburn. edu/~vagrawal/COURSE/E 7770_Spr 12/course. html Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 7

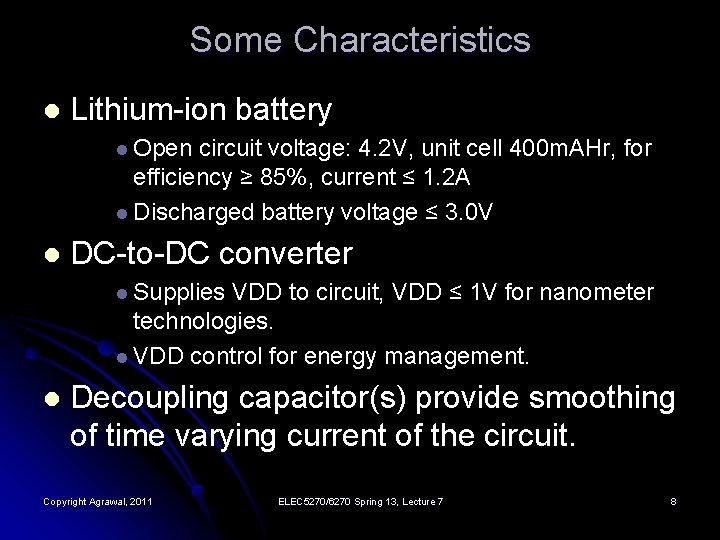

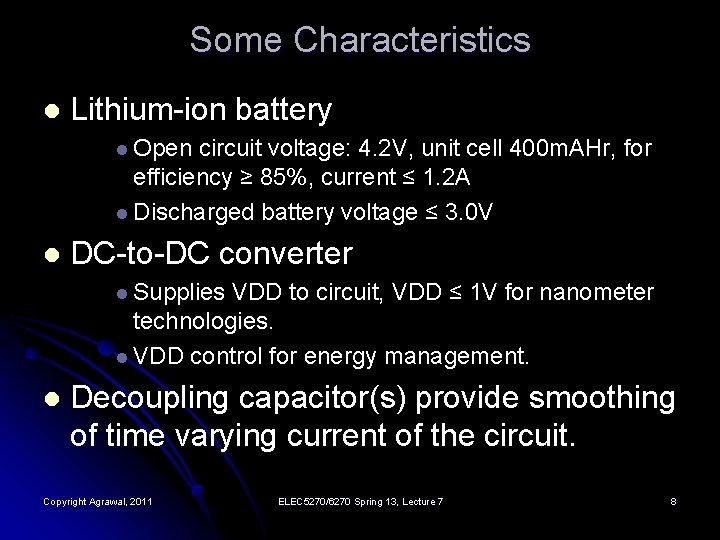

Some Characteristics l Lithium-ion battery l Open circuit voltage: 4. 2 V, unit cell 400 m. AHr, for efficiency ≥ 85%, current ≤ 1. 2 A l Discharged battery voltage ≤ 3. 0 V l DC-to-DC converter l Supplies VDD to circuit, VDD ≤ 1 V for nanometer technologies. l VDD control for energy management. l Decoupling capacitor(s) provide smoothing of time varying current of the circuit. Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 8

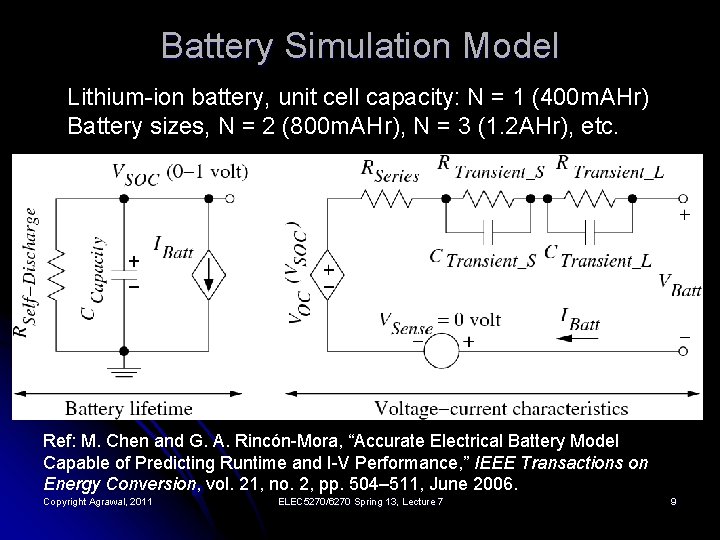

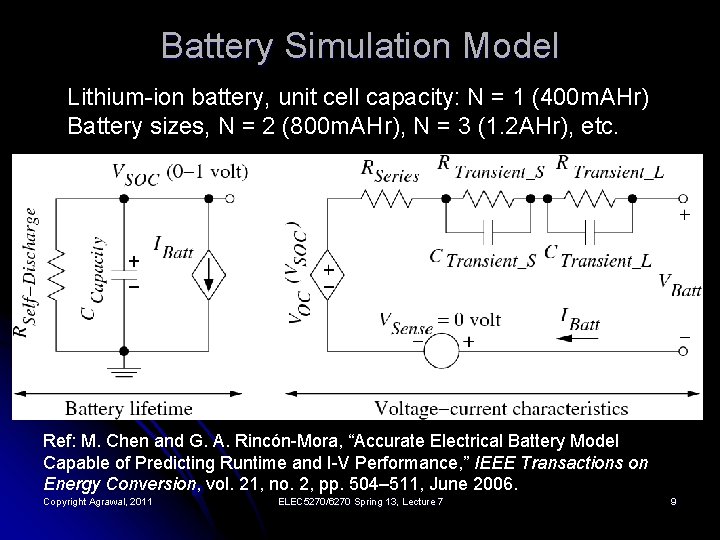

Battery Simulation Model Lithium-ion battery, unit cell capacity: N = 1 (400 m. AHr) Battery sizes, N = 2 (800 m. AHr), N = 3 (1. 2 AHr), etc. Ref: M. Chen and G. A. Rincón-Mora, “Accurate Electrical Battery Model Capable of Predicting Runtime and I-V Performance, ” IEEE Transactions on Energy Conversion, vol. 21, no. 2, pp. 504– 511, June 2006. Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 9

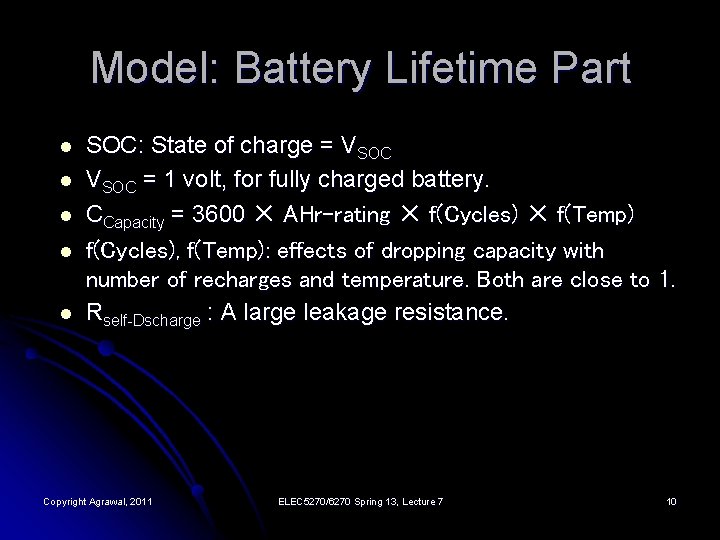

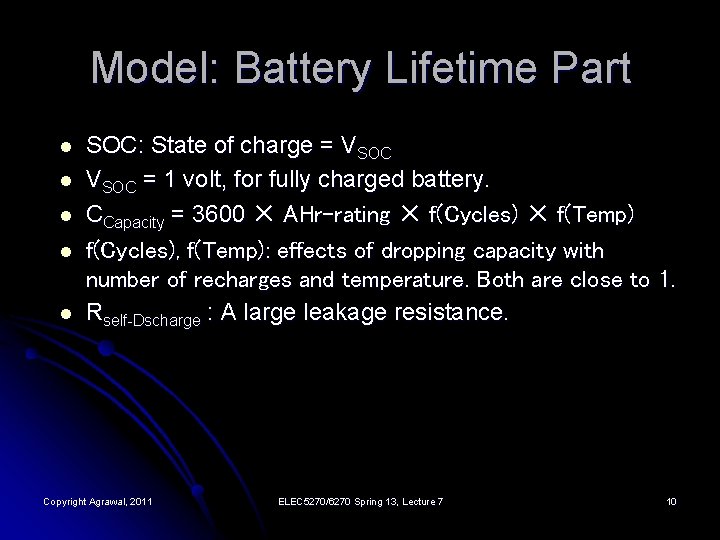

Model: Battery Lifetime Part l l l SOC: State of charge = VSOC = 1 volt, for fully charged battery. CCapacity = 3600 ✕ AHr-rating ✕ f(Cycles) ✕ f(Temp) f(Cycles), f(Temp): effects of dropping capacity with number of recharges and temperature. Both are close to 1. Rself-Dscharge : A large leakage resistance. Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 10

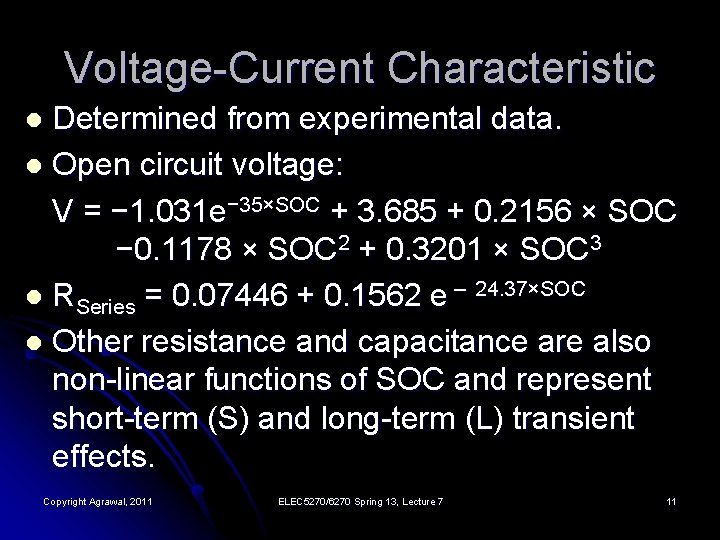

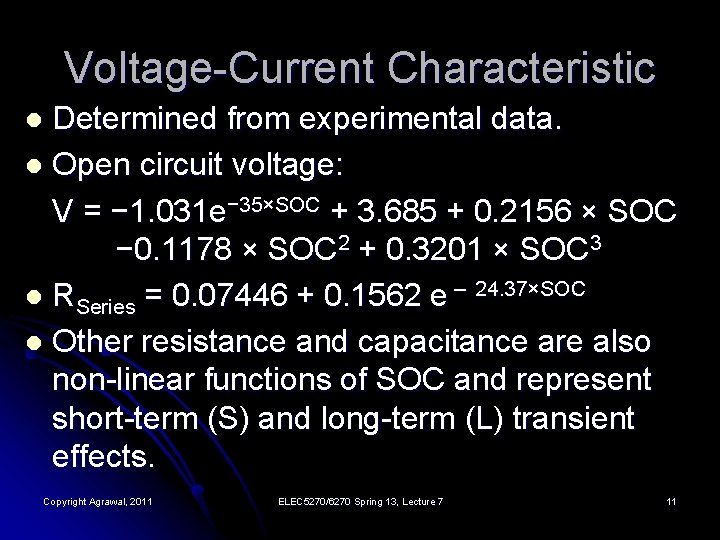

Voltage-Current Characteristic Determined from experimental data. l Open circuit voltage: V = − 1. 031 e− 35×SOC + 3. 685 + 0. 2156 × SOC − 0. 1178 × SOC 2 + 0. 3201 × SOC 3 l RSeries = 0. 07446 + 0. 1562 e – 24. 37×SOC l Other resistance and capacitance are also non-linear functions of SOC and represent short-term (S) and long-term (L) transient effects. l Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 11

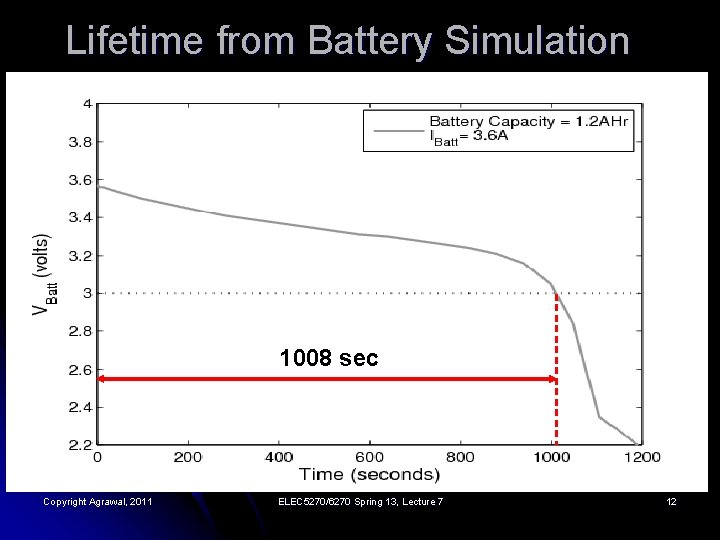

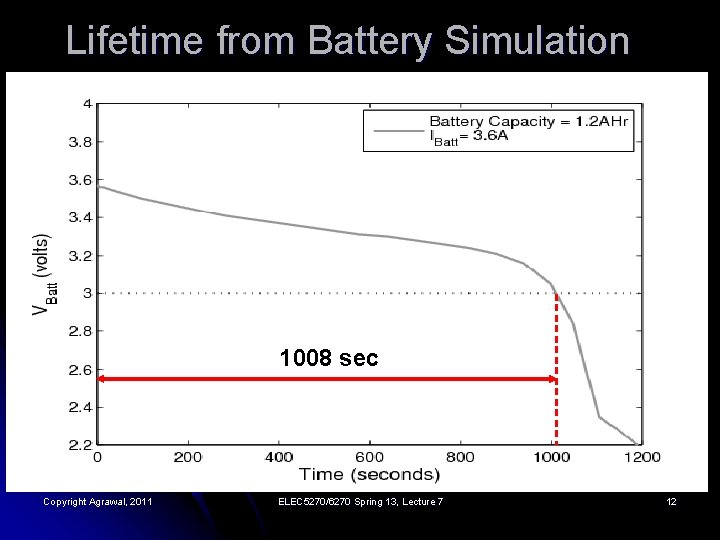

Lifetime from Battery Simulation 1008 sec Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 12

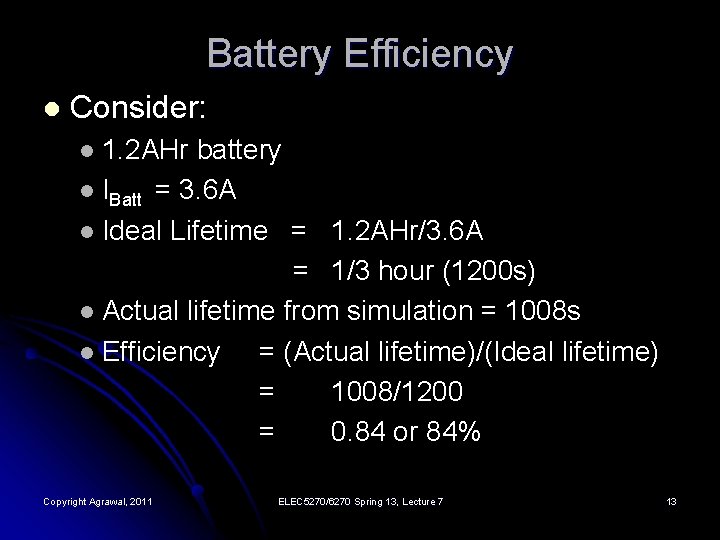

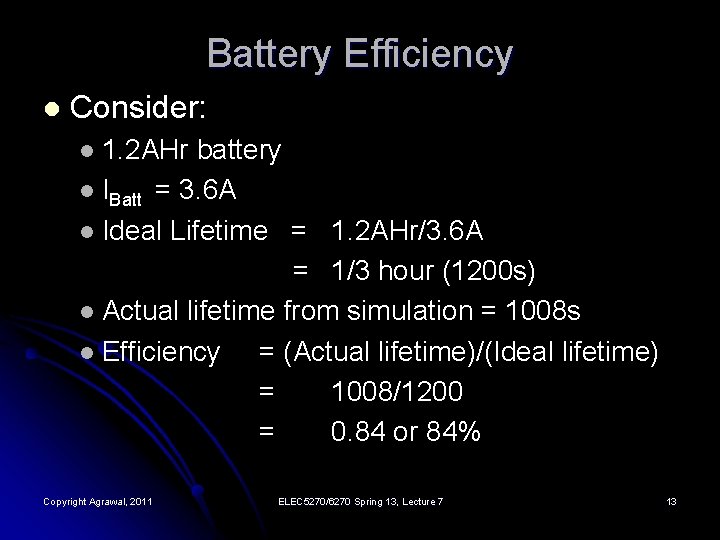

Battery Efficiency l Consider: 1. 2 AHr battery l IBatt = 3. 6 A l Ideal Lifetime = 1. 2 AHr/3. 6 A = 1/3 hour (1200 s) l Actual lifetime from simulation = 1008 s l Efficiency = (Actual lifetime)/(Ideal lifetime) = 1008/1200 = 0. 84 or 84% l Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 13

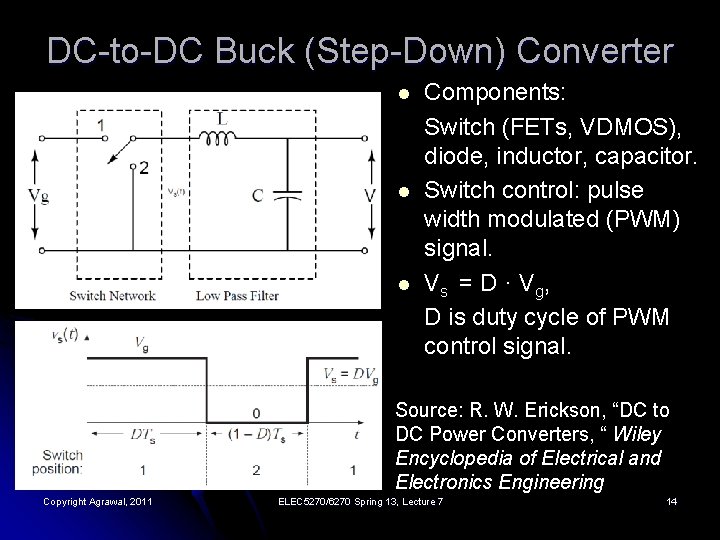

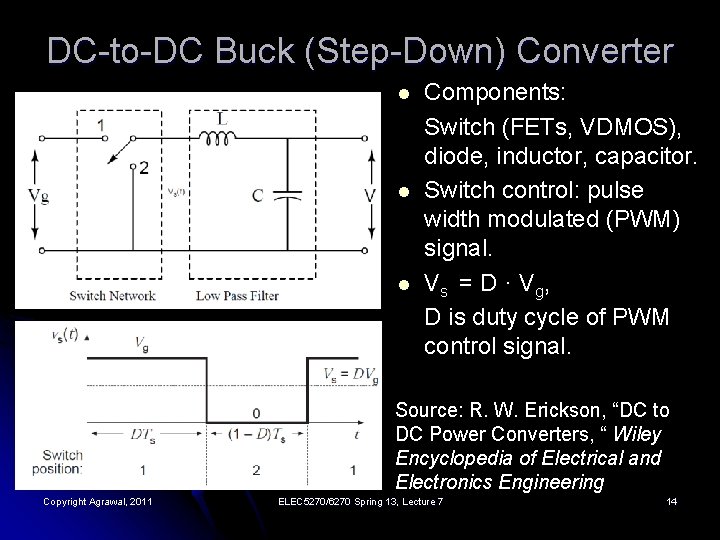

DC-to-DC Buck (Step-Down) Converter l s l l Components: Switch (FETs, VDMOS), diode, inductor, capacitor. Switch control: pulse width modulated (PWM) signal. V s = D · V g, D is duty cycle of PWM control signal. Source: R. W. Erickson, “DC to DC Power Converters, “ Wiley Encyclopedia of Electrical and Electronics Engineering Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 14

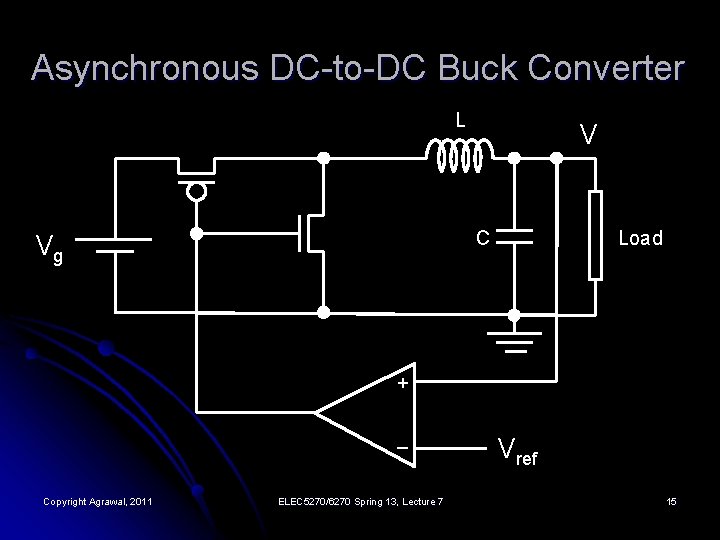

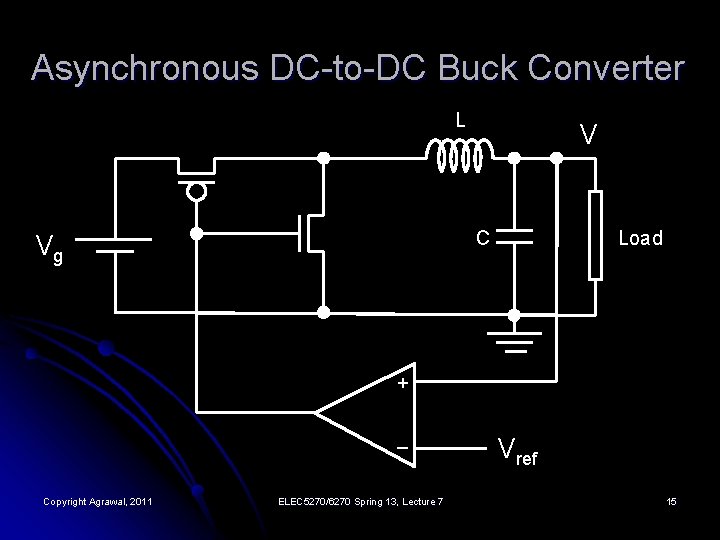

Asynchronous DC-to-DC Buck Converter L V C Vg Load + – Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 Vref 15

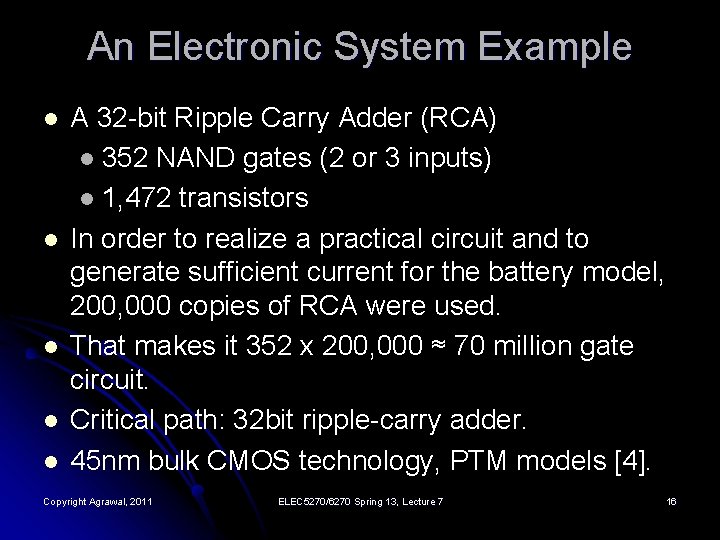

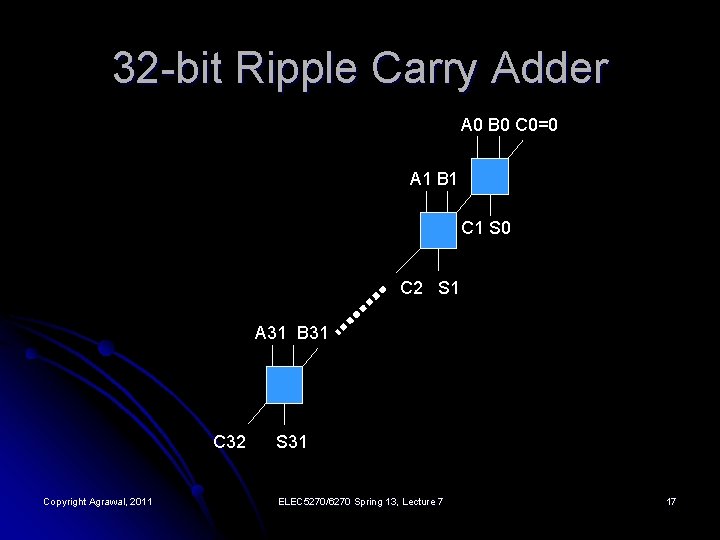

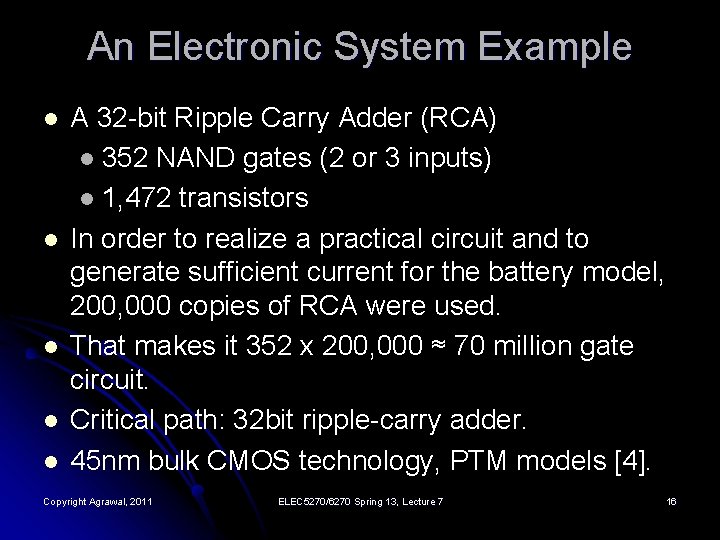

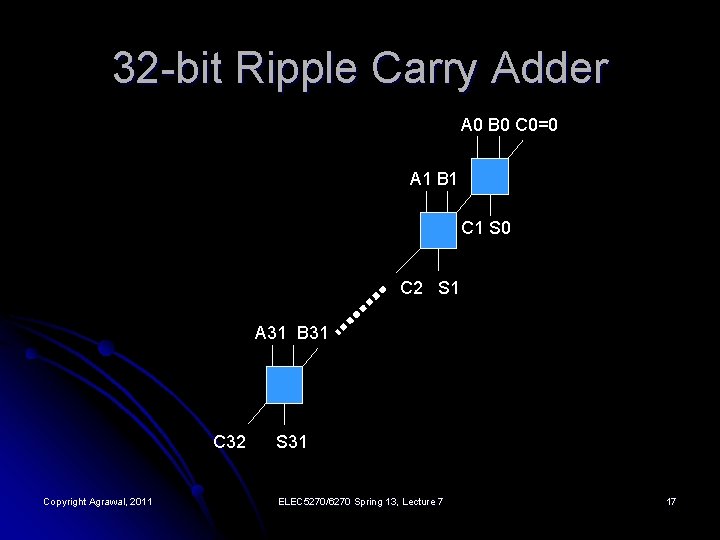

An Electronic System Example l l l A 32 -bit Ripple Carry Adder (RCA) l 352 NAND gates (2 or 3 inputs) l 1, 472 transistors In order to realize a practical circuit and to generate sufficient current for the battery model, 200, 000 copies of RCA were used. That makes it 352 x 200, 000 ≈ 70 million gate circuit. Critical path: 32 bit ripple-carry adder. 45 nm bulk CMOS technology, PTM models [4]. Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 16

32 -bit Ripple Carry Adder A 0 B 0 C 0=0 A 1 B 1 C 1 S 0 C 2 S 1 A 31 B 31 C 32 Copyright Agrawal, 2011 S 31 ELEC 5270/6270 Spring 13, Lecture 7 17

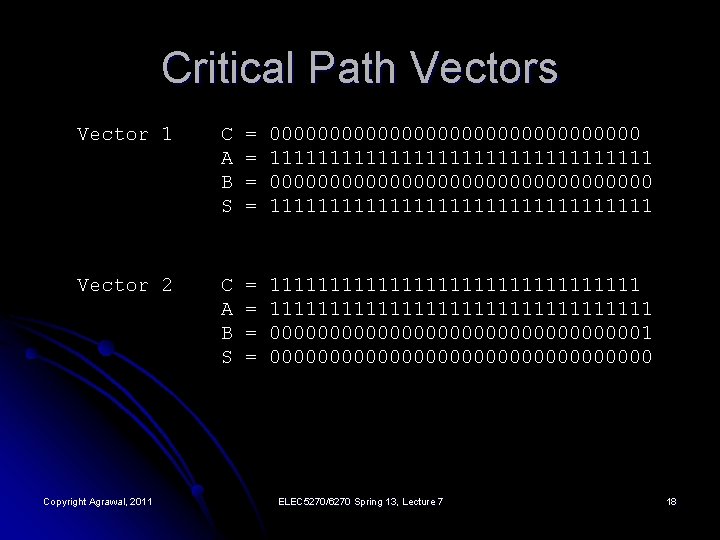

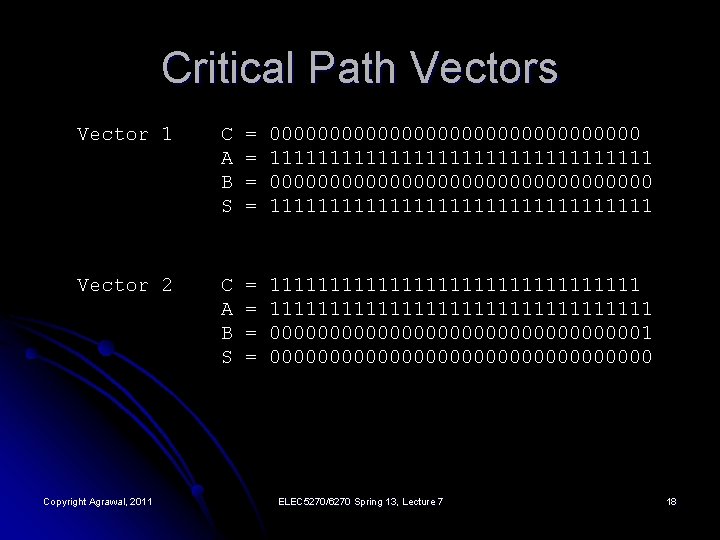

Critical Path Vectors Vector 1 C A B S = = 0000000000000000 1111111111111111 Vector 2 C A B S = = 11111111111111111111111111111111 00000000000000000000000000000000 Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 18

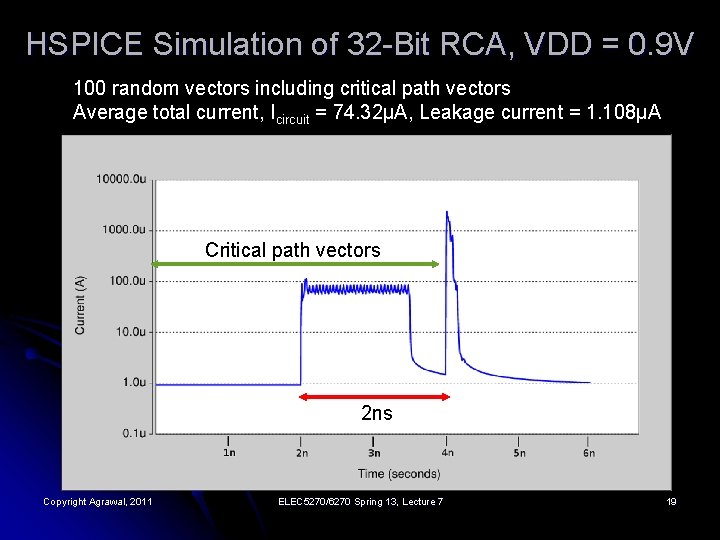

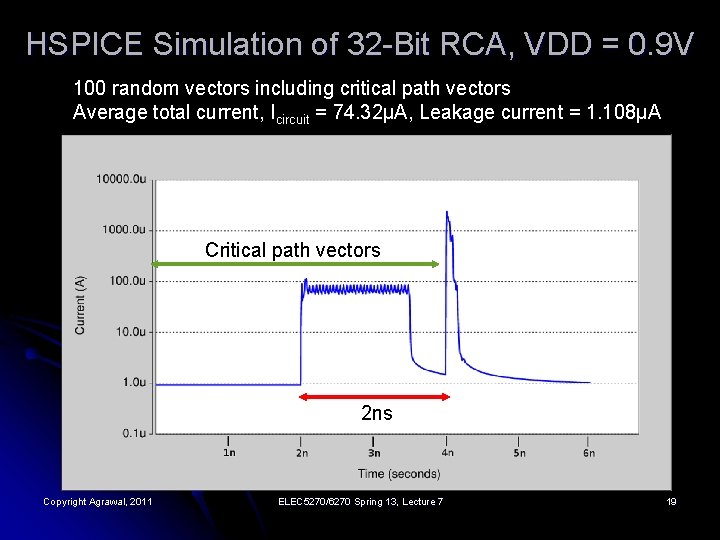

HSPICE Simulation of 32 -Bit RCA, VDD = 0. 9 V 100 random vectors including critical path vectors Average total current, Icircuit = 74. 32μA, Leakage current = 1. 108μA Critical path vectors 2 ns Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 19

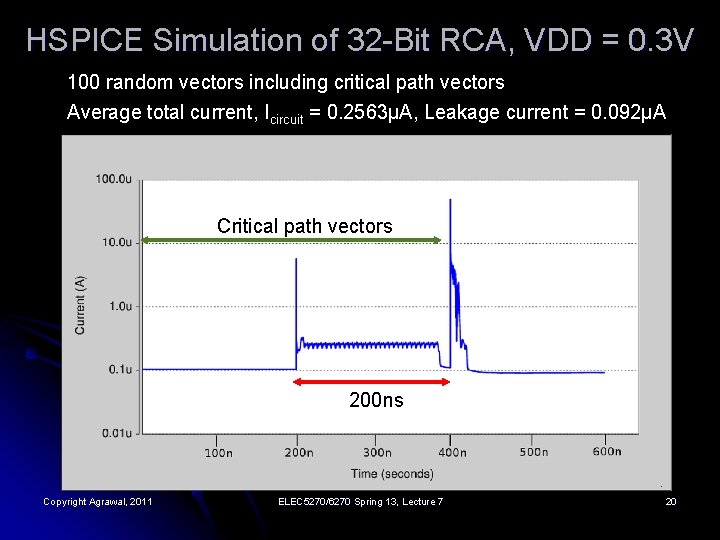

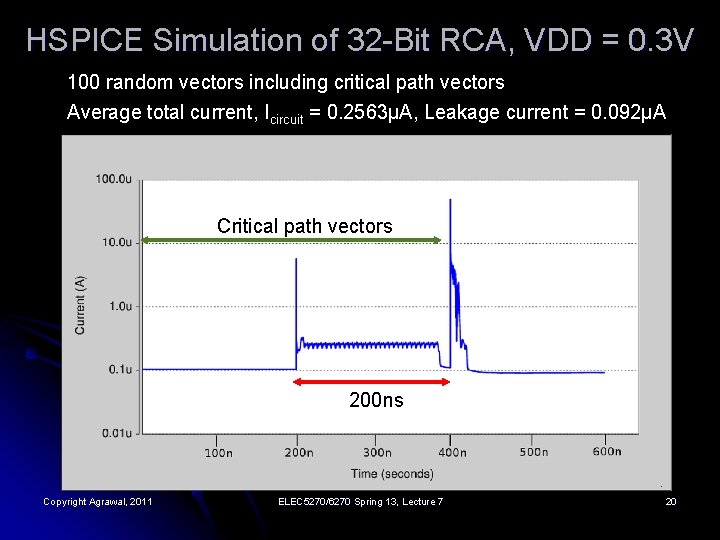

HSPICE Simulation of 32 -Bit RCA, VDD = 0. 3 V 100 random vectors including critical path vectors Average total current, Icircuit = 0. 2563μA, Leakage current = 0. 092μA Critical path vectors 200 ns Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 20

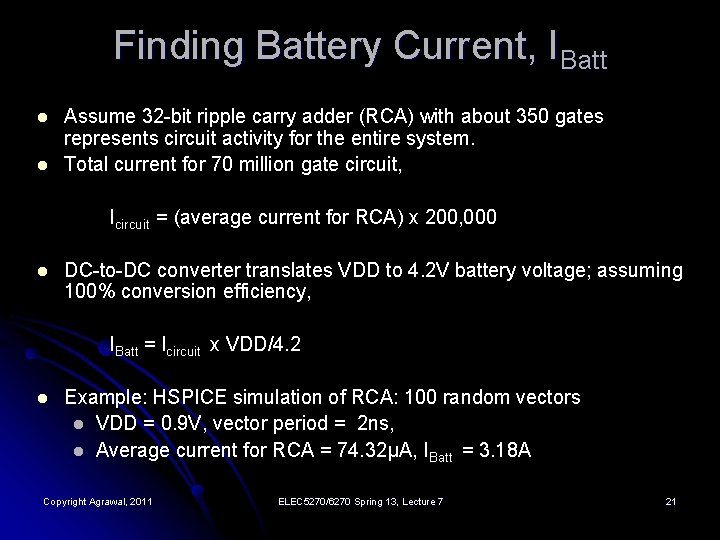

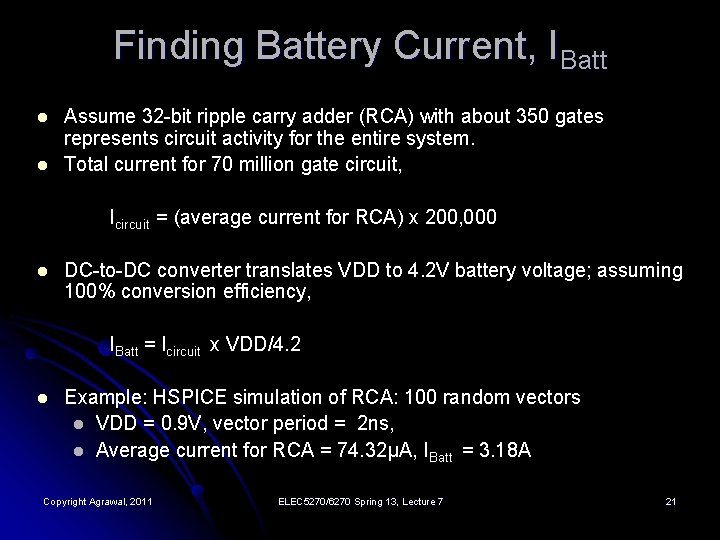

Finding Battery Current, IBatt l l Assume 32 -bit ripple carry adder (RCA) with about 350 gates represents circuit activity for the entire system. Total current for 70 million gate circuit, Icircuit = (average current for RCA) x 200, 000 l DC-to-DC converter translates VDD to 4. 2 V battery voltage; assuming 100% conversion efficiency, IBatt = Icircuit x VDD/4. 2 l Example: HSPICE simulation of RCA: 100 random vectors l VDD = 0. 9 V, vector period = 2 ns, l Average current for RCA = 74. 32μA, IBatt = 3. 18 A Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 21

Case I: Performance System is Performance Bound Battery should be capable of supplying power (current) for required system performance. l Battery should meet the lifetime (time between replacement or recharge) requirement. l Power management to extend the lifetime of selected battery. l Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 22

Four Step Design Step 1: Determine the operating voltage based on required performance. Step 2: Determine minimum battery size for efficiency ≥ 85% Step 3: Increase battery size over the minimum size to meet lifetime requirement. Step 4: Determine a lower performance mode with maximum lifetime for a given battery. Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 23

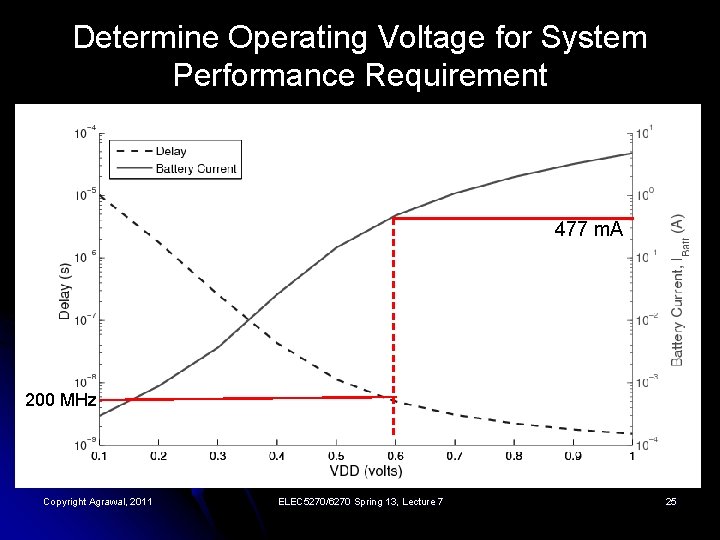

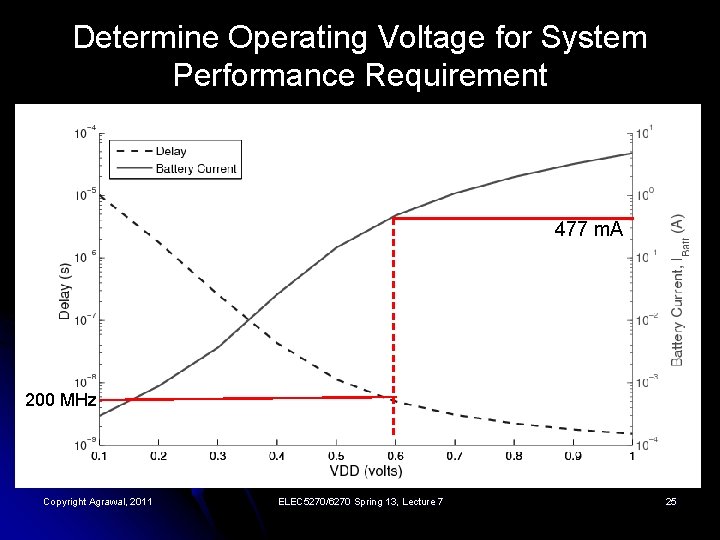

Step 1: Find Operating Voltage l Consider a performance requirement of 200 MHz clock, critical path delay ≤ 5 ns. l Circuit simulation gives, VDD = 0. 6 V and IBatt = 477 m. A. Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 24

Determine Operating Voltage for System Performance Requirement 477 m. A 200 MHz Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 25

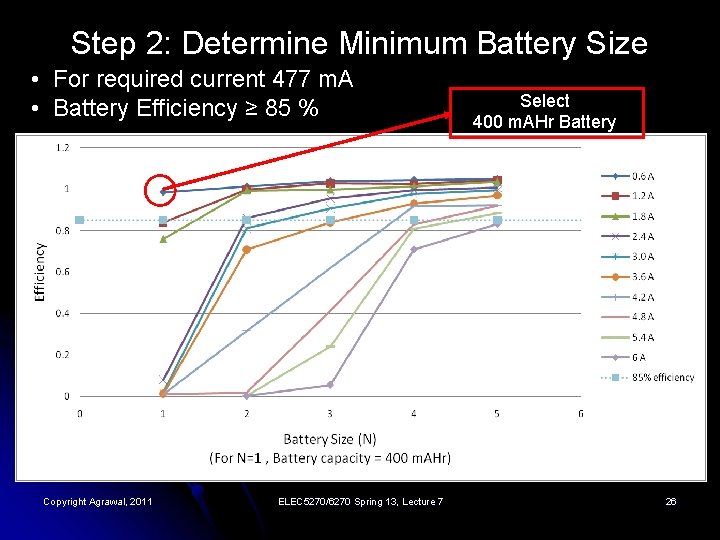

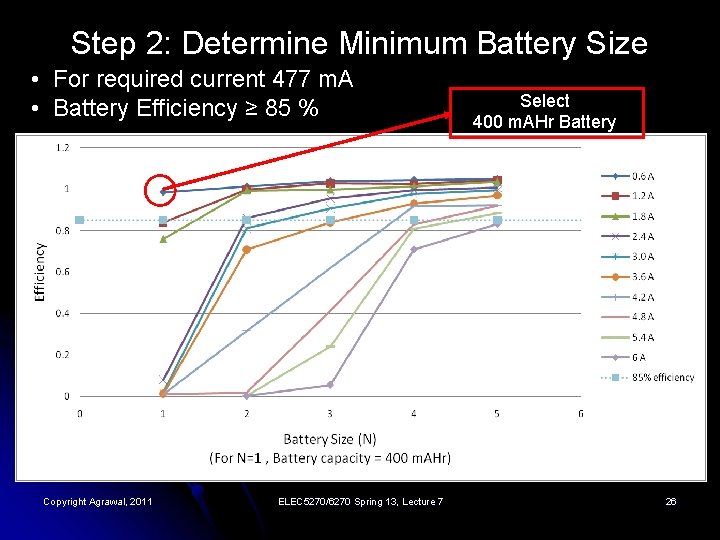

Step 2: Determine Minimum Battery Size • For required current 477 m. A • Battery Efficiency ≥ 85 % Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 Select 400 m. AHr Battery 26

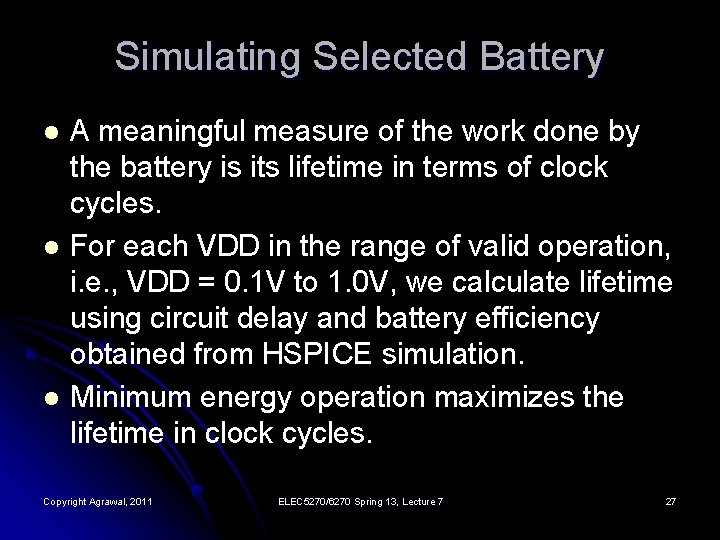

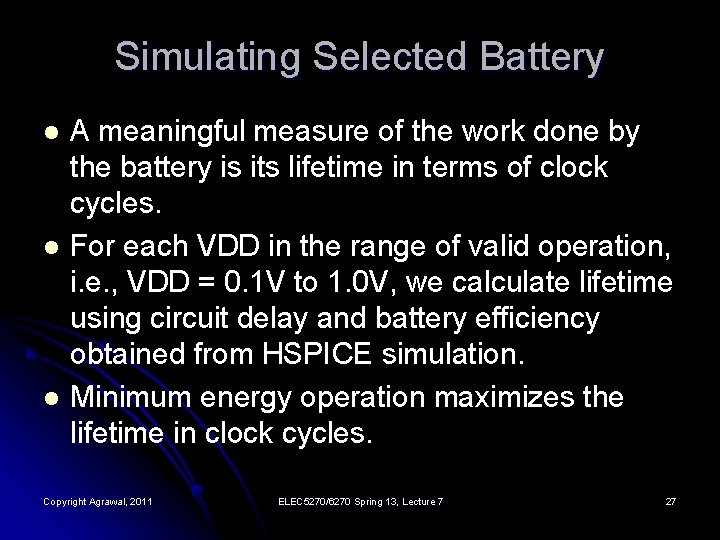

Simulating Selected Battery l l l A meaningful measure of the work done by the battery is its lifetime in terms of clock cycles. For each VDD in the range of valid operation, i. e. , VDD = 0. 1 V to 1. 0 V, we calculate lifetime using circuit delay and battery efficiency obtained from HSPICE simulation. Minimum energy operation maximizes the lifetime in clock cycles. Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 27

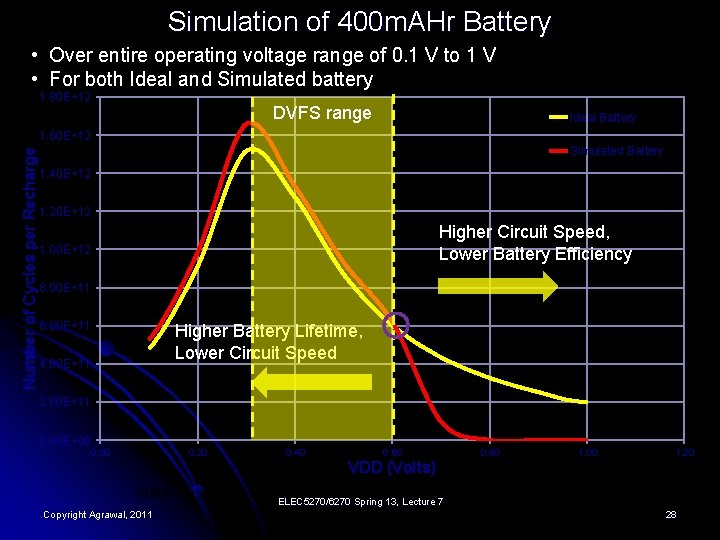

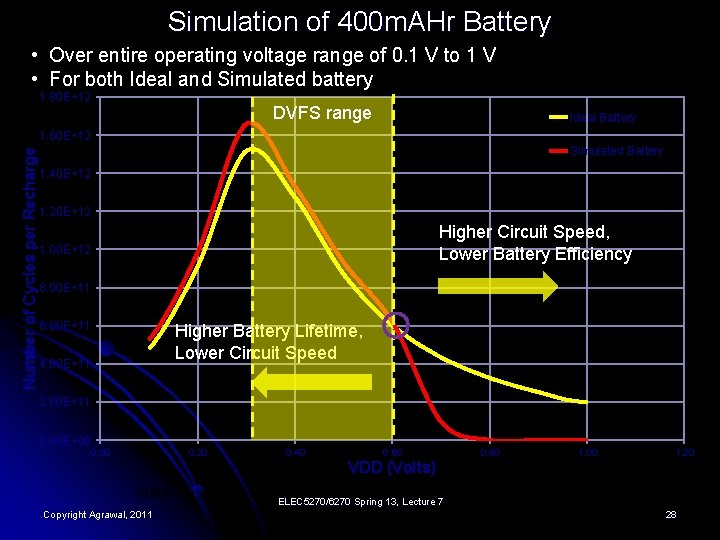

Simulation of 400 m. AHr Battery • Over entire operating voltage range of 0. 1 V to 1 V • For both Ideal and Simulated battery 1. 80 E+12 DVFS range Ideal Battery Number of Cycles per Recharge 1. 60 E+12 Simulated Battery 1. 40 E+12 1. 20 E+12 Higher Circuit Speed, Lower Battery Efficiency 1. 00 E+12 8. 00 E+11 6. 00 E+11 Higher Battery Lifetime, Lower Circuit Speed 4. 00 E+11 2. 00 E+11 0. 00 E+00 0. 20 0. 40 0. 60 0. 80 1. 00 1. 20 VDD (Volts) 0. 098 Copyright Agrawal, 2011 0. 560 3. 860 ELEC 5270/6270 23. 00 88. 00 199. 0 325. 0 Spring 13, Lecture 7 ELEC 5270/6270 Spring 13, Lecture 7 446. 0 557. 0 657. 0 (MHz) 28

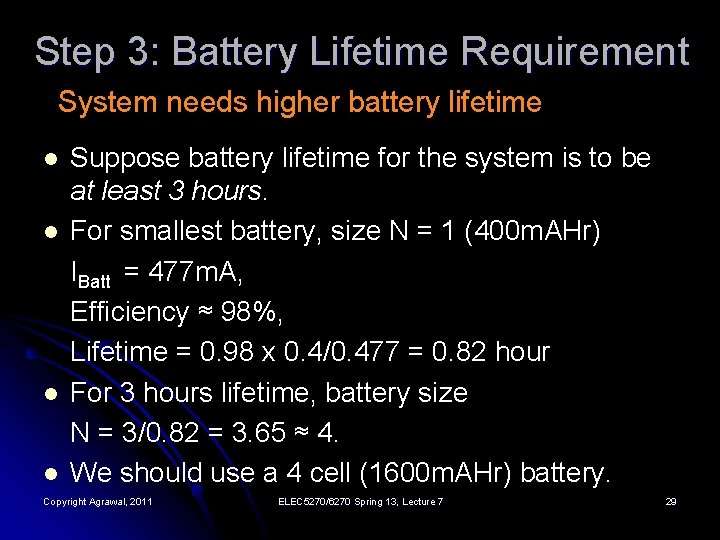

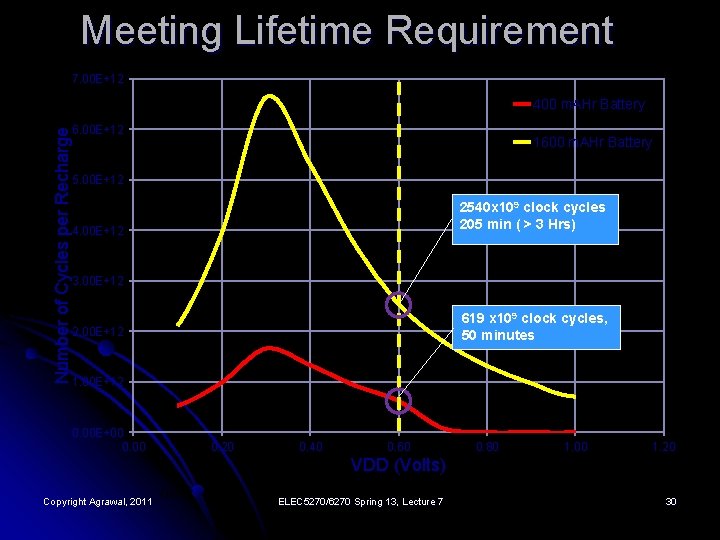

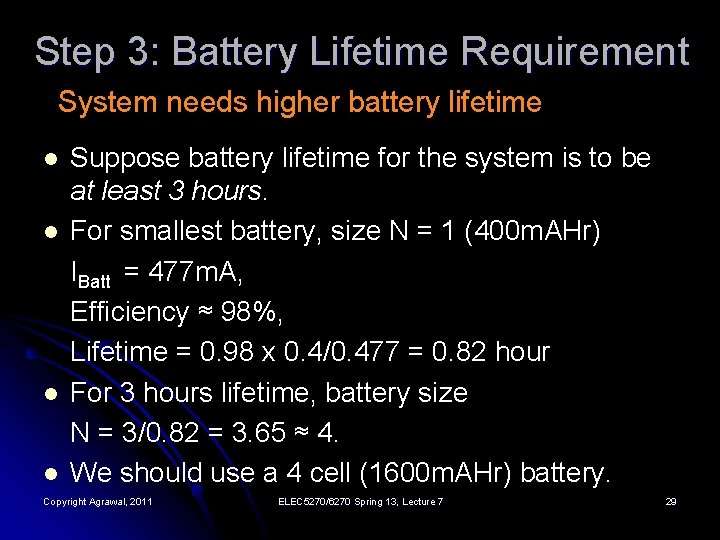

Step 3: Battery Lifetime Requirement System needs higher battery lifetime l l Suppose battery lifetime for the system is to be at least 3 hours. For smallest battery, size N = 1 (400 m. AHr) IBatt = 477 m. A, Efficiency ≈ 98%, Lifetime = 0. 98 x 0. 4/0. 477 = 0. 82 hour For 3 hours lifetime, battery size N = 3/0. 82 = 3. 65 ≈ 4. We should use a 4 cell (1600 m. AHr) battery. Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 29

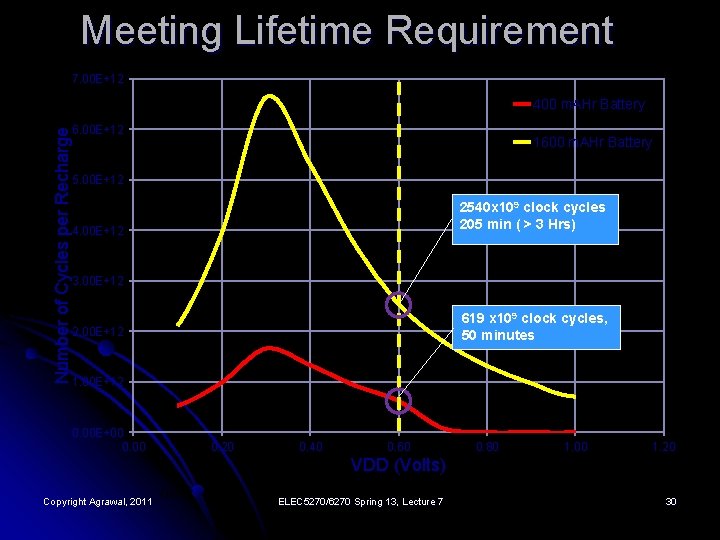

Meeting Lifetime Requirement 7. 00 E+12 Number of Cycles per Recharge 400 m. AHr Battery 6. 00 E+12 1600 m. AHr Battery 5. 00 E+12 2540 x 109 clock cycles 205 min ( > 3 Hrs) 4. 00 E+12 3. 00 E+12 619 x 109 clock cycles, 50 minutes 2. 00 E+12 1. 00 E+12 0. 00 E+00 0. 20 0. 40 0. 60 0. 80 1. 00 1. 20 VDD (Volts) Copyright Agrawal, 2011 0. 098 0. 560 3. 860 23. 00 88. 00 199. 0 325. 0 446. 0 ELEC 5270/6270 Spring 13, Lecture 7 557. 0 657. 0 (MHz) 30 30

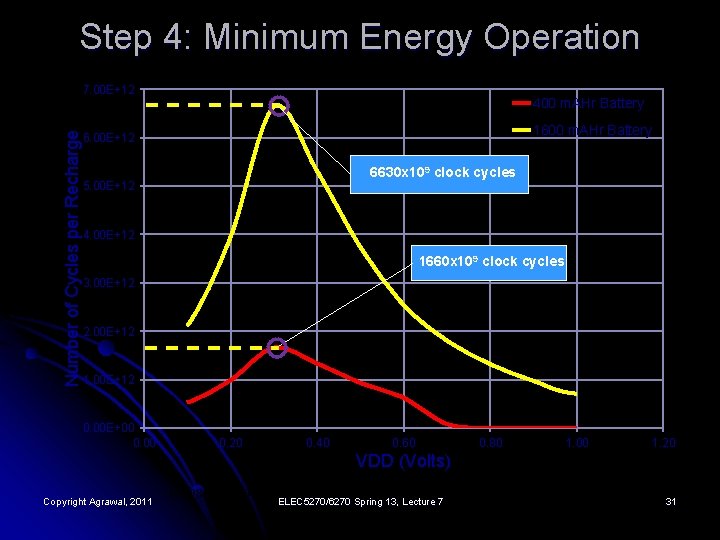

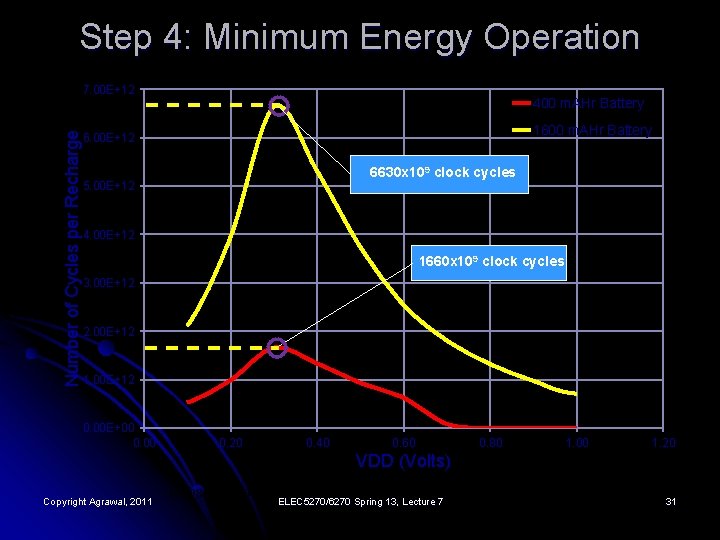

Step 4: Minimum Energy Operation Number of Cycles per Recharge 7. 00 E+12 400 m. AHr Battery 1600 m. AHr Battery 6. 00 E+12 6630 x 109 clock cycles 5. 00 E+12 4. 00 E+12 1660 x 109 clock cycles 3. 00 E+12 2. 00 E+12 1. 00 E+12 0. 00 E+00 0. 20 0. 40 0. 60 0. 80 1. 00 1. 20 VDD (Volts) Copyright Agrawal, 2011 0. 098 0. 560 3. 860 23. 00 88. 00 199. 0 325. 0 446. 0 557. 0 657. 0 ELEC 5270/6270 Spring 13, Lecture 7 (MHz)31 31

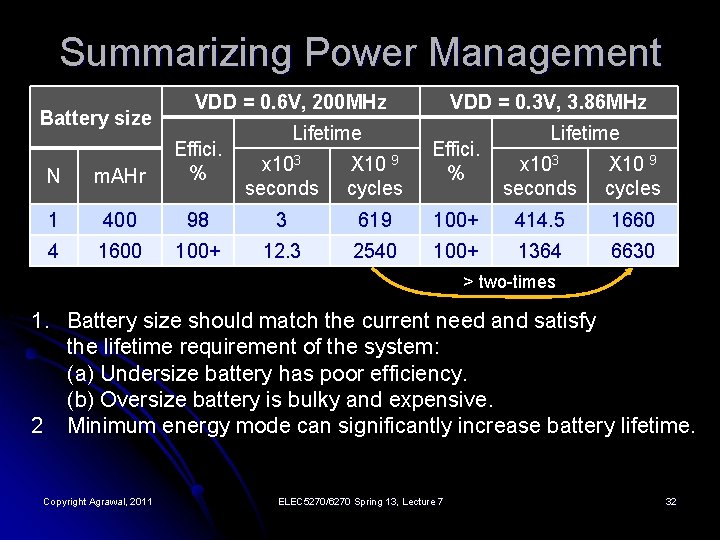

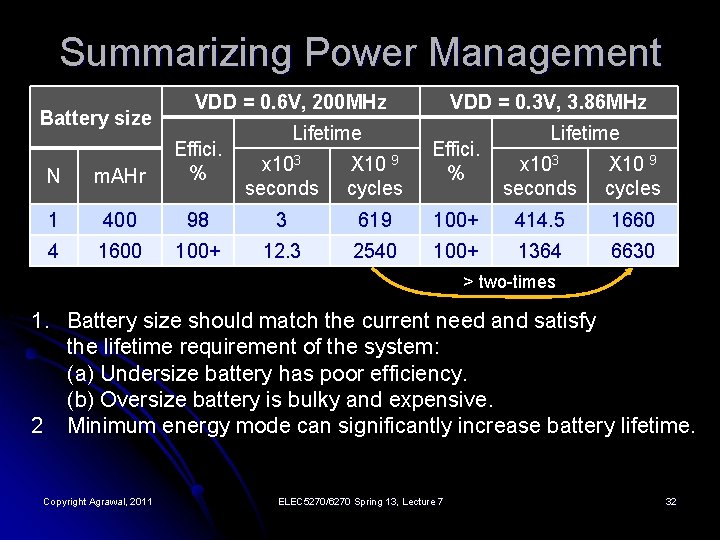

Summarizing Power Management Battery size VDD = 0. 6 V, 200 MHz Lifetime VDD = 0. 3 V, 3. 86 MHz N m. AHr 1 400 98 3 619 100+ 414. 5 1660 4 1600 100+ 12. 3 2540 100+ 1364 6630 x 103 seconds X 10 9 cycles Effici. % Lifetime Effici. % x 103 seconds X 10 9 cycles > two-times 1. Battery size should match the current need and satisfy the lifetime requirement of the system: (a) Undersize battery has poor efficiency. (b) Oversize battery is bulky and expensive. 2 Minimum energy mode can significantly increase battery lifetime. Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 32

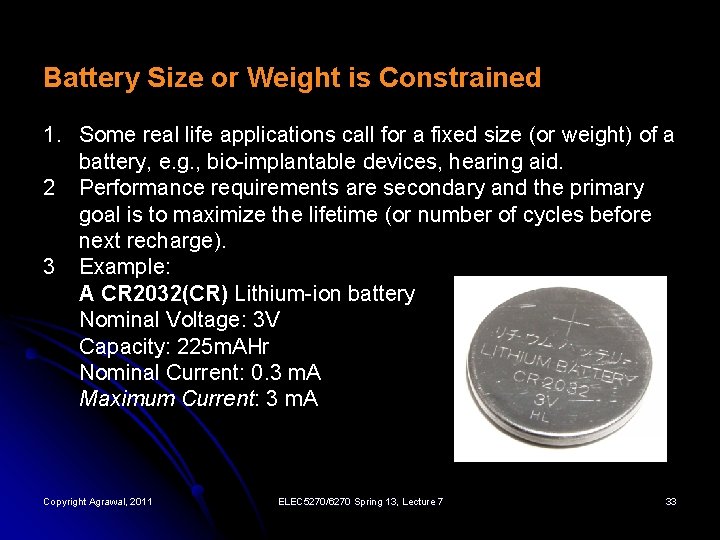

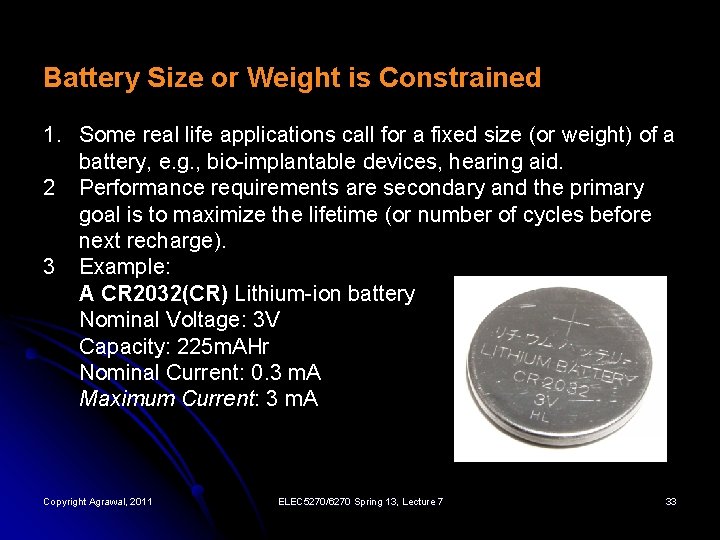

Battery Size or Weight is Constrained 1. Some real life applications call for a fixed size (or weight) of a battery, e. g. , bio-implantable devices, hearing aid. 2 Performance requirements are secondary and the primary goal is to maximize the lifetime (or number of cycles before next recharge). 3 Example: A CR 2032(CR) Lithium-ion battery Nominal Voltage: 3 V Capacity: 225 m. AHr Nominal Current: 0. 3 m. A Maximum Current: 3 m. A Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 33

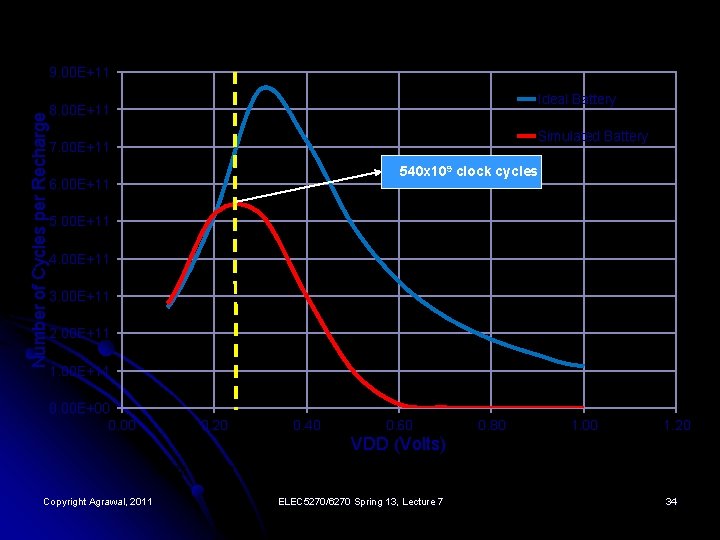

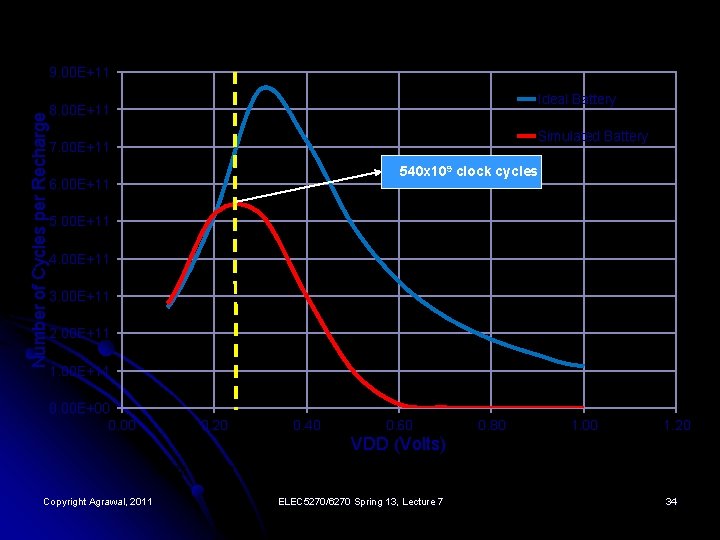

Number of Cycles per Recharge 9. 00 E+11 Ideal Battery 8. 00 E+11 Simulated Battery 7. 00 E+11 540 x 109 clock cycles 6. 00 E+11 5. 00 E+11 4. 00 E+11 3. 00 E+11 2. 00 E+11 1. 00 E+11 0. 00 E+00 0. 20 0. 40 0. 60 0. 80 1. 00 1. 20 VDD (Volts) 0. 098 Copyright Agrawal, 2011 0. 560 3. 860 23. 00 88. 00 199. 0 325. 0 446. 0 ELEC 5270/6270 Spring 13, Lecture 7 557. 0 657. 0 (MHz) 34

References 1. 2. 3. 4. 5. M. Pedram and Q. Wu, “Design Considerations for Battery-Powered Electronics, ” Proc. 36 th Design Automation Conference, June 1999, pp. 861– 866. L. Benini, G. Castelli, A. Macii, E. Macii, M. Poncino, and R. Scarsi, “A Discrete-Time Battery Model for High-Level Power Estimation, ” Proc. Conference on Design, Automation and Test in Europe, Mar. 2000, pp. 35 – 41. M. Chen and G. A. Rincón-Mora, “Accurate Electrical Battery Model Capable of Predicting Runtime and I-V Performance, ” IEEE Transactions on Energy Conversion, vol. 21, no. 2, pp. 504 – 511, June 2006. Simulation model: 45 nm bulk CMOS, predictive technology model (PTM), http: //ptm. asu. edu/ Simulator: Synopsys HSPICE, www. synopsys. com/Tools/Verification/AMSVerification/Circuit. Simulation /HSPICE/Documents/hspice%20 ds. pdf Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 35

References (Cont. ) 6. 7. 8. 9. 10. M. Kulkarni and V. D. Agrawal, “Matching Power Source to Electronic System: A Tutorial on Battery Simulation”, Proc. VLSI Design and Test Symposium, July 2010. M. Kulkarni and V. D. Agrawal, “Energy Source Lifetime Optimization for a Digital System through Power Management, ” Proc. IEEE International Conf. Industrial Technology and 43 rd IEEE Southeastern Symp. System Theory, March 2011. M. Kulkarni, S. Sheth and V. D. Agrawal, “Architectural Power Management for High Leakage Technologies, ” Proc. IEEE International Conf. Industrial Technology and 43 rd IEEE Southeastern Symp. System Theory, March 2011. M. Kulkarni, “Energy Source Lifetime Optimization for a Digital System through Power Management, ” Master’s Thesis, ECE Dept. , Auburn University, December 2010. K. Sheth, “A Hardware-Software Processor Architecture using Pipeline Stalls for Leakage Power Management, ” Master’s Thesis, ECE Dept. , Auburn University, December 2008. Copyright Agrawal, 2011 ELEC 5270/6270 Spring 13, Lecture 7 36