ECE 491 Senior Design I Lecture 12 Metastability

ECE 491 - Senior Design I Lecture 12 - Metastability Fall 2007 Homework due Friday 10/3: Metastability problem, p. 18 Prof. John Nestor ECE Department Lafayette College Easton, Pennsylvania 18042 nestorj@lafayette. edu ECE 491 Fall 2006 Lecture 12 - Metastability 1

Where we are } Last Time: } Data Communications 2 • Asynchronous Serial Receiver • Transmission codes for Clock Recovery (Manchester Codes) } Today: } Synchronizers & Metastability ECE 491 Fall 2006 Lecture 12 - Metastability 2

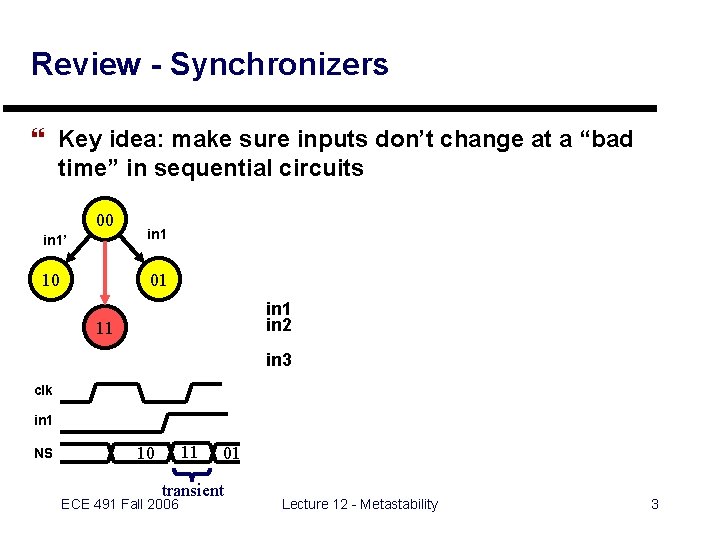

Review - Synchronizers } Key idea: make sure inputs don’t change at a “bad time” in sequential circuits 00 in 1’ in 1 10 01 in 2 11 in 3 clk in 1 NS 11 10 01 transient ECE 491 Fall 2006 Lecture 12 - Metastability 3

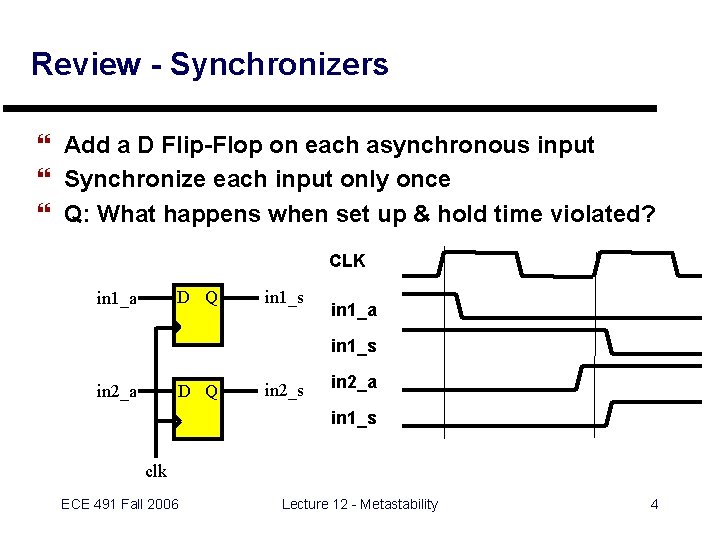

Review - Synchronizers } Add a D Flip-Flop on each asynchronous input } Synchronize each input only once } Q: What happens when set up & hold time violated? CLK D Q in 1_a in 1_s in 2_a D Q in 2_s in 2_a in 1_s clk ECE 491 Fall 2006 Lecture 12 - Metastability 4

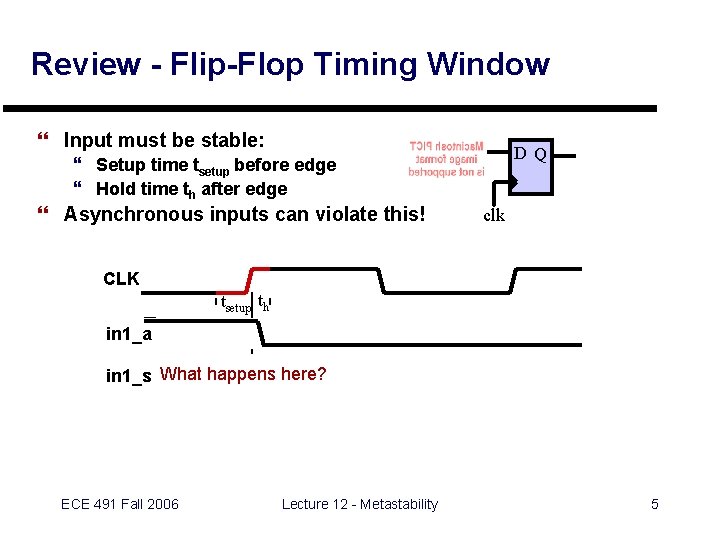

Review - Flip-Flop Timing Window } Input must be stable: DQ } Setup time tsetup before edge } Hold time th after edge } Asynchronous inputs can violate this! clk CLK tsetup th in 1_a in 1_s What happens here? t. CQ ECE 491 Fall 2006 Lecture 12 - Metastability 5

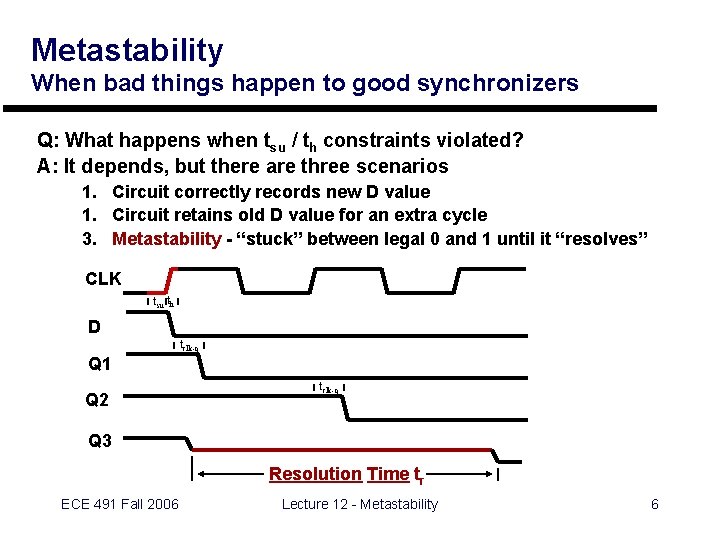

Metastability When bad things happen to good synchronizers Q: What happens when tsu / th constraints violated? A: It depends, but there are three scenarios 1. Circuit correctly records new D value 1. Circuit retains old D value for an extra cycle 3. Metastability - “stuck” between legal 0 and 1 until it “resolves” CLK tsu th D tclk-q Q 1 Q 2 tclk-q Q 3 Resolution Time tr ECE 491 Fall 2006 Lecture 12 - Metastability 6

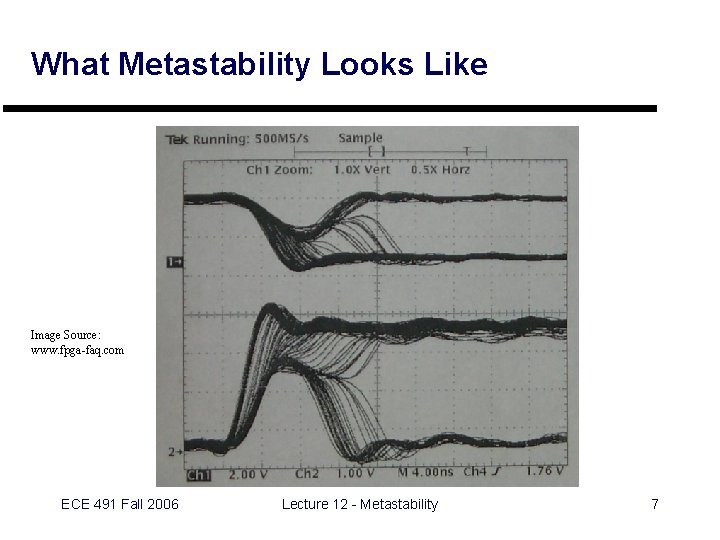

What Metastability Looks Like Image Source: www. fpga-faq. com ECE 491 Fall 2006 Lecture 12 - Metastability 7

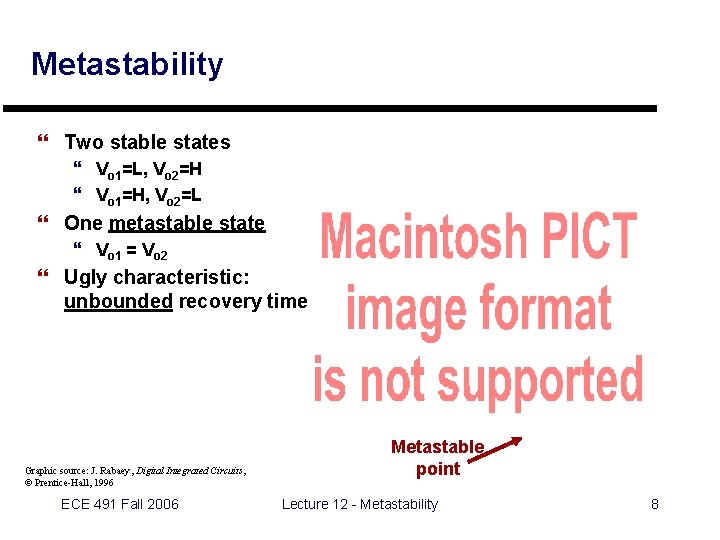

Metastability } Two stable states } Vo 1=L, Vo 2=H } Vo 1=H, Vo 2=L } One metastable state } Vo 1 = Vo 2 } Ugly characteristic: unbounded recovery time tr Graphic source: J. Rabaey, Digital Integrated Circuits, © Prentice-Hall, 1996 ECE 491 Fall 2006 Metastable point Lecture 12 - Metastability 8

Metastability - “Ball on the Hill” Analogy } } Sides of hill = stable states Top of hill = metastable state Gravity = gain of inverters Any small “push” (e. g. , noise) will move the ball off the hill and into a stable state ECE 491 Fall 2006 Lecture 12 - Metastability 9

Metastability - Bad News / Good News } Bad news } Metastability is unavoidable } Recovery time is theoretically unbounded } Good news } Can empirically measure recovery times } Can use statistics from recovery times to make failure probability arbitrarily small } Most FPGAs are highly resistant to metastability ECE 491 Fall 2006 Lecture 12 - Metastability 10

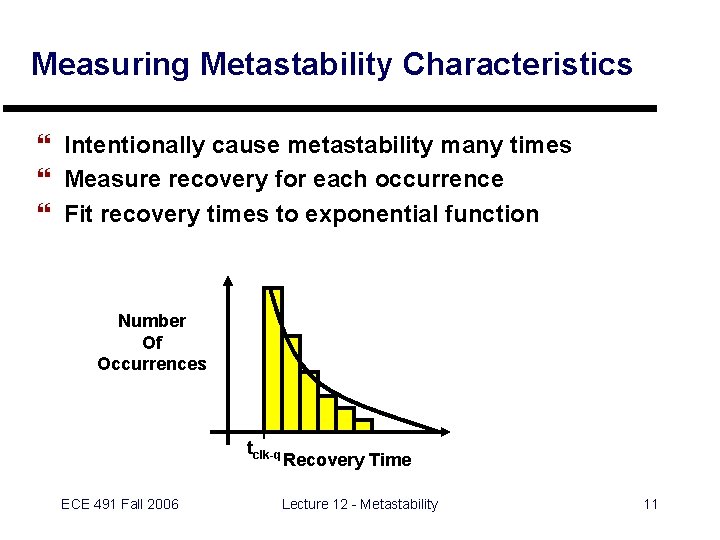

Measuring Metastability Characteristics } Intentionally cause metastability many times } Measure recovery for each occurrence } Fit recovery times to exponential function Number Of Occurrences tclk-q ECE 491 Fall 2006 Recovery Time Lecture 12 - Metastability 11

Designing with Metastability } A synchronizer design at a given clock period provides a fixed amount of resolution time tr } Definition: a synchronization failure occurs when actual recovery time tr-actual > tr-available } For a given flip-flop, the mean time between failure (MTBF) is given by the formula fclk - System clock freq. a - asynchronous input rate of change. t - empirically derived constant To - empirically derived constant tr - time available for resolution ECE 491 Fall 2006 Lecture 12 - Metastability 12

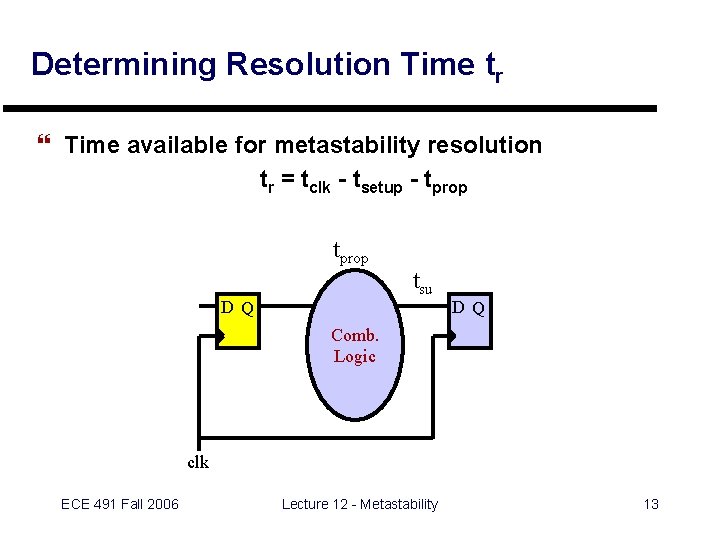

Determining Resolution Time tr } Time available for metastability resolution tr = tclk - tsetup - tprop tsu DQ DQ Comb. Logic clk ECE 491 Fall 2006 Lecture 12 - Metastability 13

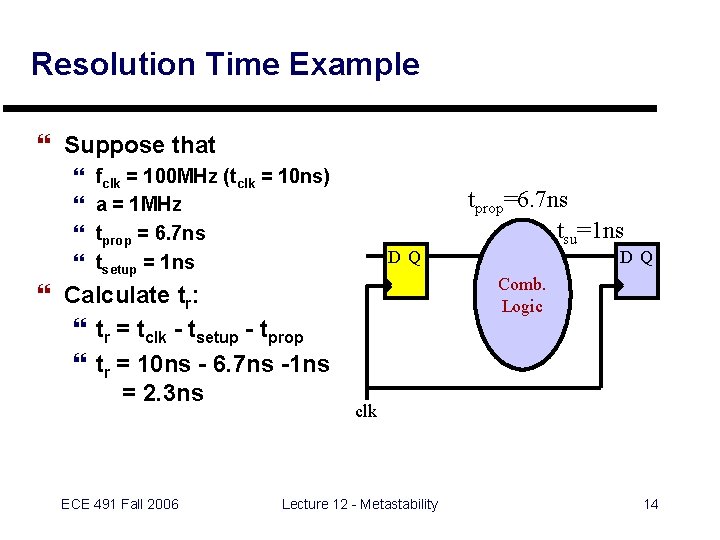

Resolution Time Example } Suppose that } } fclk = 100 MHz (tclk = 10 ns) a = 1 MHz tprop = 6. 7 ns tsetup = 1 ns } Calculate tr: } tr = tclk - tsetup - tprop } tr = 10 ns - 6. 7 ns -1 ns = 2. 3 ns ECE 491 Fall 2006 DQ tprop=6. 7 ns tsu=1 ns DQ Comb. Logic clk Lecture 12 - Metastability 14

MTBF Calculation Example } “Typical” values for a 0. 25µm ASIC library flip-flop } t = 0. 31 ns } To = 9. 6 as } tr = 2. 3 ns “as” = 10 -18 s } MTBF = 20. 1 days - unacceptable! ECE 491 Fall 2006 Lecture 12 - Metastability 15

What happens if we halve fclk? } Suppose that } } fclk = 50 MHz (tclk = 20 ns) a = 1 MHz tprop = 6. 7 ns tsetup = 1 ns } Calculate tr and MTBF: } tr = tclk - tsetup - tprop } tr = 20 ns - 6. 7 ns -1 ns = 12. 3 ns } MTBF = 5. 7 X 1028 seconds = 1. 8 X 1021 years ECE 491 Fall 2006 Lecture 12 - Metastability 16

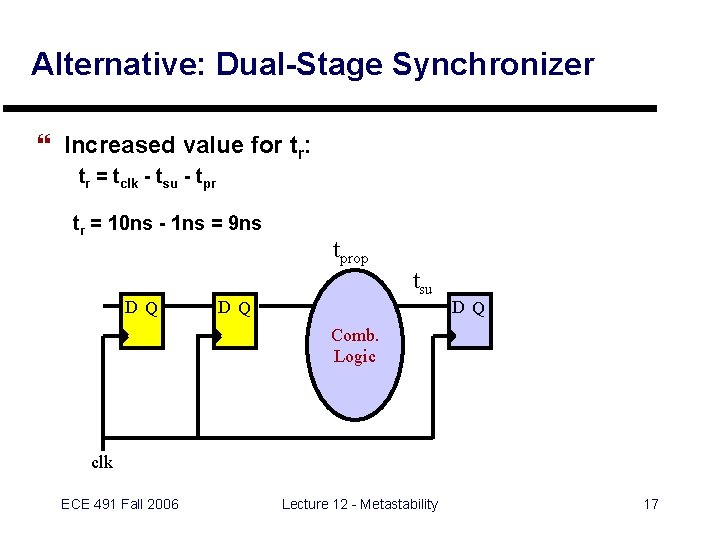

Alternative: Dual-Stage Synchronizer } Increased value for tr: tr = tclk - tsu - tpr tr = 10 ns - 1 ns = 9 ns DQ tprop tsu DQ DQ Comb. Logic clk ECE 491 Fall 2006 Lecture 12 - Metastability 17

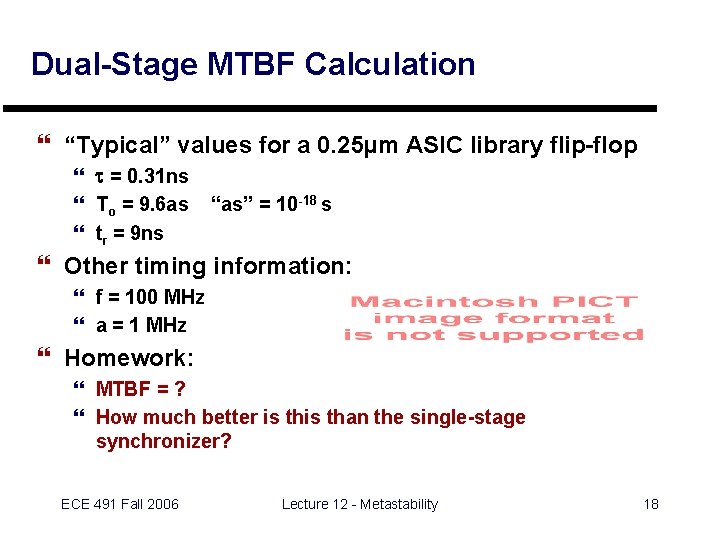

Dual-Stage MTBF Calculation } “Typical” values for a 0. 25µm ASIC library flip-flop } t = 0. 31 ns } To = 9. 6 as } tr = 9 ns “as” = 10 -18 s } Other timing information: } f = 100 MHz } a = 1 MHz } Homework: } MTBF = ? } How much better is than the single-stage synchronizer? Answer: 4. 23 X 1015 s = 8. 05 X 109 years ECE 491 Fall 2006 Lecture 12 - Metastability 18

Other Synchronizer Alternatives } Metastability-hardened SYNC flip-flops } Multiple-Stage Synchronizers } Reduced-Clock Synchronizers ECE 491 Fall 2006 Lecture 12 - Metastability 19

Reality Check: What about FPGAs? } Metastability info in FPGAs is scarce } One refrerence: Peter Alfke, “Metastability Delay and Mean Time Between Failures in Virtex-II Pro FFs”, October 2002. } Some statistical measurements for Virtex-II Pro FPGAs } Major conclusion: Metastability issues are not much of a problem ECE 491 Fall 2006 Lecture 12 - Metastability 20

MTBF Calculation Example - Virtex II Pro } Values from a Xilinx Technical note: } t = 0. 02 ns - 0. 05 ps (assume 0. 05 ps) } To = not given, but assume = 9. 6 as “as” = 10 -18 s } tr = 2. 3 ns } MTBF = 9. 89 X 1022 seconds = 7, 53 X 1016 years - not to worry! ECE 491 Fall 2006 Lecture 12 - Metastability 21

What to Do About Metastability } } } Start with simple synchronizer (single flip-flop) Calculate MTBF for your system Decide if it's acceptable If not, use a different design OR different design: } Two-stage flip-flop } Reduced-clock synchronizers ECE 491 Fall 2006 Lecture 12 - Metastability 22

Coming Up } } Detailed Design Handshaking Manchester Transmitter / Receiver Ethernet ECE 491 Fall 2006 Lecture 12 - Metastability 23

- Slides: 23