ECE 491 Senior Design I Lecture 1 Course

- Slides: 27

ECE 491 - Senior Design I Lecture 1 - Course Overview Fall 2008 Lab this week: meet at start of lab in AEC 429 See ECE 491 Moodle page for course materials Reading: Salt & Rothery Ch. 1 “Structural Design with Verilog” Sections 1 -4 Prof. John Nestor ECE Department Lafayette College Easton, Pennsylvania 18042 nestorj@lafayette. edu ECE 491 Fall 2008 Lecture 1 - Course Overview 1

Today’s Outline } } Course Goals Administrative Details About Design Problem Description ECE 491 Fall 2008 Lecture 1 - Course Overview 2

Course Objectives } Understand the “Design Process: 1. 2. 3. 4. 5. The steps of the electronic “design process”. The impact of constraints on design. The organization of design teams. Common tools for project management. Economic, environmental, social, political, ethical, health and safety, manufacturability, and sustainability concerns. } Design with FPGAs and Verilog: 1. 2. 3. 4. 5. 6. 7. 8. Understand the general structure of FPGAs Understand the basic constructs of Verilog HDL. Write Verilog code for combinational logic, sequential logic, and FSMs. Write a Verilog testbench that verifies the correctness of a design. Recognize and avoid common Verilog coding pitfalls. Understand timing of digital systems in FPGA-based systems. Understand the purpose of synchronizers in sequential logic designs. Understand handshaking between sequential circuits w/ different clocks. ECE 491 Fall 2008 Lecture 1 - Course Overview 3

Course Objectives (cont’d) } Understand Data Communications/Networking Concepts: 1. 2. 3. 4. Asynchronous serial communications. Manchester Code. Ethernet and Wi. Fi. The Open Systems Interconnect (OSI) Model. ECE 491 Fall 2008 Lecture 1 - Course Overview 4

Key Course Topics } FPGA-based Design with Verilog HDL } Data Communications and Networks } Engineering Design } } } The Design Process Constraints and Tradeoffs Design Verification Project Management Economic, environmental, social, political, ethical, health and safety, manufacturability, and sustainability concerns ECE 491 Fall 2008 Lecture 1 - Course Overview 5

Today’s Outline } } Course Goals Administrative Details About Design Problem Description ECE 491 Fall 2008 Lecture 1 - Course Overview 6

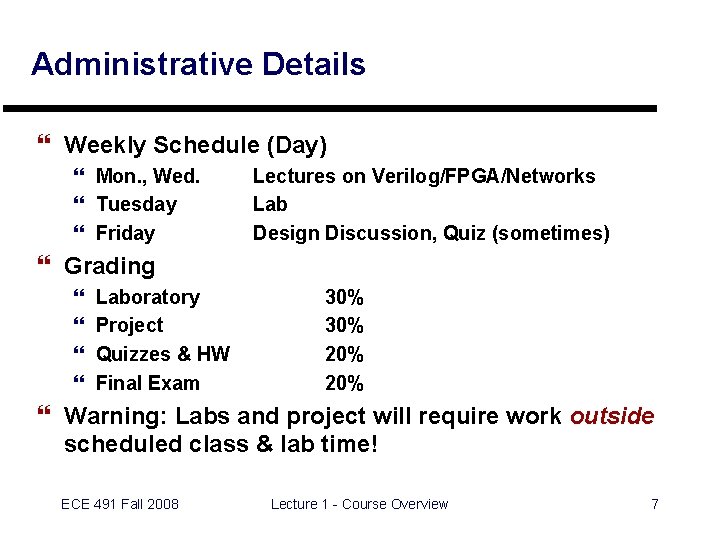

Administrative Details } Weekly Schedule (Day) } Mon. , Wed. } Tuesday } Friday Lectures on Verilog/FPGA/Networks Lab Design Discussion, Quiz (sometimes) } Grading } } Laboratory Project Quizzes & HW Final Exam 30% 20% } Warning: Labs and project will require work outside scheduled class & lab time! ECE 491 Fall 2008 Lecture 1 - Course Overview 7

Academic Expectations in the Lab } Attendance required } All students in a group are expected to contribute } Groups must work independently } It’s OK to discuss strategies & general approaches } It’s not OK* to share code or simulation results } Groups must meet design deadlines for full credit } Late penalty: 10% / day *“not OK” == “academic dishonesty” ECE 491 Fall 2008 Lecture 1 - Course Overview 8

Today’s Outline } } Course Goals Administrative Details About Design The Course Project ECE 491 Fall 2008 Lecture 1 - Course Overview 9

What is Engineering Design? “Engineering design is the process of devising a system, component, or process to meet desired needs. It is a decision-making process (often iterative), in which the basic sciences, mathematics, and the engineering sciences are applied to convert resources optimally to meet these stated needs. ” -ABET Criteria for Accrediting Engineering Programs “An engineer is someone who can build for a dollar what any damn fool can build for ten” -- Robert A. Heinlein ECE 491 Fall 2008 Lecture 1 - Course Overview 10

Some Characteristics of Design: } } } } Open-ended Subject to conflicting constraints (not just cost) Must generally conform to existing standards Requires tradeoffs Iterative Usually a team activity Analysis & verification essential to success Sophisticated planning and management needed ECE 491 Fall 2008 Lecture 1 - Course Overview 11

Design Constraints } Some Common Constraints } } } } } Cost Performance Environmental Manufacturability Sustainability Social Political Legal Ethical Health and safety ECE 491 Fall 2008 Lecture 1 - Course Overview 12

The Design Process } Usually defined as a sequence of steps } Several models are used } “Systematic Model of Design” e. g. , S&R } Colwell’s model in The Pentium Chronicles } Software Design Models • “Waterfall Model” - SW version of “Systematic Model” • Rapid Prototyping / “Extreme Programming” Model ECE 491 Fall 2008 Lecture 1 - Course Overview 13

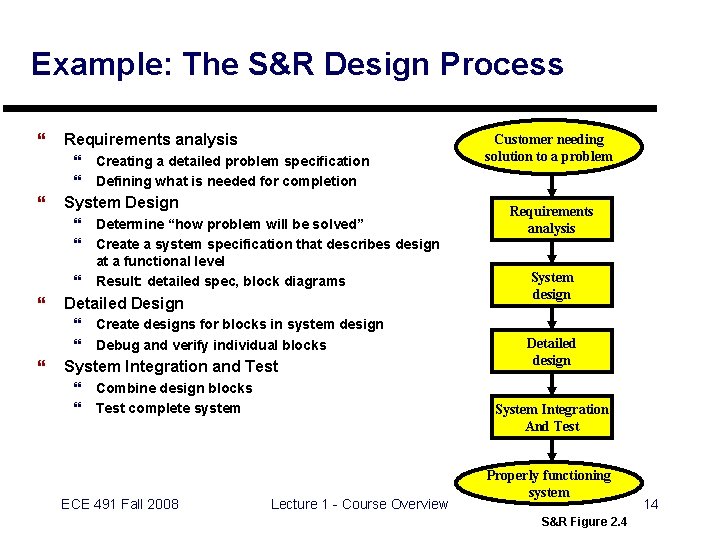

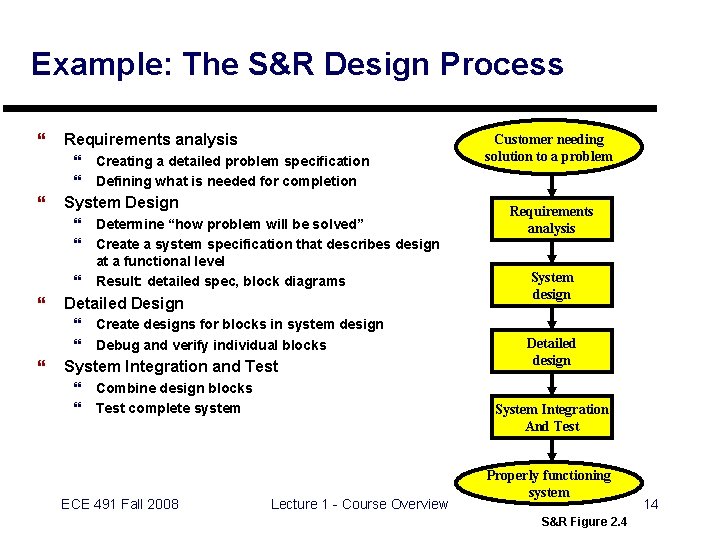

Example: The S&R Design Process } Requirements analysis } } } System Design } } Determine “how problem will be solved” Create a system specification that describes design at a functional level Result: detailed spec, block diagrams Detailed Design } } } Creating a detailed problem specification Defining what is needed for completion Create designs for blocks in system design Debug and verify individual blocks System Integration and Test } } Combine design blocks Test complete system ECE 491 Fall 2008 Customer needing solution to a problem Requirements analysis System design Detailed design System Integration And Test Lecture 1 - Course Overview Properly functioning system S&R Figure 2. 4 14

Design Process Models - Key Points } A model only approximates what really happens } Brooks: Conceptual Integrity is major challenge } Non-trivial projects require large teams } Communication of design to team members is essential } “Great designs are created by great designers” } Design errors are inevitable - need to: } } Anticipate (and look for) errors Avoid the needless creation of errors Deal with errors as they occur Tools for dealing with errors: • Verification (Simulation, Lab Testing) • Design Reviews ECE 491 Fall 2008 Lecture 1 - Course Overview 15

How We’ll Learn About Design } By example } } S&R text - general theory, project management Colwell “At Random” columns from IEEE Computer Brooks Turing Award Lecture “The Design of Design” Costello DAC ‘ 06 Lecture: “Iridium or i. Pod…” } By doing } ECE 491: small-group design of a wireless network } ECE 492: large-group design of a solar power system ECE 491 Fall 2008 Lecture 1 - Course Overview 16

Today’s Outline } } Course Goals Administrative Details About Design The Course Project ECE 491 Fall 2008 Lecture 1 - Course Overview 17

The Course Project } Design a wireless local-area network so that each “station” can communicate with other station Stations ECE 491 Fall 2008 Lecture 1 - Course Overview 18

Course Project - Key Questions 1. What physical link will we use? 2. How will we transmit data? (transmission) 3. How will stations cooperate to send and receive data? (protocol) 4. How can we break up the problem to make it tractable? 5. How will we implement the system? ECE 491 Fall 2008 Lecture 1 - Course Overview 19

1. Physical Link Options } } } Wired Fiber Optics Wireless - Optical Wireless - Microwave Wireless - VHF Radio ECE 491 Fall 2008 Lecture 1 - Course Overview 20

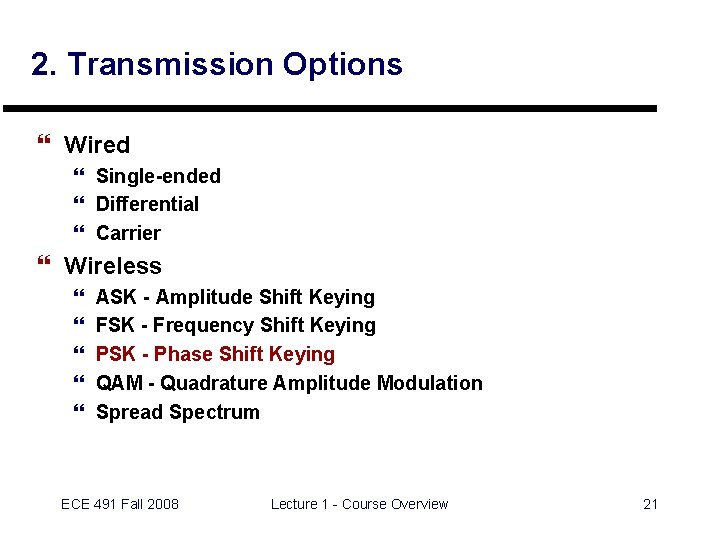

2. Transmission Options } Wired } Single-ended } Differential } Carrier } Wireless } } } ASK - Amplitude Shift Keying FSK - Frequency Shift Keying PSK - Phase Shift Keying QAM - Quadrature Amplitude Modulation Spread Spectrum ECE 491 Fall 2008 Lecture 1 - Course Overview 21

3. Protocol } A set of rules for communication over a network } Often standardized to allow interoperable hardware from different vendors } Ethernet - IEEE 802. 3 } Wireless - IEEE 802. 11 ECE 491 Fall 2008 Lecture 1 - Course Overview 22

4. Implementation Options } } Use existing hardware (e. g. , PC + Wi. Fi card) TTL Packages on a PCB or Breadboard Microcontroller plus serial interface Programmable Logic Devices } PALs / GALs } FPGAs } Application-Specific Integrated Circuit (ASIC) } Custom Integrated Circuit ECE 491 Fall 2008 Lecture 1 - Course Overview 23

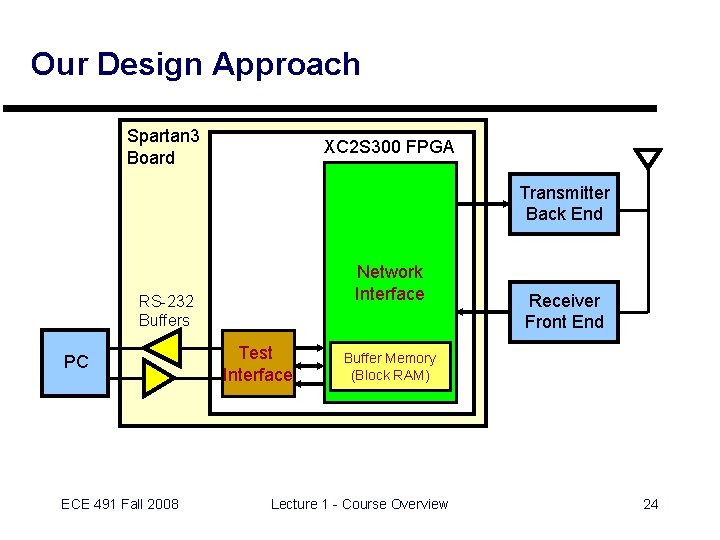

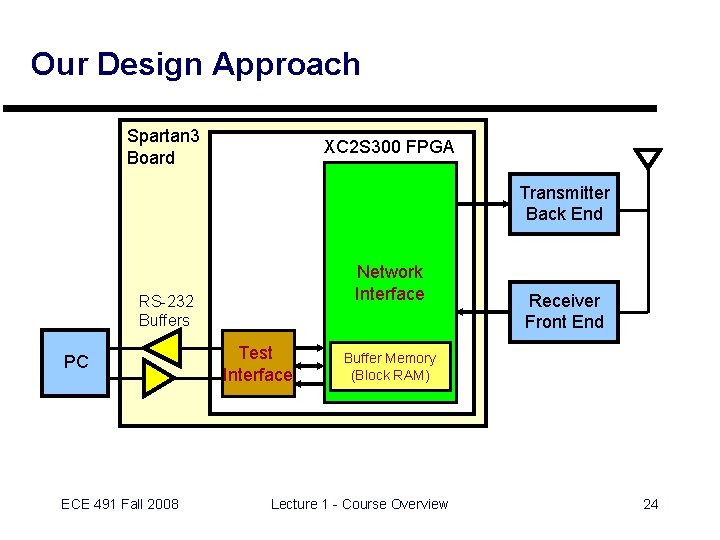

Our Design Approach Spartan 3 Board XC 2 S 300 FPGA Transmitter Back End Network Interface RS-232 Buffers PC ECE 491 Fall 2008 Test Interface Receiver Front End Buffer Memory (Block RAM) Lecture 1 - Course Overview 24

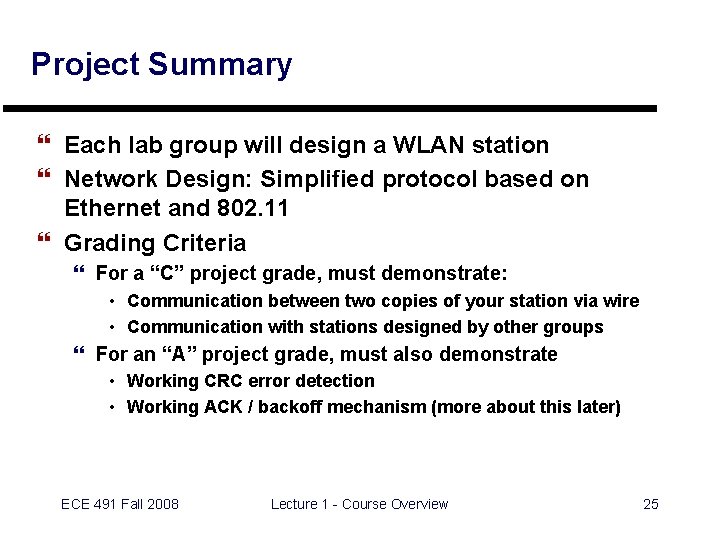

Project Summary } Each lab group will design a WLAN station } Network Design: Simplified protocol based on Ethernet and 802. 11 } Grading Criteria } For a “C” project grade, must demonstrate: • Communication between two copies of your station via wire • Communication with stations designed by other groups } For an “A” project grade, must also demonstrate • Working CRC error detection • Working ACK / backoff mechanism (more about this later) ECE 491 Fall 2008 Lecture 1 - Course Overview 25

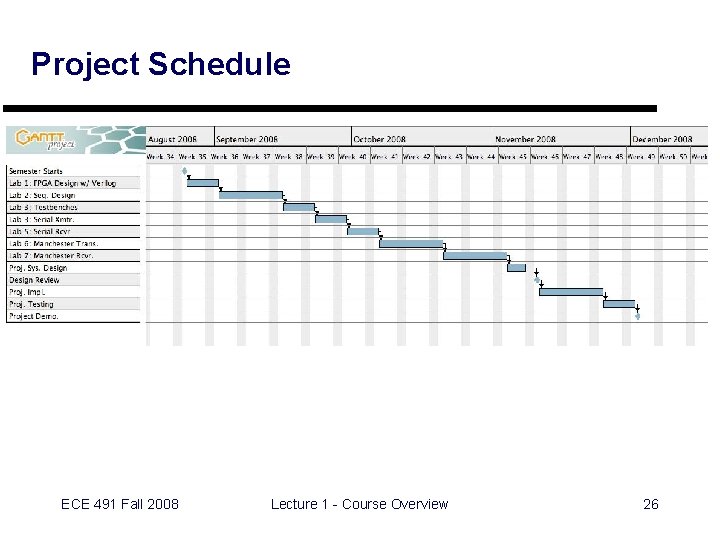

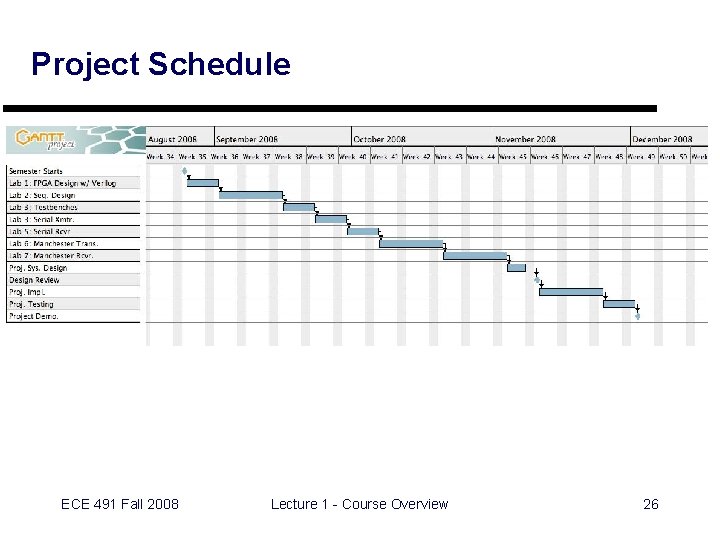

Project Schedule ECE 491 Fall 2008 Lecture 1 - Course Overview 26

Coming Up: } FPGA Review } Spartan Board Quick Intro } Digital Design with Verilog } Combinational Design } Sequential Design ECE 491 Fall 2008 Lecture 1 - Course Overview 27