1282009 Iowa State University EE 491 Senior Design

- Slides: 20

12/8/2009 Iowa State University EE 491 - Senior Design I Semester design review A TEST VEHICLE FOR RESEARCH ON THERMAL MANAGEMENT FOR INTEGRATED CIRCUITS Karl Peterson , Emmanuel Owusu, and Joshua Ellis

Our project is special… � International collaboration � Product conceptualization & specification in addition to design � Integrated circuit (IC) rather than system design � Research-orientated objectives

Problem Statement �Design an integrated circuit (IC) for testing activities related to Iowa State University research activities in the area of thermal measurement and management for highperformance chips �Research in this area is being conducted by Dr. Randy Geiger and Dr. Degang Chen and members of their research group

Problem Statement �Experimental activities related to this research have not been specifically planned �Part of our job has been to anticipate the type of tests for which the IC might be used �Flexibility and configurability are key features of the solution we have proposed �In preparation for the design, we imagined possible tests scenarios in detail and discussed them with the research team

Types of IC testing activities Evaluation of existing or novel analog temperature sensing circuits 2. Study of failure mechanisms affecting the long-term reliability of high-performance chips 3. Development of dynamic thermal management strategies taking advantage of the products of items (1) and (2) 1.

Solution approach �Flexibility can be achieved by realizing complex testing functionality on a programmable external controller �The IC itself allows test measurements to be taken and experimental conditions to be set while the controller manages these operations according to the specific test being conducted

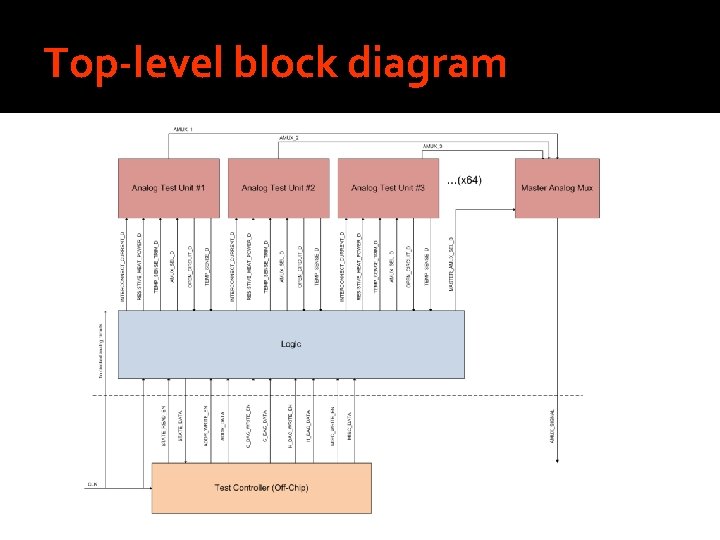

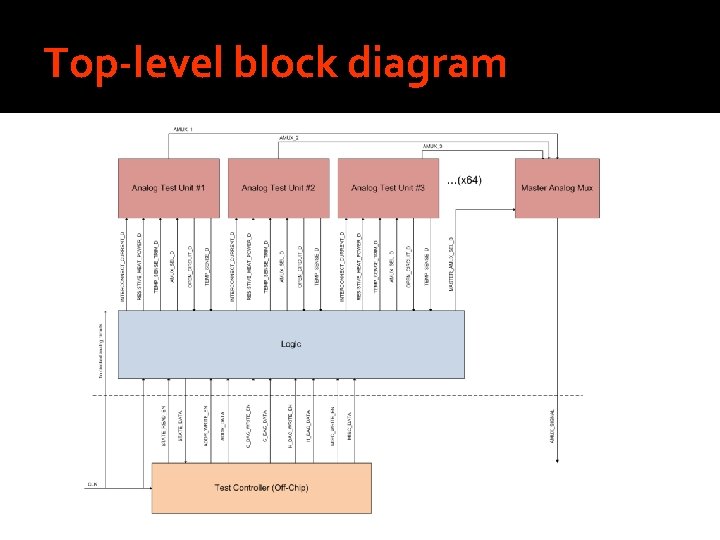

Top-level block diagram

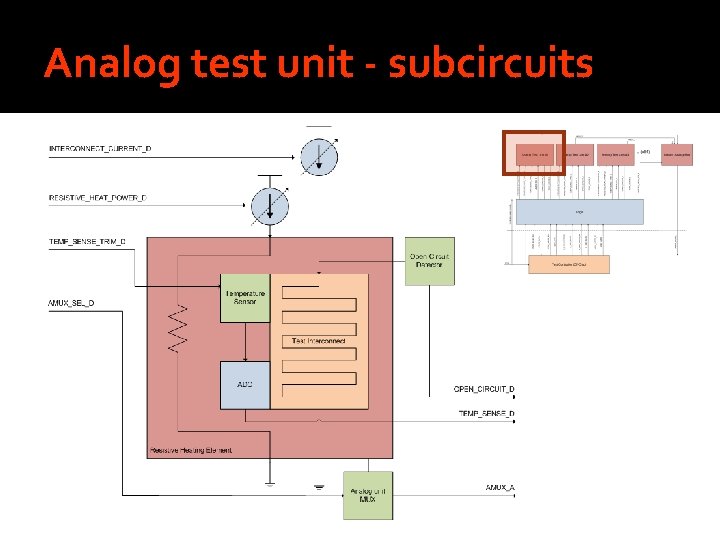

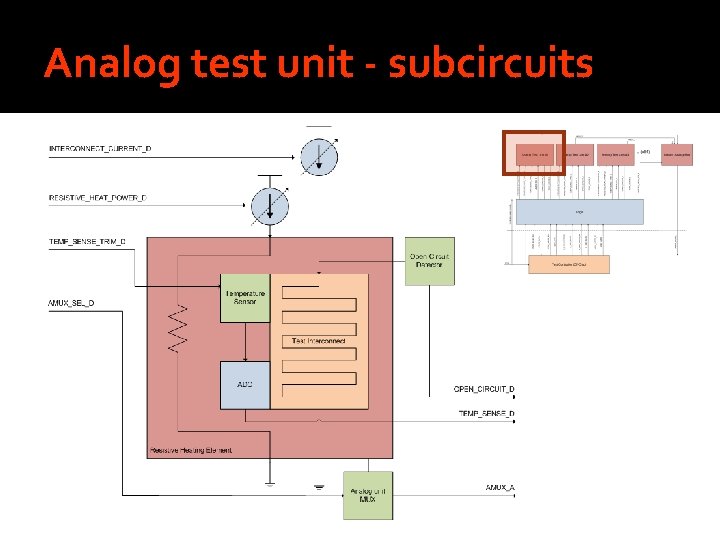

Analog test unit - subcircuits

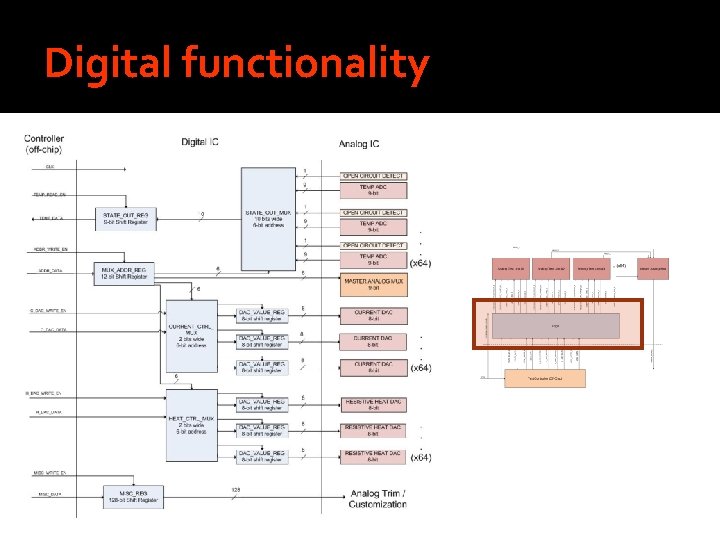

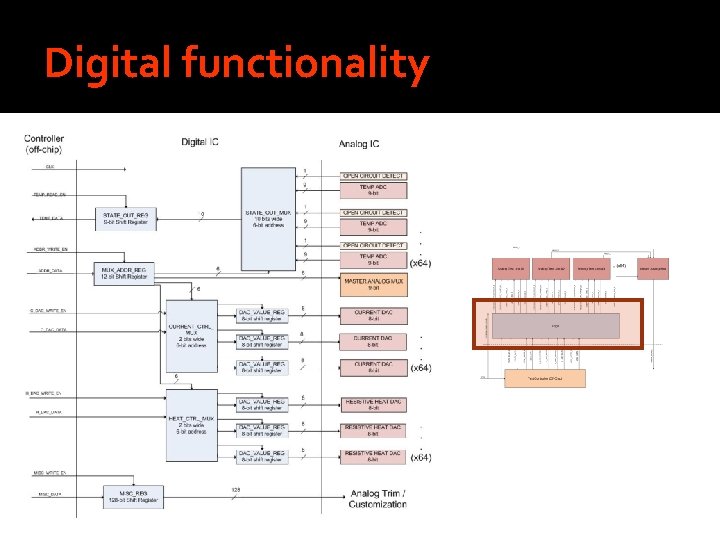

Digital functionality

Design approach � ‘Divide-and-conquer’ � Top-down design methodology � Levels of design Behavioral (Verilog, Verilog-A) Transistor level (schematic) Layout (mask description) � All descriptions (and documentation) are organized in Cadence design environment � Shared library

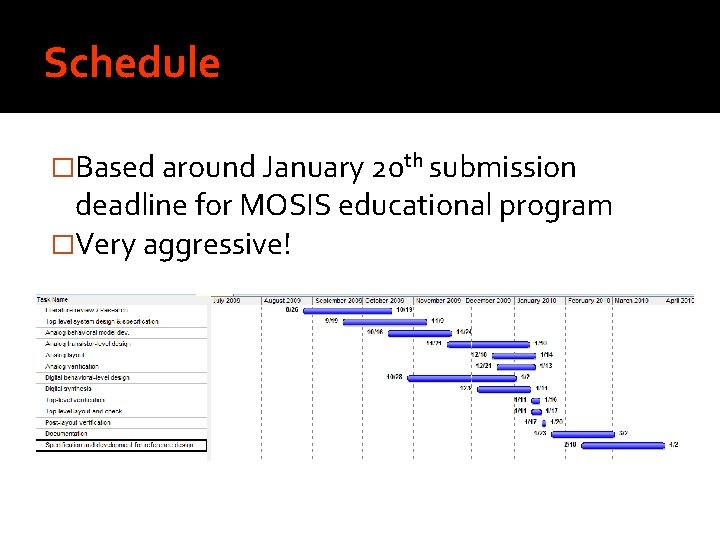

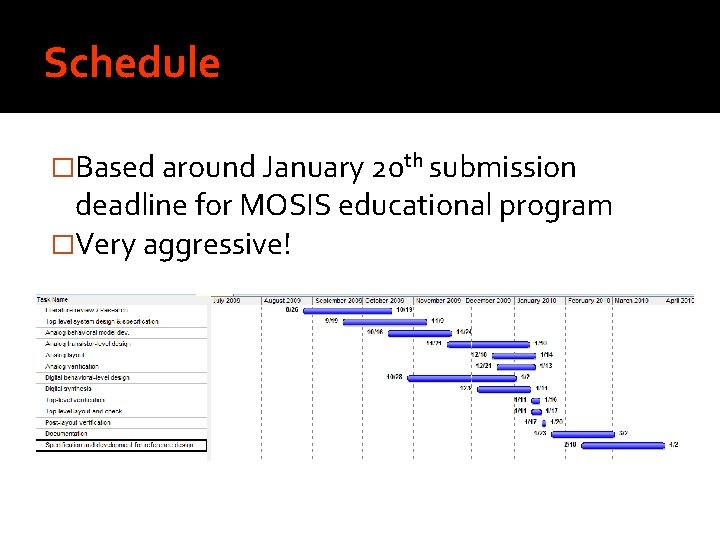

Schedule �Based around January 20 th submission deadline for MOSIS educational program �Very aggressive!

Resources �Design & fabrication are separated in modern integrated circuit operations �Design itself is really a software task, resources include: Software tools (Cadence front-to-back tool-set, Model. Sim, etc. ) Engineering labor

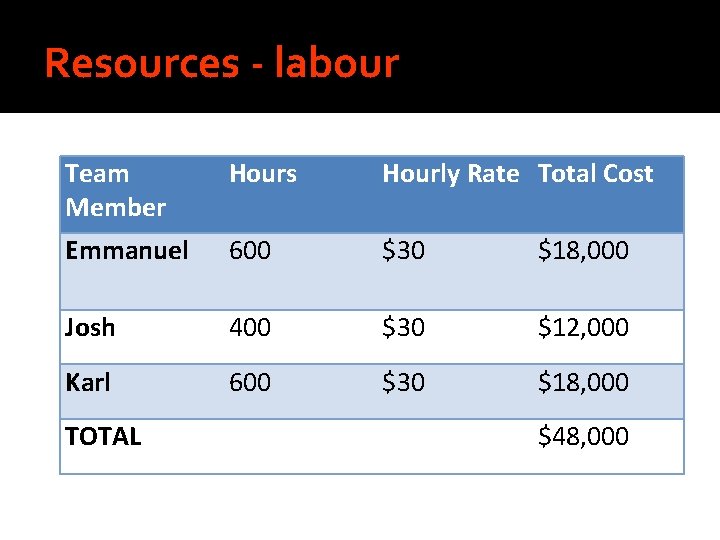

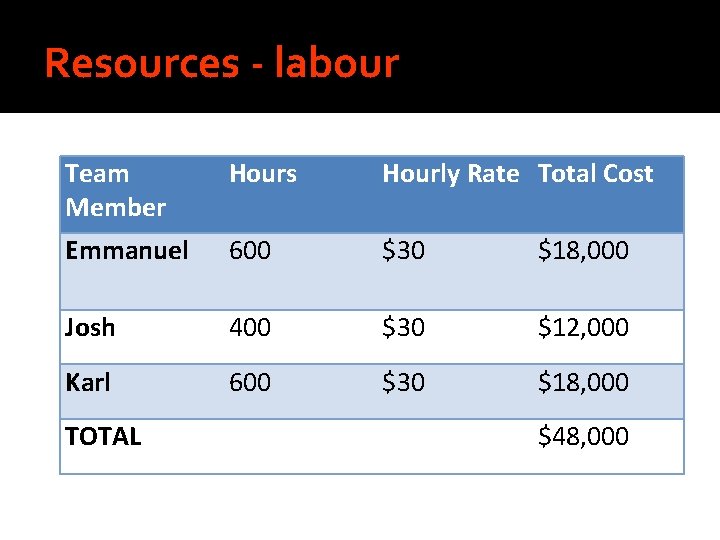

Table 7 - Labor costs for team members (September 2009 - April 2010) Resources - labour Team Member Hours Hourly Rate Total Cost Emmanuel 600 $30 $18, 000 Josh 400 $30 $12, 000 Karl 600 $30 $18, 000 TOTAL $48, 000

Risks & risk mitigation �Aggressive schedule, tight deadline Risk of not meeting deadline In this case, our product cannot be used for research or its use may be delayed �Near-impossibility of modification after fabrication Statistical variations in the fabrication process Oversights in verification

Thank you! �Any questions? �Details about sub-blocks?

BACKUP SLIDES

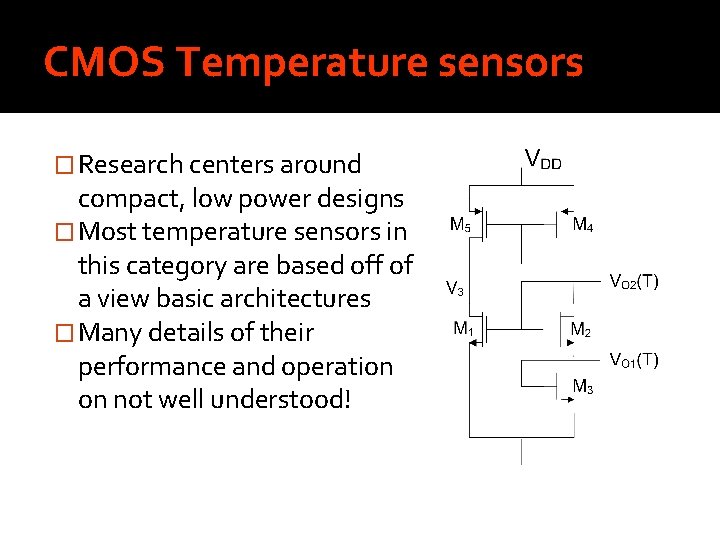

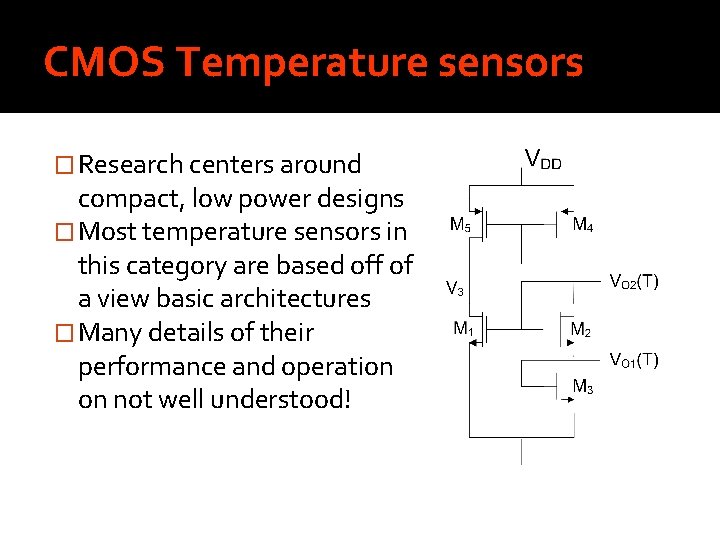

CMOS Temperature sensors � Research centers around compact, low power designs � Most temperature sensors in this category are based off of a view basic architectures � Many details of their performance and operation on not well understood!

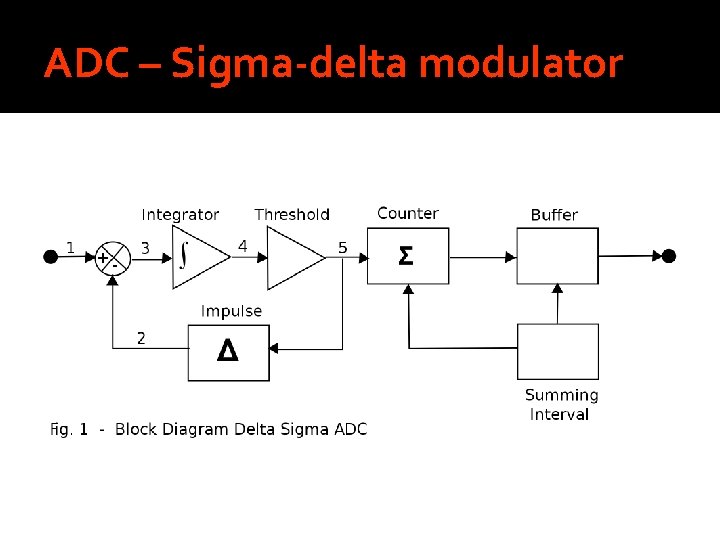

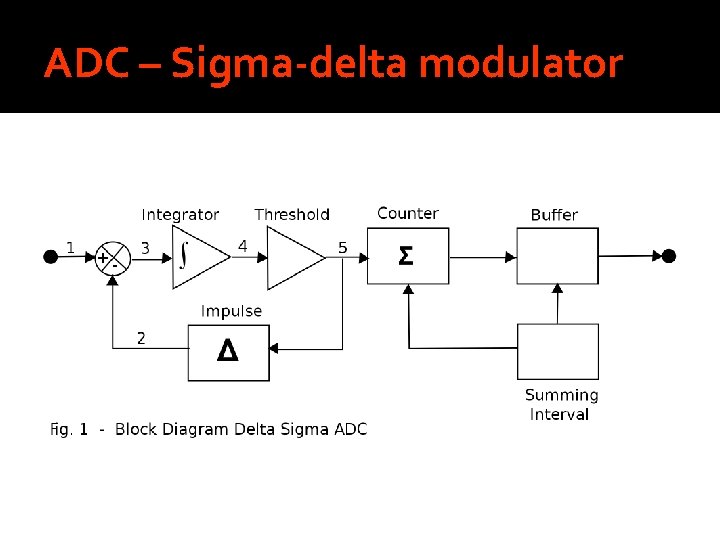

ADC – Sigma-delta modulator

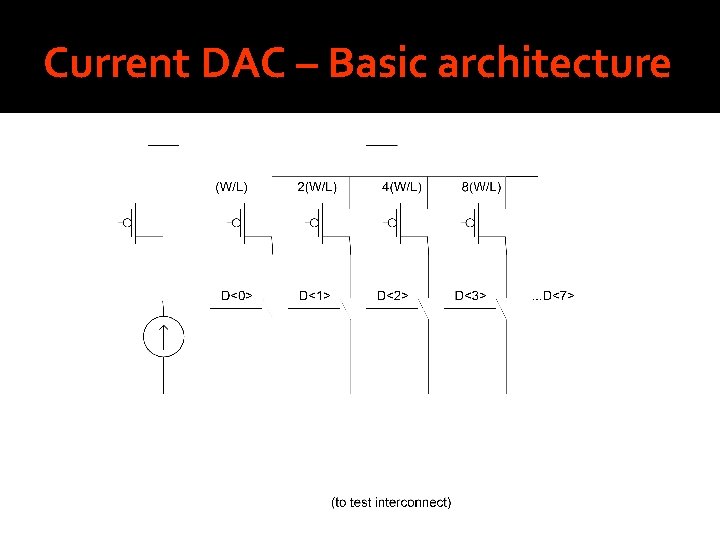

Test interconnect

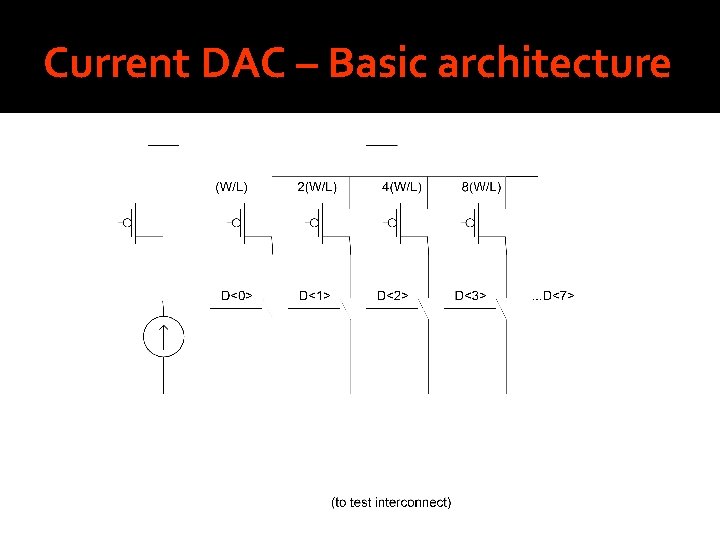

Current DAC – Basic architecture