ECE 406 Design of Complex Digital Systems Lecture

![Declaring Memories are defined by the syntax: <bit_range> <name> [<addressing_range>] reg bitmem [0: 1023] Declaring Memories are defined by the syntax: <bit_range> <name> [<addressing_range>] reg bitmem [0: 1023]](https://slidetodoc.com/presentation_image_h/368d6059e865490f97c0ea7b7f60d92b/image-4.jpg)

![Model for a ROM module ROM(addr, dout); input [13: 0] addr; output [7: 0] Model for a ROM module ROM(addr, dout); input [13: 0] addr; output [7: 0]](https://slidetodoc.com/presentation_image_h/368d6059e865490f97c0ea7b7f60d92b/image-6.jpg)

![Instruction Format l Opcode » IR[15: 12] l Addressing mode » Immediate (sign extension) Instruction Format l Opcode » IR[15: 12] l Addressing mode » Immediate (sign extension)](https://slidetodoc.com/presentation_image_h/368d6059e865490f97c0ea7b7f60d92b/image-14.jpg)

- Slides: 24

ECE 406 – Design of Complex Digital Systems Lecture 11: Memories, LC-3 Instruction Set Spring 2007 W. Rhett Davis NC State University with significant material from Paul Franzon, Bill Allen, & Xun Liu W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 1

Today’s Lecture l Using Memories l Review of the LC 3 Instruction Set W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 2

Memories Modules of even modest complexity usually contain memories. Applications of memories include register files, RAM & ROM. Memories are simply arrays of identical registers! In a memory, the “registers” are called “words”. So a memory is conventionally referred to as “n word by m bit memory”. Here, n is the number of words (array elements) and m is the size of each word. (This often shortened to “n x m”. ) W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 3

![Declaring Memories are defined by the syntax bitrange name addressingrange reg bitmem 0 1023 Declaring Memories are defined by the syntax: <bit_range> <name> [<addressing_range>] reg bitmem [0: 1023]](https://slidetodoc.com/presentation_image_h/368d6059e865490f97c0ea7b7f60d92b/image-4.jpg)

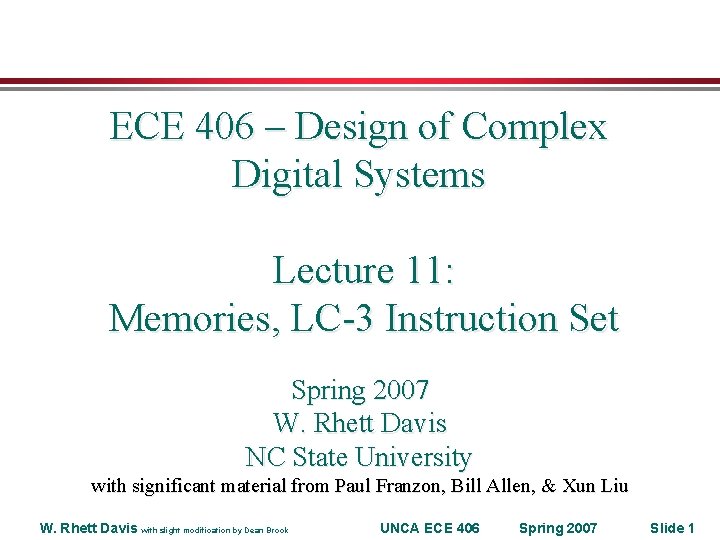

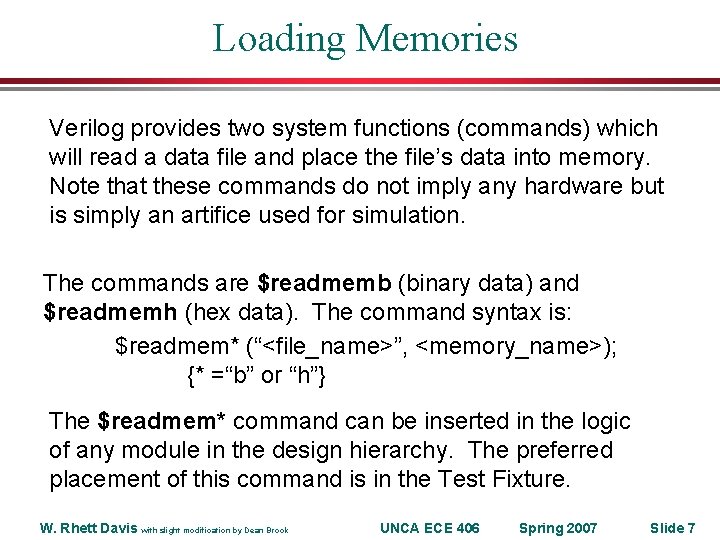

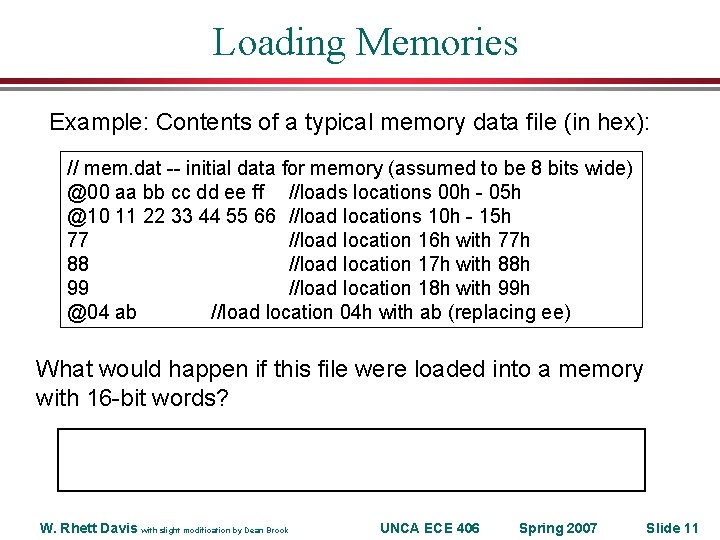

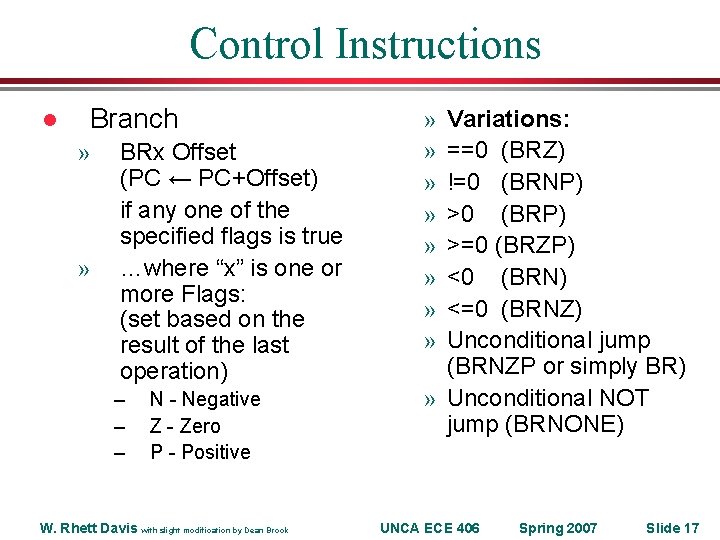

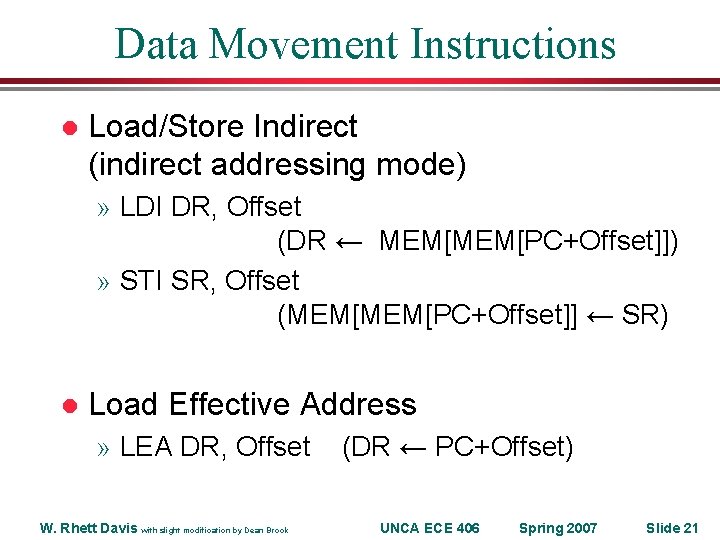

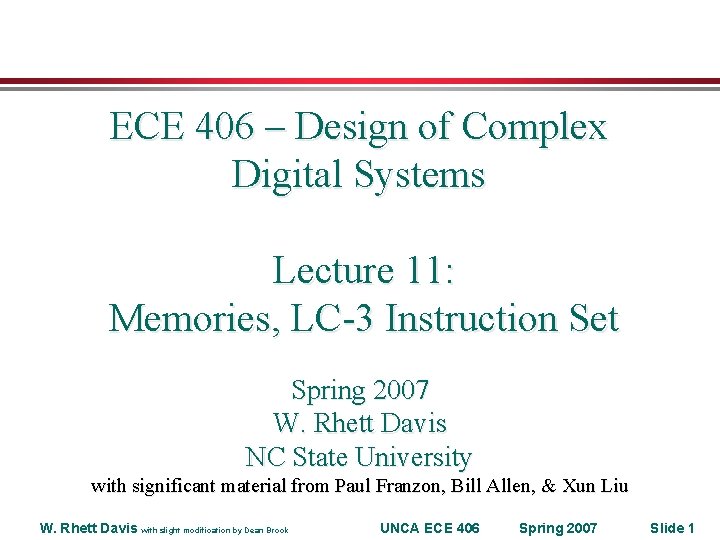

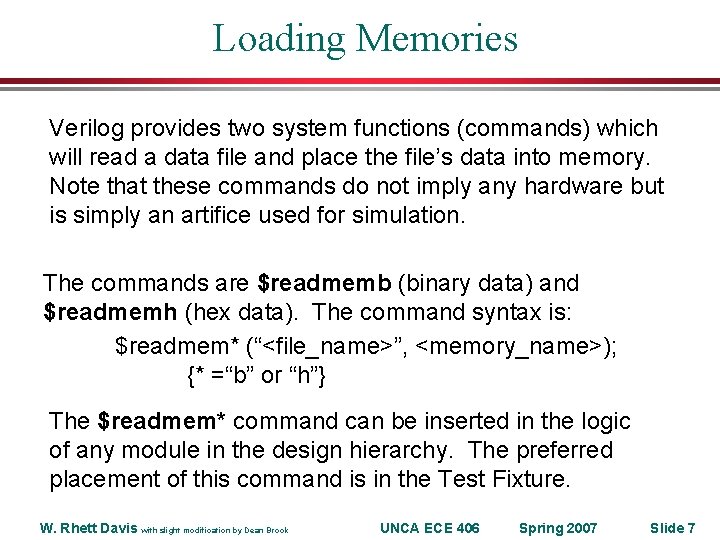

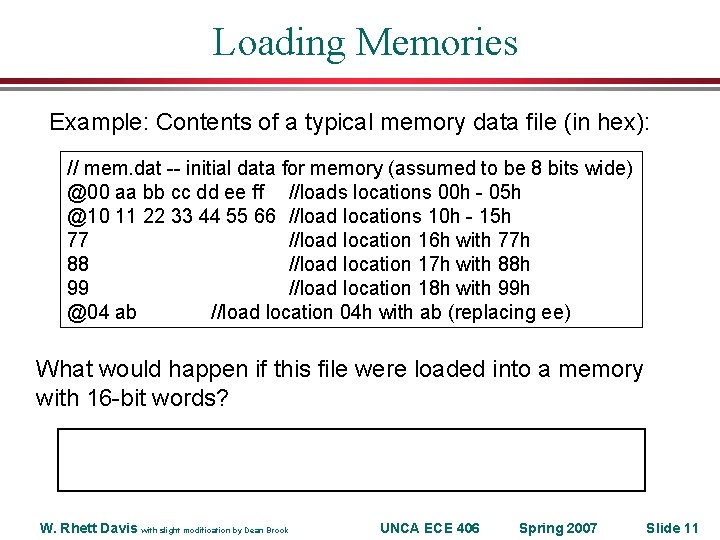

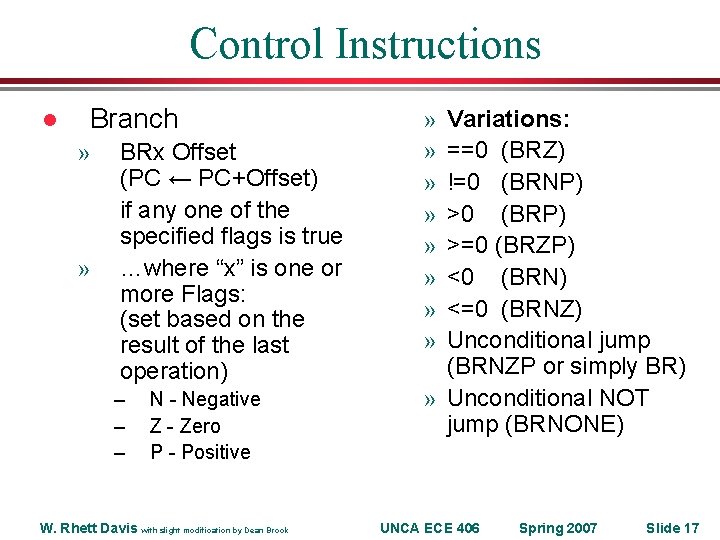

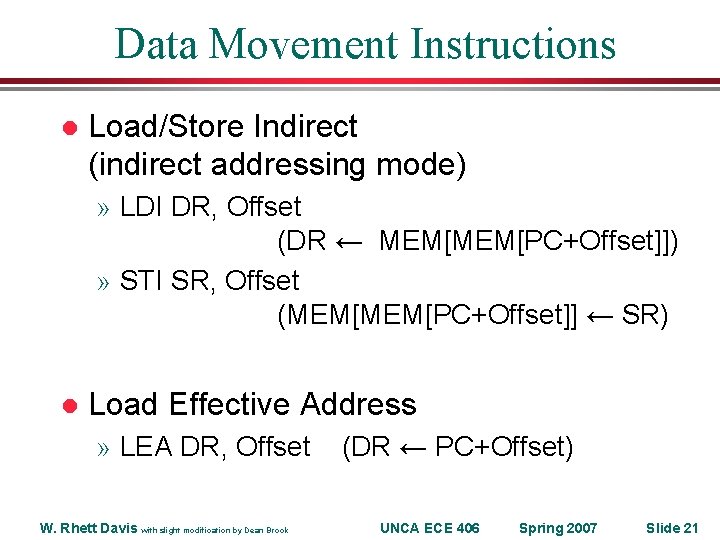

Declaring Memories are defined by the syntax: <bit_range> <name> [<addressing_range>] reg bitmem [0: 1023] reg [7: 0] MEM [0: 16383] // 1 K x 1 (bit) memory // 16 K x 8 or 16 K bytes Note that the addressing range is usually specified as [<low_address> : <high_address>] and for physical reasons, the address range starts at 0. W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 4

Verilog Language Structure Final comment: The syntax of Verilog (and physical structure of a memory) does not allow a portion of a memory word to be accessed. To read a single bit (or bit group), a memory word is brought out (read) and then dissected by additional logic. More importantly, on a write, the entire memory word must be written. Therefore to change only part of a memory word’s data, a read, modify, write must be done. W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 5

![Model for a ROM module ROMaddr dout input 13 0 addr output 7 0 Model for a ROM module ROM(addr, dout); input [13: 0] addr; output [7: 0]](https://slidetodoc.com/presentation_image_h/368d6059e865490f97c0ea7b7f60d92b/image-6.jpg)

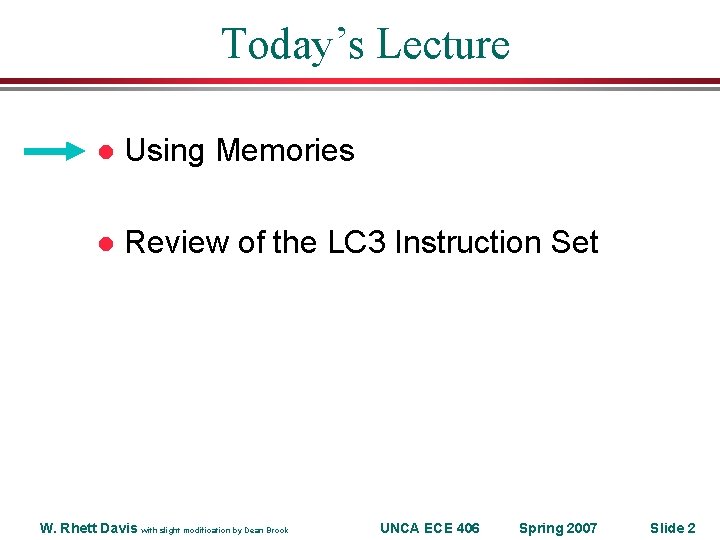

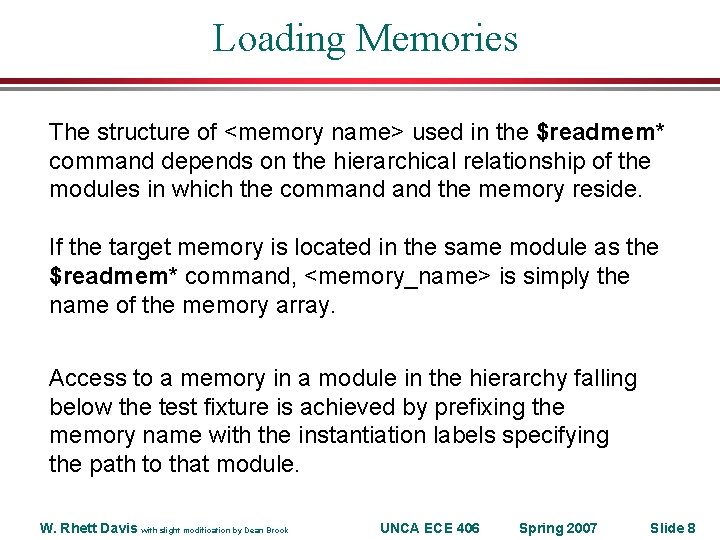

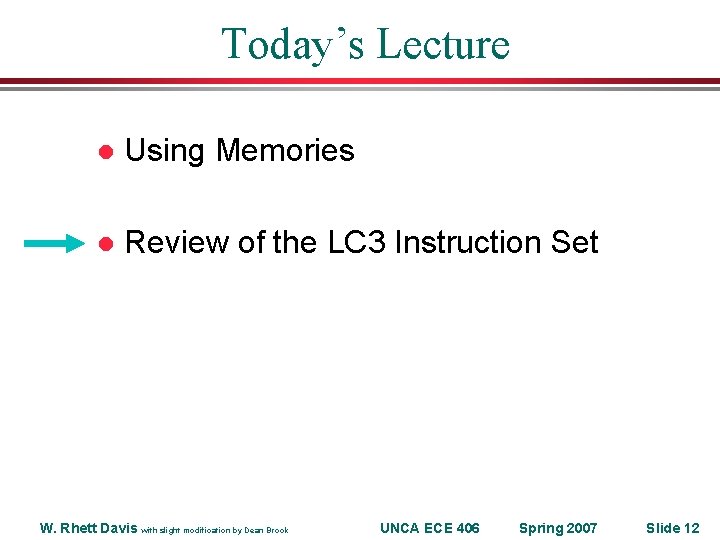

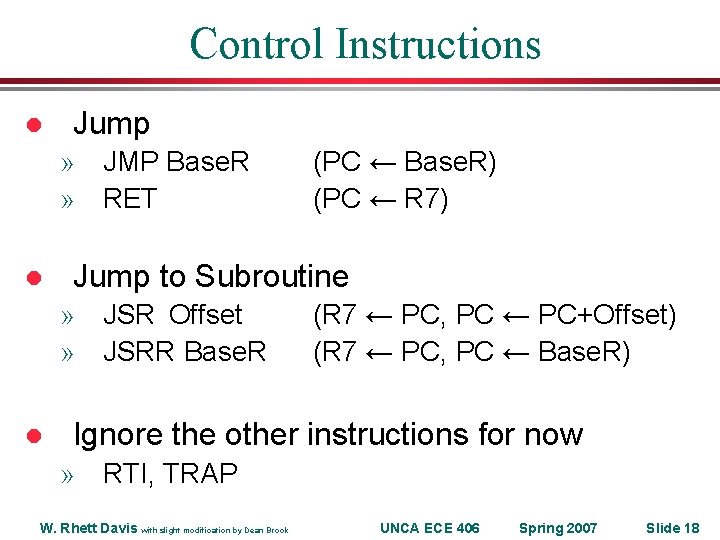

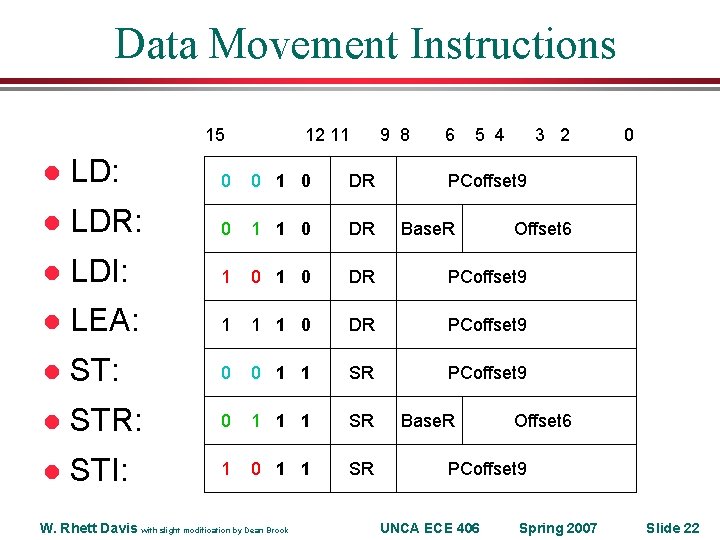

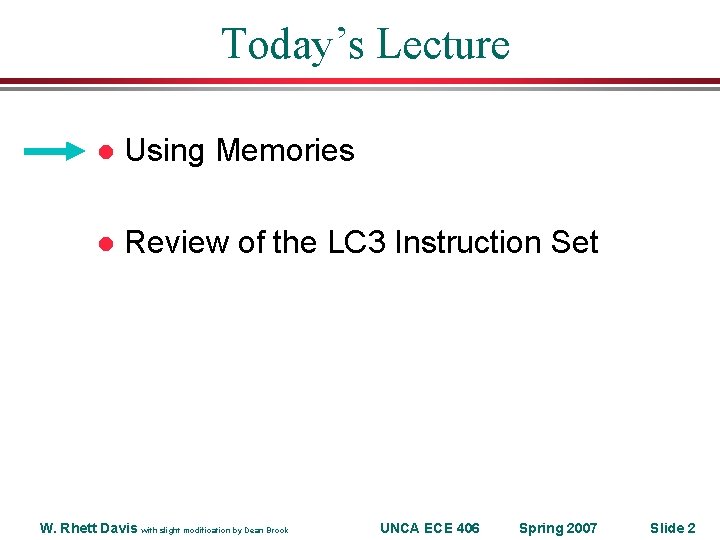

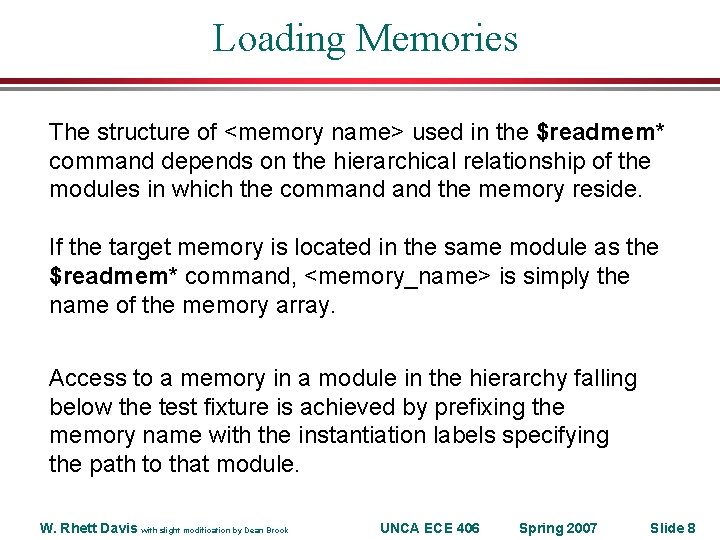

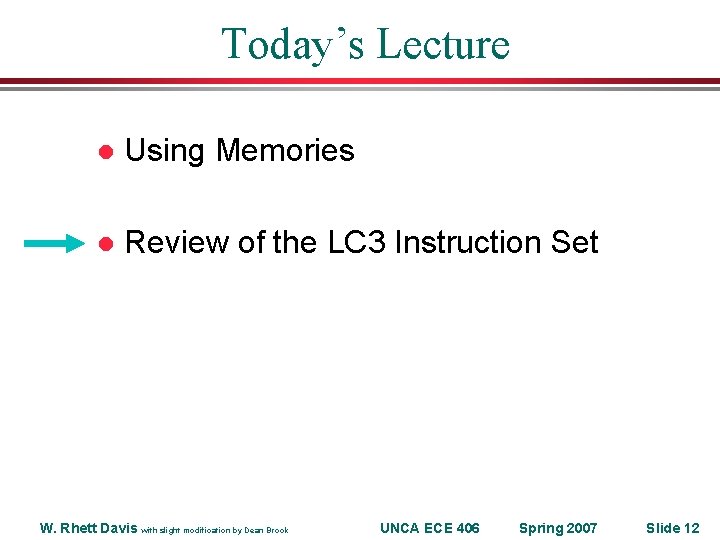

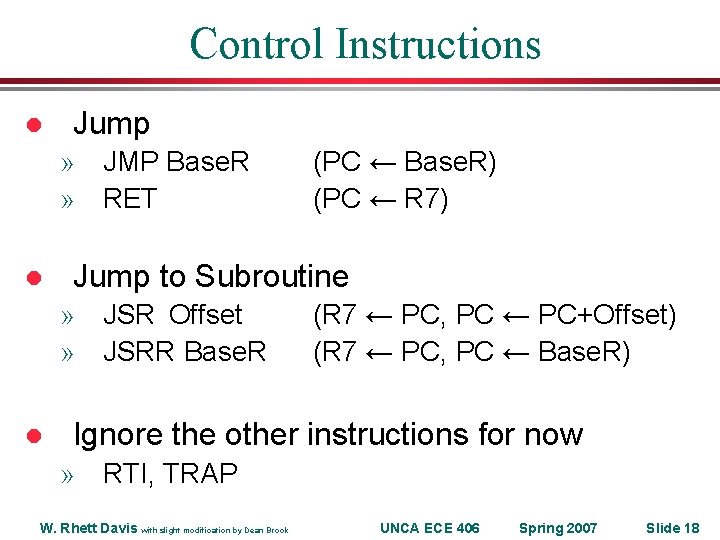

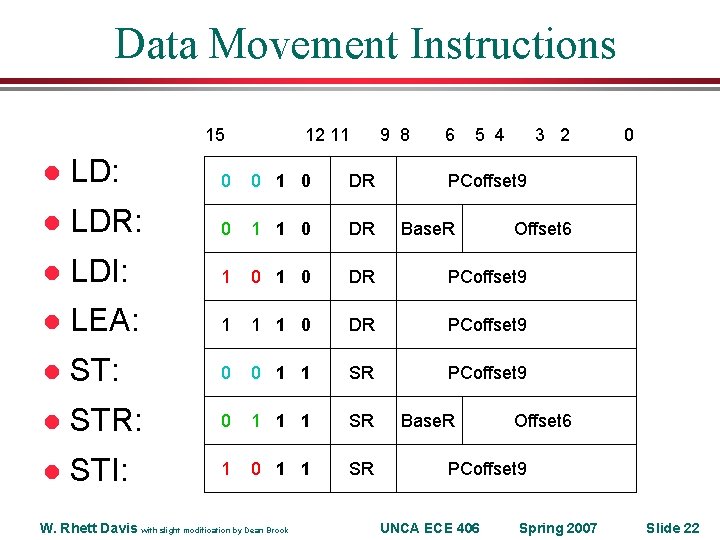

Model for a ROM module ROM(addr, dout); input [13: 0] addr; output [7: 0] dout; reg [7: 0] MEM [0: 16383] // 16 K x 8 or 16 K bytes always @(addr) dout <= MEM[addr]; endmodule W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 6

Loading Memories Verilog provides two system functions (commands) which will read a data file and place the file’s data into memory. Note that these commands do not imply any hardware but is simply an artifice used for simulation. The commands are $readmemb (binary data) and $readmemh (hex data). The command syntax is: $readmem* (“<file_name>”, <memory_name>); {* =“b” or “h”} The $readmem* command can be inserted in the logic of any module in the design hierarchy. The preferred placement of this command is in the Test Fixture. W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 7

Loading Memories The structure of <memory name> used in the $readmem* command depends on the hierarchical relationship of the modules in which the command the memory reside. If the target memory is located in the same module as the $readmem* command, <memory_name> is simply the name of the memory array. Access to a memory in a module in the hierarchy falling below the test fixture is achieved by prefixing the memory name with the instantiation labels specifying the path to that module. W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 8

Loading Memories Examples: 1. A test fixture contains a memory named MEM and the hex data file is named mem. dat. The $readmem* command would be: $readmemh (“mem. dat”, MEM); 2. If instance dut contains a memory called MEM, it can be referenced as: $readmemh (“mem. dat”, dut. MEM); W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 9

Loading Memories The memory data file is a free format text file. Values read from the file are loaded sequentially into the memory (subject to addressing commands in the file). The file must contain only the binary or hexadecimal data values, address specifications, white space and comments (both // and /* */ are recognized), . Each value must be separated with white space, comment, or new-line. Data values are loaded starting at the beginning of memory unless a starting-address is specified. Load addresses can be specified with the “@” symbol followed by an address specification. W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 10

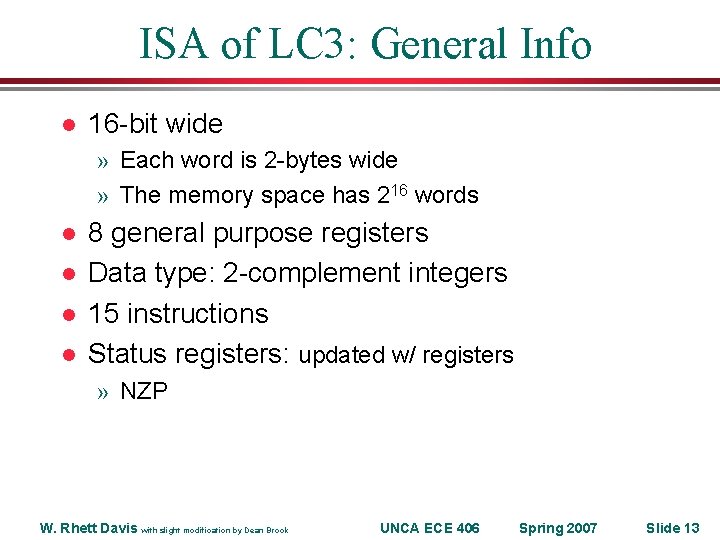

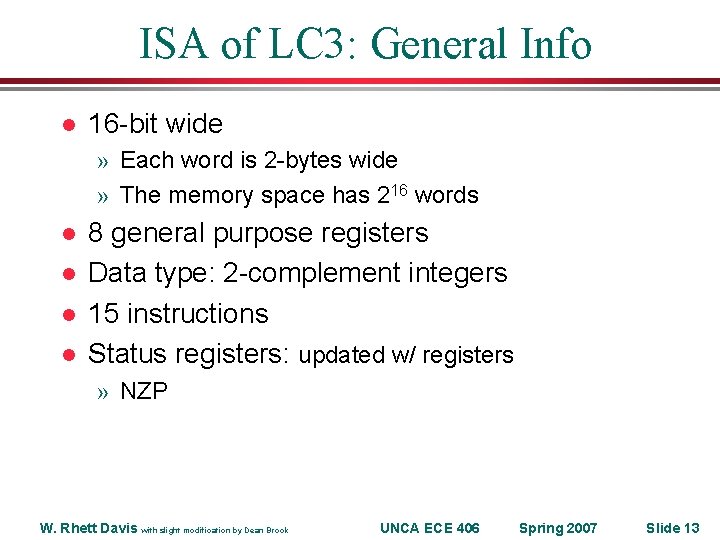

Loading Memories Example: Contents of a typical memory data file (in hex): // mem. dat -- initial data for memory (assumed to be 8 bits wide) @00 aa bb cc dd ee ff //loads locations 00 h - 05 h @10 11 22 33 44 55 66 //load locations 10 h - 15 h 77 //load location 16 h with 77 h 88 //load location 17 h with 88 h 99 //load location 18 h with 99 h @04 ab //load location 04 h with ab (replacing ee) What would happen if this file were loaded into a memory with 16 -bit words? W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 11

Today’s Lecture l Using Memories l Review of the LC 3 Instruction Set W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 12

ISA of LC 3: General Info l 16 -bit wide » Each word is 2 -bytes wide » The memory space has 216 words l l 8 general purpose registers Data type: 2 -complement integers 15 instructions Status registers: updated w/ registers » NZP W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 13

![Instruction Format l Opcode IR15 12 l Addressing mode Immediate sign extension Instruction Format l Opcode » IR[15: 12] l Addressing mode » Immediate (sign extension)](https://slidetodoc.com/presentation_image_h/368d6059e865490f97c0ea7b7f60d92b/image-14.jpg)

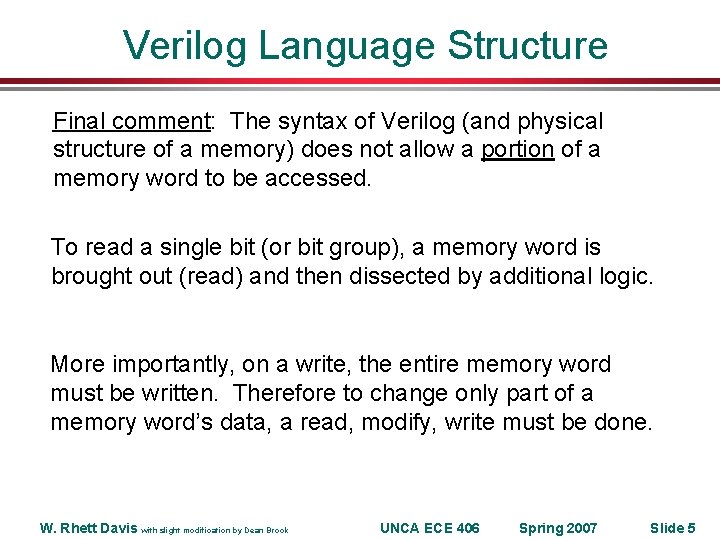

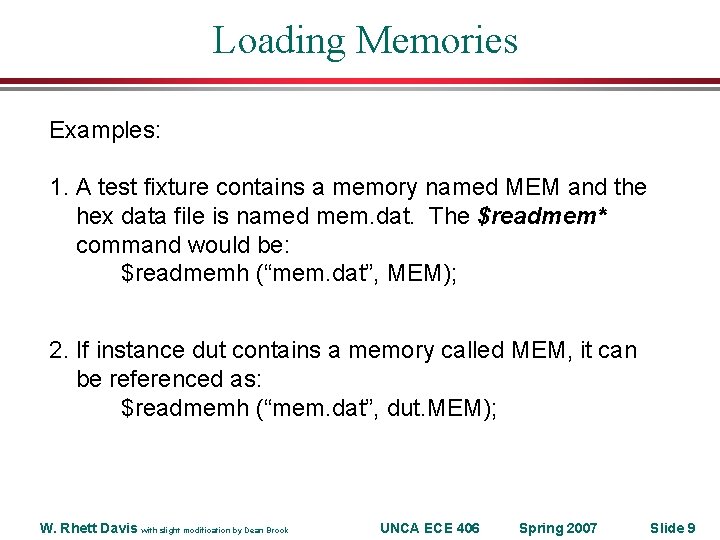

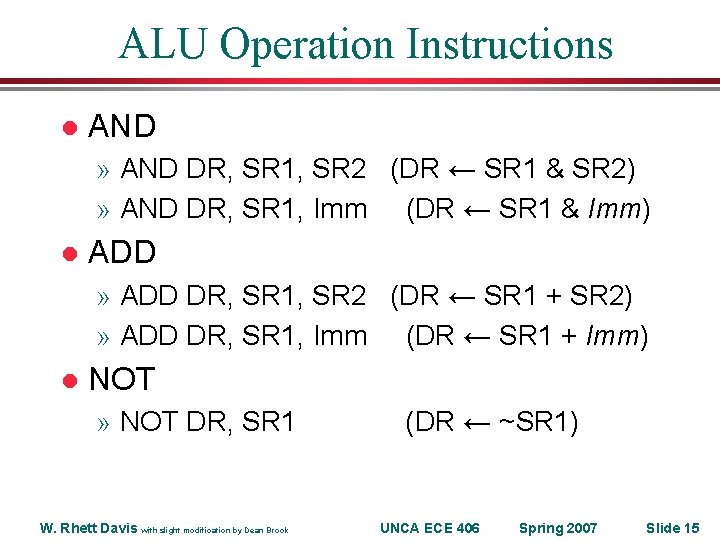

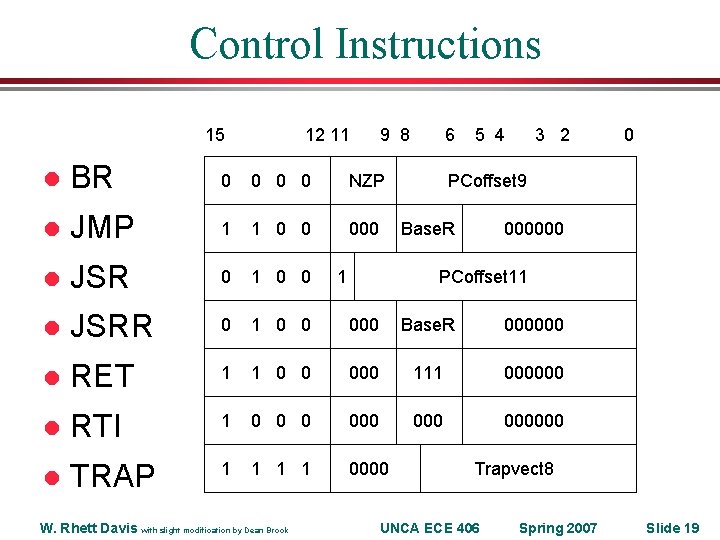

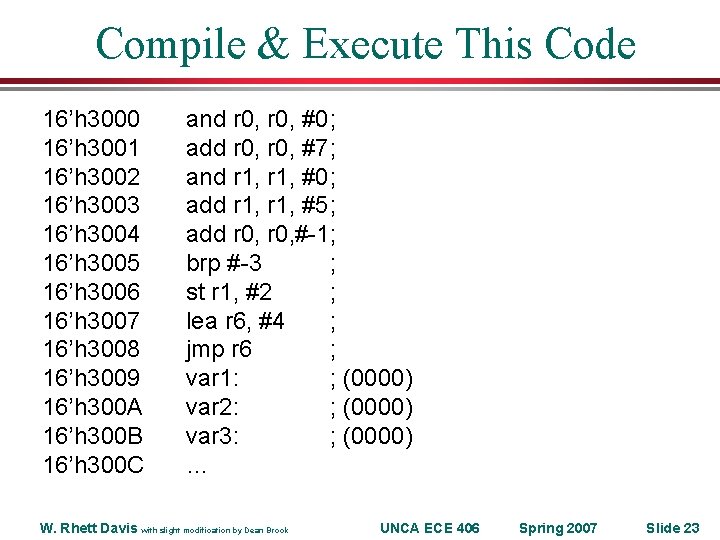

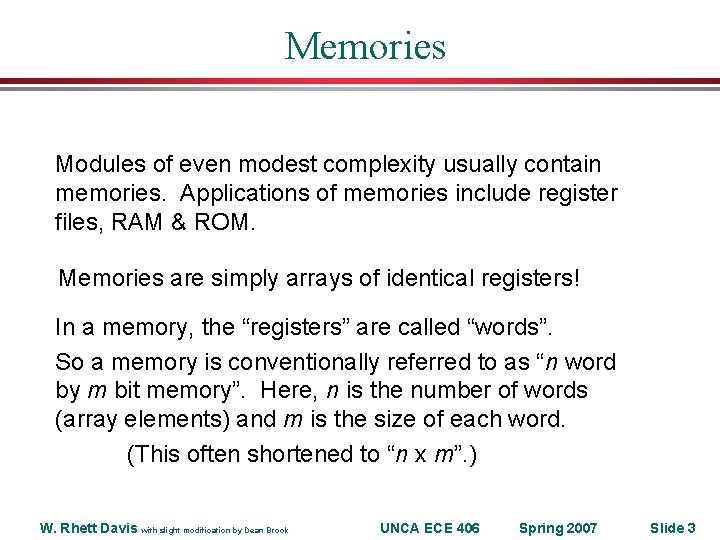

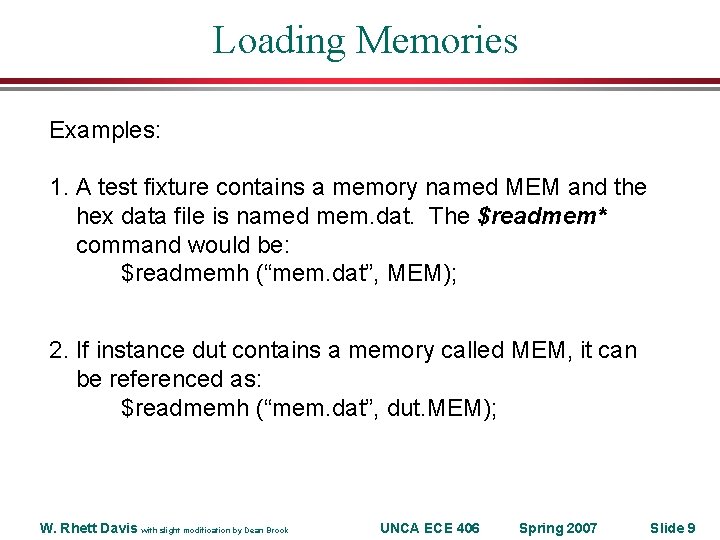

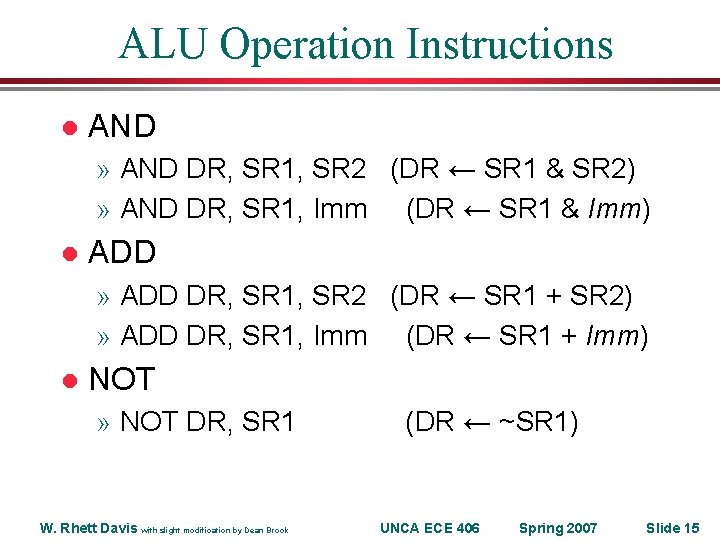

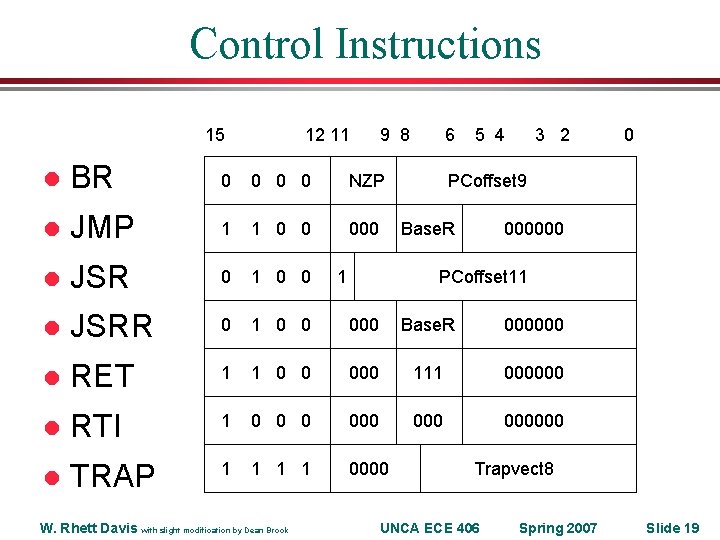

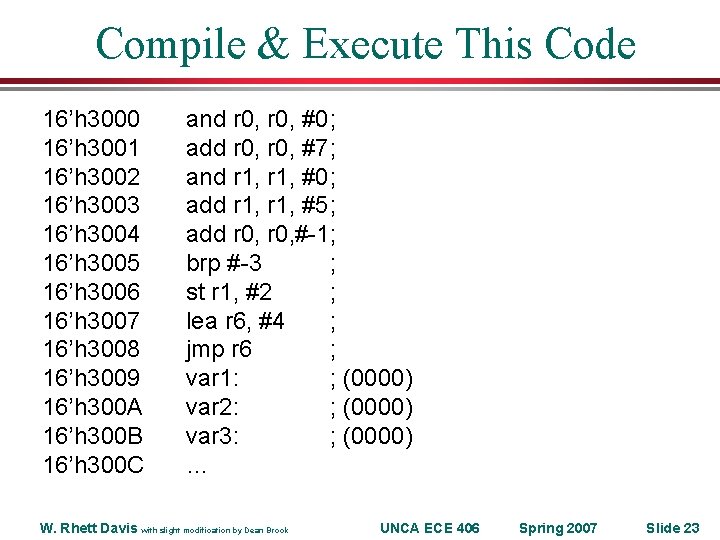

Instruction Format l Opcode » IR[15: 12] l Addressing mode » Immediate (sign extension) » Register » Memory: PC relative » Memory: indirect » Memory: base+offset W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 14

ALU Operation Instructions l AND » AND DR, SR 1, SR 2 (DR ← SR 1 & SR 2) » AND DR, SR 1, Imm (DR ← SR 1 & Imm) l ADD » ADD DR, SR 1, SR 2 (DR ← SR 1 + SR 2) » ADD DR, SR 1, Imm (DR ← SR 1 + Imm) l NOT » NOT DR, SR 1 W. Rhett Davis with slight modification by Dean Brock (DR ← ~SR 1) UNCA ECE 406 Spring 2007 Slide 15

ALU Operation Instructions l l l ADD AND NOT 15 12 11 9 8 6 5 4 0 0 0 1 DR SR 1 1 0 1 DR SR 1 0 0 1 DR SR 1 1 1 0 0 1 DR SR 1 W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 0 3 2 0 0 SR 2 imm 5 111111 Spring 2007 Slide 16

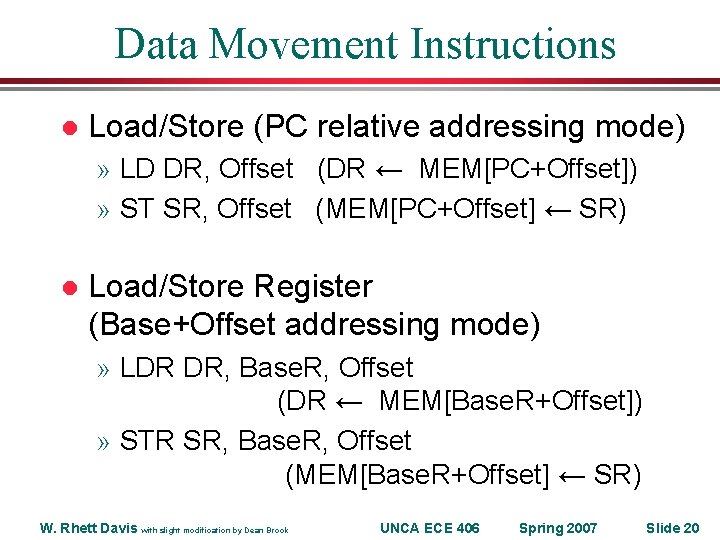

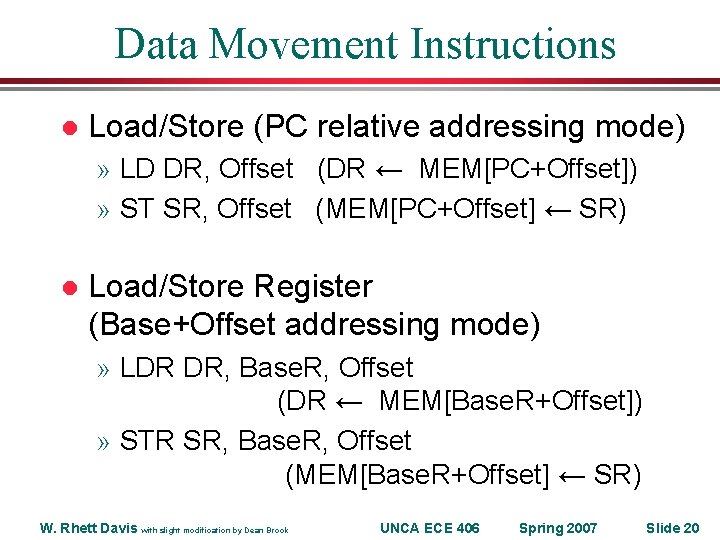

Control Instructions l Branch » » BRx Offset (PC ← PC+Offset) if any one of the specified flags is true …where “x” is one or more Flags: (set based on the result of the last operation) – – – N - Negative Z - Zero P - Positive W. Rhett Davis with slight modification by Dean Brock » » » » Variations: ==0 (BRZ) !=0 (BRNP) >0 (BRP) >=0 (BRZP) <0 (BRN) <=0 (BRNZ) Unconditional jump (BRNZP or simply BR) » Unconditional NOT jump (BRNONE) UNCA ECE 406 Spring 2007 Slide 17

Control Instructions l Jump » JMP Base. R » RET l Jump to Subroutine » JSR Offset » JSRR Base. R l (PC ← Base. R) (PC ← R 7) (R 7 ← PC, PC ← PC+Offset) (R 7 ← PC, PC ← Base. R) Ignore the other instructions for now » RTI, TRAP W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 18

Control Instructions 15 12 11 9 8 6 5 4 3 2 l BR 0 0 NZP l JMP 1 1 0 0 000 l JSR 0 1 0 0 l JSRR 0 1 0 0 000 Base. R 000000 l RET 1 1 0 0 000 111 000000 l RTI 1 0 000 000000 l TRAP 1 1 0000 W. Rhett Davis with slight modification by Dean Brock 0 PCoffset 9 Base. R 000000 PCoffset 11 1 Trapvect 8 UNCA ECE 406 Spring 2007 Slide 19

Data Movement Instructions l Load/Store (PC relative addressing mode) » LD DR, Offset (DR ← MEM[PC+Offset]) » ST SR, Offset (MEM[PC+Offset] ← SR) l Load/Store Register (Base+Offset addressing mode) » LDR DR, Base. R, Offset (DR ← MEM[Base. R+Offset]) » STR SR, Base. R, Offset (MEM[Base. R+Offset] ← SR) W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 20

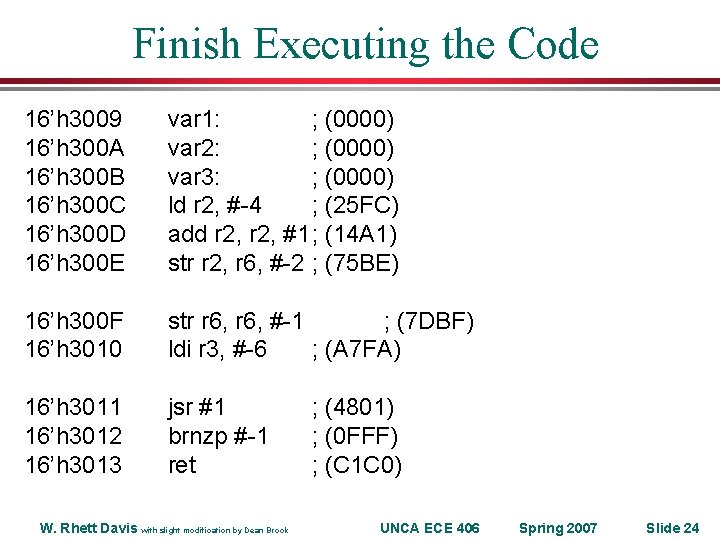

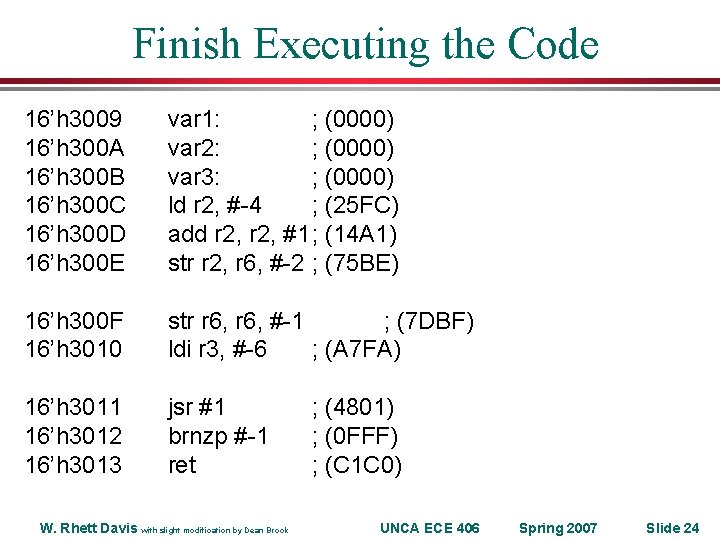

Data Movement Instructions l Load/Store Indirect (indirect addressing mode) » LDI DR, Offset (DR ← MEM[PC+Offset]]) » STI SR, Offset (MEM[PC+Offset]] ← SR) l Load Effective Address » LEA DR, Offset W. Rhett Davis with slight modification by Dean Brock (DR ← PC+Offset) UNCA ECE 406 Spring 2007 Slide 21

Data Movement Instructions 15 12 11 9 8 6 5 4 3 2 l LD: 0 0 1 0 DR l LDR: 0 1 1 0 DR l LDI: 1 0 DR PCoffset 9 l LEA: 1 1 1 0 DR PCoffset 9 l ST: 0 0 1 1 SR PCoffset 9 l STR: 0 1 1 1 SR l STI: 1 0 1 1 SR W. Rhett Davis with slight modification by Dean Brock 0 PCoffset 9 Base. R Offset 6 PCoffset 9 UNCA ECE 406 Spring 2007 Slide 22

Compile & Execute This Code 16’h 3000 16’h 3001 16’h 3002 16’h 3003 16’h 3004 16’h 3005 16’h 3006 16’h 3007 16’h 3008 16’h 3009 16’h 300 A 16’h 300 B 16’h 300 C and r 0, #0; add r 0, #7; and r 1, #0; add r 1, #5; add r 0, #-1; brp #-3 ; st r 1, #2 ; lea r 6, #4 ; jmp r 6 ; var 1: ; (0000) var 2: ; (0000) var 3: ; (0000) … W. Rhett Davis with slight modification by Dean Brock UNCA ECE 406 Spring 2007 Slide 23

Finish Executing the Code 16’h 3009 16’h 300 A 16’h 300 B 16’h 300 C 16’h 300 D 16’h 300 E var 1: ; (0000) var 2: ; (0000) var 3: ; (0000) ld r 2, #-4 ; (25 FC) add r 2, #1; (14 A 1) str r 2, r 6, #-2 ; (75 BE) 16’h 300 F 16’h 3010 str r 6, #-1 ; (7 DBF) ldi r 3, #-6 ; (A 7 FA) 16’h 3011 16’h 3012 16’h 3013 jsr #1 brnzp #-1 ret W. Rhett Davis with slight modification by Dean Brock ; (4801) ; (0 FFF) ; (C 1 C 0) UNCA ECE 406 Spring 2007 Slide 24