DYNAMICALLY RECONFIGURABLE SYSTOLIC ARRAY ACCELERATORS A CASE STUDY

DYNAMICALLY RECONFIGURABLE SYSTOLIC ARRAY ACCELERATORS: A CASE STUDY WITH EKF AND DWT ALGORITHMS Robert Barnes Utah State University Department of Electrical and Computer Engineering Thesis Defense, November 13 th 2008

Outline � Introduction & Background � System Design � Results & Conclusions

Motivation �Increasing Demands for Spacecraft Low Power Fault Tolerant Flexibility High Performance �Solution: FPGA

General Goals �Flexible Extended Kalman Filter (EKF) System on an FPGA Adaptable to changing performance requirements (scalable). System adaptable to other algorithms (DWT). �Outperform �Explore RAD 750 Power. PC applications of dynamic reconfiguration.

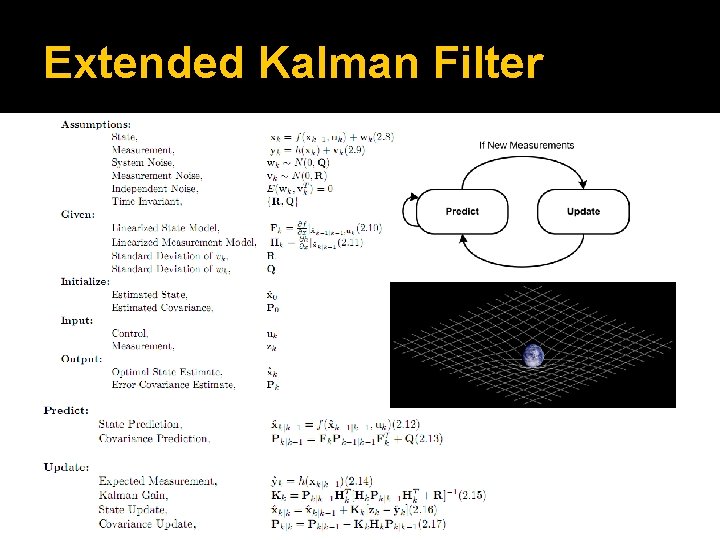

Kalman Filter �To navigate in space an autonomous spacecraft must accurately estimate its state from noisy measurements. �The filter is very flexible Estimate a system’s state from only a single sensor Estimate the bias in sensors Determine an unknown system model Predict a future states

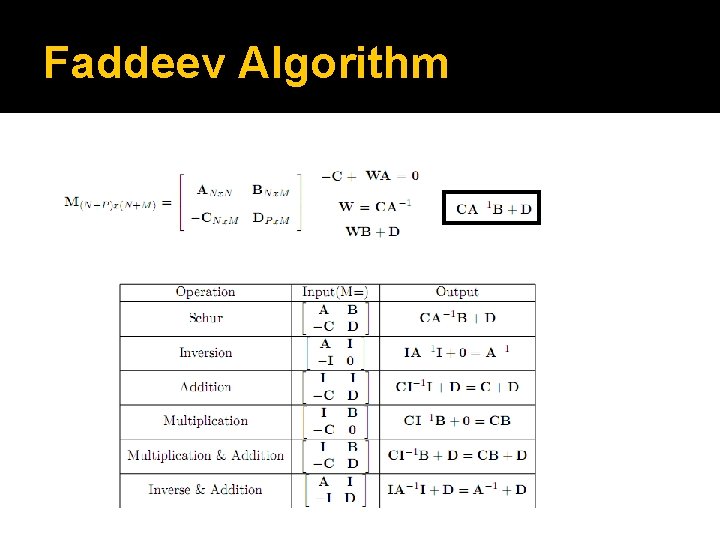

Faddeev Algorithm

Extended Kalman Filter

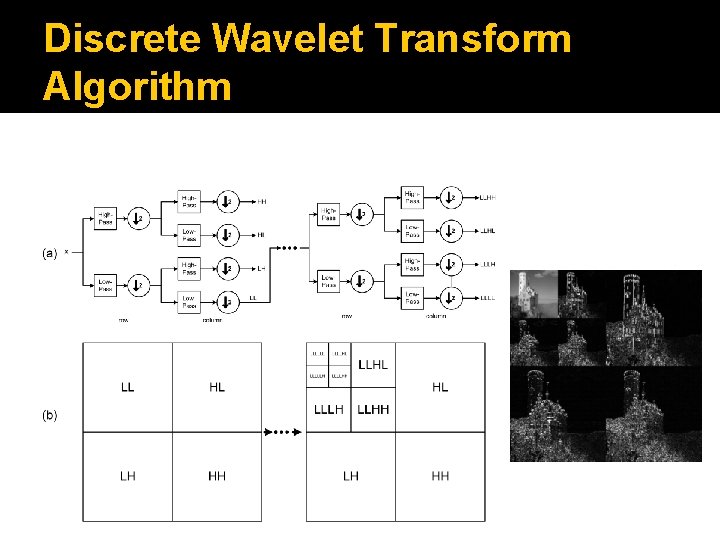

Discrete Wavelet Transform Algorithm

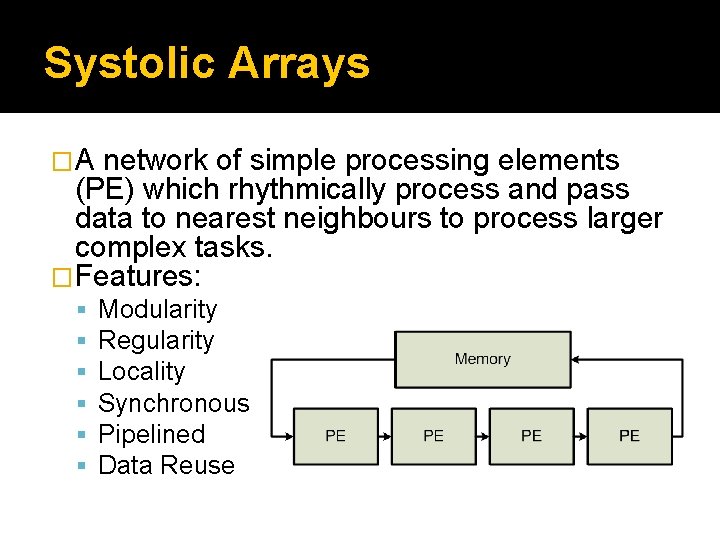

Systolic Arrays �A network of simple processing elements (PE) which rhythmically process and pass data to nearest neighbours to process larger complex tasks. �Features: Modularity Regularity Locality Synchronous Pipelined Data Reuse

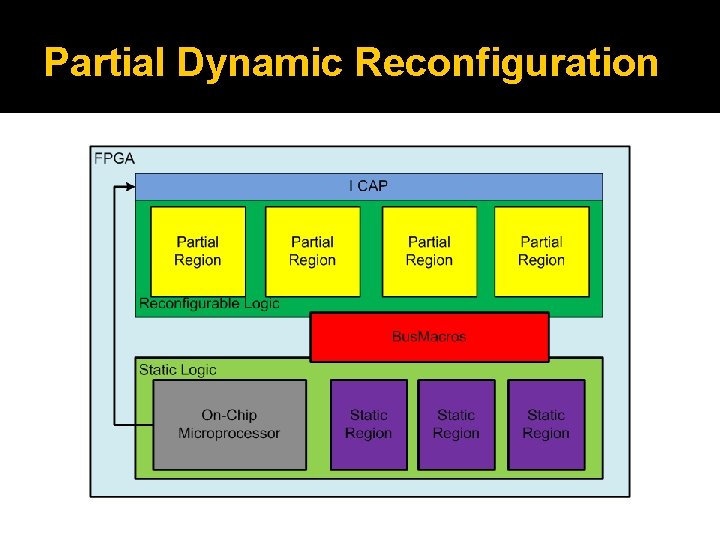

Partial Dynamic Reconfiguration

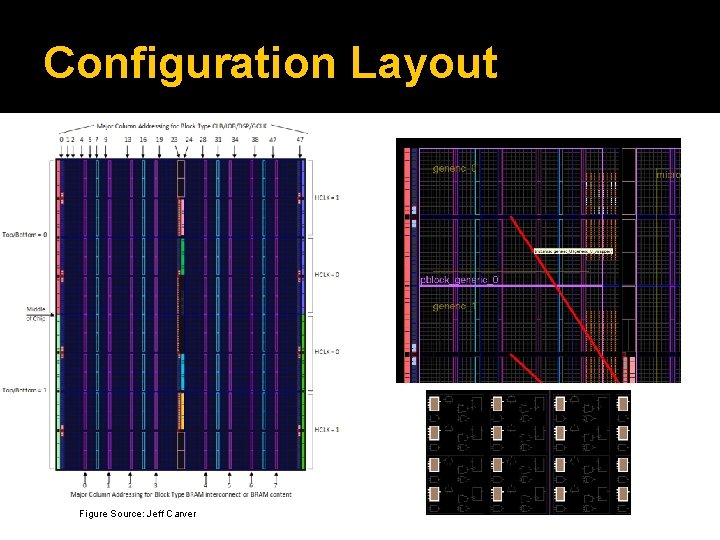

Configuration Layout Figure Source: Jeff Carver

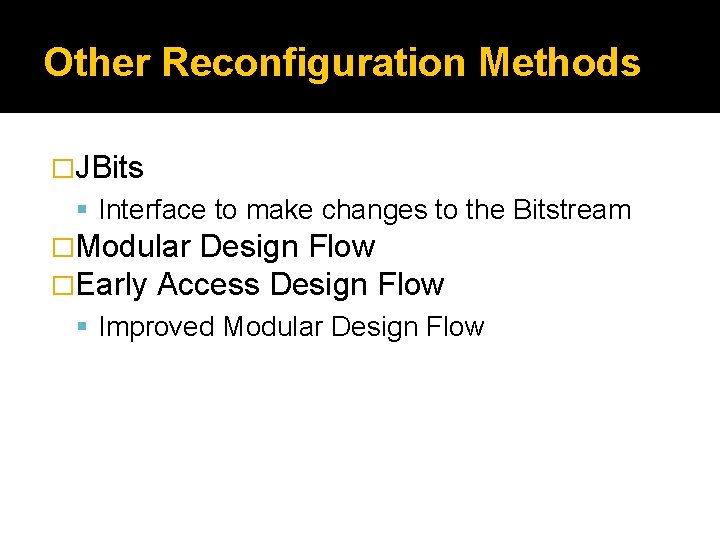

Other Reconfiguration Methods �JBits Interface to make changes to the Bitstream �Modular Design Flow �Early Access Design Flow Improved Modular Design Flow

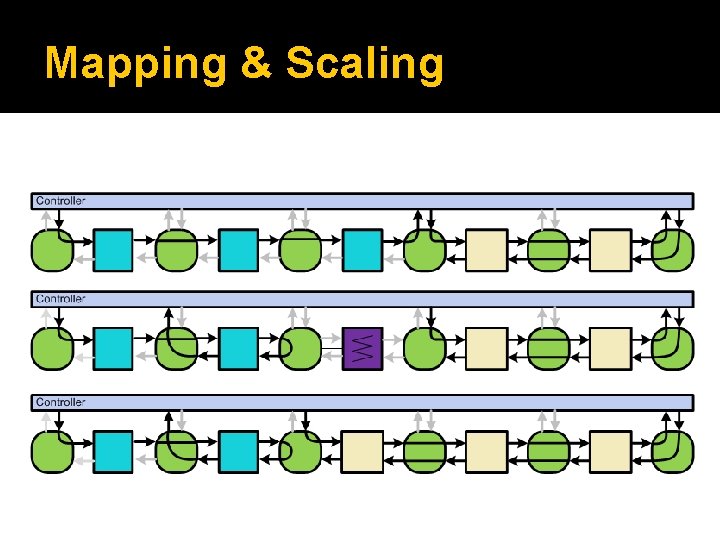

Scaling Methods �Soft scaling Using conditional variable loops and conditional statements, software can easily be made to scale to different parameters. �Static Hardware Scaling Using MUXes a hardware architecture can be designed where data can be re-routed to different hardware cores. �Reconfigurable Hardware Scaling Using partial dynamic reconfiguration the physical size of the systolic array can be scaled.

Outline � Introduction & Background � System Design � Results & Conclusions

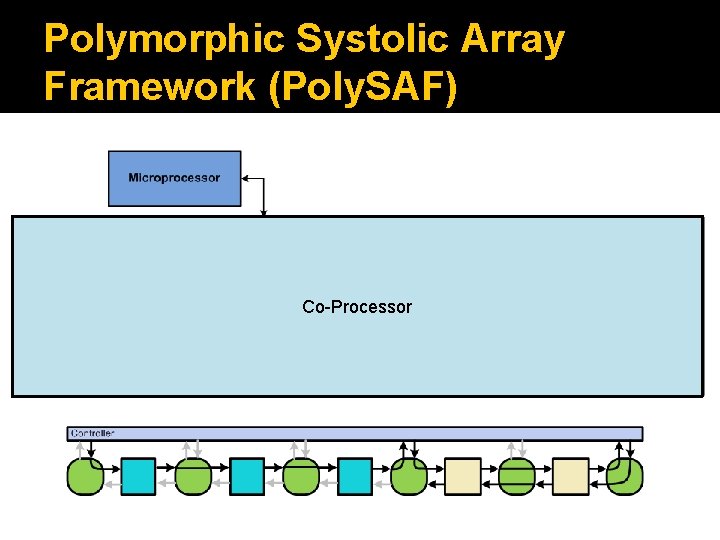

Polymorphic Systolic Array Framework (Poly. SAF) Co-Processor Poly. SAF

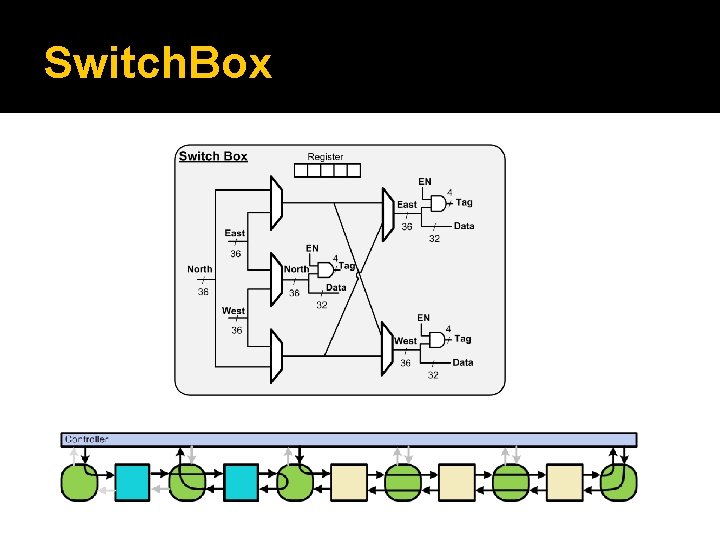

Switch. Box

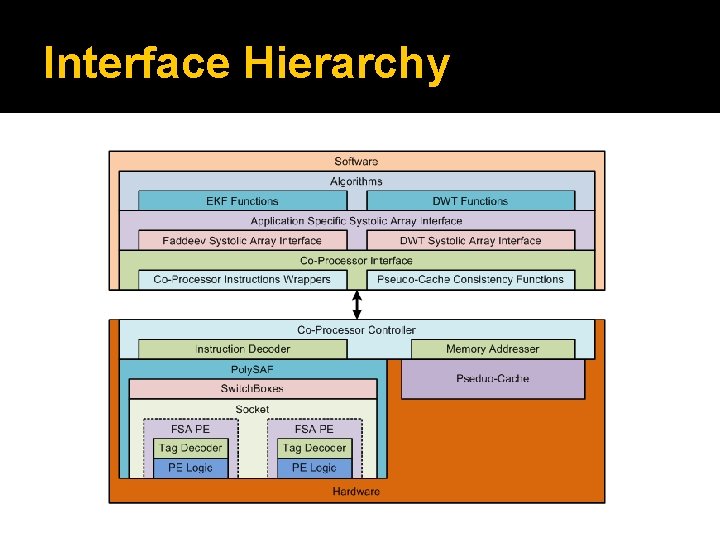

Interface Hierarchy

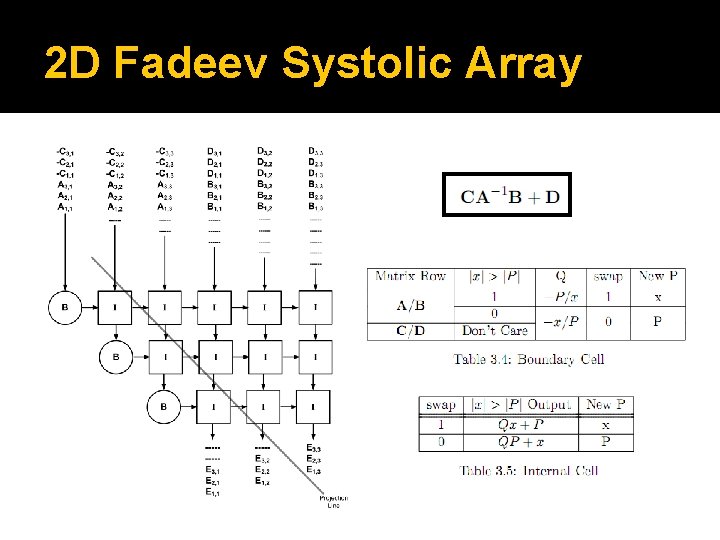

2 D Fadeev Systolic Array

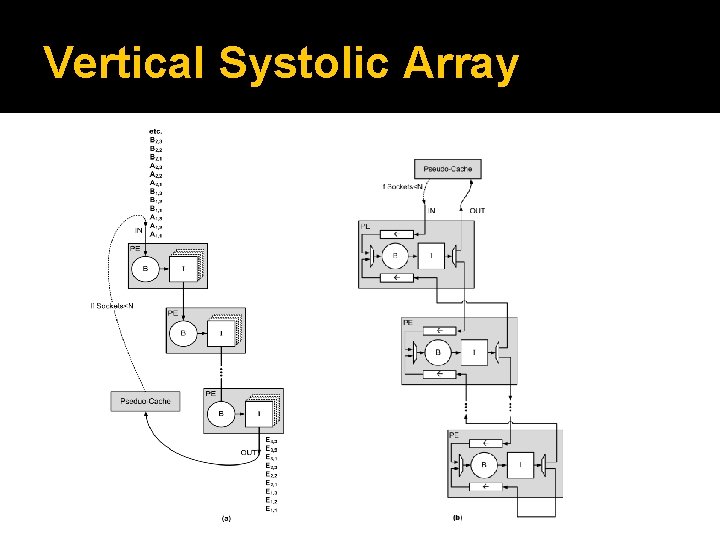

Vertical Systolic Array

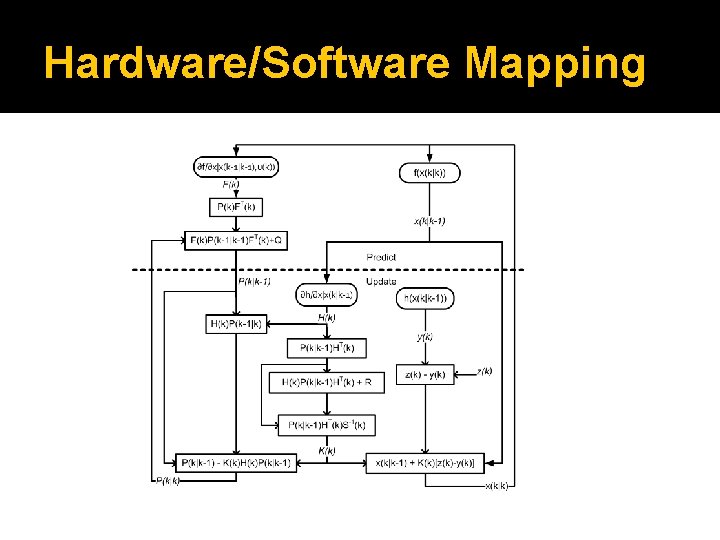

Hardware/Software Mapping

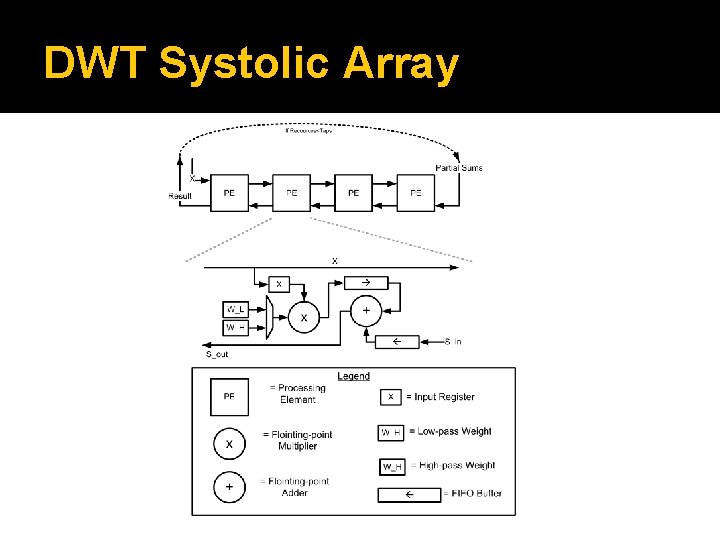

DWT Systolic Array

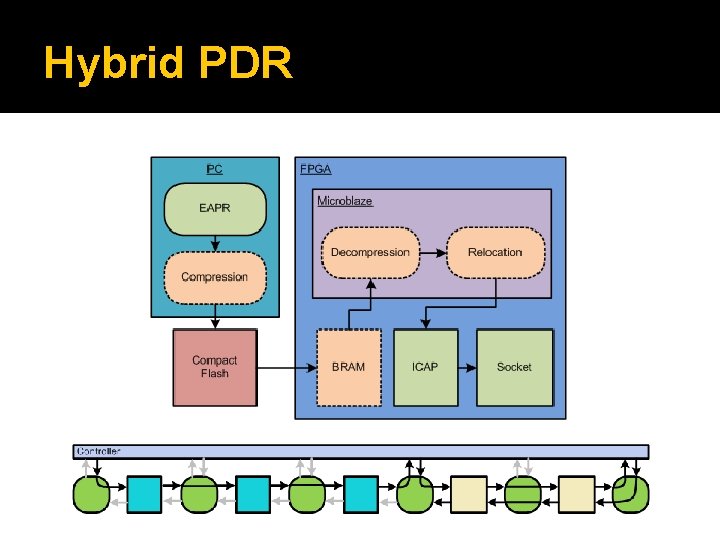

Hybrid PDR

Mapping & Scaling

Outline � Introduction & Background � System Design � Results & Conclusions

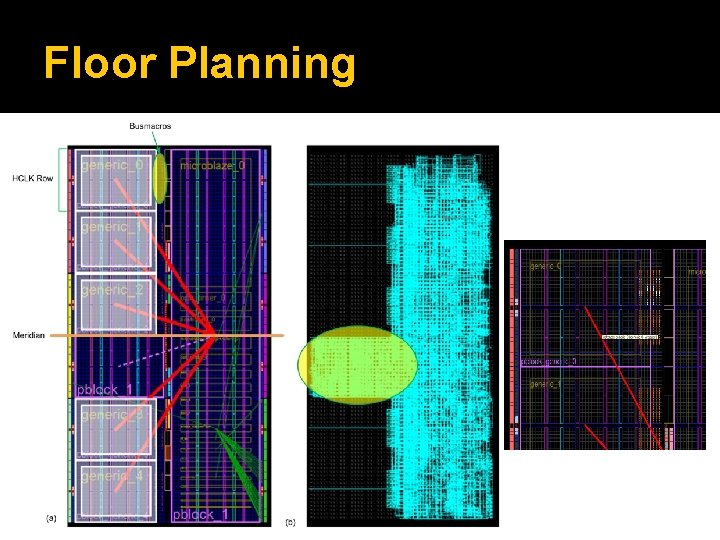

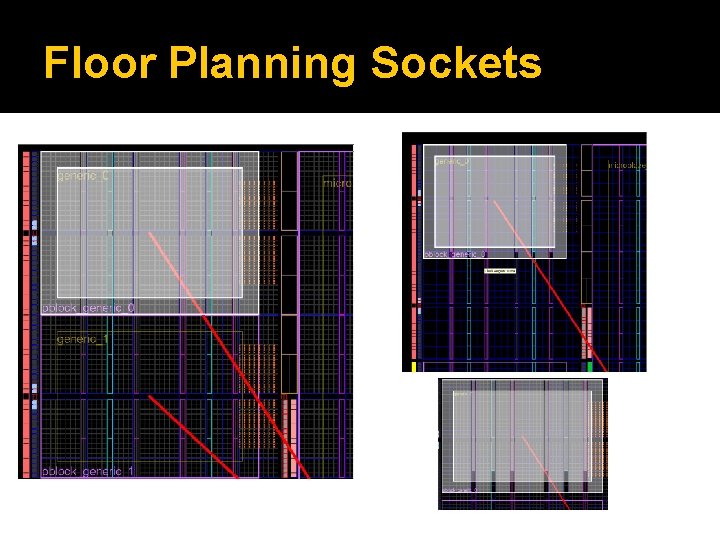

Floor Planning

Floor Planning Sockets

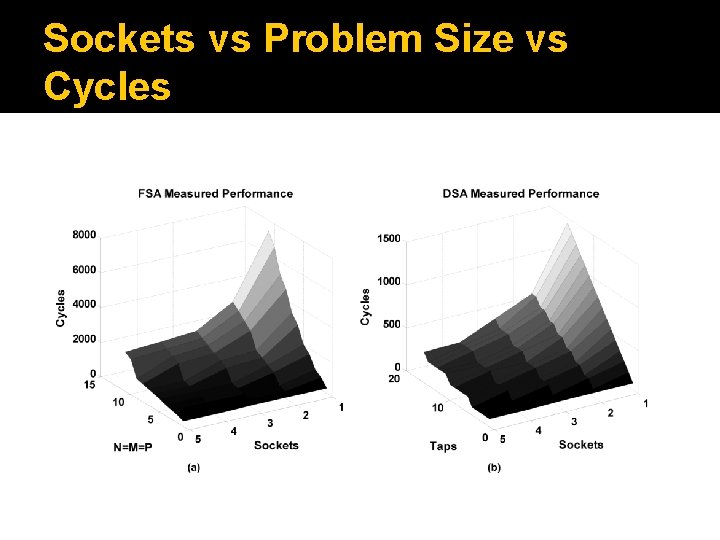

Sockets vs Problem Size vs Cycles

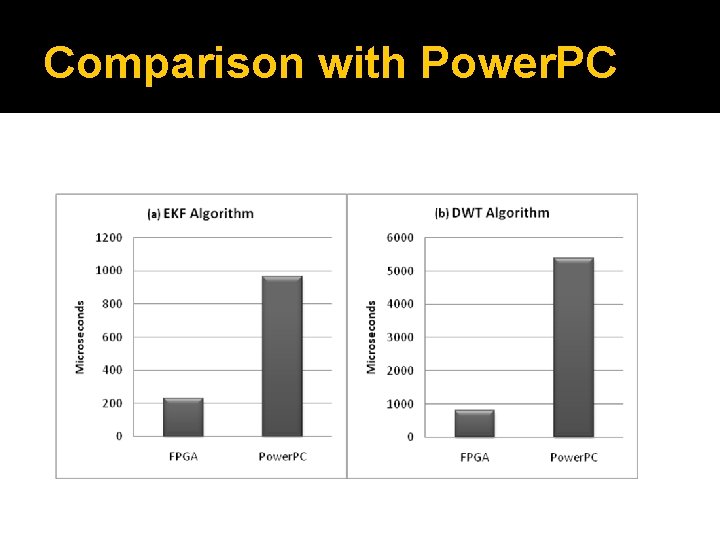

Comparison with Power. PC

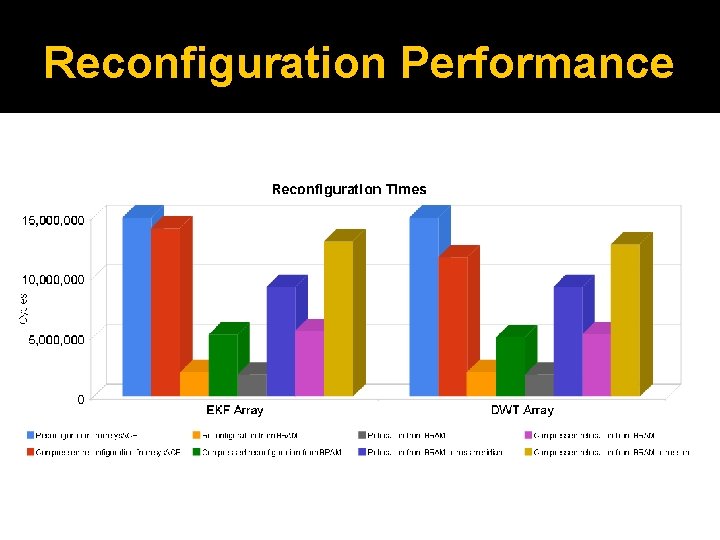

Reconfiguration Performance

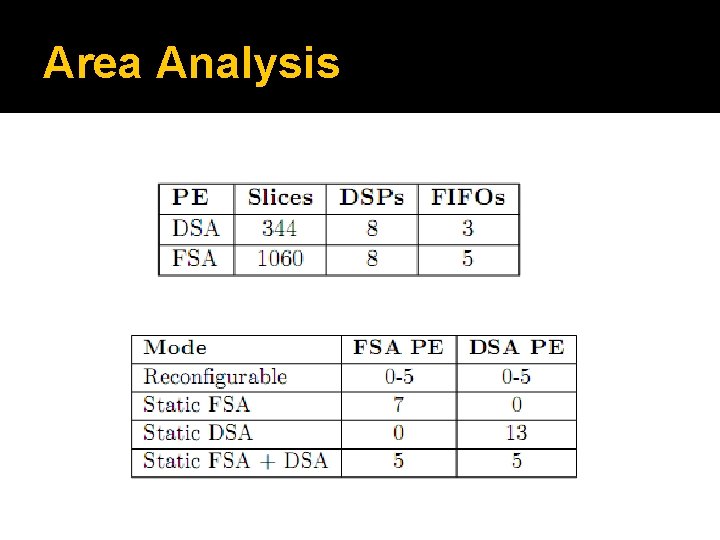

Area Analysis

Conclusions & Limitations A polymorphic systolic array framework (Poly. SAF). Programmable switchboxes and protocol to allow dynamic scaling in the array. � Efficient EKF and DWT accelerators � � Speedup of at least 4. 18 x and 6. 61 x over Power. PC for EKF and DWT. � Integration of bitstream relocation and bitstream compression into a practical system. 2. 7 x improvement in reconfiguration time. A 44% improvement in BRAM usage. � The flexible and simple framework allows this design to host a broad range of algorithms. � Dynamic reconfiguration is powerful, but it is not useful in every application. The trade-offs must be weighed carefully.

Questions?

Publications � R. Barnes and A. Dasu, “Hardware/software Codesigned Extended Kalman Flter on an FPGA, ” in The International Conference on Engineering of Reconfigurable Systems and Algorithms (ERSA), 2008. � R. Barnes, A. Dasu, J. Carver, and R. Kallam, “Dynamically Reconfigurable Systolic Array Accelerators: A case study with EKF and DWT Algorithms, ” Institution of Engineering and Technology (IET) Computers & Digital Techniques. In Review.

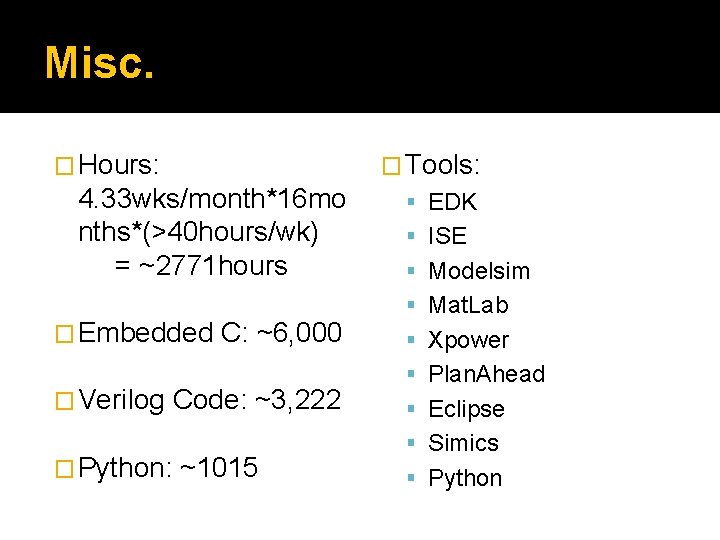

Misc. � Hours: � Tools: 4. 33 wks/month*16 mo nths*(>40 hours/wk) = ~2771 hours � Embedded � Verilog C: ~6, 000 � Python: Code: ~3, 222 ~1015 EDK ISE Modelsim Mat. Lab Xpower Plan. Ahead Eclipse Simics Python

- Slides: 34