A dynamically Reconfigurable System for Space Efficient Computation

A dynamically Reconfigurable System for Space Efficient Computation of the FFT C. H. Llanos, R. P. Jacobi, M. Ayala-Rincón, R. W. Hartenstein A Paper Review by Michael Chapman 1

Outline Introduction Butterfly Circuit Reconfigurable Architecture Results Contributions Conclusions 2

Introduction The FFT (Fast Fourier Transform) Takes a time domain signal and transforms it to the frequency domain Uses Can be used to find the unfilled parts of the spectrum in cognitive radio Can be used in filter design 3

Discrete FFT Given an n-array of complex numbers from a 0, …, an-1 4

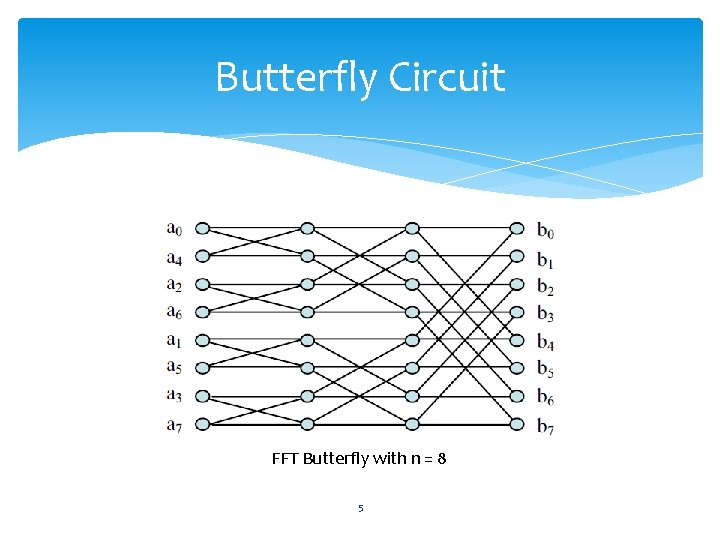

Butterfly Circuit FFT Butterfly with n = 8 5

Node Architecture 6

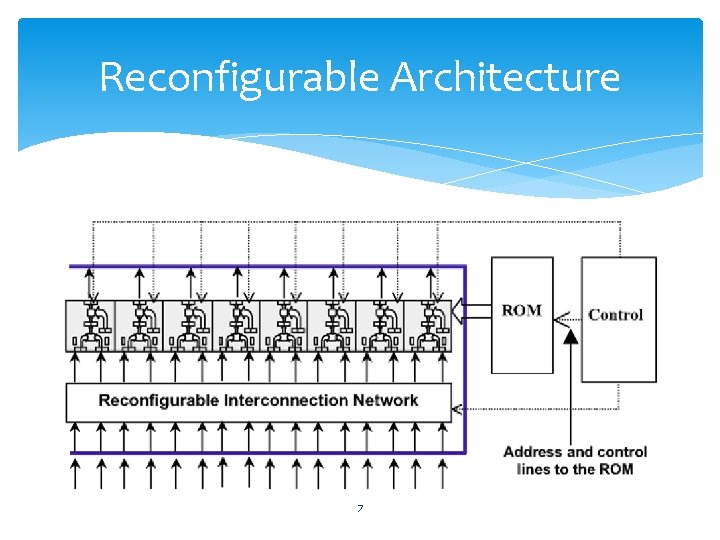

Reconfigurable Architecture 7

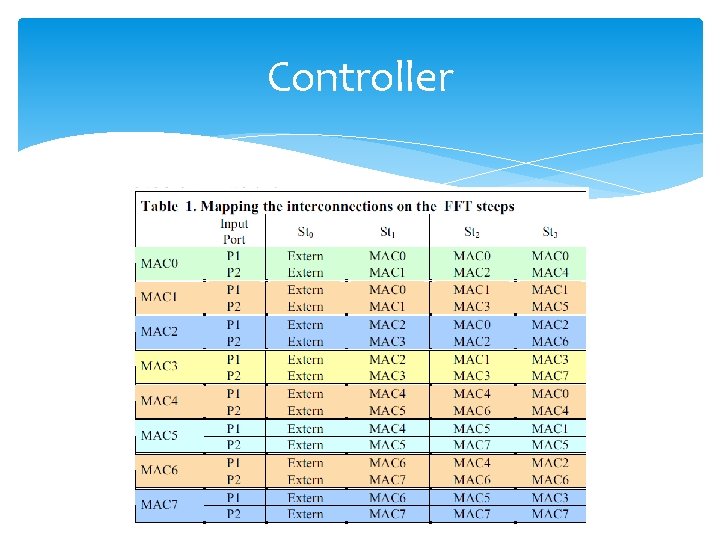

Controller 8

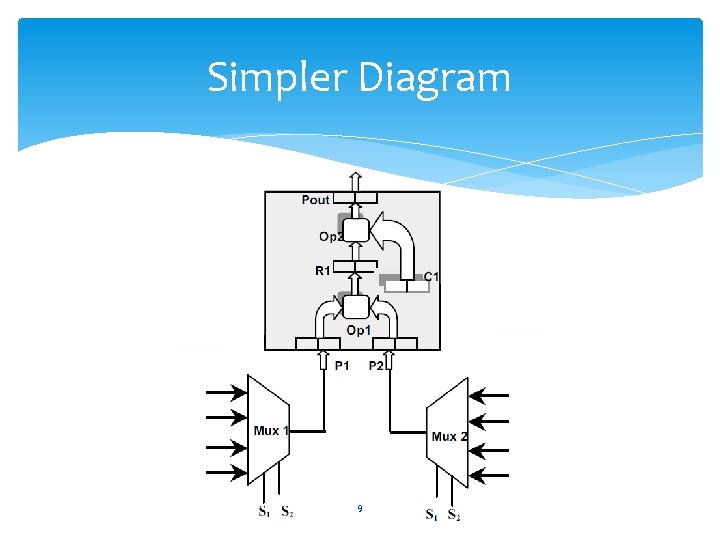

Simpler Diagram 9

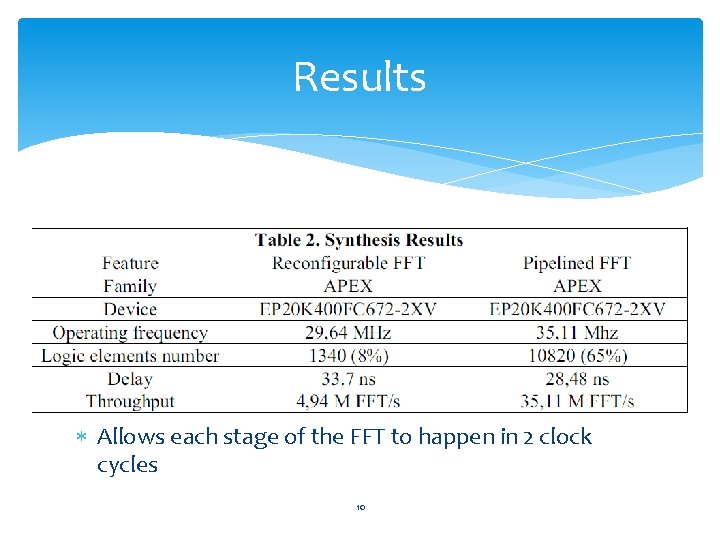

Results Allows each stage of the FFT to happen in 2 clock cycles 10

Contributions A way to effectively implement the FFT in Hardware using a form of optimization Able to fit this module easily into other applications as an IP Core Blocks have multipurpose use for matrix multiplication or convolution coding 11

Critique Relatively uncreative solution to optimize the system by looping over the first step Dynamically reconfigurable As a complete FFT unit Configuring the FFT registers to be a matrix multiplier etc. No mention to testing the system on bigger FFT sample sizes 12

Questions? 13

References A dynamically Reconfigurable System for Space Efficient Computation of the FFT - C. H. Llanos, R. P. Jacobi, M. Ayala-Rincón, R. W. Hartenstein 14

- Slides: 14