DESIGN OF A DYNAMICALLY RECONFIGURABLE PIPELINED RISC PROCESSOR

DESIGN OF A DYNAMICALLY RECONFIGURABLE PIPELINED RISC PROCESSOR Under the guidance of Azmath Moosa Md. Aneesh Dept. of Electronics Engg. School of Engg. & Tech, Pondicherry University 1 st Review 19 th March 2015

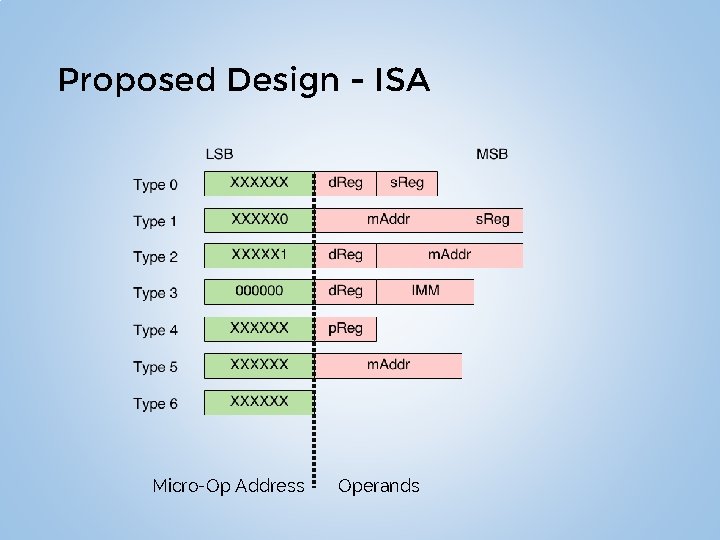

Proposed Design - ISA Micro-Op Address Operands

Fluid Core ISA v 2. 0 RRR 0 1 3 2 1 0 2 3 5 4 4 5 3 4 2 Address 1 0 Micro-Op RRI 0 1 2 3 4 5 5 6 7 8 9 10 Branch Condition or 10 9 8 7 6 Destination Register 6 7 8 9 11 10 12 13 15 12 11 12 A 13 11 Reg 10 14 13 14 15 15 Reg B 12 11 14 Reg A RI Immediate 13 14 15 Immediate

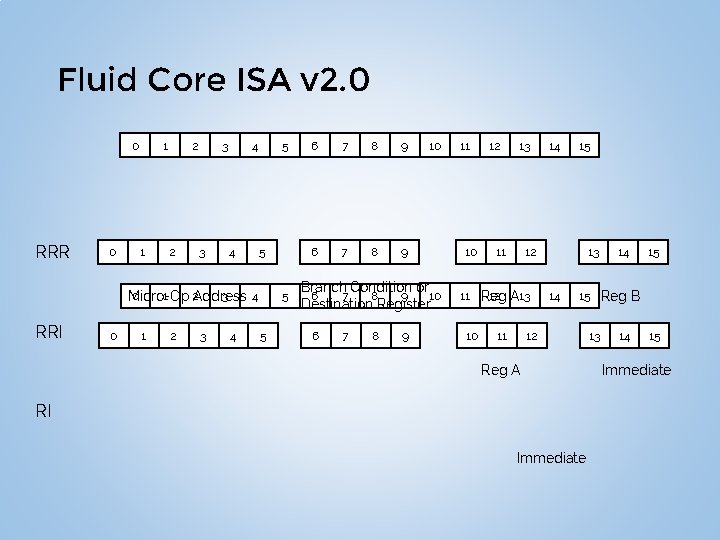

The Pipeline Fetch 0 1 2 5 3 4 Decode 6 9 8 7 Execute Memory 12 11 13 Access 10 Micro. Store Type Mod. Sel 14 Write 15 Back Register File Operation Dest. Reg/BC Operand A Operand B

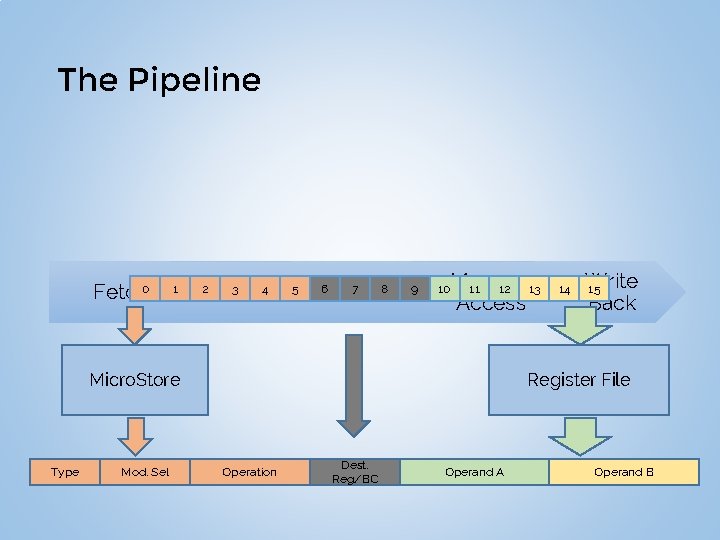

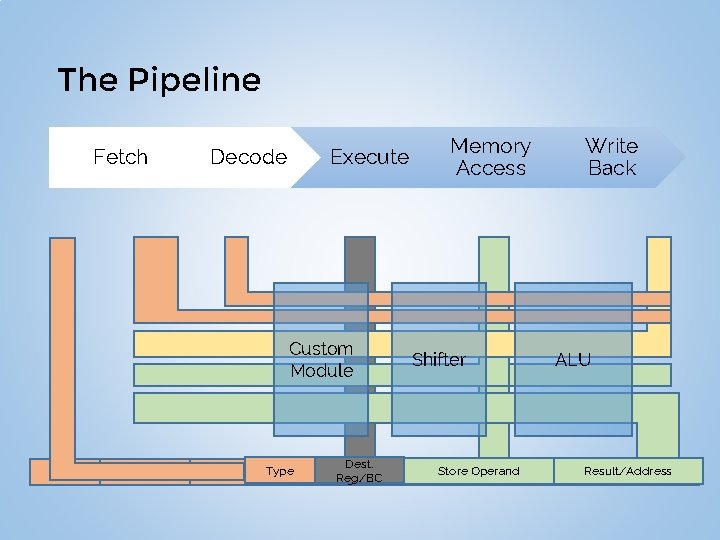

The Pipeline Fetch Decode Execute Custom Module Type Mod. Sel Type Operation Dest. Reg/BC Memory Access Shifter Store Operand A Write Back ALU Result/Address Operand B

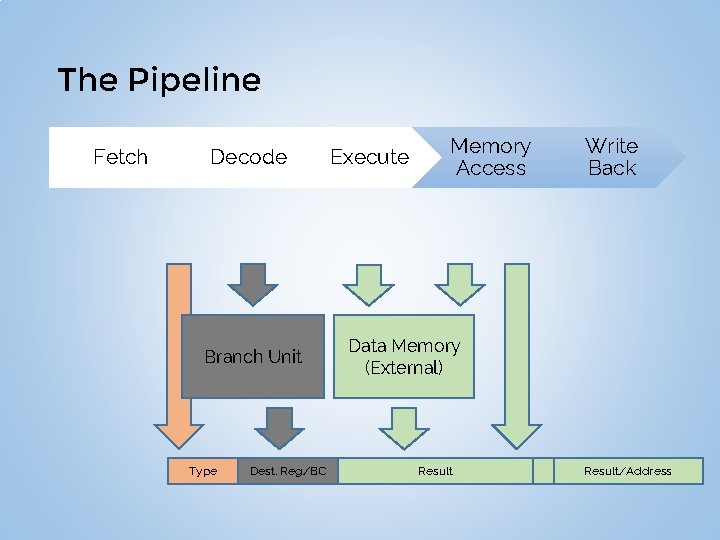

The Pipeline Fetch Decode Branch Unit Type Dest. Reg/BC Type Execute Memory Access Write Back Data Memory (External) Dest. Reg/BC Result Store Operand Result/Address

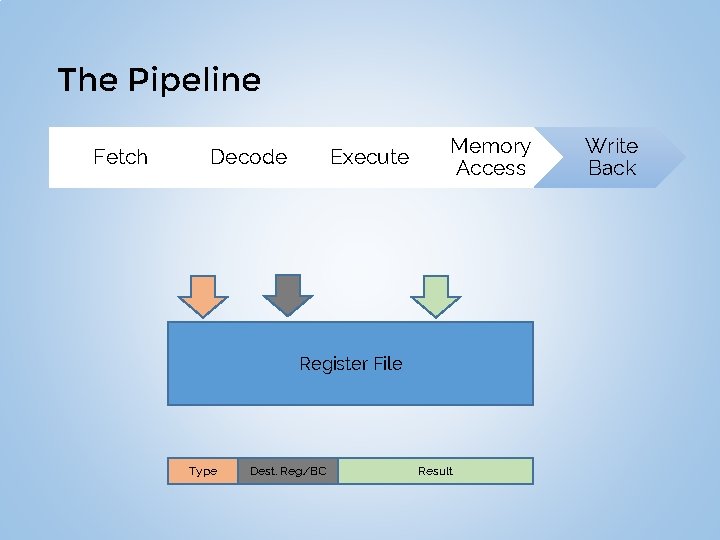

The Pipeline Fetch Decode Execute Memory Access Register File Type Dest. Reg/BC Result Write Back

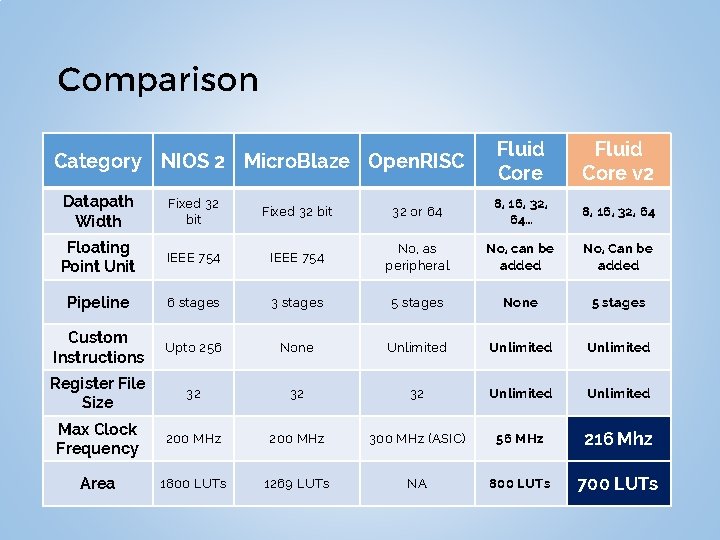

Comparison Category NIOS 2 Micro. Blaze Open. RISC Fluid Core v 2 Datapath Width Fixed 32 bit 32 or 64 8, 16, 32, 64… 8, 16, 32, 64 Floating Point Unit IEEE 754 No, as peripheral No, can be added No, Can be added Pipeline 6 stages 3 stages 5 stages None 5 stages Custom Instructions Upto 256 None Unlimited Register File Size 32 32 32 Unlimited Max Clock Frequency 200 MHz 300 MHz (ASIC) 56 MHz 216 Mhz Area 1800 LUTs 1269 LUTs NA 800 LUTs 700 LUTs

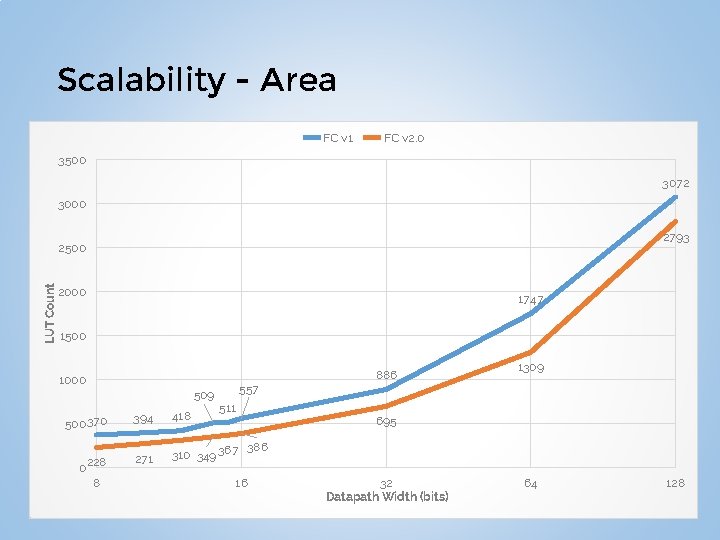

Scalability - Area FC v 1 FC v 2. 0 3500 3072 3000 2793 LUT Count 2500 2000 1747 1500 1000 509 557 511 500 370 394 418 0 228 8 271 310 349 367 886 1309 695 386 16 32 Datapath Width (bits) 64 128

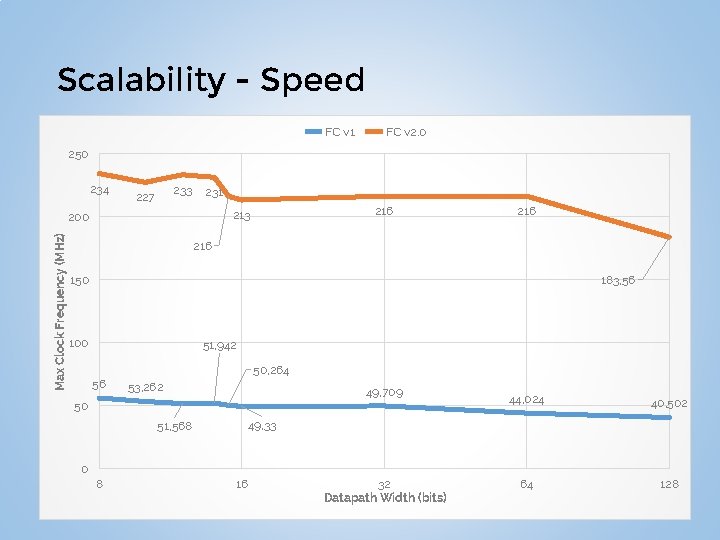

Scalability - Speed FC v 1 FC v 2. 0 250 234 233 227 231 Max Clock Frequency (MHz) 216 213 200 216 150 183, 56 100 51, 942 56 50, 264 53, 262 49, 709 50 51, 568 44, 024 40, 502 64 128 49, 33 0 8 16 32 Datapath Width (bits)

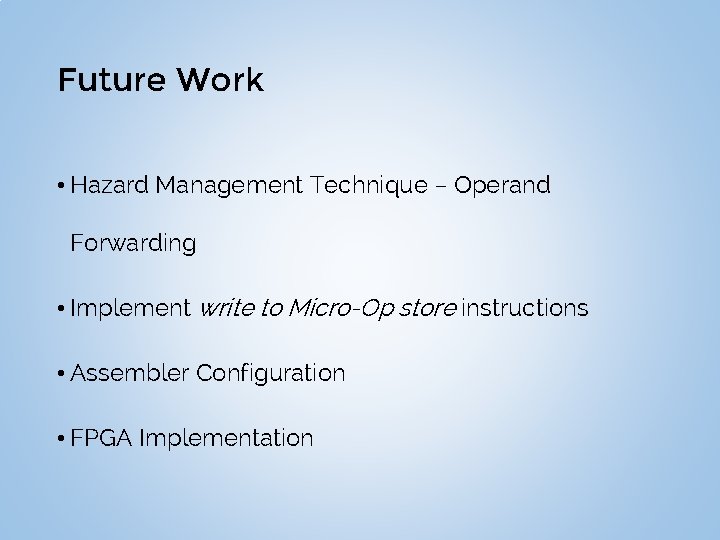

Future Work • Hazard Management Technique – Operand Forwarding • Implement write to Micro-Op store instructions • Assembler Configuration • FPGA Implementation

References • Pocek, Kenneth, Russell Tessier, and André De. Hon. "Birth and adolescence of reconfigurable computing: A survey of the first 20 years of field-programmable custom computing machines. " Highlights of the First Twenty Years of the IEEE International Symposium on Field-Programmable Custom Computing Machines. 2013. • J. Tong, , "Soft-Core Processors for Embedded Systems, " IEEE Conferences on Reconfigurable Computing, Vol. , no. , pp. 170 -173. 2006. • Chapman, Ken , Pico. Blaze 8 -Bit Microcontroller for Virtex-E and Spartan-II/IIE Devices , Xilinx , version 2. 1 • Michael Gschwind, Valentina Salapura, , FPGA Prototyping of a RISC Processor Core for Embedded Applications , IEEE Transactions on VLSI , vol 9 , no 2, p. 241 - 250 • J. Gray, “Designing a Simple FPGA-Optimized RISC CPU and System-on-a-Chip”, Design. Con’ 2001, online at http: //www. fpgacpu. org/gr/index. html, 2001.

Thank You Queries may be put forth

- Slides: 13