Design Codesign of Embedded Systems Distributed System Cosynthesis

Design & Co-design of Embedded Systems Distributed System Co-synthesis (1) Maziar Goudarzi Fall 2005 Design & Co-design of Embedded Systems

Today Program z. Introduction z. Preliminaries z. Hardware/Software Partitioning z. Distributed System Co-Synthesis (part 1) References: Wayne Wolf, “Hardware/Software Co-Synthesis Algorithms, ” Chapter 2, Hardware/Software Co-Design: Principles and Practice, Eds: J. Staunstrup, W. Wolf, Kluwer Academic Publishers, 1997. S. Prakash, A. Parker, “Synthesis of Application-Specific Multiprocessor Architectures, ” ACM/IEEE Design Automation Conference, 1991. Fall 2005 Design & Co-design of Embedded Systems 2

Topics z. Introduction z. A Integer Linear Programming Model z. A Heuristic Algorithm (next session) y. On ordinary task graphs y. On an Object-Oriented model Fall 2005 Design & Co-design of Embedded Systems 3

Introduction to Distributed System Co-Syn. z. Does not use an architectural template z. Instead, creates a multiprocessor architecture during co-synthesis y. Usually heterogeneous multiprocessor in x. Processing Elements x. Communication Channels x. Topologies z. Less emphasis on the design of ASICs z. More emphasis on the design of multiprocessor topology Design & Co-design of Fall 2005 Embedded Systems 4

Introduction to Distrib. Sys. Co. Syn. (cont’d) z. Very common in practice y. A decade ago: x. Specially large CPU + small microcontrollers + small ASICs y. Specifically today: x. MPSo. C: Multiprocessor System-on-Chip Fall 2005 Design & Co-design of Embedded Systems 5

Co-Synthesis Algorithms: Distributed System Co-Synthesis Integer Linear Programming Model Fall 2005 Design & Co-design of Embedded Systems

ILP Model z. Introduction y. Linear Programming (LP): x. Minimizing/maximizing a Linear target function • Subject to a set of Linear constraints x. Current algorithms: Do find the optimal solution, or else the problem is not feasible at all. x. Example: Knapsack problem y. Integer Linear Programming (ILP) x. Integer-solution counterpart of LP x. Example: Knapsack problem with integer-solution constraint Fall 2005 Design & Co-design of Embedded Systems 7

ILP Model (cont’d) z. Introduction (cont’d) y. Mixed Integer Linear Programming (MILP) x. One (or more) non-integer variables included y 0 -1 Integer Linear Programming (0 -1 ILP) x. Only binary variables (can only be 0 or 1) y. Current algorithms: x. Absolute optimal solution is found • Takes much CPU time • Only feasible for fairly small problems Fall 2005 Design & Co-design of Embedded Systems 8

Prakash-Parker ILP Model z. By Prakash and Parker, 1991 y. Developed an ILP formulation x. Used general ILP solvers to solve it y. Inputs to the algorithm x. Single-rate task graph x. Technology model for the PEs, communication channels, and processes’ execution characteristics on them y. Target function x. Minimize system implementation cost y. Constraints x. Describe the requirements of the system Fall 2005 Design & Co-design of Embedded Systems 9

Prakash-Parker ILP Model (cont’d) z. Algorithm classification criteria y. Input Model x. Single-rate task graph y. Target Architecture x. Distributed multiprocessor y. Quantum x. Processes of the task graph y. Cost Estimation x. Based on technology models provided to the algorithm x. Represented as target function of the ILP Fall 2005 Design & Co-design of Embedded Systems 10

Prakash-Parker ILP Model (cont’d) z. Algorithm classification criteria (cont’d) y. Performance Estimation x. Based on technology models provided to the algorithm y. Scheduling, Allocation x. Embedded in the ILP formulation constraints y. Algorithm details x. Target Function • Minimize cost (or maximize performance) x. Sets of Constraints • Allocation (PE and communication links) • Scheduling (Processes on PEs, and communications on links) Fall 2005 Design & Co-design of Embedded Systems 11

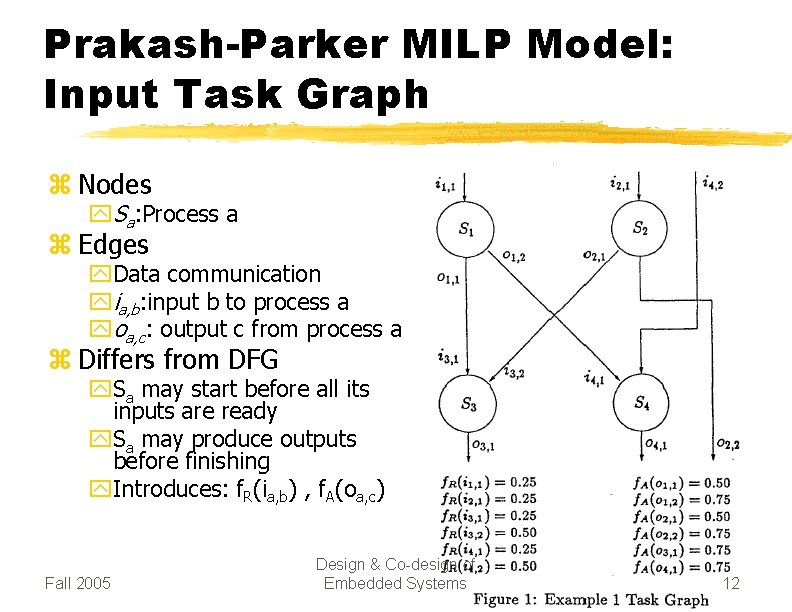

Prakash-Parker MILP Model: Input Task Graph z Nodes y. Sa: Process a z Edges y. Data communication yia, b: input b to process a yoa, c: output c from process a z Differs from DFG y. Sa may start before all its inputs are ready y. Sa may produce outputs before finishing y. Introduces: f. R(ia, b) , f. A(oa, c) Fall 2005 Design & Co-design of Embedded Systems 12

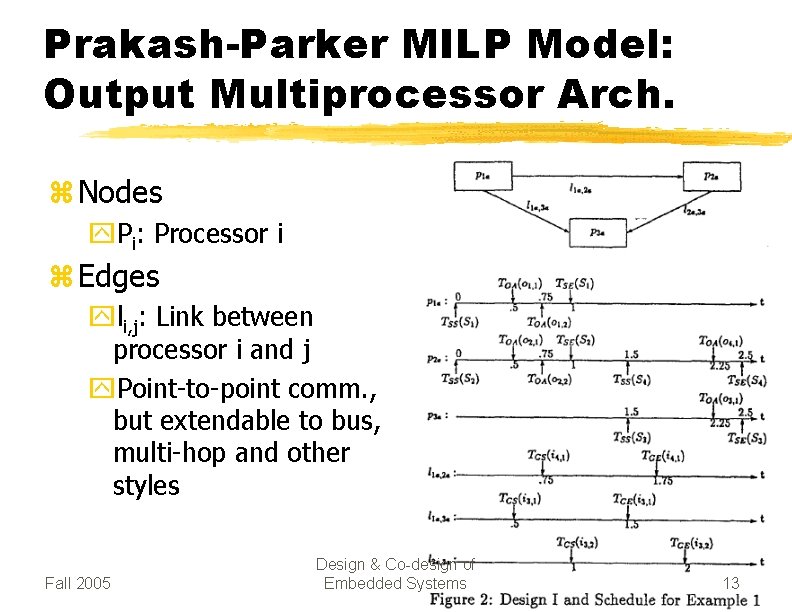

Prakash-Parker MILP Model: Output Multiprocessor Arch. z Nodes y. Pi: Processor i z Edges yli, j: Link between processor i and j y. Point-to-point comm. , but extendable to bus, multi-hop and other styles Fall 2005 Design & Co-design of Embedded Systems 13

Prakash-Parker MILP Model: Given Inputs z Pa: set of all processors capable of running Sa z Dps(Pt, Sa): Exec. time of Sa if run on a processor of type Pt z Va 1, a 2: volume of data transferred from Sa 1 to Sa 2 y. Remote transfer: if Sa 1 and Sa 2 are mapped to different processors y. Local transfer: if both mapped to the same processor z Comm. cost depends on the transfer being local/remote y. DCL: cost of local transfer of unit volume of data y. DCR: cost of remote transfer Design & Co-designof of unit volume of data Fall 2005 Embedded Systems x. Waiting time for the channel is not included in DCR 14

Prakash-Parker MILP Model: Given Inputs (cont’d) z. Set P: set of all available processors y. P= a Pa z. Cd: Cost of processor pd P z. CL: Cost of a comm. link between two processors Fall 2005 Design & Co-design of Embedded Systems 15

Prakash-Parker MILP Model: Variables z. Timing variables + binary variables z. Timing variables yreal-valued y. Data availability timing variables x. TIA(ia, b): input availability time x. TOA(oa, c): output availability time y. Subtask execution timing variables x. TSS(Sa): start-time of sub-task Sa x. TSE(Sa): end-time of sub-task Sa Fall 2005 Design & Co-design of Embedded Systems 16

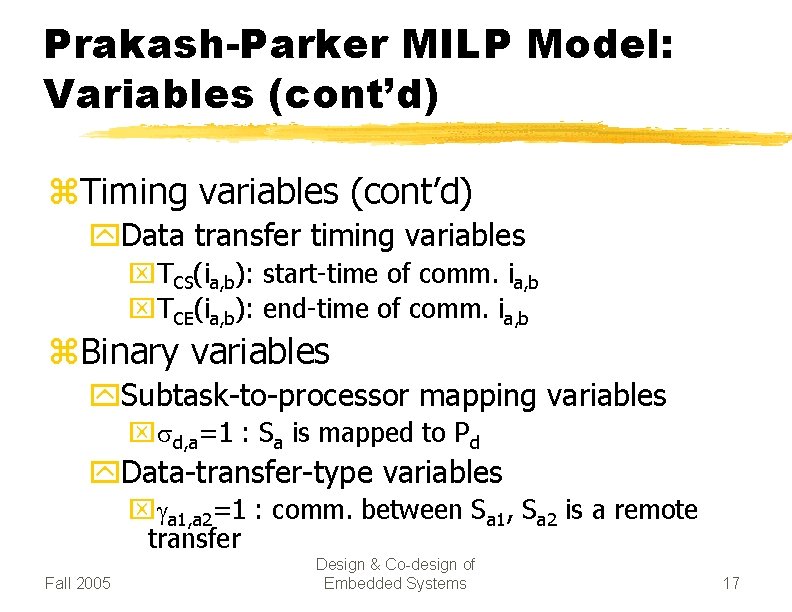

Prakash-Parker MILP Model: Variables (cont’d) z. Timing variables (cont’d) y. Data transfer timing variables x. TCS(ia, b): start-time of comm. ia, b x. TCE(ia, b): end-time of comm. ia, b z. Binary variables y. Subtask-to-processor mapping variables x d, a=1 : Sa is mapped to Pd y. Data-transfer-type variables x a 1, a 2=1 : comm. between Sa 1, Sa 2 is a remote transfer Fall 2005 Design & Co-design of Embedded Systems 17

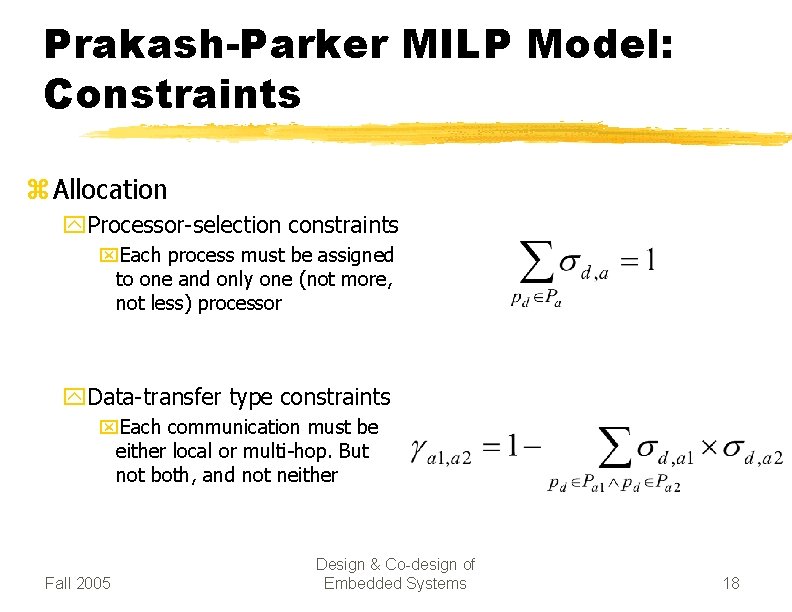

Prakash-Parker MILP Model: Constraints z Allocation y. Processor-selection constraints x. Each process must be assigned to one and only one (not more, not less) processor y. Data-transfer type constraints x. Each communication must be either local or multi-hop. But not both, and not neither Fall 2005 Design & Co-design of Embedded Systems 18

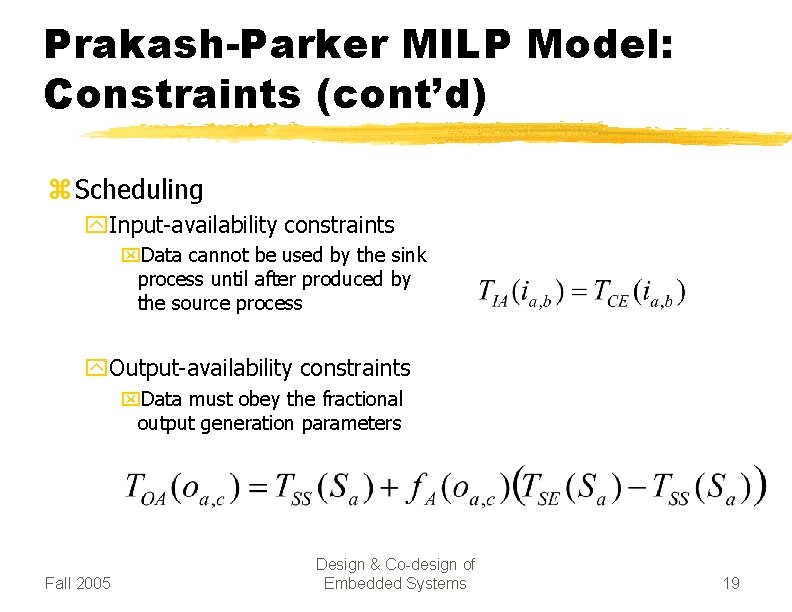

Prakash-Parker MILP Model: Constraints (cont’d) z Scheduling y. Input-availability constraints x. Data cannot be used by the sink process until after produced by the source process y. Output-availability constraints x. Data must obey the fractional output generation parameters Fall 2005 Design & Co-design of Embedded Systems 19

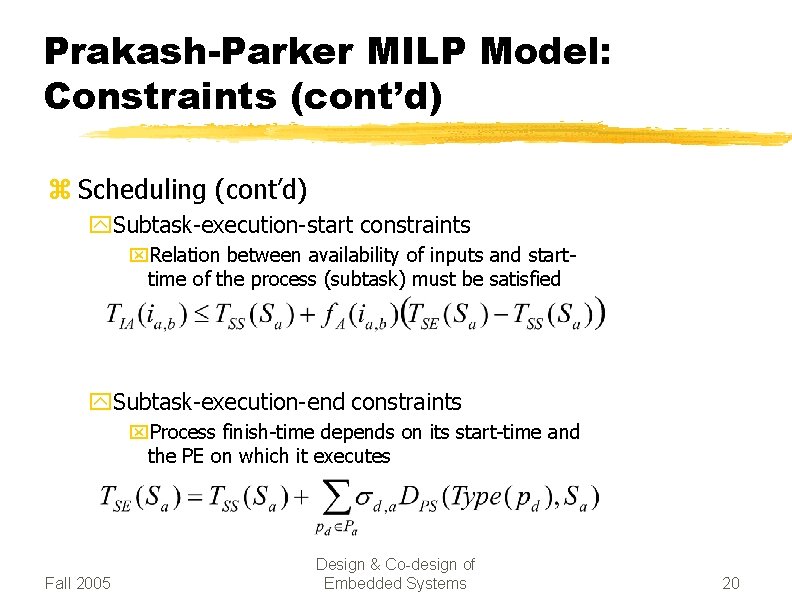

Prakash-Parker MILP Model: Constraints (cont’d) z Scheduling (cont’d) y. Subtask-execution-start constraints x. Relation between availability of inputs and starttime of the process (subtask) must be satisfied y. Subtask-execution-end constraints x. Process finish-time depends on its start-time and the PE on which it executes Fall 2005 Design & Co-design of Embedded Systems 20

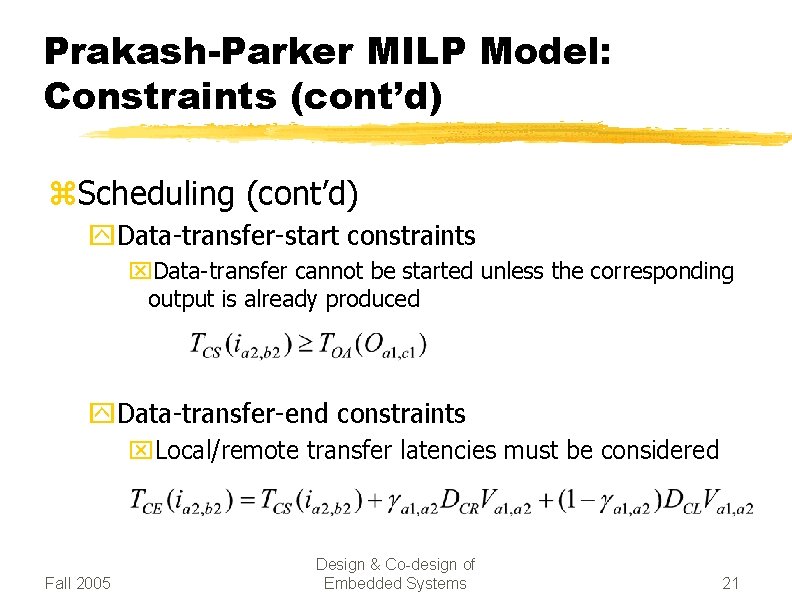

Prakash-Parker MILP Model: Constraints (cont’d) z. Scheduling (cont’d) y. Data-transfer-start constraints x. Data-transfer cannot be started unless the corresponding output is already produced y. Data-transfer-end constraints x. Local/remote transfer latencies must be considered Fall 2005 Design & Co-design of Embedded Systems 21

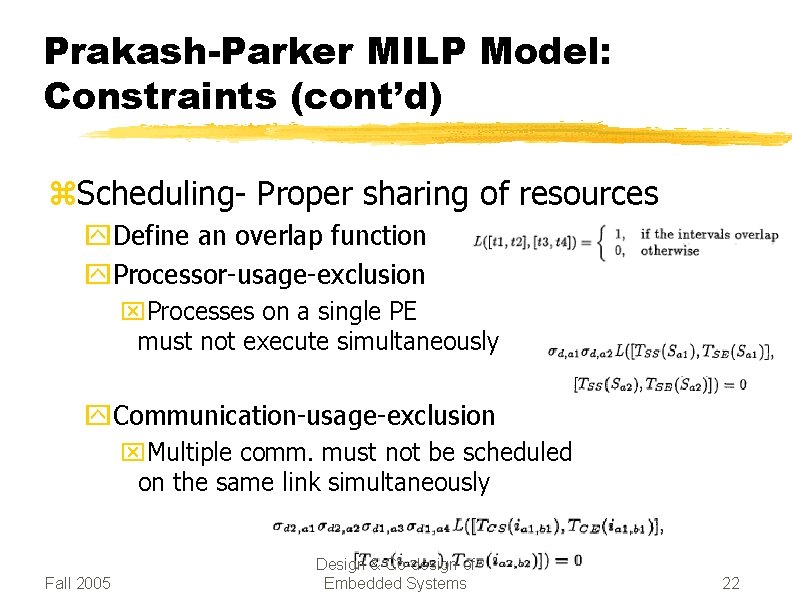

Prakash-Parker MILP Model: Constraints (cont’d) z. Scheduling- Proper sharing of resources y. Define an overlap function y. Processor-usage-exclusion x. Processes on a single PE must not execute simultaneously y. Communication-usage-exclusion x. Multiple comm. must not be scheduled on the same link simultaneously Fall 2005 Design & Co-design of Embedded Systems 22

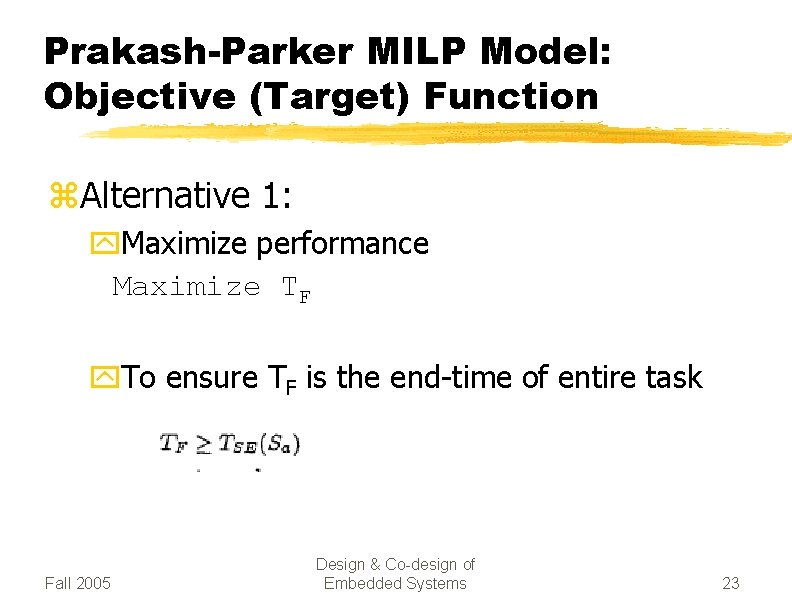

Prakash-Parker MILP Model: Objective (Target) Function z. Alternative 1: y. Maximize performance Maximize TF y. To ensure TF is the end-time of entire task Fall 2005 Design & Co-design of Embedded Systems 23

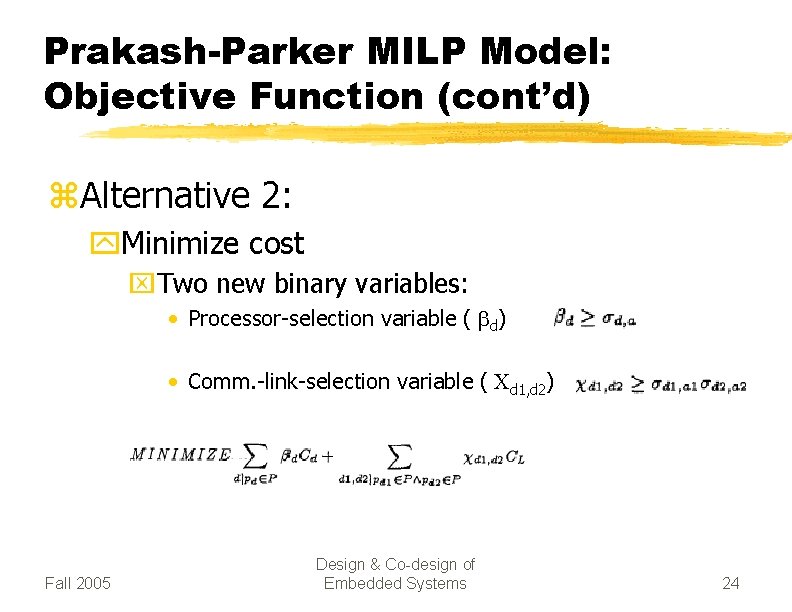

Prakash-Parker MILP Model: Objective Function (cont’d) z. Alternative 2: y. Minimize cost x. Two new binary variables: • Processor-selection variable ( d) • Comm. -link-selection variable ( d 1, d 2) Fall 2005 Design & Co-design of Embedded Systems 24

Prakash-Parker MILP Model (cont’d) z. More constraints can be added at wish z. Non-linear constraints were linearized z. The MILP formulation solved using Bozo (Branch-and-Bound MILP solver using XMP linear-programming package) Fall 2005 Design & Co-design of Embedded Systems 25

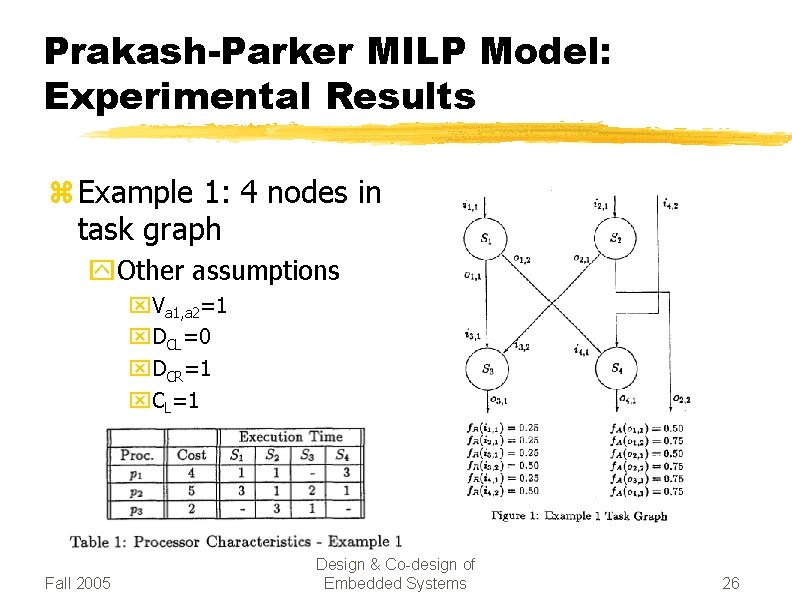

Prakash-Parker MILP Model: Experimental Results z Example 1: 4 nodes in task graph y. Other assumptions x. Va 1, a 2=1 x. DCL=0 x. DCR=1 x. CL=1 Fall 2005 Design & Co-design of Embedded Systems 26

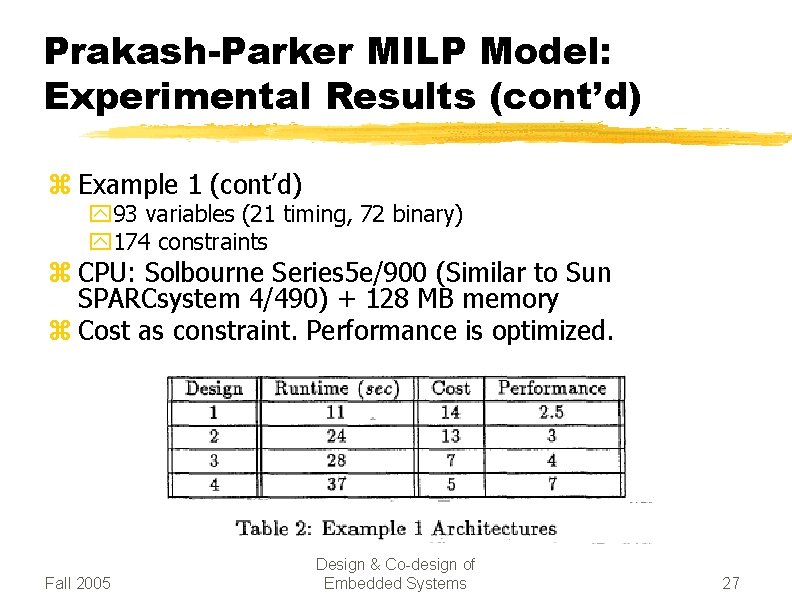

Prakash-Parker MILP Model: Experimental Results (cont’d) z Example 1 (cont’d) y 93 variables (21 timing, 72 binary) y 174 constraints z CPU: Solbourne Series 5 e/900 (Similar to Sun SPARCsystem 4/490) + 128 MB memory z Cost as constraint. Performance is optimized. Fall 2005 Design & Co-design of Embedded Systems 27

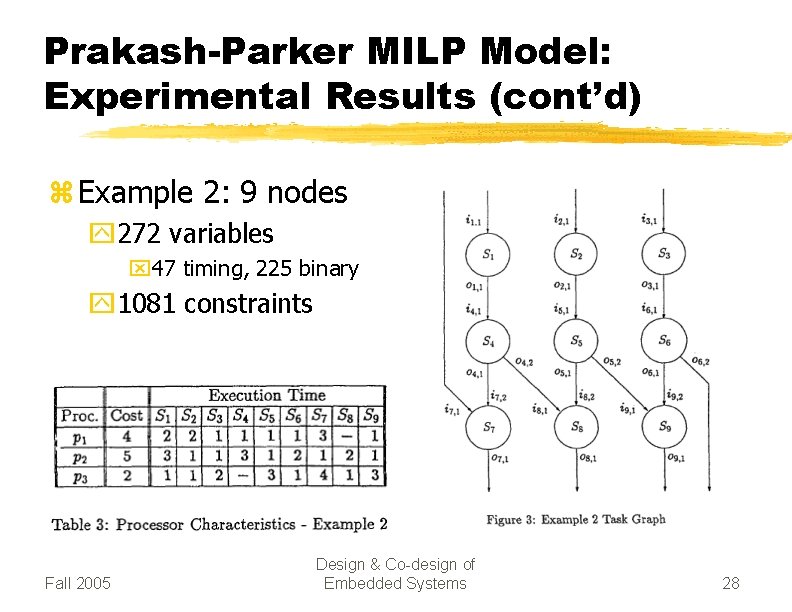

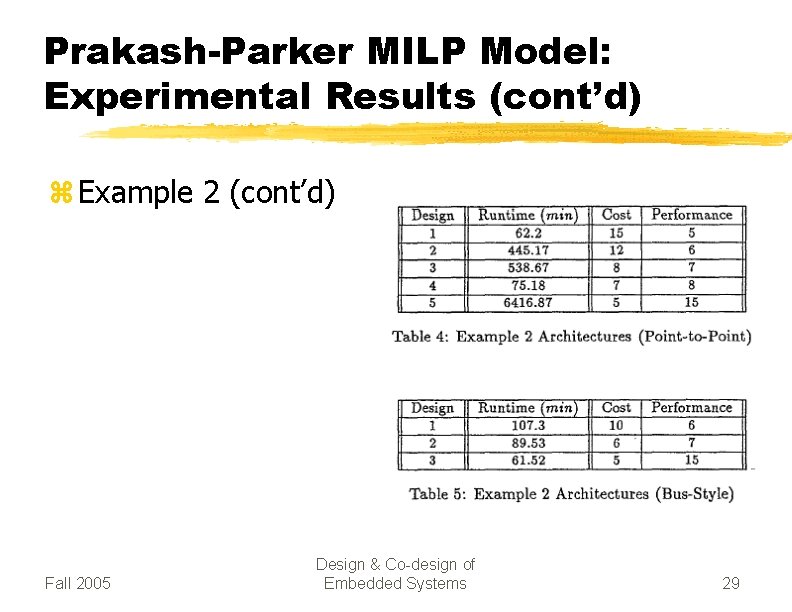

Prakash-Parker MILP Model: Experimental Results (cont’d) z Example 2: 9 nodes y 272 variables x 47 timing, 225 binary y 1081 constraints Fall 2005 Design & Co-design of Embedded Systems 28

Prakash-Parker MILP Model: Experimental Results (cont’d) z Example 2 (cont’d) Fall 2005 Design & Co-design of Embedded Systems 29

Prakash-Parker MILP Model: Experimental Results (cont’d) z. Experimental Results y. Applied only to relatively small problems x. Reason: use of general ILP solvers x. Their largest task graph: 9 processes • Took 6000 CPU minutes on an unspecified processor y. Significance of the work x. Did Achieve precisely optimal solutions on those examples which they could solve x. Used as benchmarks for heuristic co-synthesis algorithms Fall 2005 Design & Co-design of Embedded Systems 30

What we learned today z. Distributed System Co-Synthesis : y. The other broad category of co-synthesis algorithms y. General terms y. One famous instance: Integer Linear Programming [Prakash-Parker 91] Fall 2005 Design & Co-design of Embedded Systems 31

- Slides: 31