Chapter 6 Cosynthesis Techniques 1 Cosynthesis l Methodical

- Slides: 50

Chapter 6 Co-synthesis Techniques 1

Cosynthesis l Methodical approach to system implementations using automated synthesis-oriented techniques l Methodology and performance constraints determine partitioning into hardware and software implementations l The result is “optimal” system that benefits from analysis of hardware/software design trade-off analysis 2

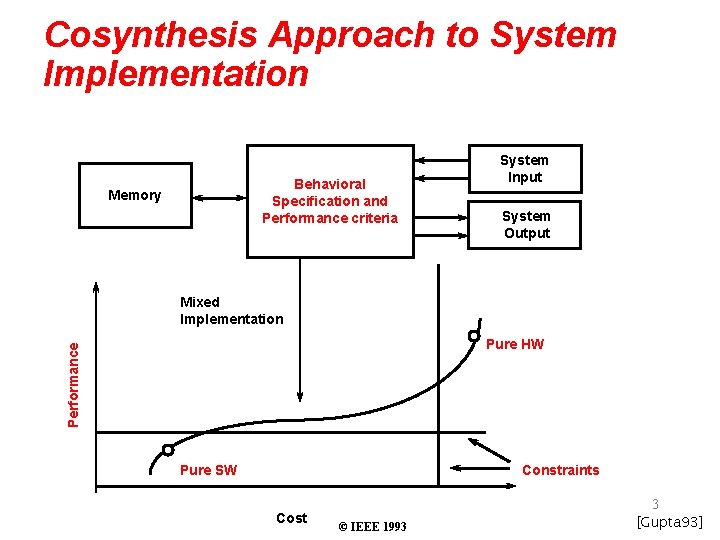

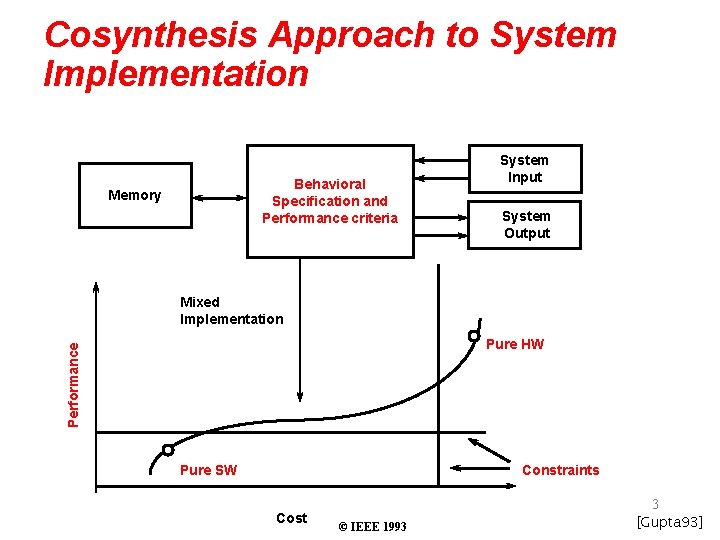

Cosynthesis Approach to System Implementation Behavioral Specification and Performance criteria Memory System Input System Output Mixed Implementation Performance Pure HW Pure SW Constraints Cost © IEEE 1993 3 [Gupta 93]

Co-synthesis l Implementation of hardware and software components after partitioning l Constraints and optimization criteria similar to those for partitioning l Area and size traded-off against performance l Cost considerations 4

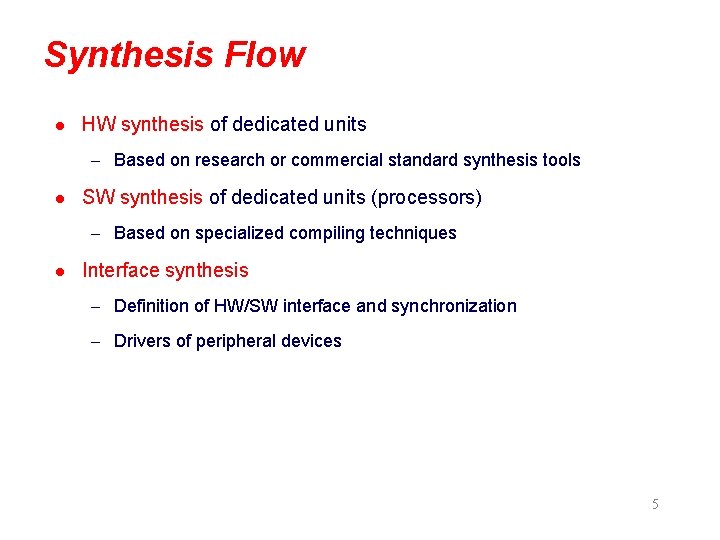

Synthesis Flow l HW synthesis of dedicated units – Based on research or commercial standard synthesis tools l SW synthesis of dedicated units (processors) – Based on specialized compiling techniques l Interface synthesis – Definition of HW/SW interface and synchronization – Drivers of peripheral devices 5

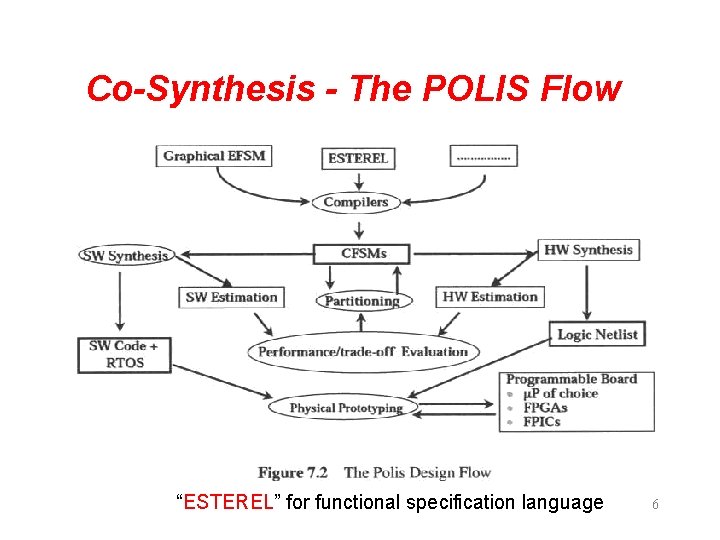

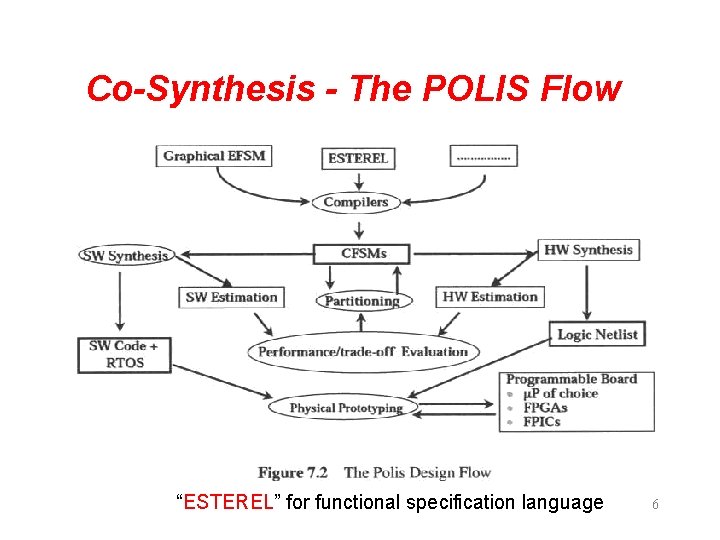

Co-Synthesis - The POLIS Flow “ESTEREL” for functional specification language 6

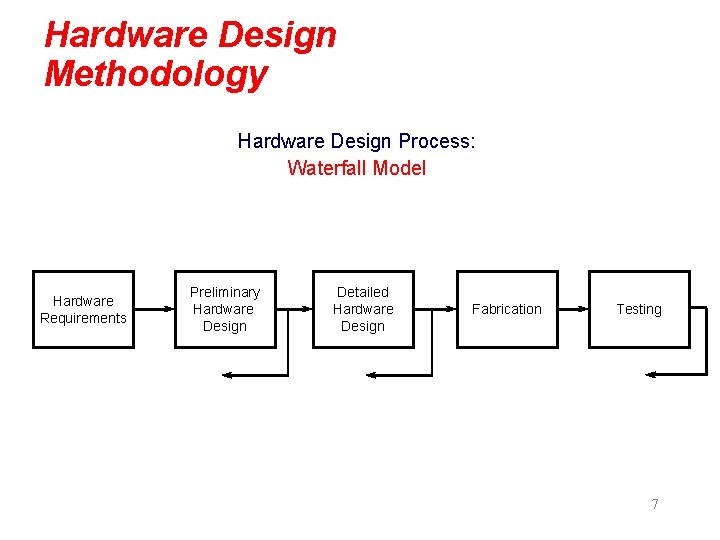

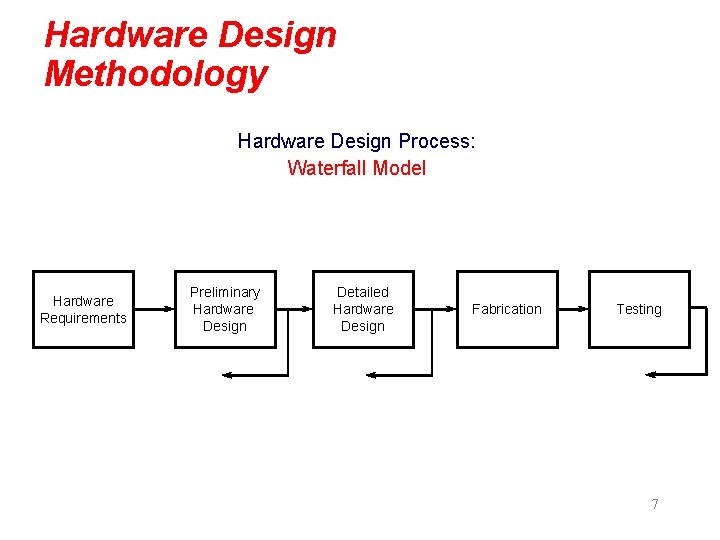

Hardware Design Methodology Hardware Design Process: Waterfall Model Hardware Requirements Preliminary Hardware Design Detailed Hardware Design Fabrication Testing 7

Hardware Design Methodology (Cont. ) l Use of HDLs for modeling and simulation l Use of lower-level synthesis tools to derive register transfer and lower-level designs l Use of high-level hardware synthesis tools – Behavioral descriptions – System design constraints l Introduction of synthesis for testability at all levels 8

Hardware Synthesis l Definition – The automatic design and implementation of hardware from a specification written in a hardware description language l Goals/benefits – To quickly create and modify designs – To support a methodology that allows for multiple design alternative consideration – To remove from the designer the handling of the tedious details of VLSI design – To support the development of correct designs 9

Hardware Synthesis Categories l Algorithm synthesis – Synthesis from design requirements to control-flow behavior or abstract behavior – Largely a manual process l Register-transfer synthesis – Also referred to as “high-level” or “behavioral” synthesis – Synthesis from abstract behavior, control-flow behavior, or register-transfer behavior (on one hand) to register-transfer structure (on the other) – Logic synthesis – Synthesis from register-transfer structures or Boolean equations to gate-level logic (or physical implementations using a predefined cell or IC library) 10

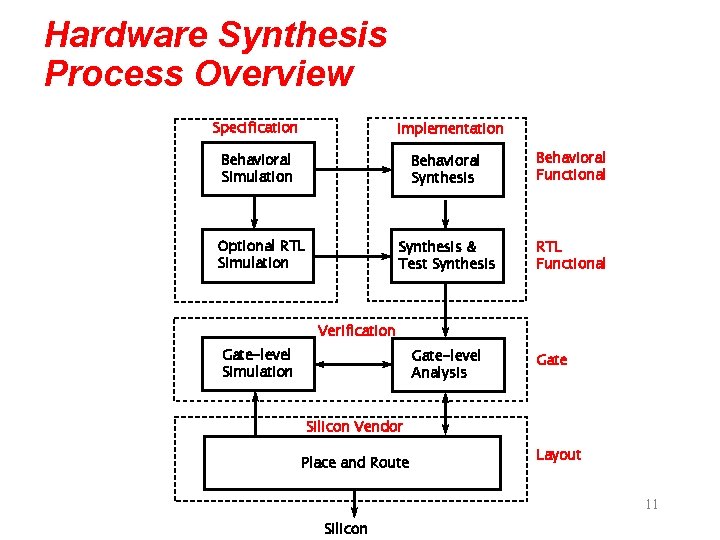

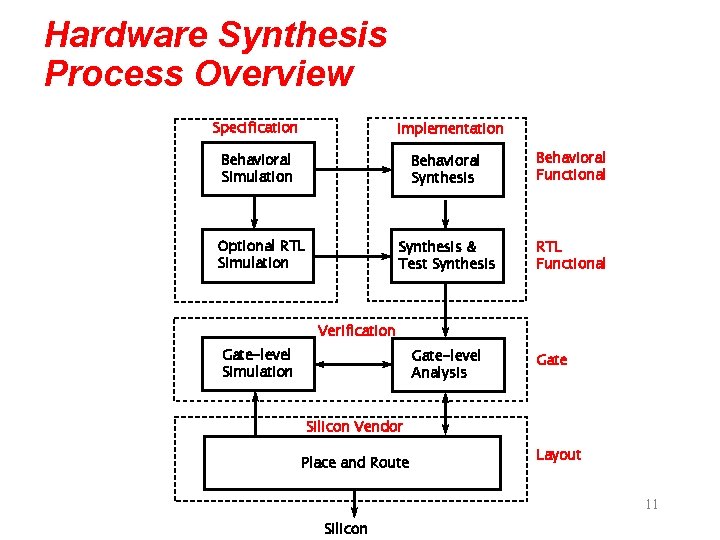

Hardware Synthesis Process Overview Specification Implementation Behavioral Synthesis Behavioral Functional Synthesis & Test Synthesis RTL Functional Behavioral Simulation Optional RTL Simulation Verification Gate-level Simulation Gate-level Analysis Gate Silicon Vendor Place and Route Layout 11 Silicon

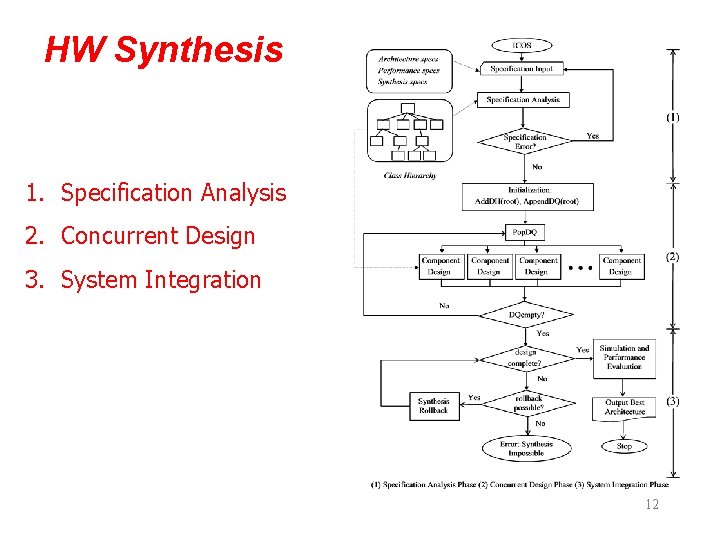

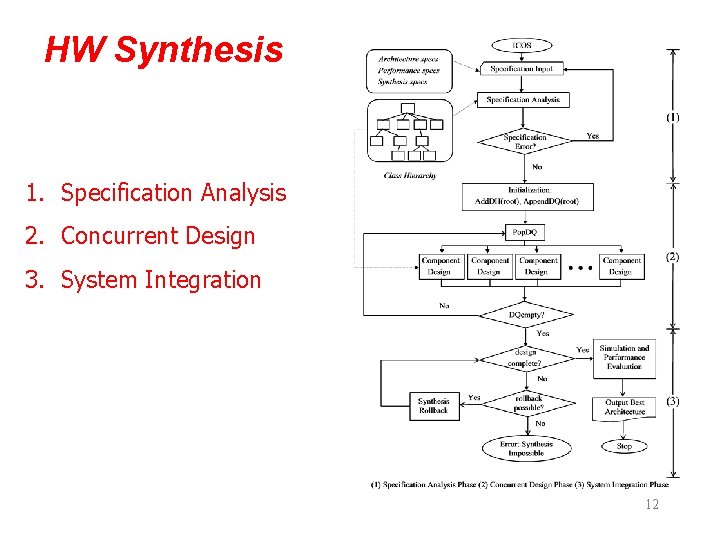

HW Synthesis 1. Specification Analysis 2. Concurrent Design 3. System Integration 12

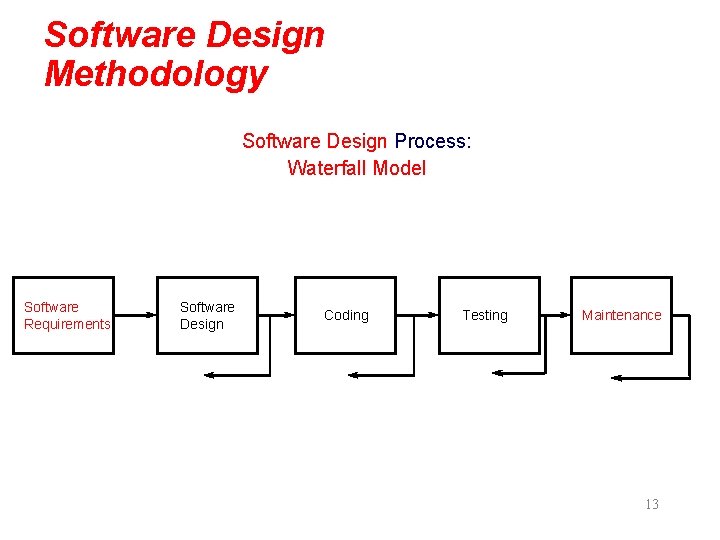

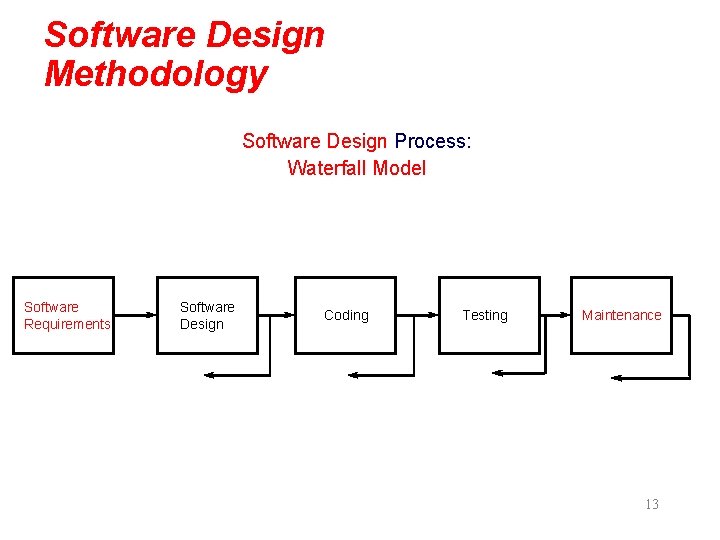

Software Design Methodology Software Design Process: Waterfall Model Software Requirements Software Design Coding Testing Maintenance 13

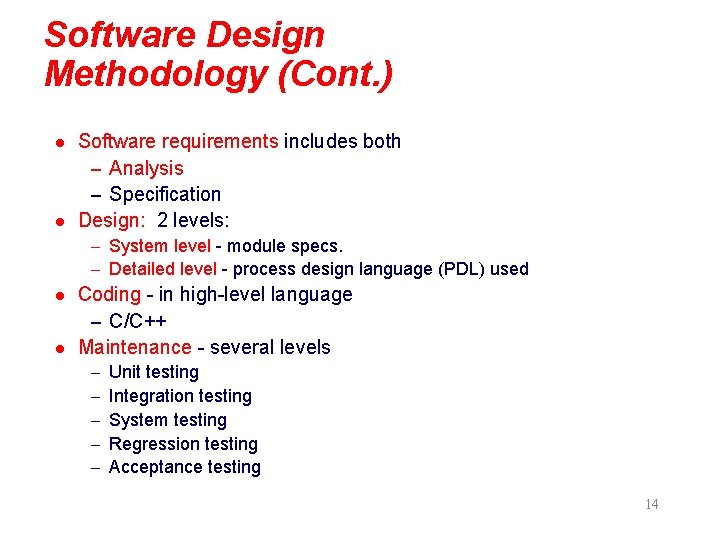

Software Design Methodology (Cont. ) l l Software requirements includes both – Analysis – Specification Design: 2 levels: – System level - module specs. – Detailed level - process design language (PDL) used l l Coding - in high-level language – C/C++ Maintenance - several levels – – – Unit testing Integration testing System testing Regression testing Acceptance testing 14

Software Synthesis l Definition: the automatic development of correct and efficient software from specifications and reusable components l Goals/benefits – To Increase software productivity – To lower development costs – To Increase confidence that software implementation satisfies specification – To support the development of correct programs 15

Why Use Software Synthesis? l Software development is becoming the major cost driver in fielding a system l To significantly improve both the design cycle time and life-cycle cost of embedded systems, a new software design methodology, including automated code generation, is necessary l Synthesis supports a correct-by-construction philosophy l Techniques support software reuse 16

Why Software Synthesis? l More software high complexity need for automatic design (synthesis) l Eliminate human and logical errors l Relatively immature synthesis techniques for software l Code optimizations – size – efficiency l Automatic code generation 17

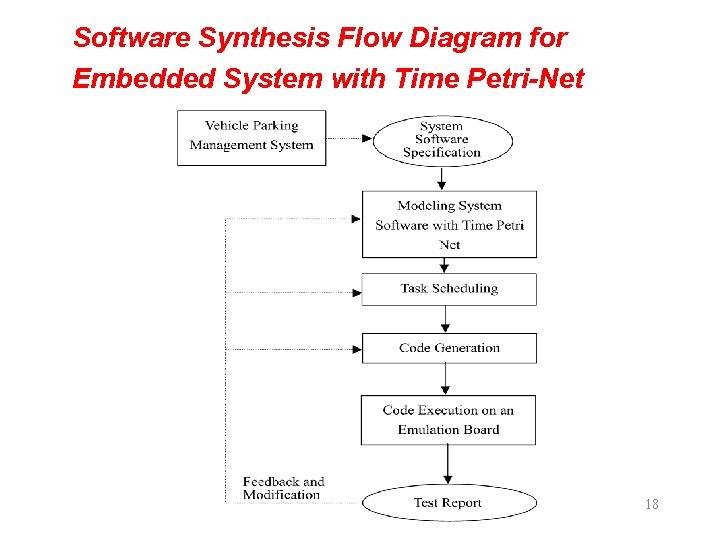

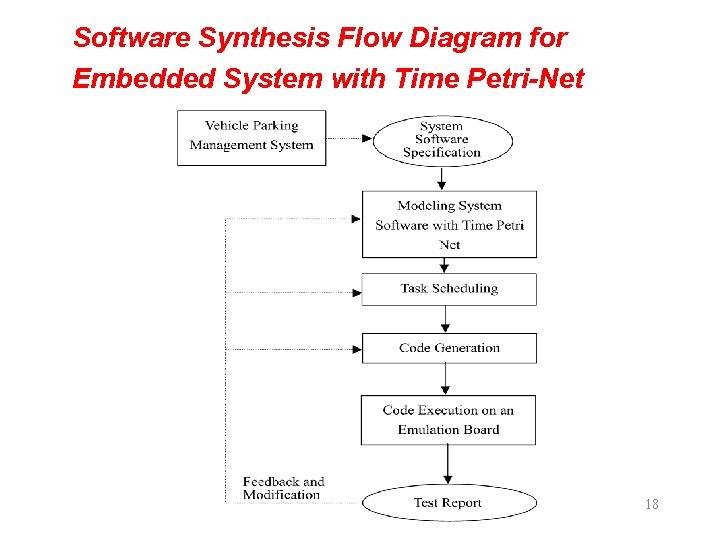

Software Synthesis Flow Diagram for Embedded System with Time Petri-Net 18

Automatically Generate CODE l Real-Time Embedded System Model? Set of concurrent tasks with memory and timing constraints! l How to execute in an embedded system (e. g. 1 CPU, 100 KB Mem)? Task Scheduling! l How to generate code? Map schedules to software code! l Code optimizations? Minimize size, maximize efficiency! 19

Software Synthesis Categories l Language compilers – ADA and C compilers – YACC - yet another compiler – Visual Basic l Domain-specific synthesis – Application generators from software libraries 20

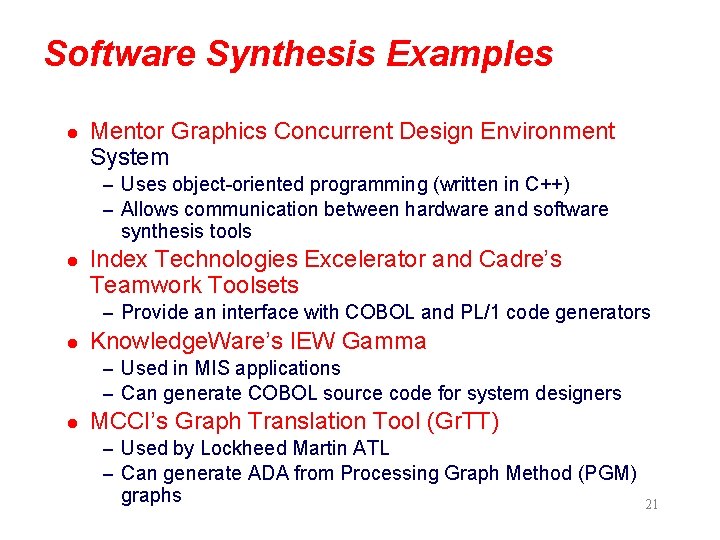

Software Synthesis Examples l Mentor Graphics Concurrent Design Environment System – Uses object-oriented programming (written in C++) – Allows communication between hardware and software synthesis tools l Index Technologies Excelerator and Cadre’s Teamwork Toolsets – Provide an interface with COBOL and PL/1 code generators l Knowledge. Ware’s IEW Gamma – Used in MIS applications – Can generate COBOL source code for system designers l MCCI’s Graph Translation Tool (Gr. TT) – Used by Lockheed Martin ATL – Can generate ADA from Processing Graph Method (PGM) graphs 21

Software Synthesis Tool: The Design of Synthesis Tool for Interrupted-based Embedded Software 22

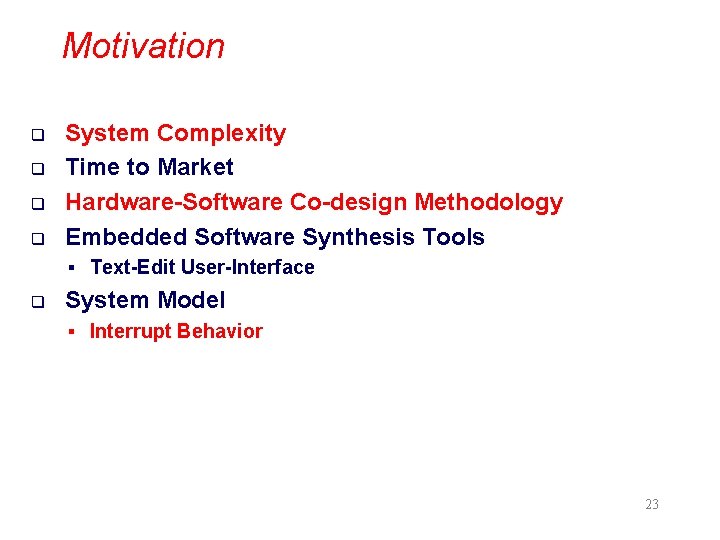

Motivation q q System Complexity Time to Market Hardware-Software Co-design Methodology Embedded Software Synthesis Tools § Text-Edit User-Interface q System Model § Interrupt Behavior 23 Introduction

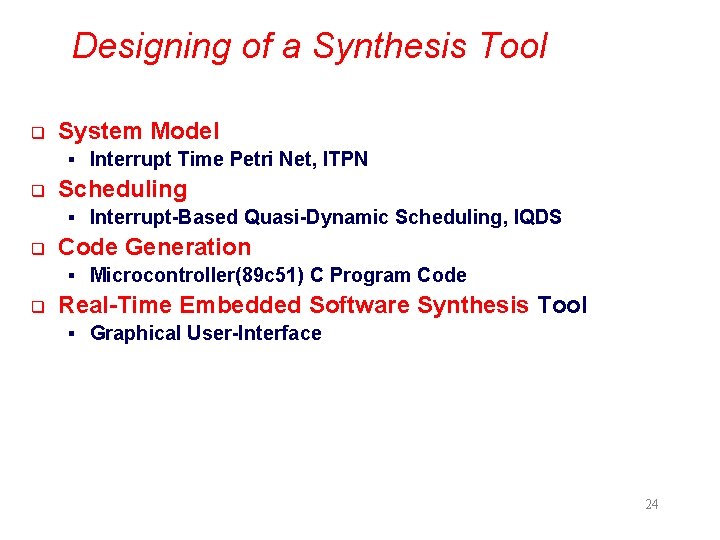

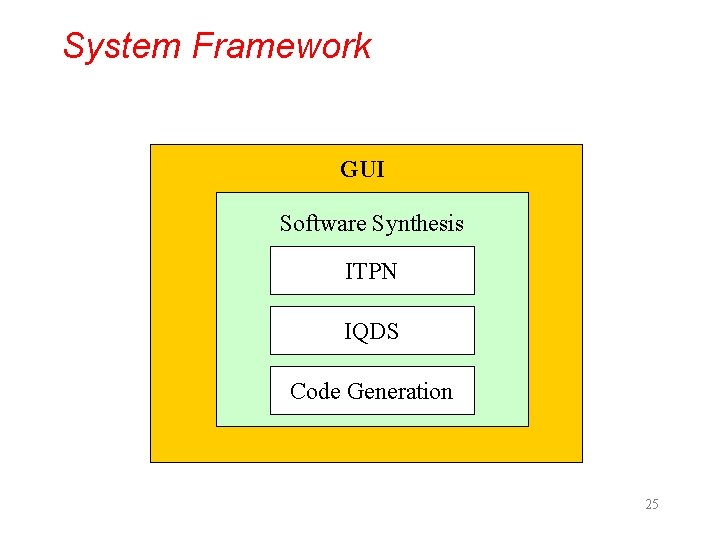

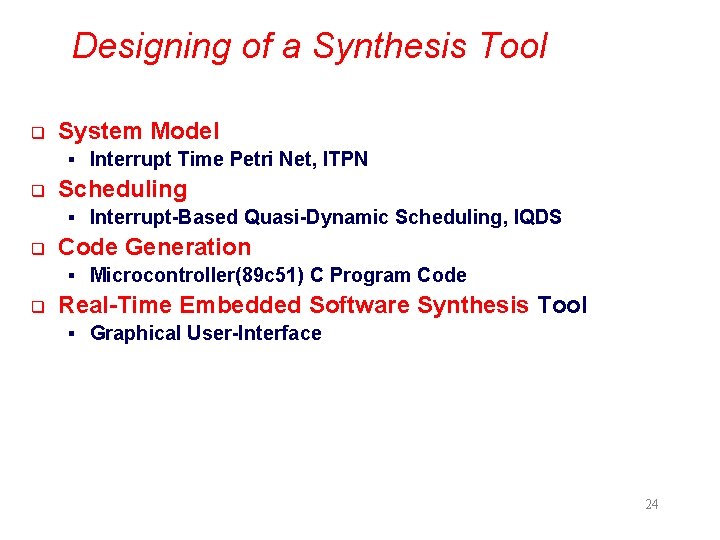

Designing of a Synthesis Tool q System Model § Interrupt Time Petri Net, ITPN q Scheduling § Interrupt-Based Quasi-Dynamic Scheduling, IQDS q Code Generation § Microcontroller(89 c 51) C Program Code q Real-Time Embedded Software Synthesis Tool § Graphical User-Interface 24 Introduction

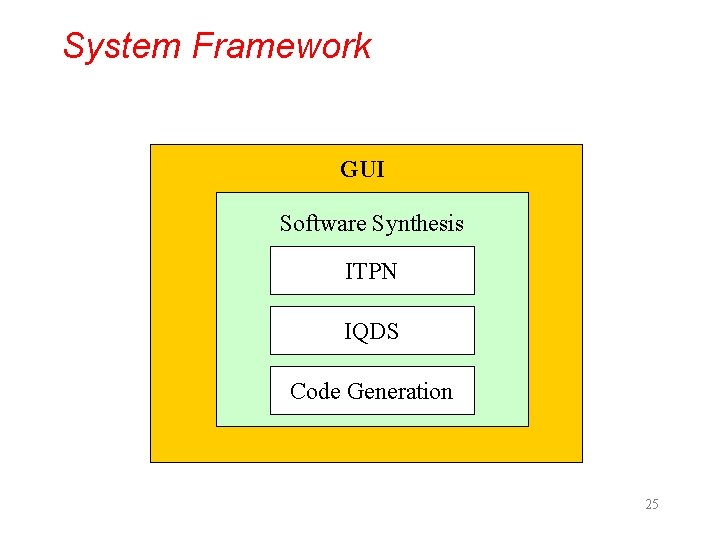

System Framework GUI Software Synthesis ITPN IQDS Code Generation 25 Introduction

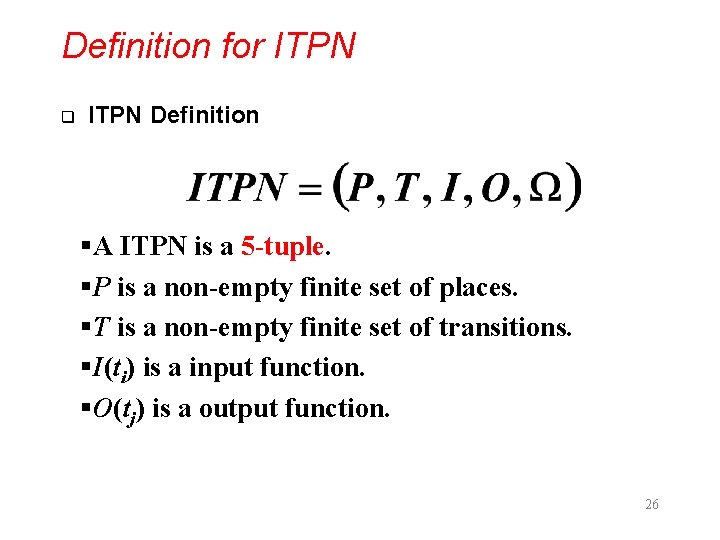

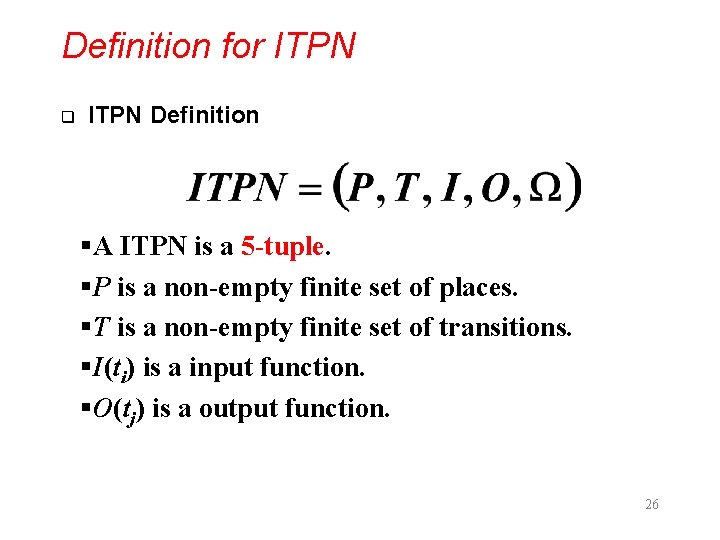

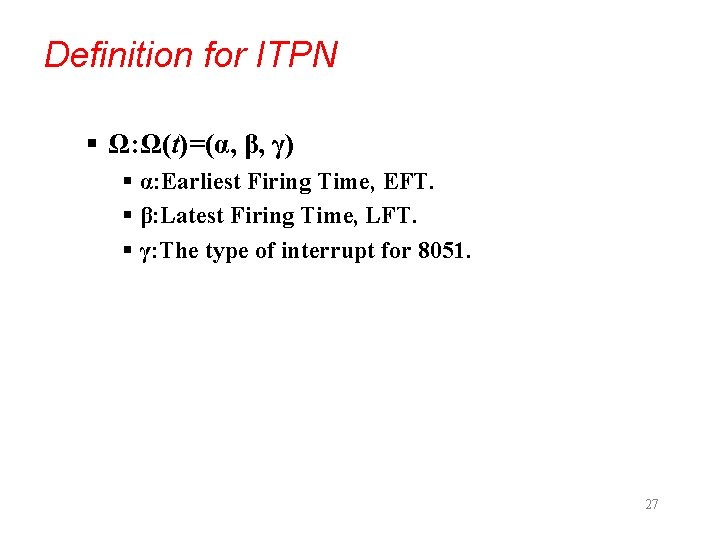

Definition for ITPN q ITPN Definition §A ITPN is a 5 -tuple. §P is a non-empty finite set of places. §T is a non-empty finite set of transitions. §I(ti) is a input function. §O(tj) is a output function. 26 System Model

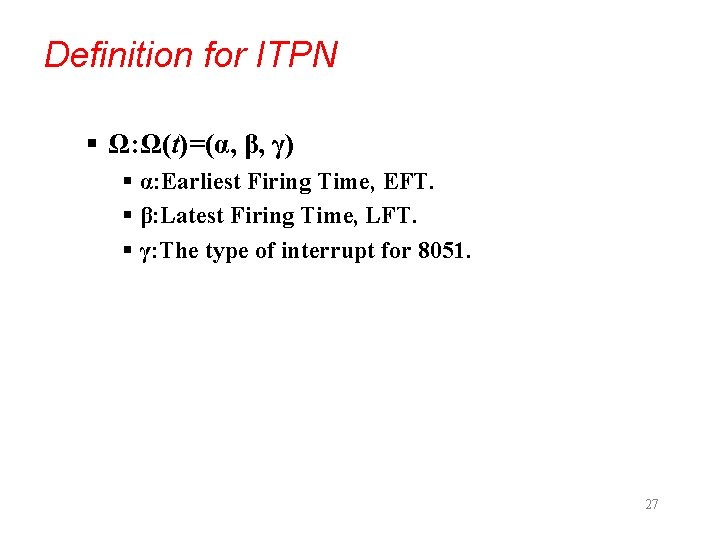

Definition for ITPN § Ω: Ω(t)=(α, β, γ) § α: Earliest Firing Time, EFT. § β: Latest Firing Time, LFT. § γ: The type of interrupt for 8051. 27

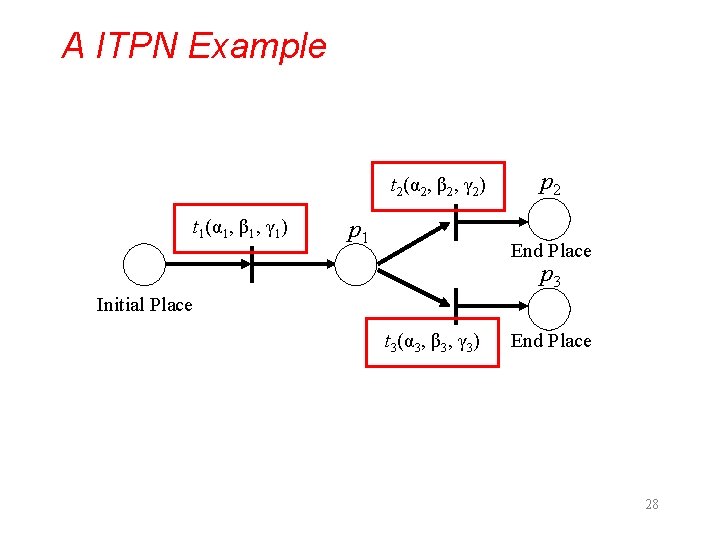

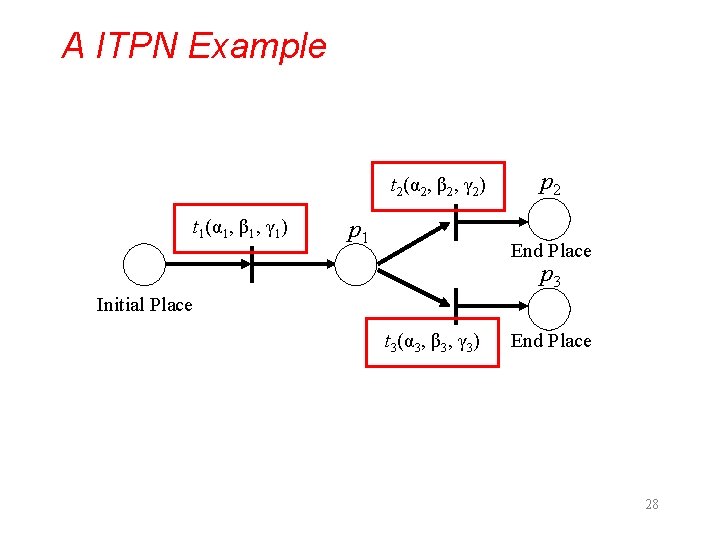

A ITPN Example t 2(α 2, β 2, γ 2) t 1(α 1, β 1, γ 1) p 1 p 2 End Place p 3 Initial Place t 3(α 3, β 3, γ 3) End Place 28 System Model

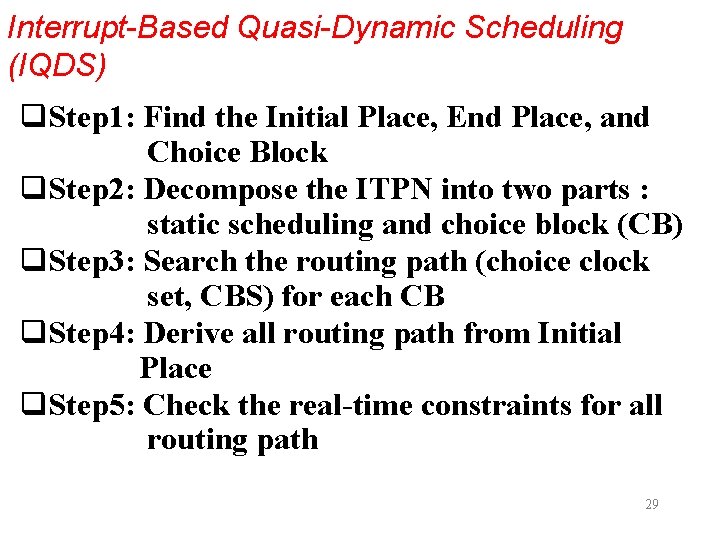

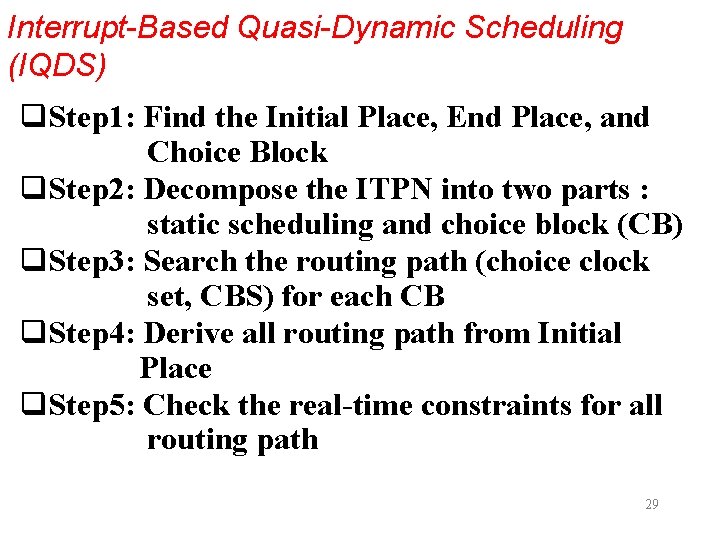

Interrupt-Based Quasi-Dynamic Scheduling (IQDS) q. Step 1: Find the Initial Place, End Place, and Choice Block q. Step 2: Decompose the ITPN into two parts : static scheduling and choice block (CB) q. Step 3: Search the routing path (choice clock set, CBS) for each CB q. Step 4: Derive all routing path from Initial Place q. Step 5: Check the real-time constraints for all routing path Scheduling & Code Generation 29

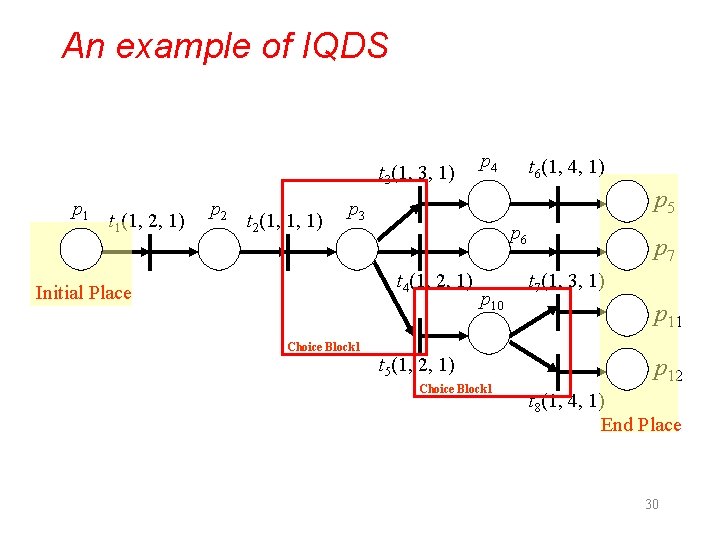

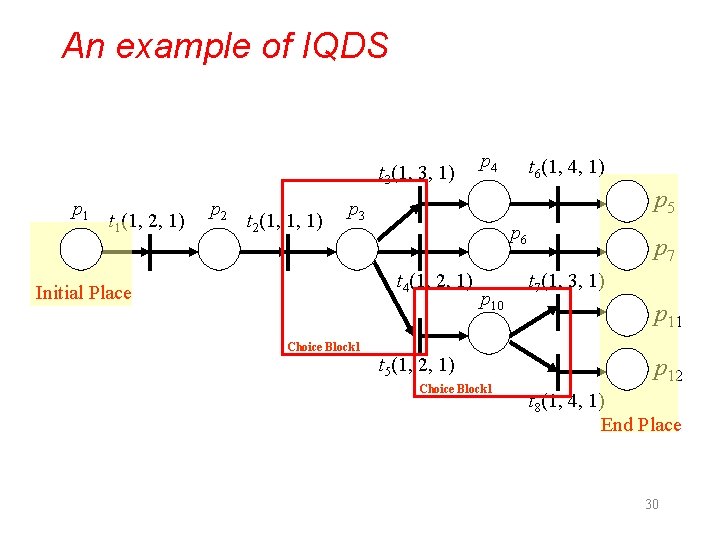

An example of IQDS t 3(1, 3, 1) p 1 t 1(1, 2, 1) p 2 t 2(1, 1, 1) p 4 p 5 p 3 p 6 t 4(1, 2, 1) Initial Place Choice Block 1 p 10 t 5(1, 2, 1) Choice Block 1 Scheduling & Code Generation t 6(1, 4, 1) p 7 t 7(1, 3, 1) p 11 p 12 t 8(1, 4, 1) End Place 30

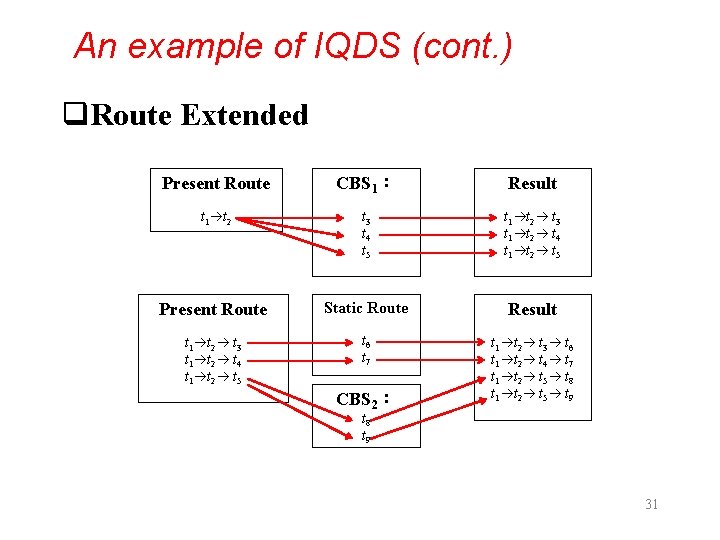

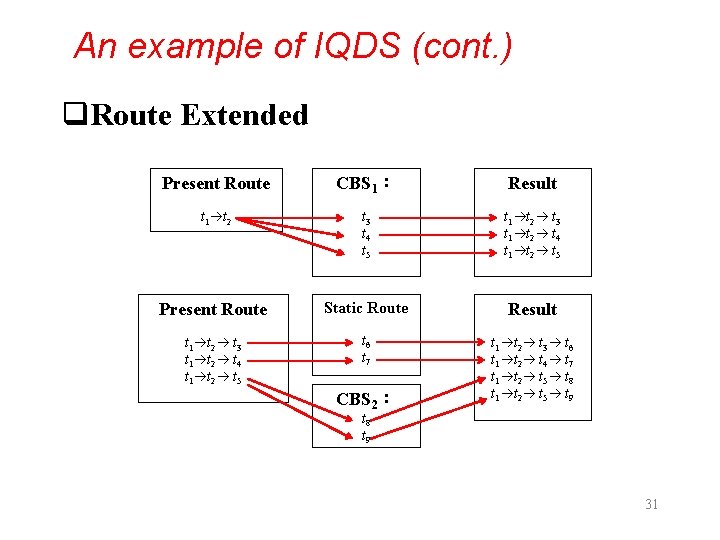

An example of IQDS (cont. ) q. Route Extended Present Route CBS 1: Result t 1 t 2 t 3 t 4 t 5 t 1 t 2 t 3 t 1 t 2 t 4 t 1 t 2 t 5 Present Route Static Route Result t 1 t 2 t 3 t 1 t 2 t 4 t 1 t 2 t 5 t 6 t 7 t 1 t 2 t 3 t 6 t 1 t 2 t 4 t 7 t 1 t 2 t 5 t 8 t 1 t 2 t 5 t 9 CBS 2: t 8 t 9 Scheduling & Code Generation 31

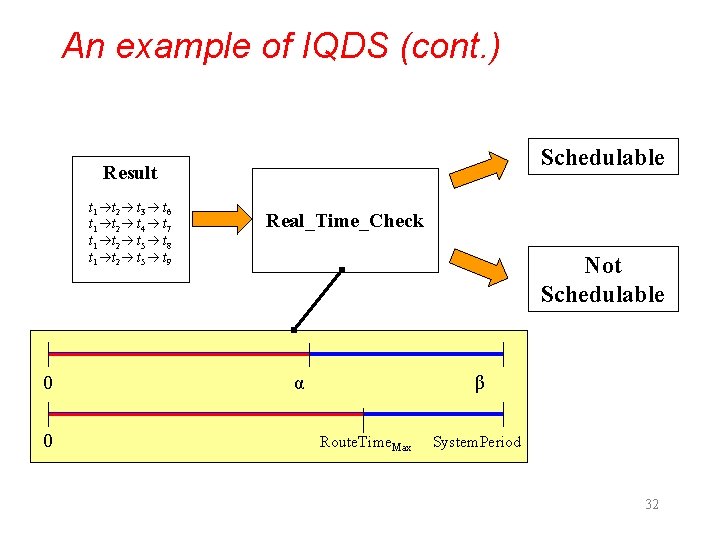

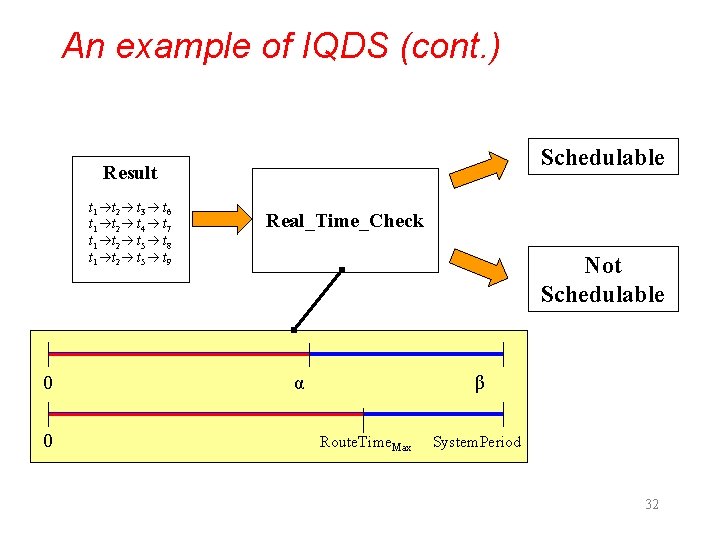

An example of IQDS (cont. ) Schedulable Result t 1 t 2 t 3 t 6 t 1 t 2 t 4 t 7 t 1 t 2 t 5 t 8 t 1 t 2 t 5 t 9 0 0 Scheduling & Code Generation Real_Time_Check Not Schedulable α β Route. Time. Max System. Period 32

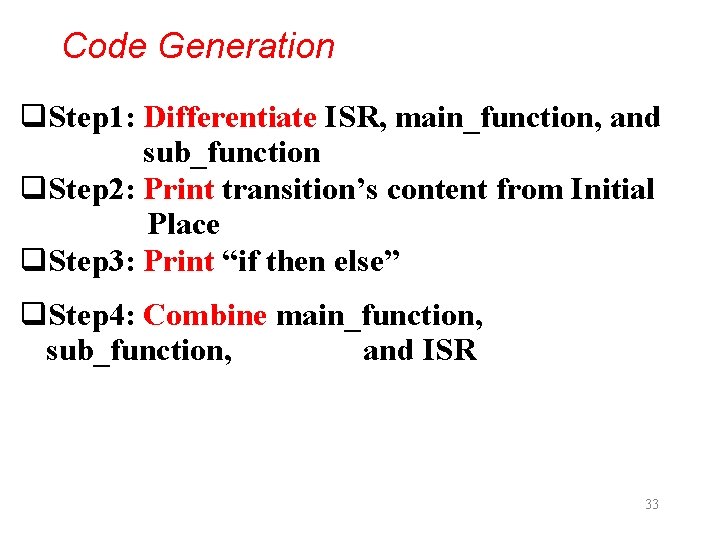

Code Generation q. Step 1: Differentiate ISR, main_function, and sub_function q. Step 2: Print transition’s content from Initial Place q. Step 3: Print “if then else” q. Step 4: Combine main_function, sub_function, and ISR 33

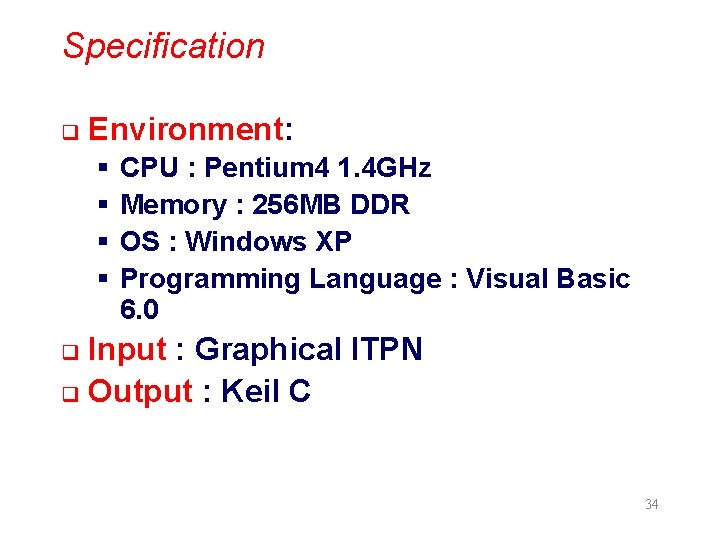

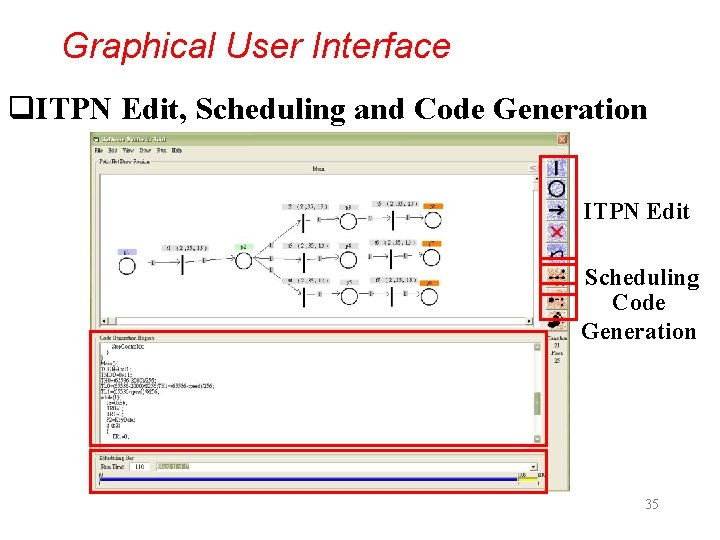

Specification q Environment: § § CPU : Pentium 4 1. 4 GHz Memory : 256 MB DDR OS : Windows XP Programming Language : Visual Basic 6. 0 Input : Graphical ITPN q Output : Keil C q 34 Software Synthesis Tool

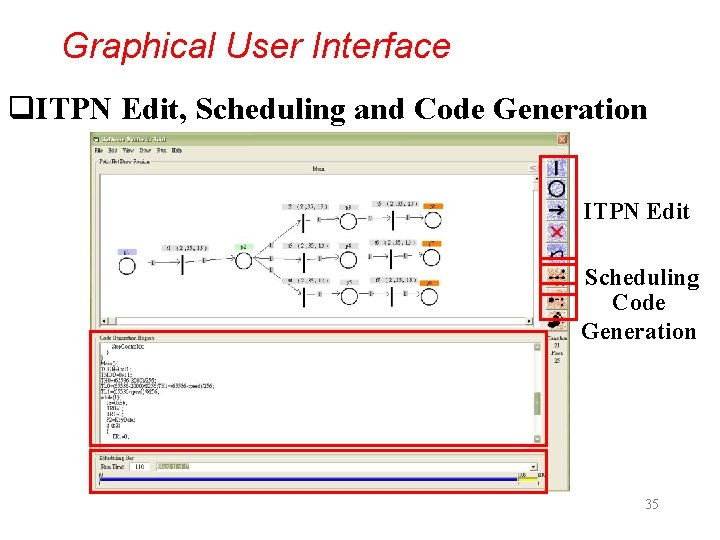

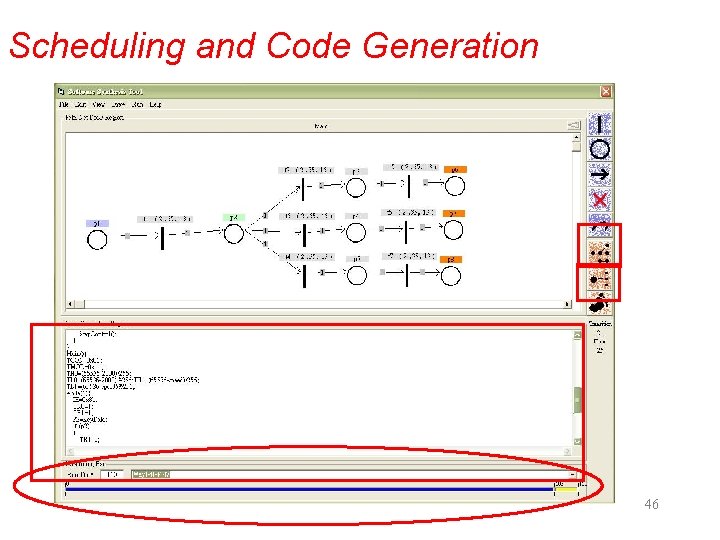

Graphical User Interface q. ITPN Edit, Scheduling and Code Generation ITPN Edit Scheduling Code Generation 35 Software Synthesis Tool

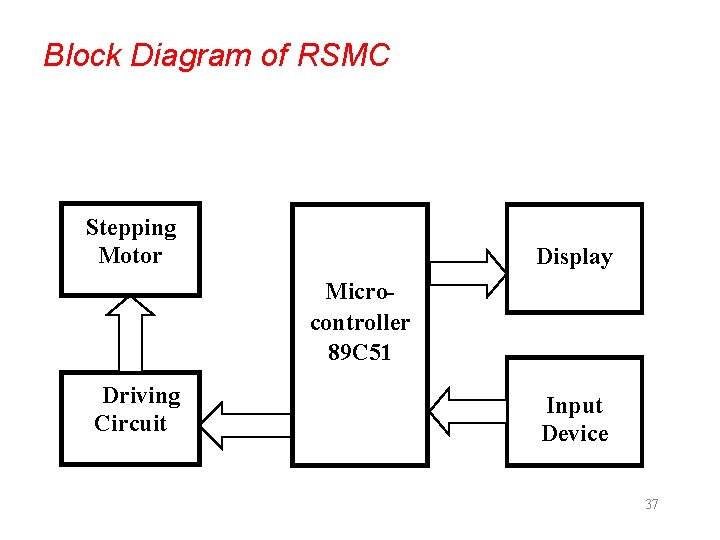

Real-time Stepping Motor Control (RSMC) q System Function: § Control Stepping Motor speed and direction. § INT 0, Timer 1: Motor’s speed control. § Timer 0 : Motor’s direction control. 36 Examples

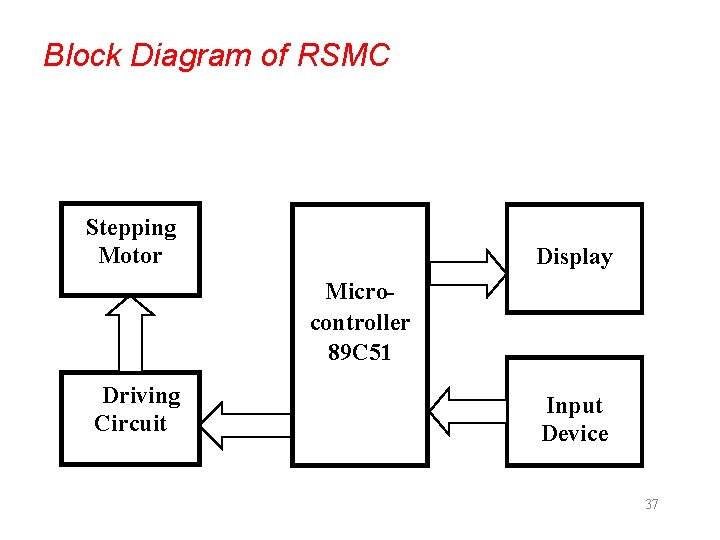

Block Diagram of RSMC Stepping Motor Display Microcontroller 89 C 51 Driving Circuit Input Device 37 Example

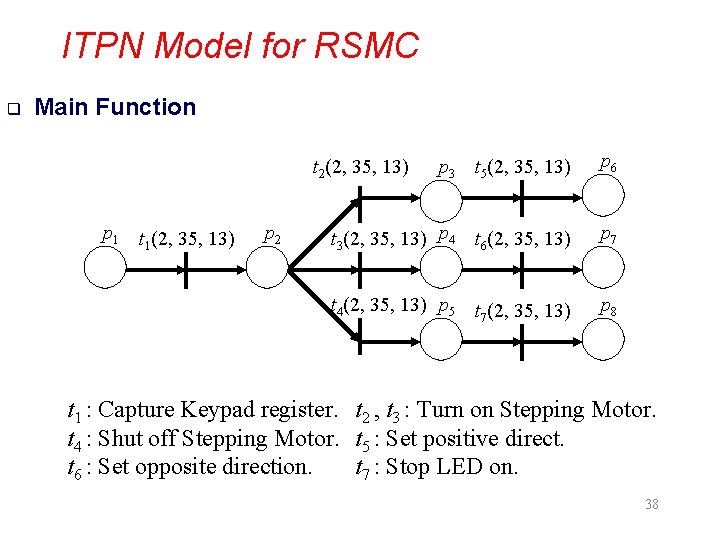

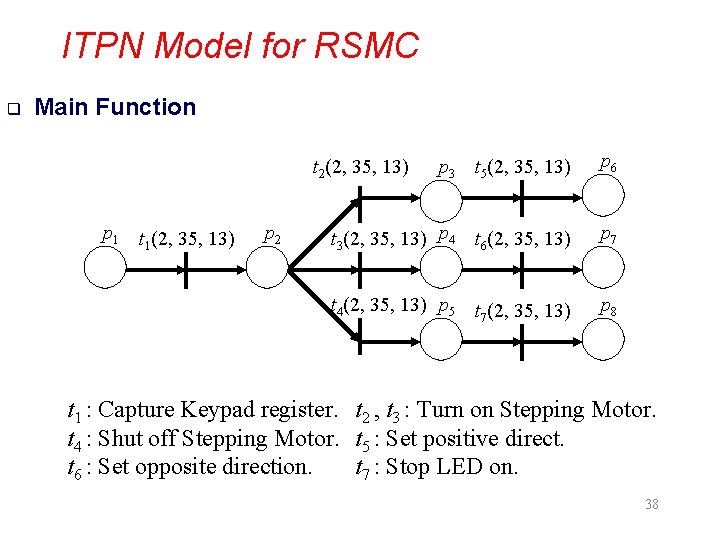

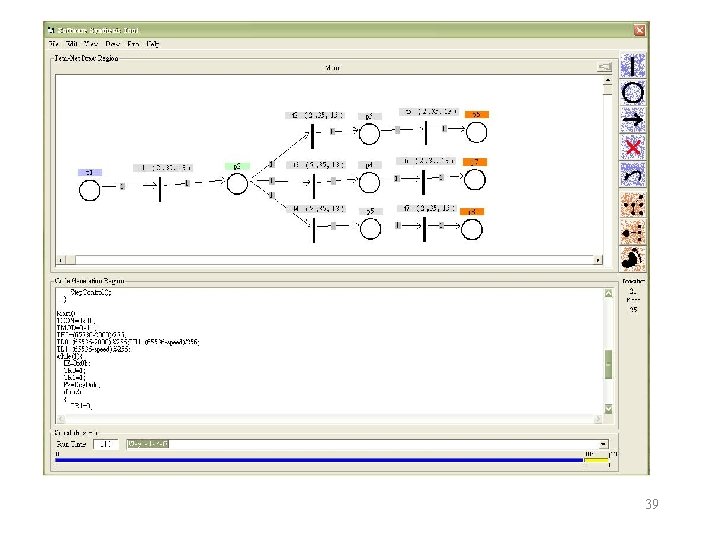

ITPN Model for RSMC q Main Function p 3 t 5(2, 35, 13) p 6 t 3(2, 35, 13) p 4 t 6(2, 35, 13) p 7 t 4(2, 35, 13) p 5 t (2, 35, 13) 7 p 8 t 2(2, 35, 13) p 1 t (2, 35, 13) 1 p 2 t 1 : Capture Keypad register. t 2 , t 3 : Turn on Stepping Motor. t 4 : Shut off Stepping Motor. t 5 : Set positive direct. t 6 : Set opposite direction. t 7 : Stop LED on. 38 Example

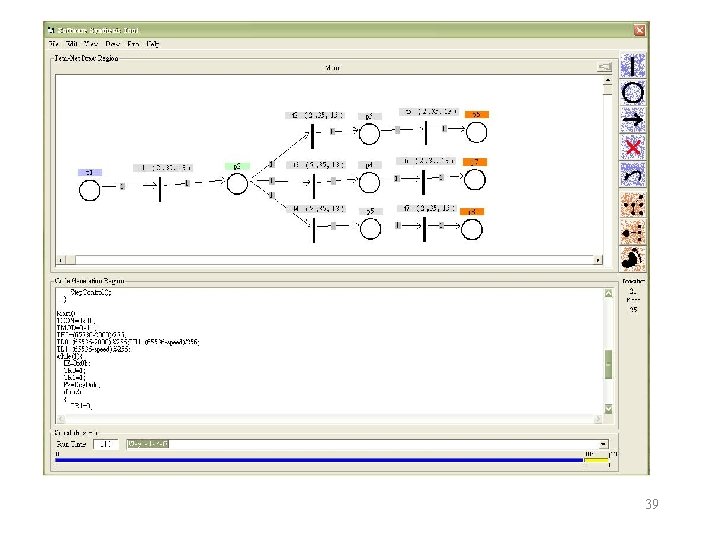

39

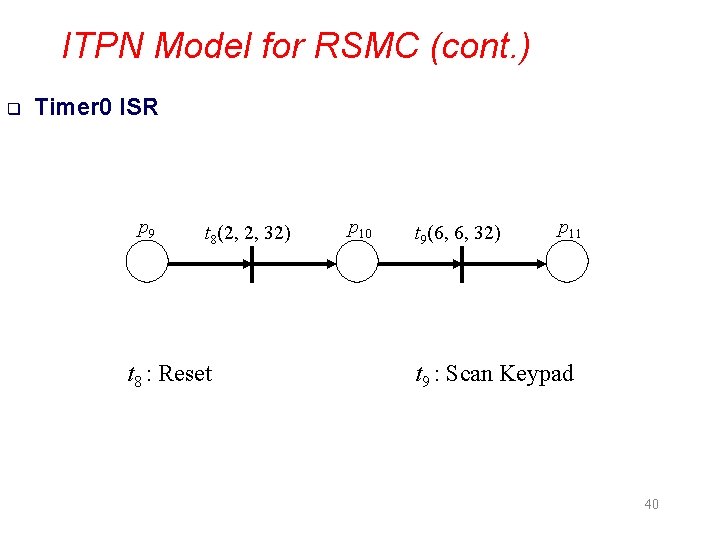

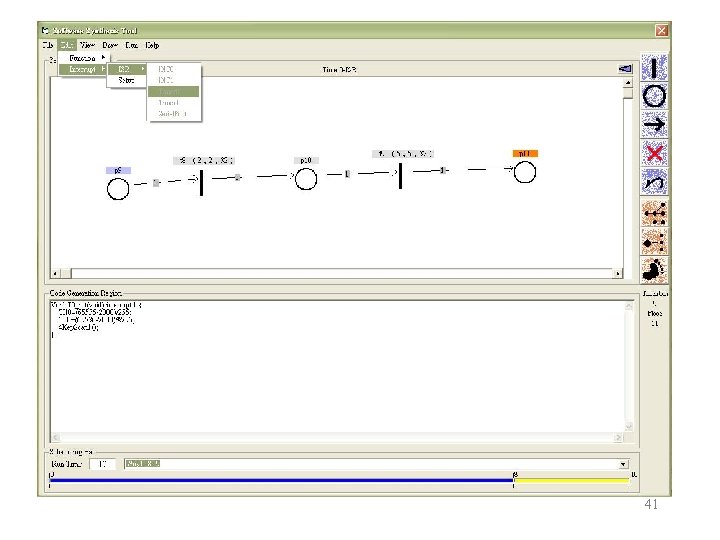

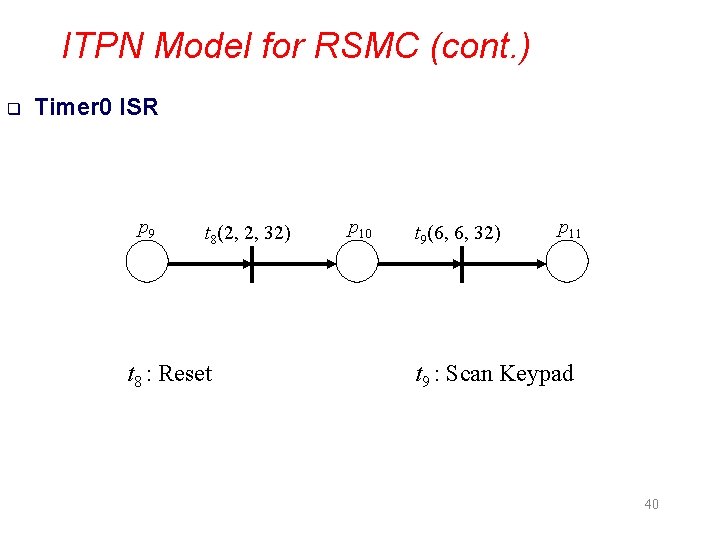

ITPN Model for RSMC (cont. ) q Timer 0 ISR p 9 t 8(2, 2, 32) t 8 : Reset p 10 t 9(6, 6, 32) p 11 t 9 : Scan Keypad 40 Example

41

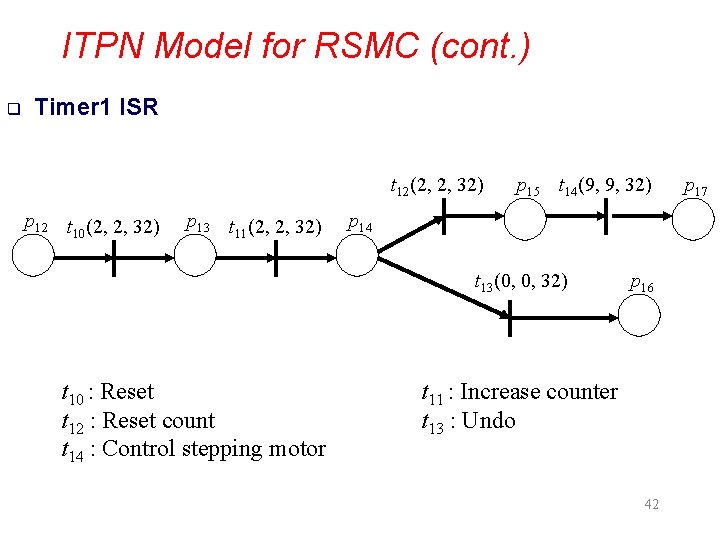

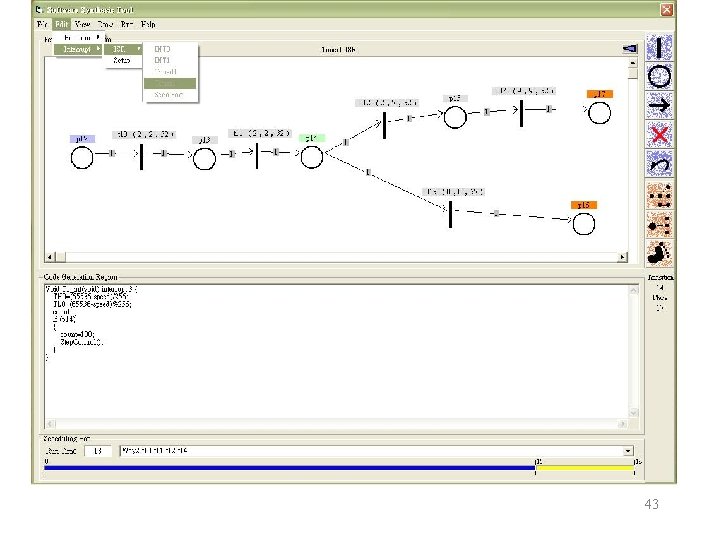

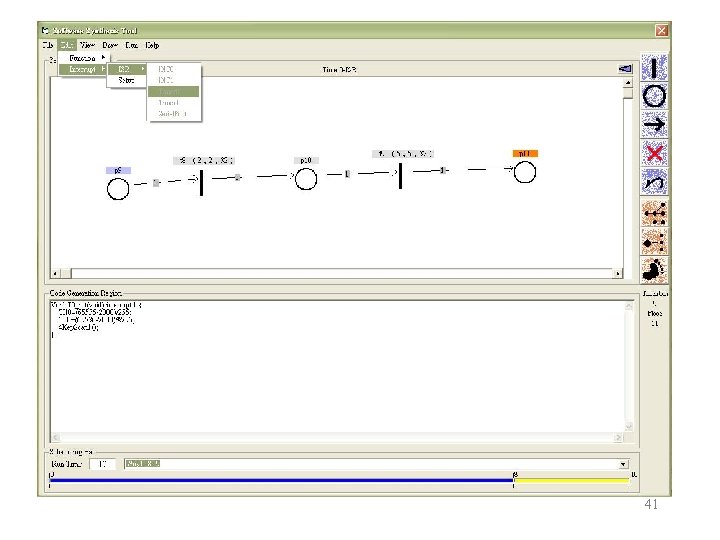

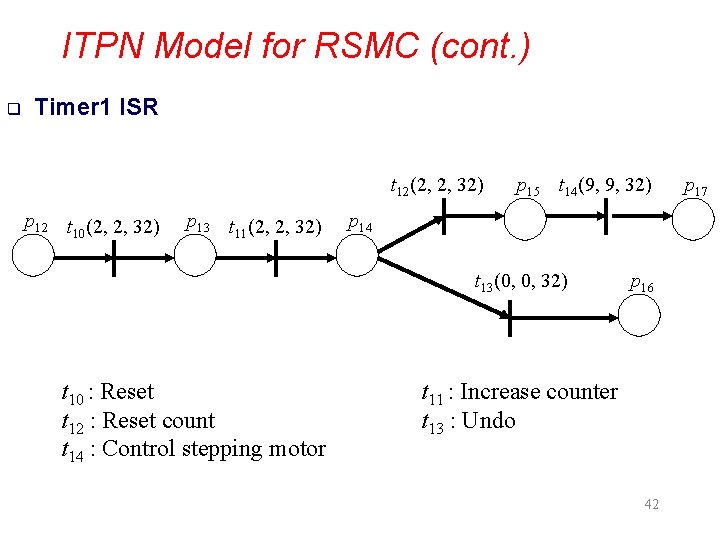

ITPN Model for RSMC (cont. ) q Timer 1 ISR t 12(2, 2, 32) p 12 t (2, 2, 32) 10 p 13 t (2, 2, 32) 11 p 15 t 14(9, 9, 32) p 14 t 13(0, 0, 32) t 10 : Reset t 12 : Reset count t 14 : Control stepping motor p 16 t 11 : Increase counter t 13 : Undo 42 Example p 17

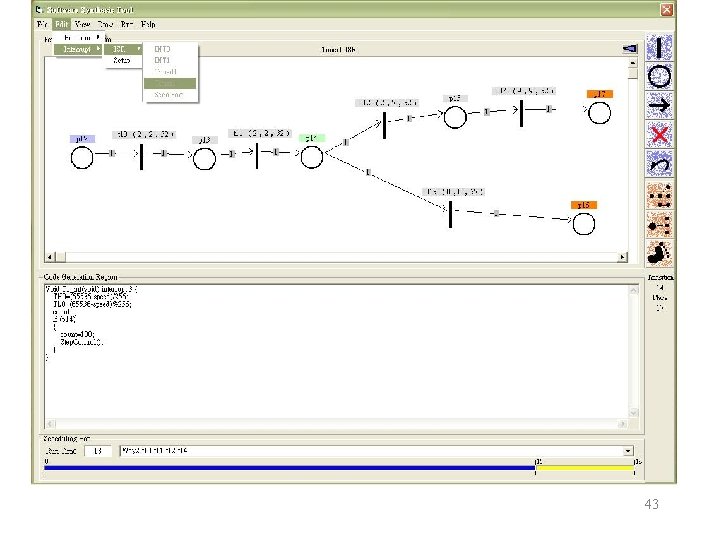

43

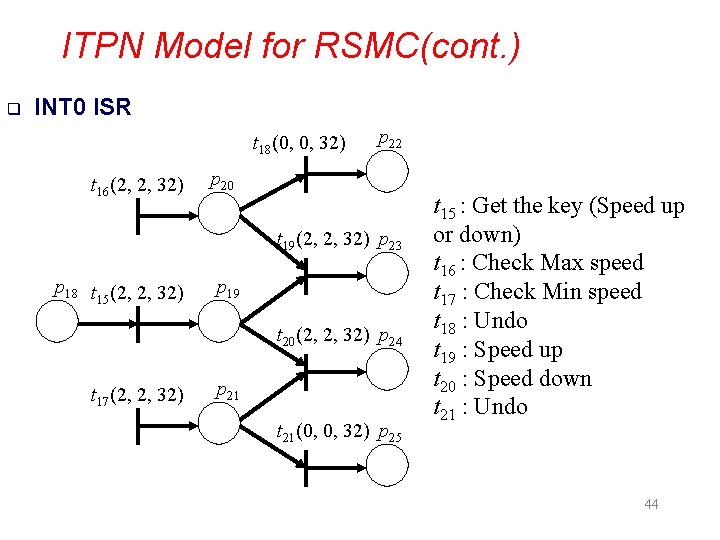

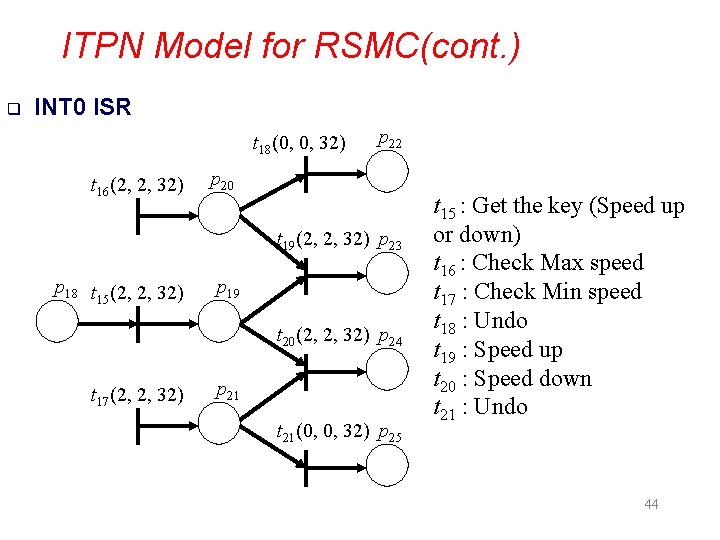

ITPN Model for RSMC(cont. ) q INT 0 ISR t 18(0, 0, 32) t 16(2, 2, 32) p 22 p 20 t 19(2, 2, 32) p 23 p 18 t (2, 2, 32) 15 p 19 t 20(2, 2, 32) p 24 t 17(2, 2, 32) p 21 t 21(0, 0, 32) p 25 t 15 : Get the key (Speed up or down) t 16 : Check Max speed t 17 : Check Min speed t 18 : Undo t 19 : Speed up t 20 : Speed down t 21 : Undo 44 Example

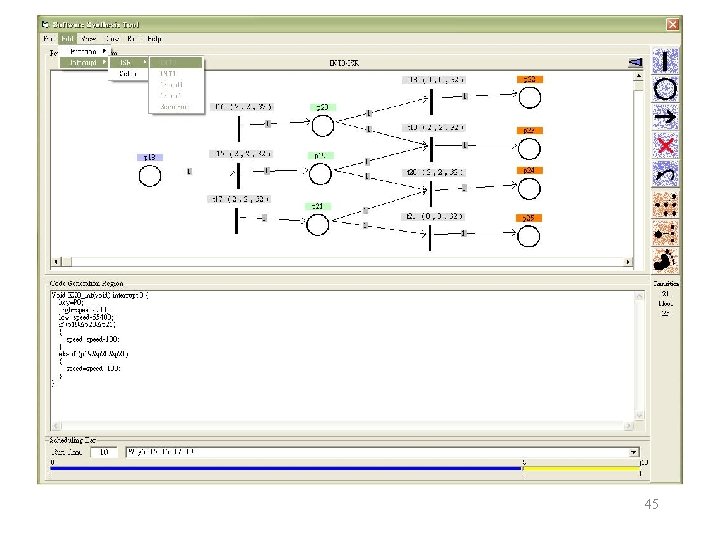

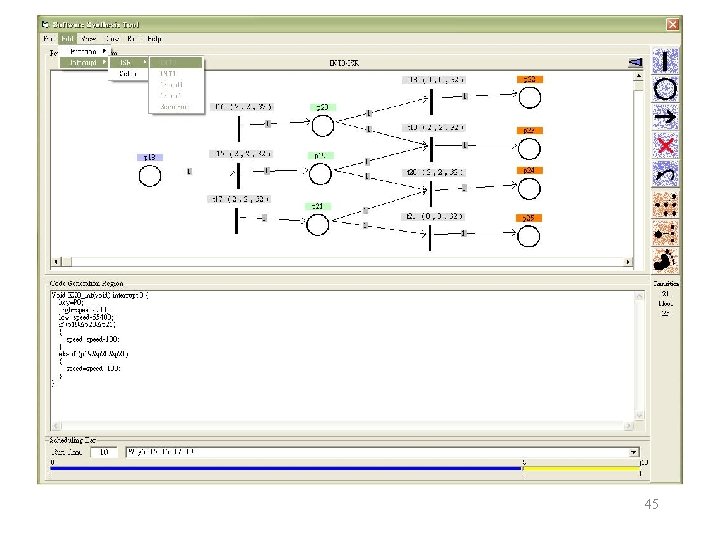

45

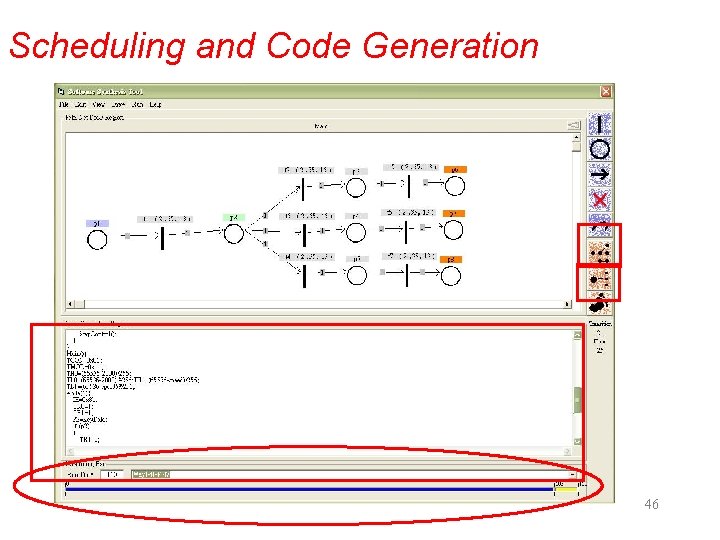

Scheduling and Code Generation 46 Example

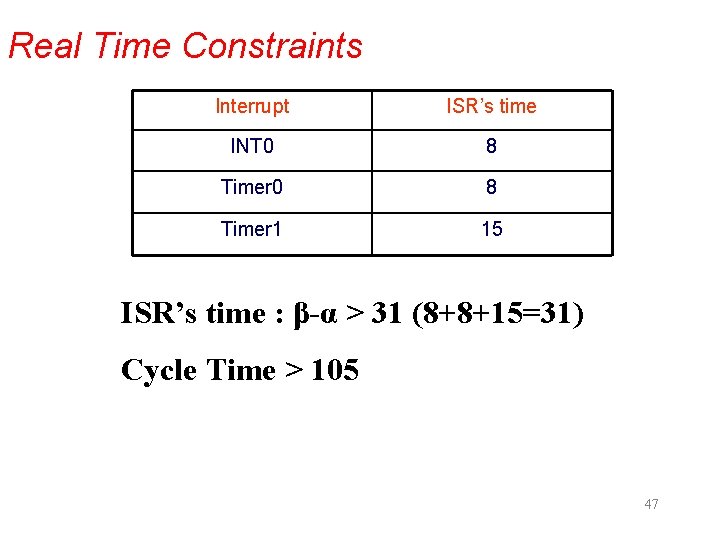

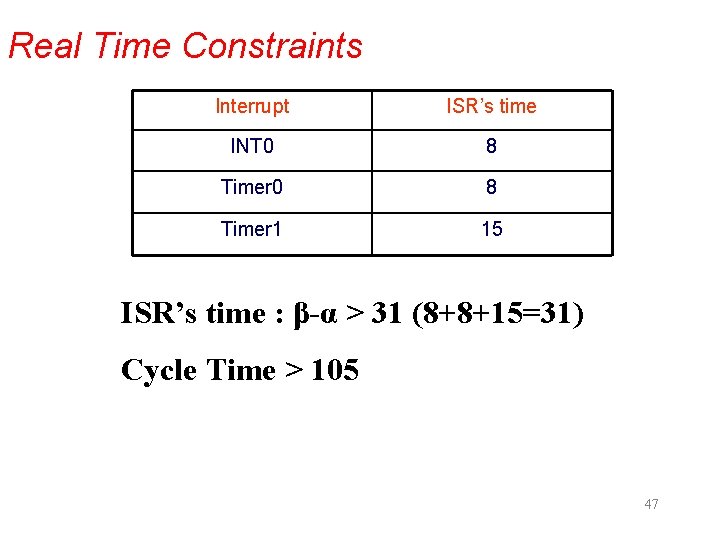

Real Time Constraints Interrupt ISR’s time INT 0 8 Timer 1 15 ISR’s time : β-α > 31 (8+8+15=31) Cycle Time > 105 47 Example

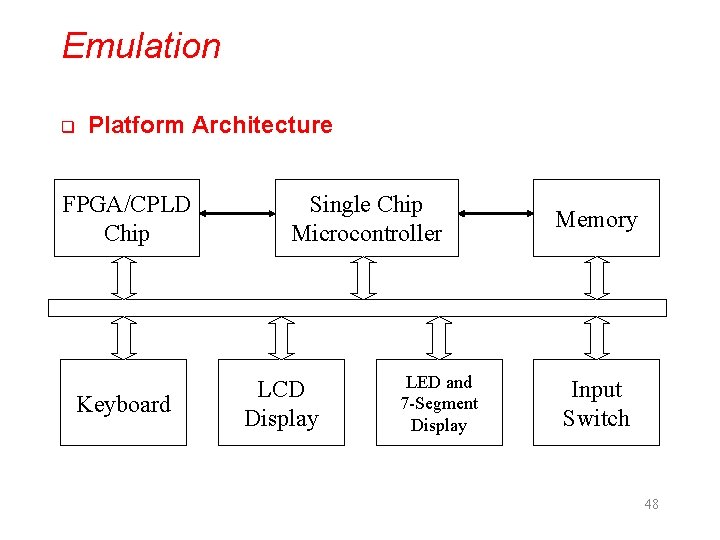

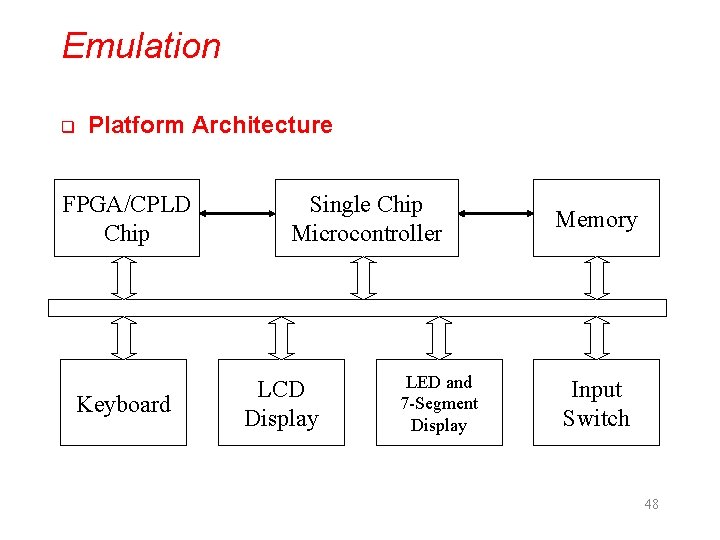

Emulation q Platform Architecture FPGA/CPLD Chip Keyboard Single Chip Microcontroller LCD Display LED and 7 -Segment Display Memory Input Switch 48 Example

Summary Extended system model called “Interrupt Time Petri Net, ITPN” q An Interrupt-Based Quasi-Dynamic Scheduling, IQDS is proposed q Generate a microcontroller (8051) C program code q Graphical user interface make the tool more user-friendly q 49 Conclusion

END 50