Design Codesign of Embedded Systems Other Simulation Techniques

Design & Co-design of Embedded Systems Other Simulation Techniques in System. C Maziar Goudarzi 2005 Design & Co-design of Embedded Systems

Today Program z Advanced Simulation Control z Reactivity in SC_CTHREAD processes z FSM Modeling Techniques 2005 Design & Co-design of Embedded Systems 2

Other Simulation Techniques Advanced Simulation Control 2005 Design & Co-design of Embedded Systems

Special Objects: Clocks z Clocks generate timing signals to synchronize simulation events z No clock-signal is declared y. Instead, an sc_clock object is instantiated z Declaration syntax (old) sc_clock clk_name(“clk_name”, clk_period=1, clk_duty_cycle=0. 5, first_edge_time=0, first_edge_type=true); 2005 Design & Co-design of Embedded Systems 4

Special Objects: Clocks (cont’d) z Declaration syntax (new) sc_clock clk(“clk”, clk_period=1, time_unit=SC_NS); z Example: sc_clock clk 1(“clk 1”, 10, SC_PS); z Values for time_unit argument y SC_FS, SC_PS, SC_NS, SC_US, SC_MS, SC_SEC 2005 Design & Co-design of Embedded Systems 5

Special Objects: Clocks (cont’d) z Multiple clocks are allowed y. Different frequencies y. Different phase relations z Declaration point y. Typically generated at top-level module and passed down to lower-level modules y. The clock object or its signal (i. e. clock_object. signal() ) can be passed down 2005 Design & Co-design of Embedded Systems 6

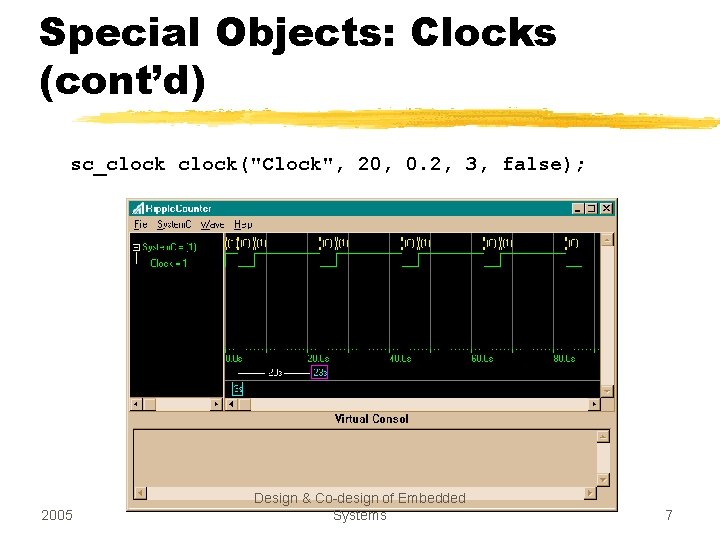

Special Objects: Clocks (cont’d) sc_clock("Clock", 20, 0. 2, 3, false); 2005 Design & Co-design of Embedded Systems 7

Simulation Control Functions z Simulation Control ysc_start(double simulation_duration) ysc_start(double duration, sc_time_unit) x. Use non-positive or no value for duration to continue indefinitely ysc_stop() y. Debugging aid xread/print signal, port, and variable values x. For ports and signals: The printed value is the current value, not the value just written to it 2005 Design & Co-design of Embedded Systems 8

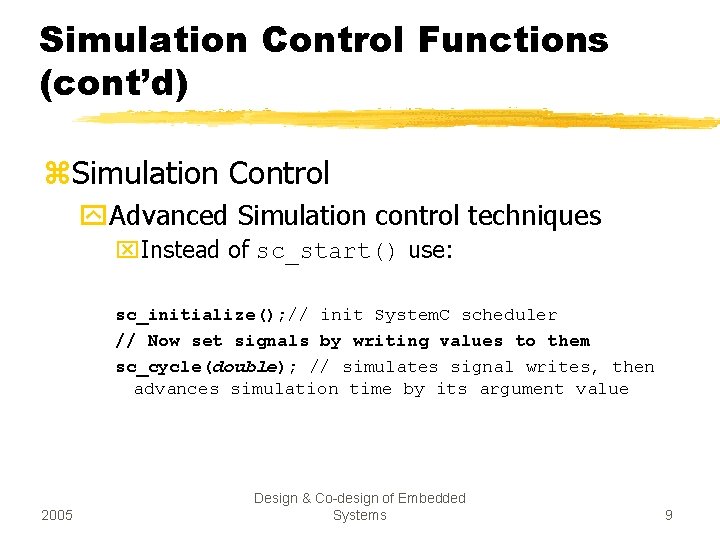

Simulation Control Functions (cont’d) z. Simulation Control y. Advanced Simulation control techniques x. Instead of sc_start() use: sc_initialize(); // init System. C scheduler // Now set signals by writing values to them sc_cycle(double); // simulates signal writes, then advances simulation time by its argument value 2005 Design & Co-design of Embedded Systems 9

![Simulation Control Functions (cont’d) z Example int sc_main(int, char *[]) {. . . // Simulation Control Functions (cont’d) z Example int sc_main(int, char *[]) {. . . //](http://slidetodoc.com/presentation_image_h/36ca0b87d44a075ecccb1b1af39ca213/image-10.jpg)

Simulation Control Functions (cont’d) z Example int sc_main(int, char *[]) {. . . // signal declarations. . . // module instantiations sc_signal<bool> clock; sc_initialize(); for (int i = 0; i <= 10; i++) { clock = 1; sc_cycle(10); clock = 0; sc_cycle(10); } } 2005 Design & Co-design of Embedded Systems 10

![Example 20 5 int sc_main(int, char*[]) { 20 sc_initialize(); // Let the clock run Example 20 5 int sc_main(int, char*[]) { 20 sc_initialize(); // Let the clock run](http://slidetodoc.com/presentation_image_h/36ca0b87d44a075ecccb1b1af39ca213/image-11.jpg)

Example 20 5 int sc_main(int, char*[]) { 20 sc_initialize(); // Let the clock run for 10 cycles for (int i = 0; i <= 10; i++) clock = 1; sc_cycle(10); // Now let the clock run indefinitely clock = 0; for (; ; ){ sc_cycle(10); clock = 1; } sc_cycle(10); // Inject asynchronous reset clock = 0; clock = 1; sc_cycle(10); sc_cycle(5); } reset = 1; } sc_cycle(5); clock = 0; sc_cycle(10); clock = 1; sc_cycle(5); reset = 0; sc_cycle(5); clock = 0; Design & Co-design of Embedded sc_cycle(10); 2005 Systems 11

Other Simulation Techniques Describing FSM in System. C 2005 Design & Co-design of Embedded Systems

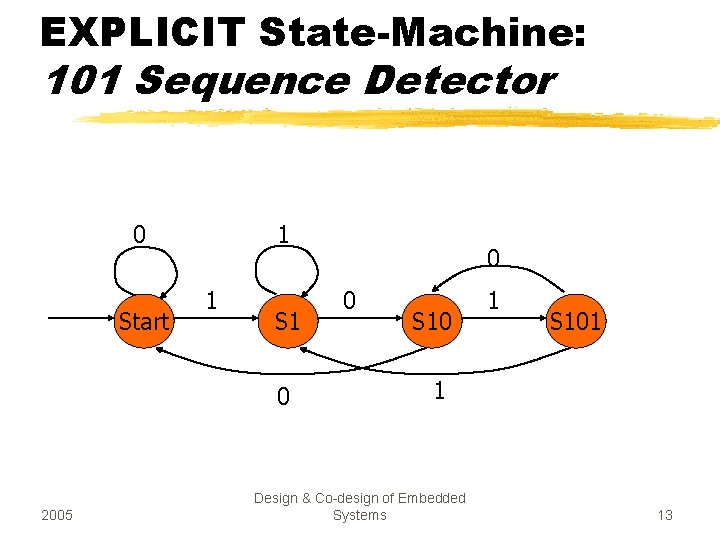

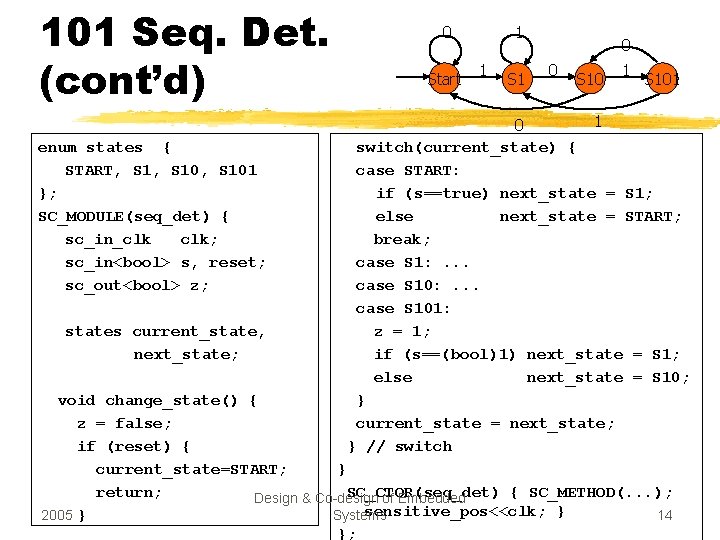

EXPLICIT State-Machine: 101 Sequence Detector 0 Start 1 1 S 1 0 2005 0 0 S 10 1 S 101 1 Design & Co-design of Embedded Systems 13

101 Seq. Det. (cont’d) enum states { START, S 10, S 101 }; SC_MODULE(seq_det) { sc_in_clk clk; sc_in<bool> s, reset; sc_out<bool> z; states current_state, next_state; 0 Start 1 1 S 1 0 0 S 10 1 S 101 1 0 switch(current_state) { case START: if (s==true) next_state = S 1; else next_state = START; break; case S 1: . . . case S 101: z = 1; if (s==(bool)1) next_state = S 1; else next_state = S 10; } current_state = next_state; } // switch void change_state() { z = false; if (reset) { current_state=START; } return; SC_CTOR(seq_det) { SC_METHOD(. . . ); Design & Co-design of Embedded sensitive_pos<<clk; } 2005 } Systems 14 };

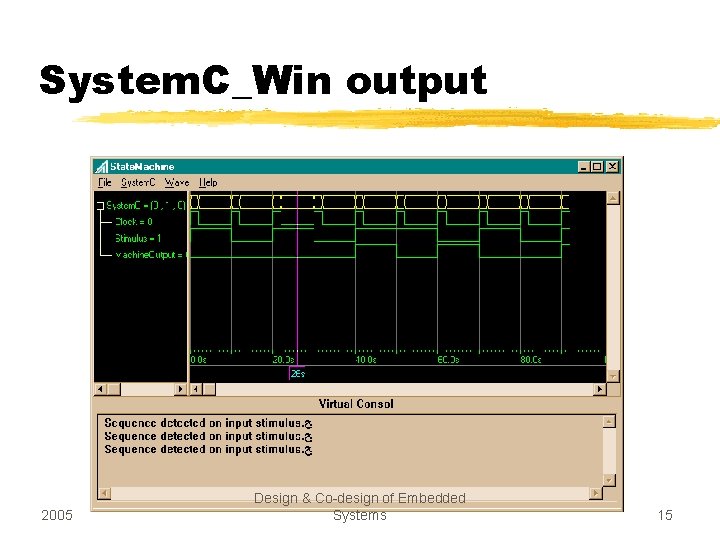

System. C_Win output 2005 Design & Co-design of Embedded Systems 15

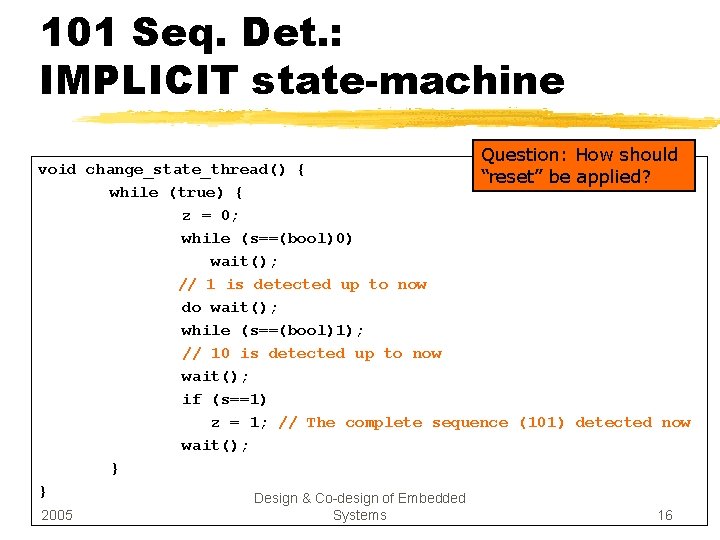

101 Seq. Det. : IMPLICIT state-machine Question: How should void change_state_thread() { “reset” be applied? while (true) { z = 0; while (s==(bool)0) wait(); // 1 is detected up to now do wait(); while (s==(bool)1); // 10 is detected up to now wait(); if (s==1) z = 1; // The complete sequence (101) detected now wait(); } } Design & Co-design of Embedded 2005 Systems 16

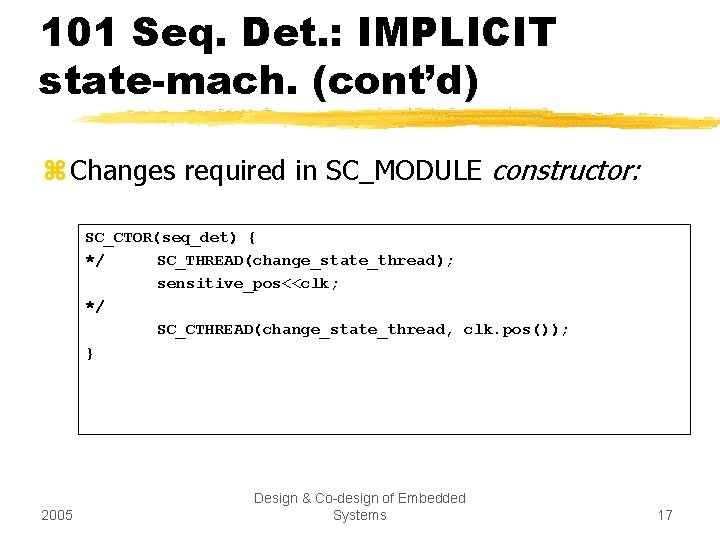

101 Seq. Det. : IMPLICIT state-mach. (cont’d) z Changes required in SC_MODULE constructor: SC_CTOR(seq_det) { */ SC_THREAD(change_state_thread); sensitive_pos<<clk; */ SC_CTHREAD(change_state_thread, clk. pos()); } 2005 Design & Co-design of Embedded Systems 17

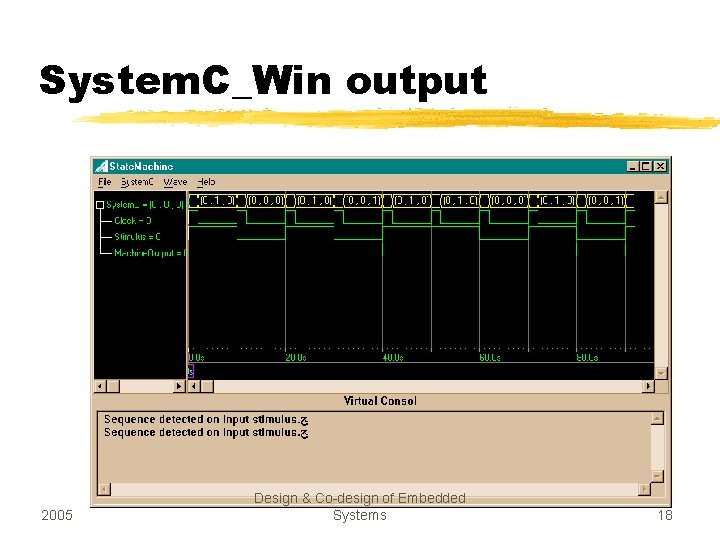

System. C_Win output 2005 Design & Co-design of Embedded Systems 18

Other Simulation Techniques Modeling Reactivity in SC_CTHREAD Processes 2005 Design & Co-design of Embedded Systems

Concept of Reactivity z Property of Reaction to external events y. Inherent in HW => There MUST be some way to model it in any HDL y. Many SW or HW-SW systems are reactive as well: x. Any control systems (Chemical process control, ABS, …) x. Client-Server systems (Database Engines, …) 2005 Design & Co-design of Embedded Systems 20

Concept of Reactivity (cont’d) z Things to consider y. Events to react to x. Type of event (Clock edge, Signal change, some condition on signals or ports, …) y. Style of reaction x. Waiting style • Suspend process until an event comes or some condition holds (i. e. Blocking wait) x. Watching style • Do not suspend. But always WATCH if some condition holds. Then, react accordingly: e. g. Jump to a certain routine, or point of a routine. (Non-blocking wait) 2005 Design & Co-design of Embedded Systems 21

Reactivity Facilities in System. C z Events to react to y. Sensitivity lists in SC_METHOD, SC_THREAD, and clock edge in SC_CTHREAD. x. Sensitivity to any event on a signal: sensitive data member of SC_MODULE x. Sensitivity to positive edge of a signal: sensitive_pos data member of SC_MODULE x. Sensitivity to negative edge of a signal: sensitive_neg data member of SC_MODULE y. Special case of infinite loop processes (SC_THREAD, SC_CTHREAD) x. Loop re-initialization, Wait for Signal condition Design & Co-design of Embedded 2005 Systems 22

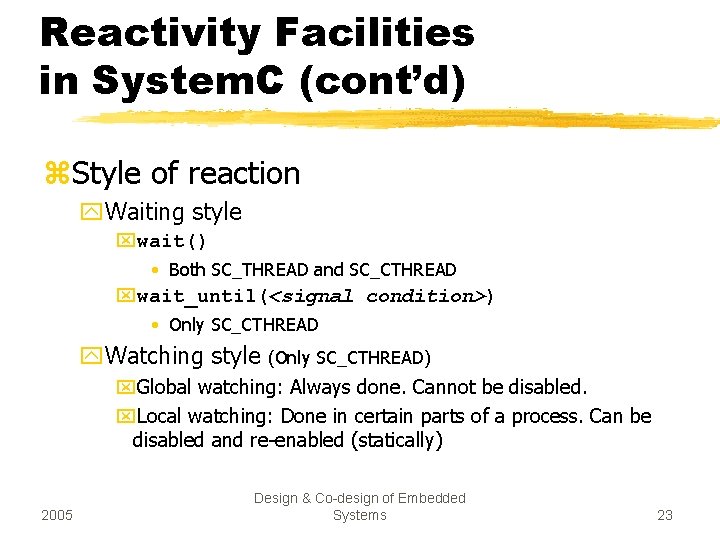

Reactivity Facilities in System. C (cont’d) z. Style of reaction y. Waiting style xwait() • Both SC_THREAD and SC_CTHREAD xwait_until(<signal condition>) • Only SC_CTHREAD y. Watching style (Only SC_CTHREAD) x. Global watching: Always done. Cannot be disabled. x. Local watching: Done in certain parts of a process. Can be disabled and re-enabled (statically) 2005 Design & Co-design of Embedded Systems 23

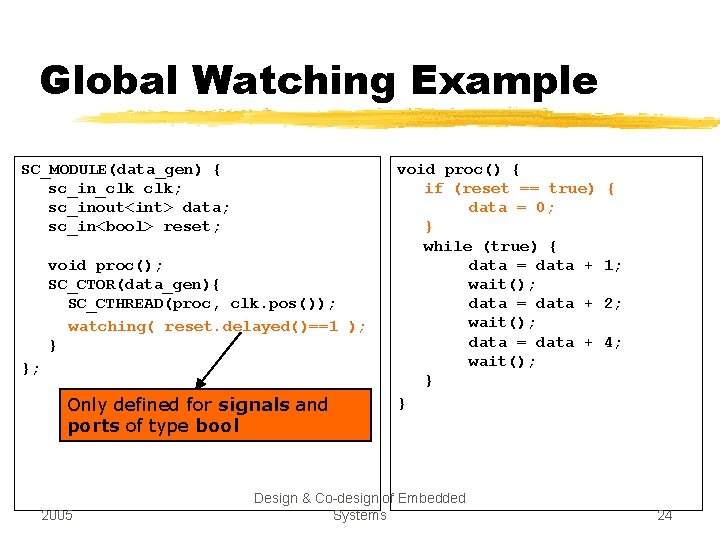

Global Watching Example SC_MODULE(data_gen) { sc_in_clk clk; sc_inout<int> data; sc_in<bool> reset; void proc(); SC_CTOR(data_gen){ SC_CTHREAD(proc, clk. pos()); watching( reset. delayed()==1 ); } }; Only defined for signals and ports of type bool 2005 void proc() { if (reset == true) data = 0; } while (true) { data = data + wait(); } } Design & Co-design of Embedded Systems { 1; 2; 4; 24

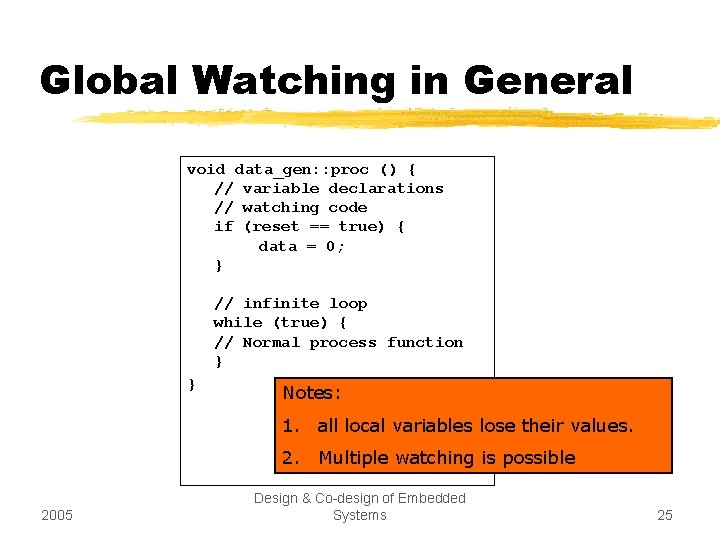

Global Watching in General void data_gen: : proc () { // variable declarations // watching code if (reset == true) { data = 0; } // infinite loop while (true) { // Normal process function } } Notes: 1. all local variables lose their values. 2. Multiple watching is possible 2005 Design & Co-design of Embedded Systems 25

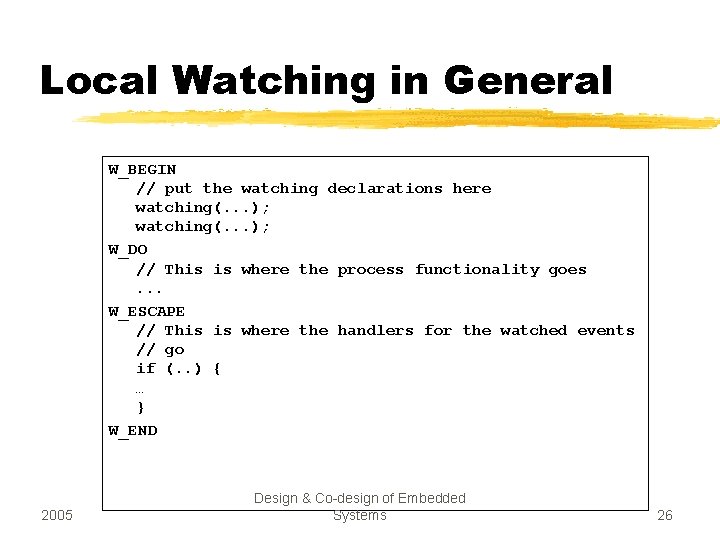

Local Watching in General W_BEGIN // put the watching declarations here watching(. . . ); W_DO // This is where the process functionality goes. . . W_ESCAPE // This is where the handlers for the watched events // go if (. . ) { … } W_END 2005 Design & Co-design of Embedded Systems 26

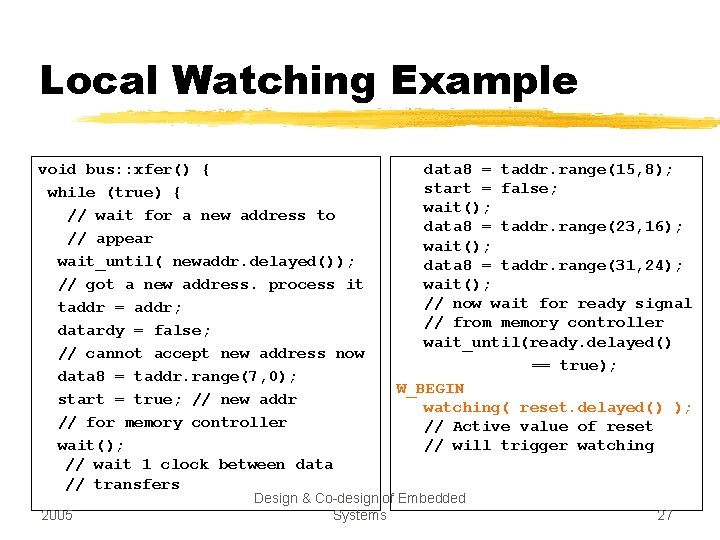

Local Watching Example void bus: : xfer() { while (true) { // wait for a new address to // appear wait_until( newaddr. delayed()); // got a new address. process it taddr = addr; datardy = false; // cannot accept new address now data 8 = taddr. range(7, 0); start = true; // new addr // for memory controller wait(); // wait 1 clock between data // transfers 2005 data 8 = taddr. range(15, 8); start = false; wait(); data 8 = taddr. range(23, 16); wait(); data 8 = taddr. range(31, 24); wait(); // now wait for ready signal // from memory controller wait_until(ready. delayed() == true); W_BEGIN watching( reset. delayed() ); // Active value of reset // will trigger watching Design & Co-design of Embedded Systems 27

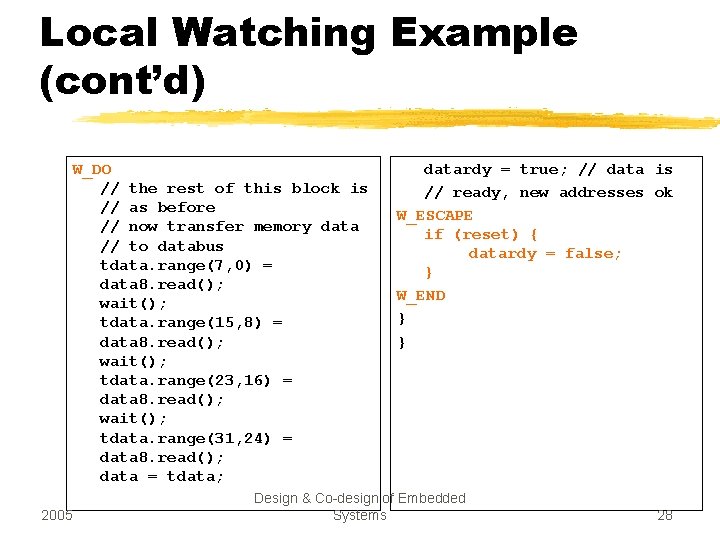

Local Watching Example (cont’d) W_DO // the rest of this block is // as before // now transfer memory data // to databus tdata. range(7, 0) = data 8. read(); wait(); tdata. range(15, 8) = data 8. read(); wait(); tdata. range(23, 16) = data 8. read(); wait(); tdata. range(31, 24) = data 8. read(); data = tdata; 2005 datardy = true; // data is // ready, new addresses ok W_ESCAPE if (reset) { datardy = false; } W_END } } Design & Co-design of Embedded Systems 28

watching statements (cont’d) z. Final notes y. Local watching x. All events have the same priority. Use nested watches to change this. y. The watched signals are only sampled at the active edges of the SC_CTHREAD clock y. Global watching has priority over local watching 2005 Design & Co-design of Embedded Systems 29

Today Summary z. Advanced Simulation Control Techniques z. Local and Global Watching z. Self-study y. Chapters 7, 8, and 9 of “A System. C Primer” book 2005 Design & Co-design of Embedded Systems 30

Other Notes z. Project Progress Report 1 y. Today is the (postponed!) deadline y 2 -3 pages, covering • List of your collected material • Summary of what you’ve done + demo of the C++ app. • Your plan for next phases and role of each person 2005 Design & Co-design of Embedded Systems 31

- Slides: 31