Design Codesign of Embedded Systems Data Types in

Design & Co-design of Embedded Systems Data Types in System. C Part 2 Maziar Goudarzi 2005 Design & Co-design of Embedded Systems

Today Program z. Tracing variable values (as waveforms) in System. C z. User-defined data types 2005 Design & Co-design of Embedded Systems 2

Points Remained from Last Session z sc_logic AND table 2005 & 0 1 X Z 0 0 0 1 X X X 0 X X X Z 0 X X X Design & Co-design of Embedded Systems 3

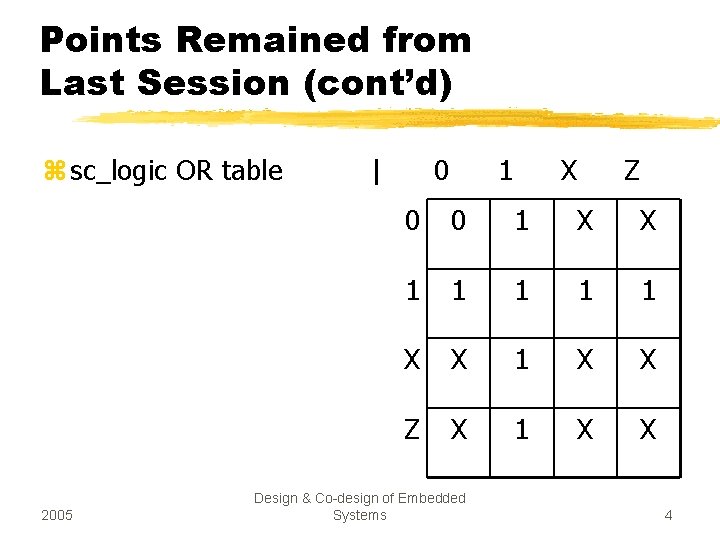

Points Remained from Last Session (cont’d) z sc_logic OR table 2005 | 0 1 X Z 0 0 1 X X 1 1 1 X X Z X 1 X X Design & Co-design of Embedded Systems 4

Points Remained from Last Session (cont’d) z Conversion between signed and unsigned integers of different sizes y. Conversion from wider to narrower variable x. Allowed, but clearly risks losing valuable bits x. Just least significant bits are copied y. Conversion from narrower to wider variable x. Converting from unsigned to signed • Bits are just copied. No sign-extension is performed. x. Converting from signed to unsigned • Bits are just copied. Sign-extension is performed. y. Conversion with the same width x. Bits are just copied. 2005 Design & Co-design of Embedded Systems 5

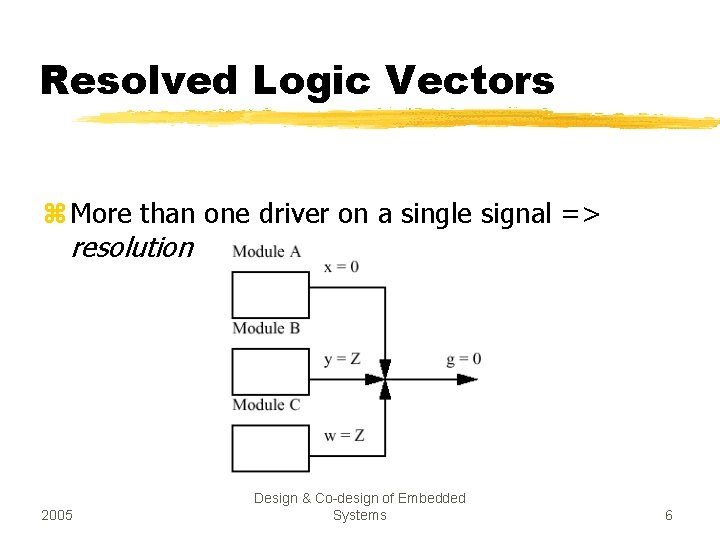

Resolved Logic Vectors z More than one driver on a single signal => resolution is required 2005 Design & Co-design of Embedded Systems 6

Resolved Logic Vectors (cont’d) 2005 Design & Co-design of Embedded Systems 7

Resolved Logic Vectors (cont’d) z Syntax for resolved-logic ports sc_in_rv<n> port_name; sc_out_rv<n> port_name; sc_inout_rv<n> port_name; z Notes y. Imposes extra simulation overhead y. Virtually no limit on the vector size (n) z Corresponding resolved logic vector signal sc_signal_rv<n> signal_name; y. Used to connect resolved logic ports 2005 Design & Co-design of Embedded Systems 8

Tracing Variable Values z. Tracing Waveforms y. Creating The Trace File y. Tracing Scalar Variable and Signals y. Tracing Variable and Signal Arrays 2005 Design & Co-design of Embedded Systems 9

Tracing Variable Values (cont’d) z Supported waveformats y. VCD (Value Change Dump) y. ASCII WIF (Wave Intermediate Format) y. ISDB (Integrated Signal Data. Base) z Waveform viewers y. VCD x. Commercial tools: Model. Sim® x. Free tools: • GTKWave http: //www. cs. man. ac. uk/amulet/tools/gtkwave/ • System. C_Win http: //www. geocities. com/systemc_win/ 2005 Design & Co-design of Embedded Systems 10

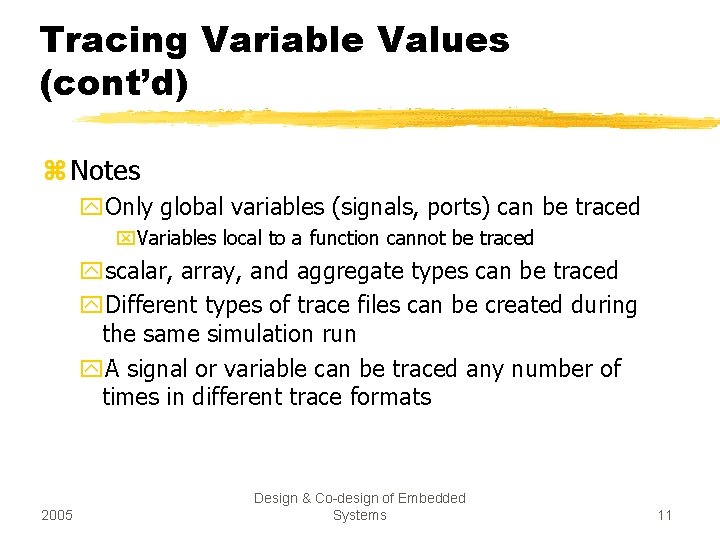

Tracing Variable Values (cont’d) z Notes y. Only global variables (signals, ports) can be traced x. Variables local to a function cannot be traced yscalar, array, and aggregate types can be traced y. Different types of trace files can be created during the same simulation run y. A signal or variable can be traced any number of times in different trace formats 2005 Design & Co-design of Embedded Systems 11

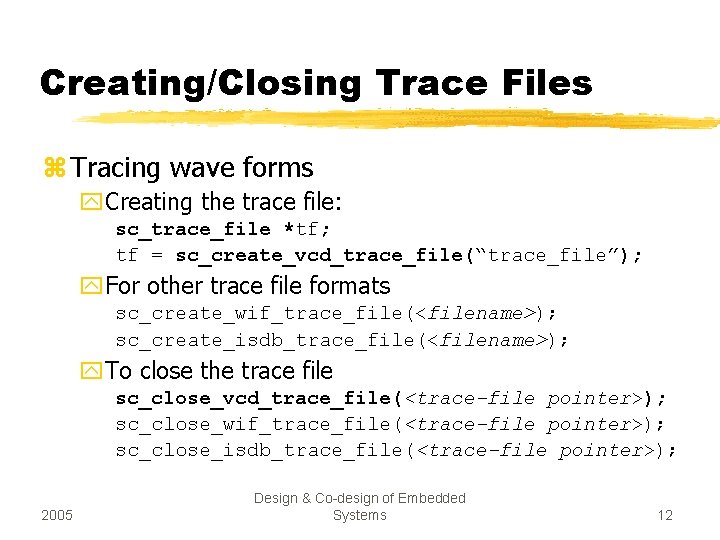

Creating/Closing Trace Files z Tracing wave forms y. Creating the trace file: sc_trace_file *tf; tf = sc_create_vcd_trace_file(“trace_file”); y. For other trace file formats sc_create_wif_trace_file(<filename>); sc_create_isdb_trace_file(<filename>); y. To close the trace file sc_close_vcd_trace_file(<trace-file pointer>); sc_close_wif_trace_file(<trace-file pointer>); sc_close_isdb_trace_file(<trace-file pointer>); 2005 Design & Co-design of Embedded Systems 12

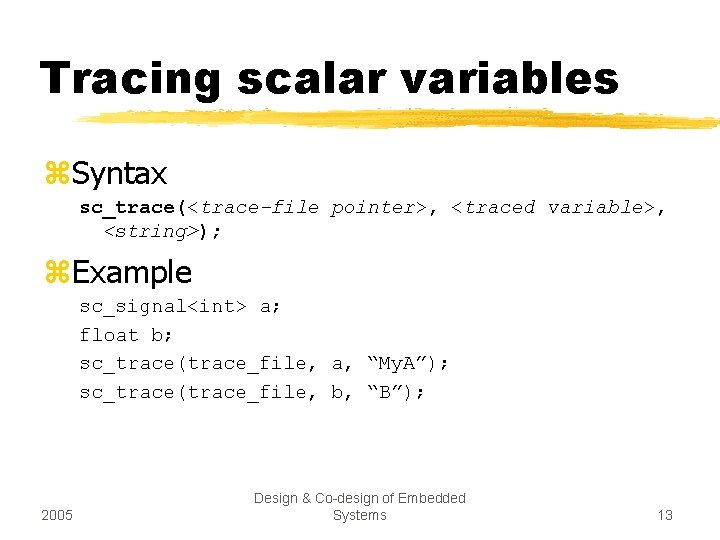

Tracing scalar variables z. Syntax sc_trace(<trace-file pointer>, <traced variable>, <string>); z. Example sc_signal<int> a; float b; sc_trace(trace_file, a, “My. A”); sc_trace(trace_file, b, “B”); 2005 Design & Co-design of Embedded Systems 13

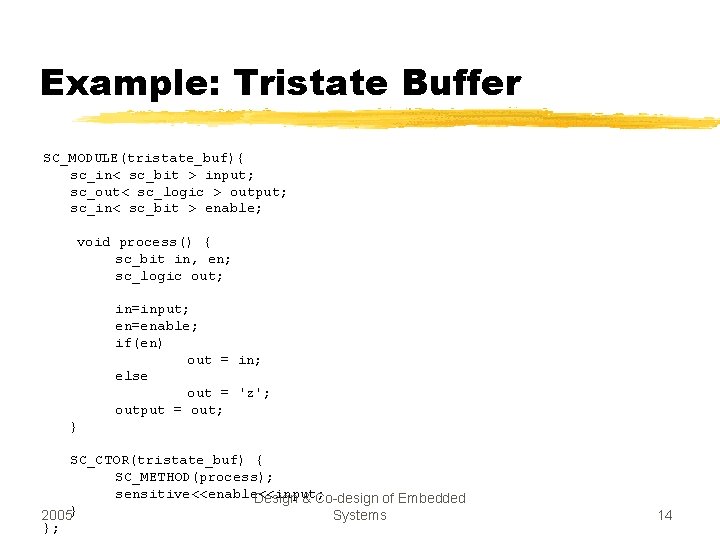

Example: Tristate Buffer SC_MODULE(tristate_buf){ sc_in< sc_bit > input; sc_out< sc_logic > output; sc_in< sc_bit > enable; void process() { sc_bit in, en; sc_logic out; in=input; en=enable; if(en) out = in; else out = 'z'; output = out; } SC_CTOR(tristate_buf) { SC_METHOD(process); sensitive<<enable<<input; Design & Co-design of Embedded } 2005 Systems }; 14

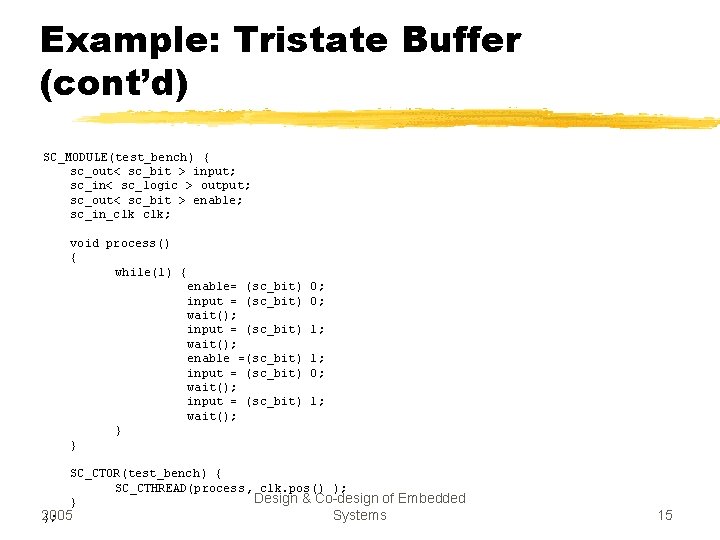

Example: Tristate Buffer (cont’d) SC_MODULE(test_bench) { sc_out< sc_bit > input; sc_in< sc_logic > output; sc_out< sc_bit > enable; sc_in_clk clk; void process() { while(1) { enable= (sc_bit) input = (sc_bit) wait(); enable =(sc_bit) input = (sc_bit) wait(); 0; 0; 1; 1; 0; 1; } } SC_CTOR(test_bench) { SC_CTHREAD(process, clk. pos() ); Design & Co-design of Embedded } 2005 }; Systems 15

![Example: Tristate Buffer (cont’d) int sc_main(int, char*[]) { tristate_buf buf("tristate. Buffer"); test_bench tb("test. Bench"); Example: Tristate Buffer (cont’d) int sc_main(int, char*[]) { tristate_buf buf("tristate. Buffer"); test_bench tb("test. Bench");](http://slidetodoc.com/presentation_image/f581582674cdea7c169575887e7d2574/image-16.jpg)

Example: Tristate Buffer (cont’d) int sc_main(int, char*[]) { tristate_buf buf("tristate. Buffer"); test_bench tb("test. Bench"); sc_signal< sc_bit > in, en; sc_signal< sc_logic > out; sc_clock clk; buf(in, out, en); tb(in, out, en, clk); sc_trace_file *tf; tf = sc_create_vcd_trace_file("Buffer. Trace. File "); // file extension defaults to ". vcd" sc_trace(tf, in, "input signal"); sc_trace(tf, en, "enable signal"); sc_trace(tf, out, "output signal"); sc_start(10); sc_close_vcd_trace_file(tf ); return 0; } 2005 Design & Co-design of Embedded Systems 16

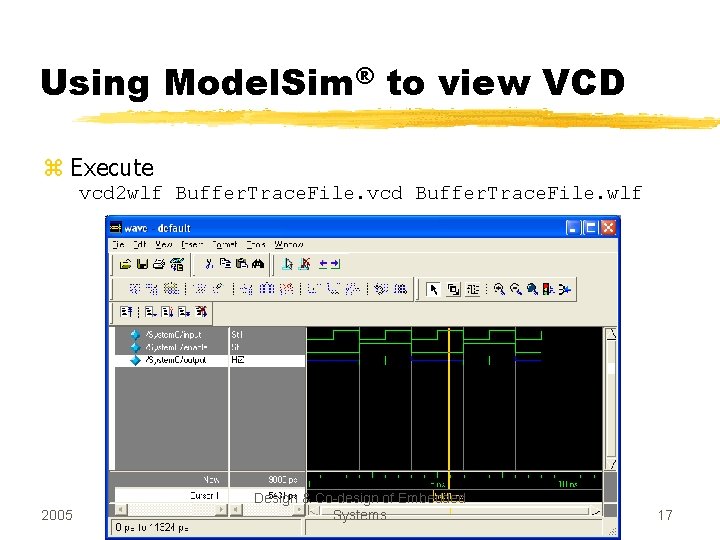

Using Model. Sim® to view VCD z Execute vcd 2 wlf Buffer. Trace. File. vcd Buffer. Trace. File. wlf 2005 Design & Co-design of Embedded Systems 17

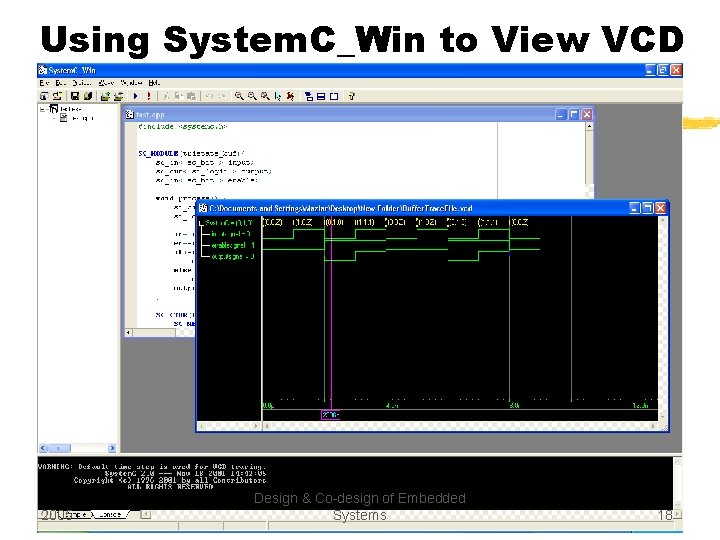

Using System. C_Win to View VCD 2005 Design & Co-design of Embedded Systems 18

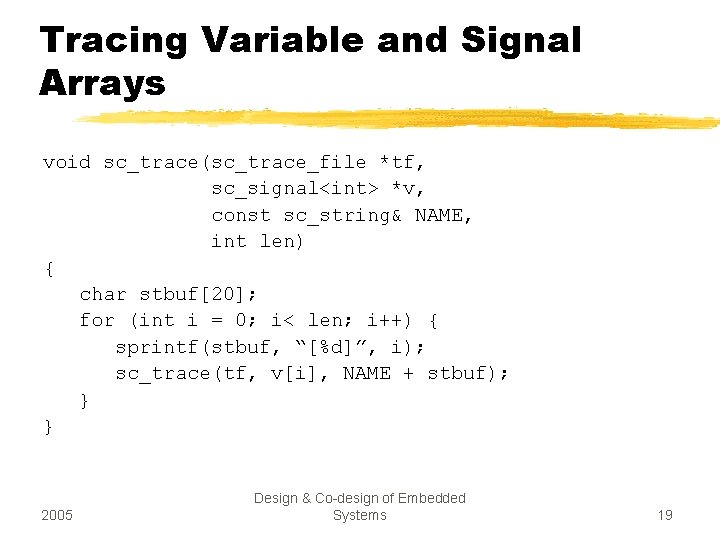

Tracing Variable and Signal Arrays void sc_trace(sc_trace_file *tf, sc_signal<int> *v, const sc_string& NAME, int len) { char stbuf[20]; for (int i = 0; i< len; i++) { sprintf(stbuf, “[%d]”, i); sc_trace(tf, v[i], NAME + stbuf); } } 2005 Design & Co-design of Embedded Systems 19

Data Types in System. C User-Defined Data Types 2005 Design & Co-design of Embedded Systems

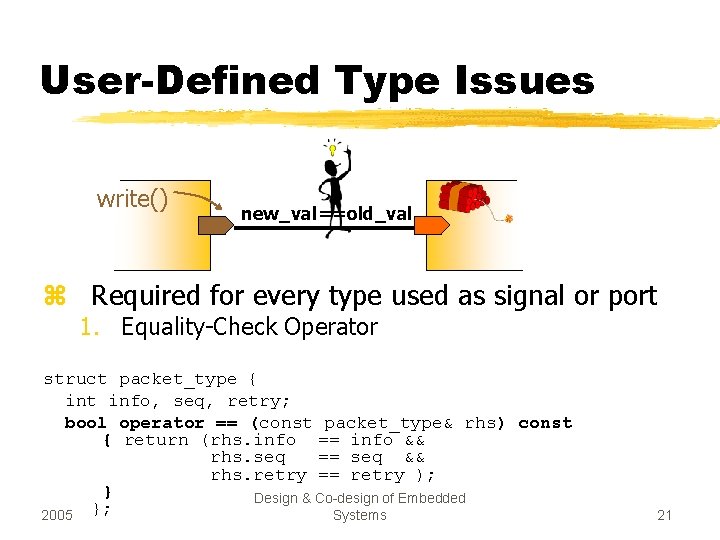

User-Defined Type Issues write() new_val==old_val z Required for every type used as signal or port 1. Equality-Check Operator struct packet_type { int info, seq, retry; bool operator == (const packet_type& rhs) const { return (rhs. info == info && rhs. seq == seq && rhs. retry == retry ); } Design & Co-design of Embedded }; 2005 Systems 21

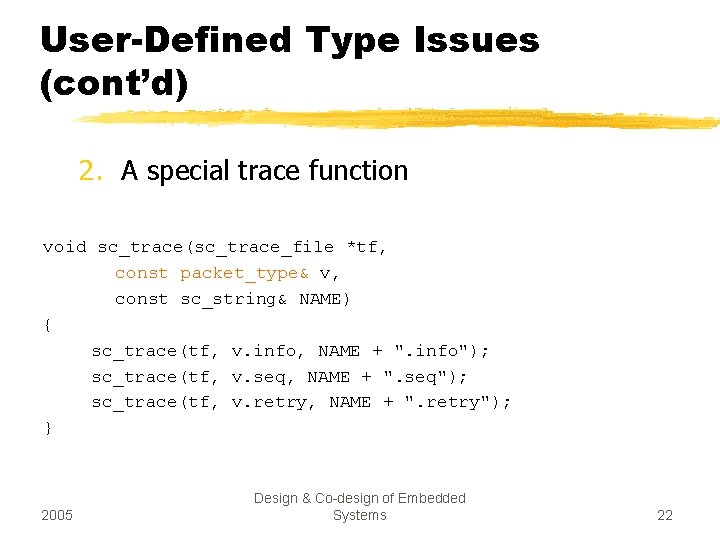

User-Defined Type Issues (cont’d) 2. A special trace function void sc_trace(sc_trace_file *tf, const packet_type& v, const sc_string& NAME) { sc_trace(tf, v. info, NAME + ". info"); sc_trace(tf, v. seq, NAME + ". seq"); sc_trace(tf, v. retry, NAME + ". retry"); } 2005 Design & Co-design of Embedded Systems 22

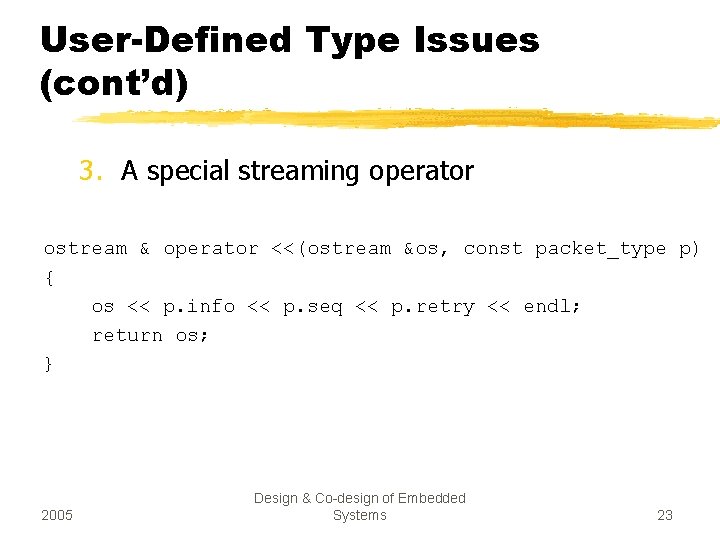

User-Defined Type Issues (cont’d) 3. A special streaming operator ostream & operator <<(ostream &os, const packet_type p) { os << p. info << p. seq << p. retry << endl; return os; } 2005 Design & Co-design of Embedded Systems 23

What we learned today z Rest of major data types in System. C z Generating waveforms in System. C y. Very much useful for validation purposes z User-Defined Data Types y. Required operators y. Tracing Issues 2005 Design & Co-design of Embedded Systems 24

Quiz 1 z. Design a 4 -bit Shift-register with two controls: enable and shift y. If enable=0, output is high-impedance y. If enable=1 and shift=1, shift (one bit) the contents of the register to right, and readin one data bit from din 2005 Design & Co-design of Embedded Systems 25

- Slides: 25