Debounce Slide Switches and Push Button Switches Slide

Debounce

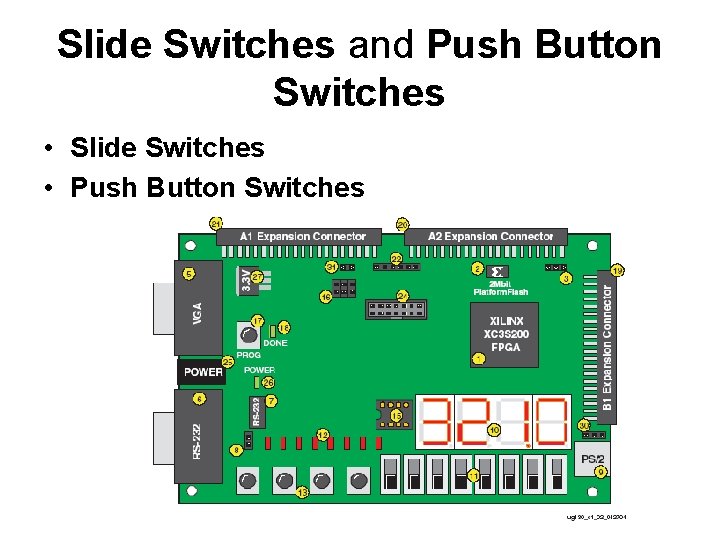

Slide Switches and Push Button Switches • Slide Switches • Push Button Switches

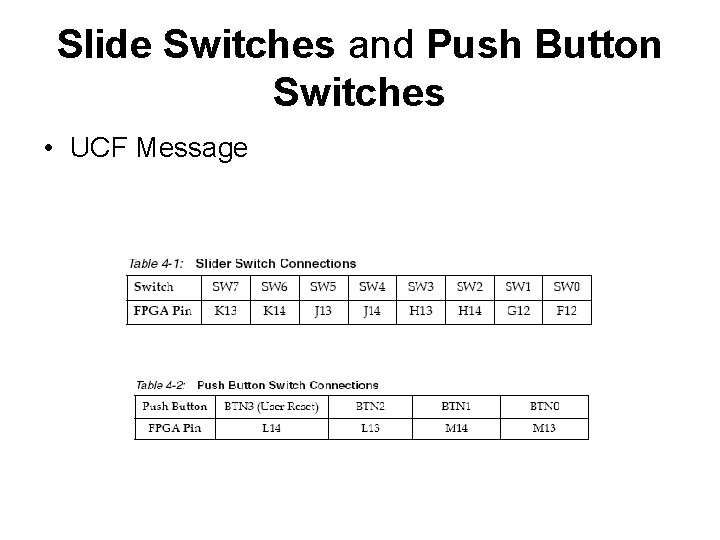

Slide Switches and Push Button Switches • UCF Message

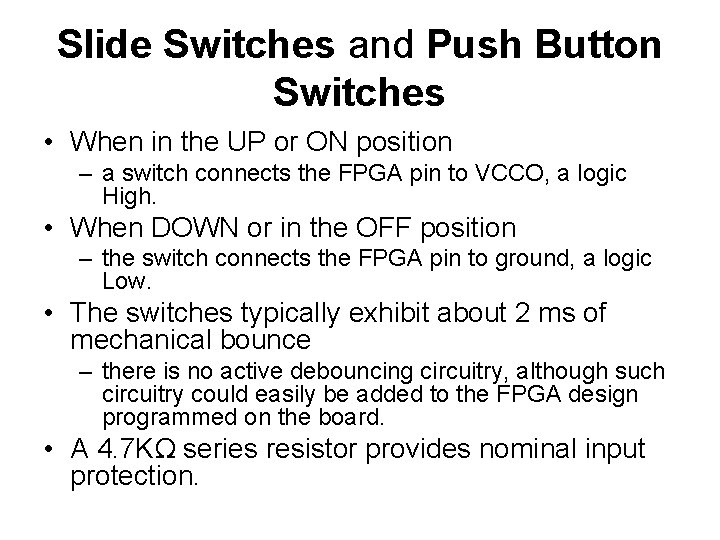

Slide Switches and Push Button Switches • When in the UP or ON position – a switch connects the FPGA pin to VCCO, a logic High. • When DOWN or in the OFF position – the switch connects the FPGA pin to ground, a logic Low. • The switches typically exhibit about 2 ms of mechanical bounce – there is no active debouncing circuitry, although such circuitry could easily be added to the FPGA design programmed on the board. • A 4. 7 KΩ series resistor provides nominal input protection.

Slide Switches and Push Button Switches • Pressing a push button generates a logic High on the associated FPGA pin. • There is no active debouncing circuitry on the push button.

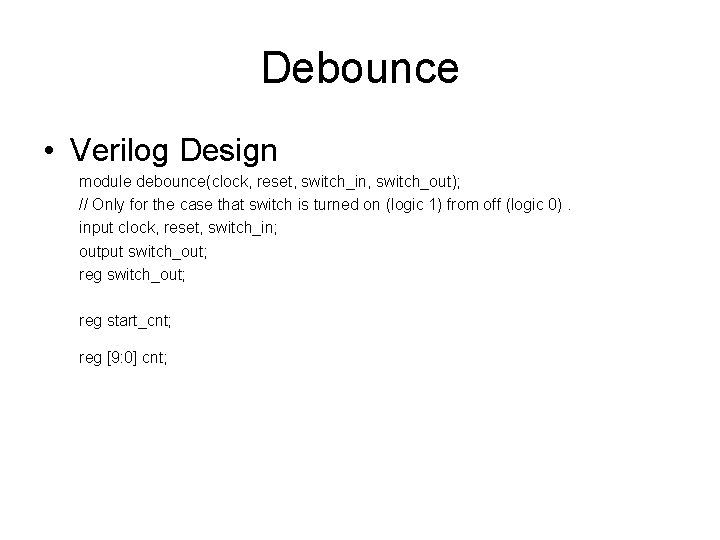

Debounce • Verilog Design module debounce(clock, reset, switch_in, switch_out); // Only for the case that switch is turned on (logic 1) from off (logic 0). input clock, reset, switch_in; output switch_out; reg start_cnt; reg [9: 0] cnt;

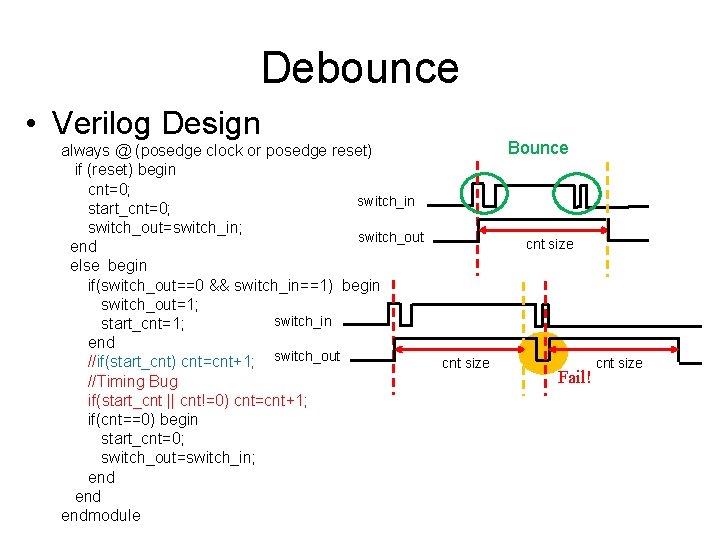

Debounce • Verilog Design always @ (posedge clock or posedge reset) if (reset) begin cnt=0; switch_in start_cnt=0; switch_out=switch_in; switch_out end else begin if(switch_out==0 && switch_in==1) begin switch_out=1; switch_in start_cnt=1; end //if(start_cnt) cnt=cnt+1; switch_out //Timing Bug if(start_cnt || cnt!=0) cnt=cnt+1; if(cnt==0) begin start_cnt=0; switch_out=switch_in; end endmodule Bounce cnt size Fail! cnt size

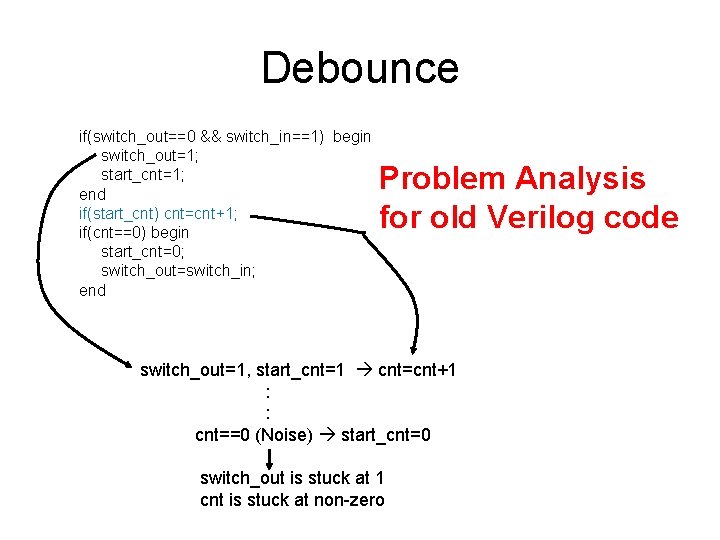

Debounce if(switch_out==0 && switch_in==1) begin switch_out=1; start_cnt=1; end if(start_cnt) cnt=cnt+1; if(cnt==0) begin start_cnt=0; switch_out=switch_in; end Problem Analysis for old Verilog code switch_out=1, start_cnt=1 cnt=cnt+1 : : cnt==0 (Noise) start_cnt=0 switch_out is stuck at 1 cnt is stuck at non-zero

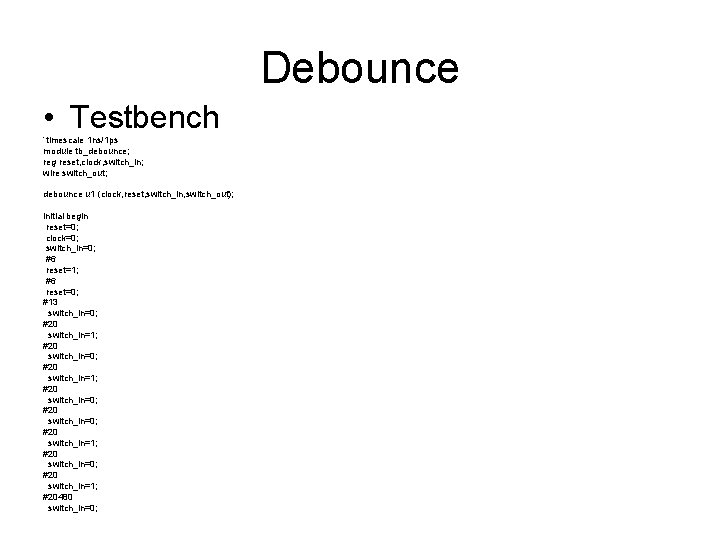

Debounce • Testbench `timescale 1 ns/1 ps module tb_debounce; reg reset, clock, switch_in; wire switch_out; debounce u 1 (clock, reset, switch_in, switch_out); initial begin reset=0; clock=0; switch_in=0; #6 reset=1; #6 reset=0; #13 switch_in=0; #20 switch_in=1; #20 switch_in=0; #20 switch_in=1; #20480 switch_in=0;

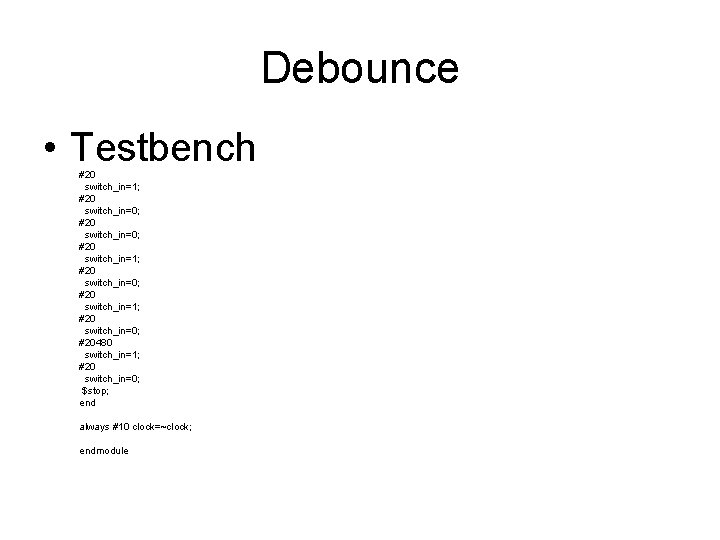

Debounce • Testbench #20 switch_in=1; #20 switch_in=0; #20480 switch_in=1; #20 switch_in=0; $stop; end always #10 clock=~clock; endmodule

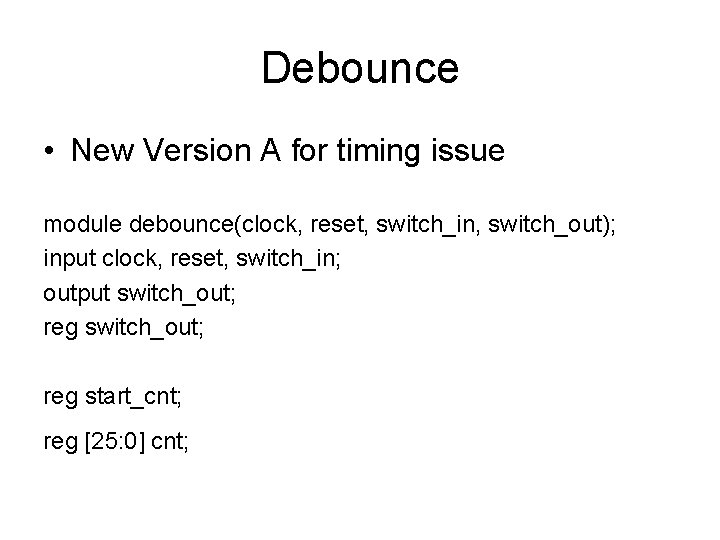

Debounce • New Version A for timing issue module debounce(clock, reset, switch_in, switch_out); input clock, reset, switch_in; output switch_out; reg start_cnt; reg [25: 0] cnt;

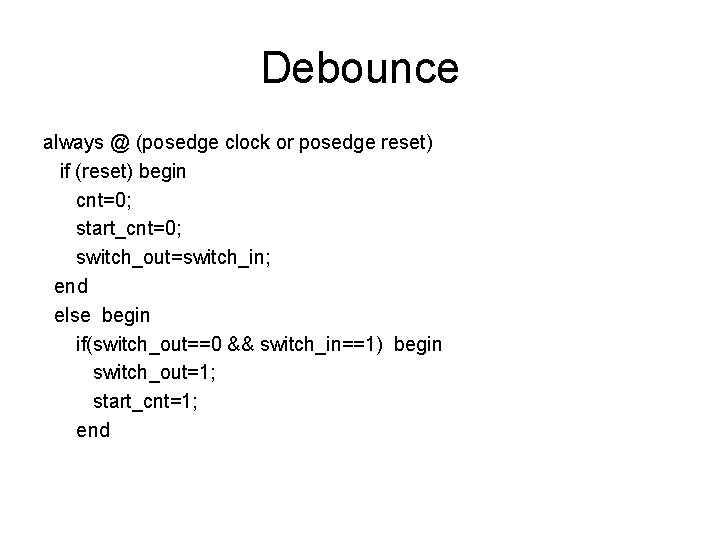

Debounce always @ (posedge clock or posedge reset) if (reset) begin cnt=0; start_cnt=0; switch_out=switch_in; end else begin if(switch_out==0 && switch_in==1) begin switch_out=1; start_cnt=1; end

![Debounce if(start_cnt) cnt=cnt+1; if(cnt[25]==1) begin //Reducing Computation Delay cnt=0; start_cnt=0; switch_out=switch_in; end endmodule Debounce if(start_cnt) cnt=cnt+1; if(cnt[25]==1) begin //Reducing Computation Delay cnt=0; start_cnt=0; switch_out=switch_in; end endmodule](http://slidetodoc.com/presentation_image_h/925312a1bce93c2d270e821f2a363522/image-13.jpg)

Debounce if(start_cnt) cnt=cnt+1; if(cnt[25]==1) begin //Reducing Computation Delay cnt=0; start_cnt=0; switch_out=switch_in; end endmodule

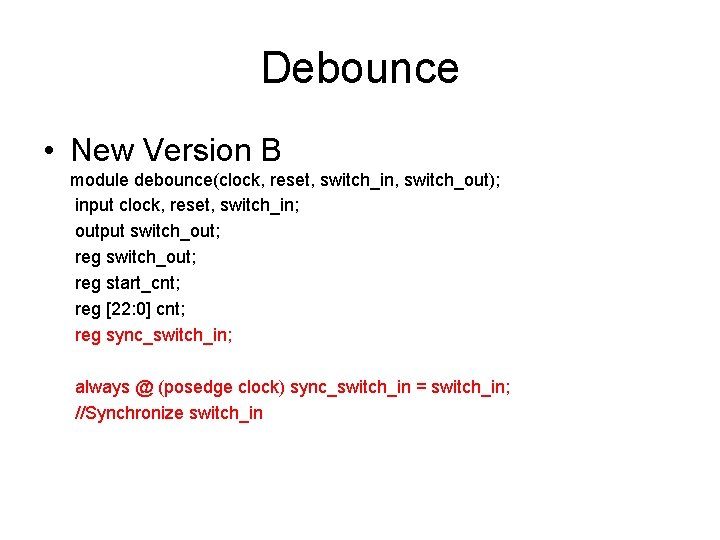

Debounce • New Version B module debounce(clock, reset, switch_in, switch_out); input clock, reset, switch_in; output switch_out; reg start_cnt; reg [22: 0] cnt; reg sync_switch_in; always @ (posedge clock) sync_switch_in = switch_in; //Synchronize switch_in

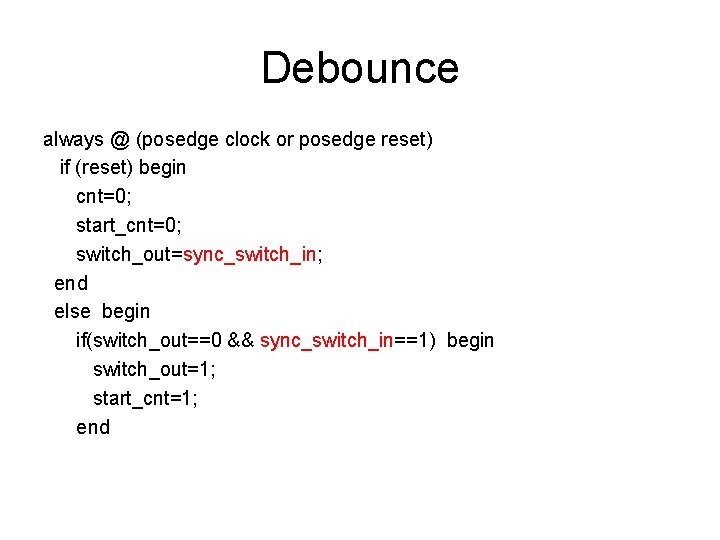

Debounce always @ (posedge clock or posedge reset) if (reset) begin cnt=0; start_cnt=0; switch_out=sync_switch_in; end else begin if(switch_out==0 && sync_switch_in==1) begin switch_out=1; start_cnt=1; end

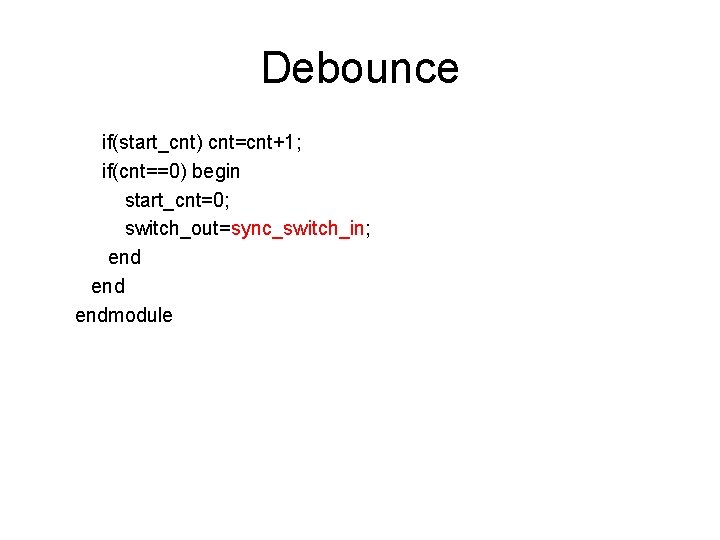

Debounce if(start_cnt) cnt=cnt+1; if(cnt==0) begin start_cnt=0; switch_out=sync_switch_in; end endmodule

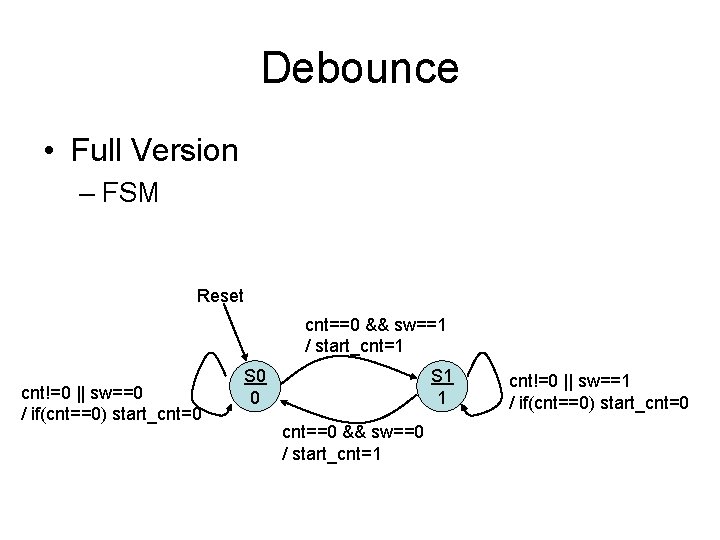

Debounce • Full Version – FSM Reset cnt==0 && sw==1 / start_cnt=1 cnt!=0 || sw==0 / if(cnt==0) start_cnt=0 S 0 0 S 1 1 cnt==0 && sw==0 / start_cnt=1 cnt!=0 || sw==1 / if(cnt==0) start_cnt=0

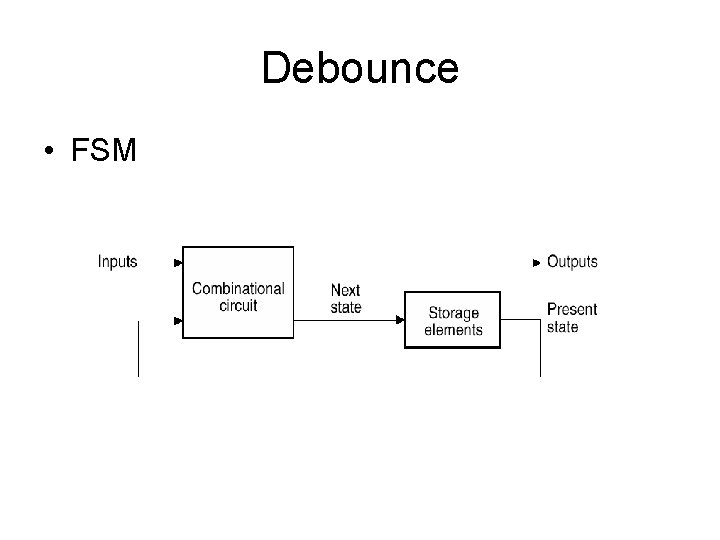

Debounce • FSM

FSM (not for debounce) • FSM module seq_rec_v(CLK, RESET, X, Z); input CLK, RESET, X; output Z; reg [1: 0] state, next_state; parameter A = 2'b 00, B = 2'b 01, C = 2 'b 10, D = 2'b 11;

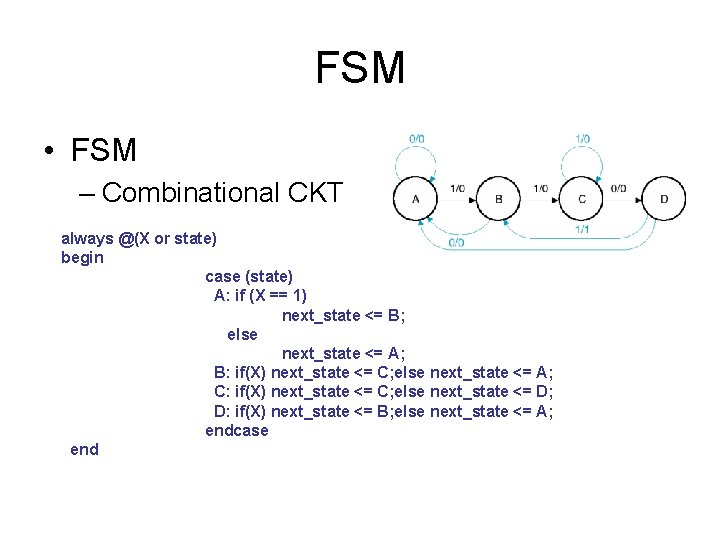

FSM • FSM – Combinational CKT always @(X or state) begin case (state) A: if (X == 1) next_state <= B; else next_state <= A; B: if(X) next_state <= C; else next_state <= A; C: if(X) next_state <= C; else next_state <= D; D: if(X) next_state <= B; else next_state <= A; endcase end

FSM • FSM – F/Fs always @(posedge CLK or posedge RESET) begin if (RESET == 1) state <= A; else state <= next_state; end

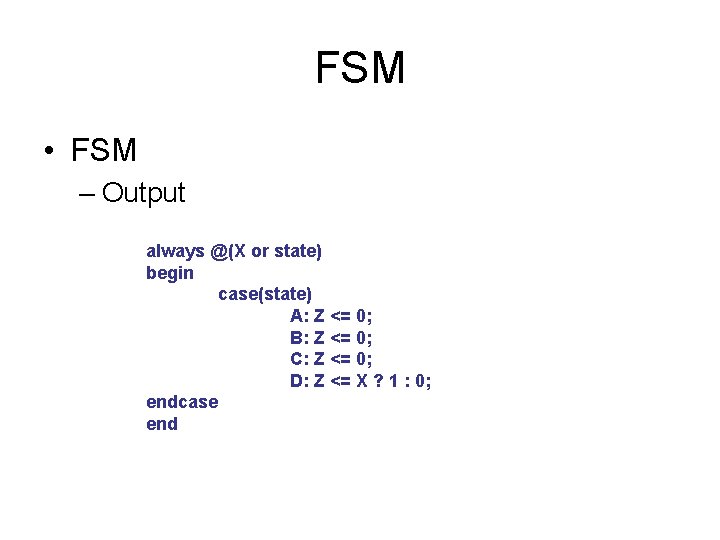

FSM • FSM – Output always @(X or state) begin case(state) A: Z <= 0; B: Z <= 0; C: Z <= 0; D: Z <= X ? 1 : 0; endcase end

Lab • Elements – Two Push Button Switches • PTN 0 and PTN 1 – A 7 Segment LED • The initial LED value – 0 • Push PTN 1 – LED++ • Push PTN 0 – LED--

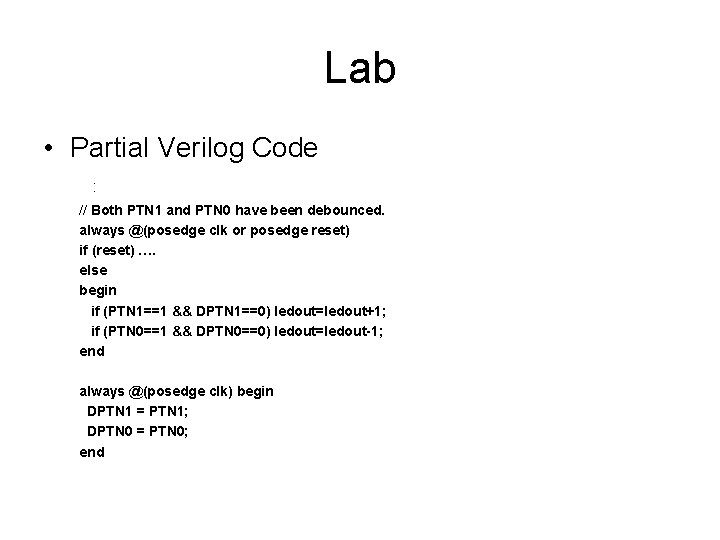

Lab • Partial Verilog Code : // Both PTN 1 and PTN 0 have been debounced. always @(posedge clk or posedge reset) if (reset) …. else begin if (PTN 1==1 && DPTN 1==0) ledout=ledout+1; if (PTN 0==1 && DPTN 0==0) ledout=ledout-1; end always @(posedge clk) begin DPTN 1 = PTN 1; DPTN 0 = PTN 0; end

- Slides: 24