Chapter 8 Hardware Software Codesign on Prototype Professor

- Slides: 67

Chapter 8 Hardware / Software Co-design on Prototype Professor Ching-Lung Su E-mail: kevinsu@yuntech. edu. tw Http: //soc. eecs. yuntech. edu. tw NYUST/EL

Outline 8. 1 Hardware / Software Co-design on Prototype 8. 2 Test and Debug on Prototype 8. 3 Introduction to GDB Server 8. 4 Reference 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-2/115

8. 1 Hardware / Software Co-design on Prototype 8. 2 Test and Debug on Prototype 8. 3 Introduction to GDB Server 8. 4 Reference 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-3/115

8. 1 Hardware / Software Co-design on Prototype u Software and Hardware Partition u Procedure Structure of the Software u Systematic Structure of the Hardware u Integrate Hardware and Software 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-4/115

8. 1 Software and Hardware Partition n Software and Hardware Partition u Separate the partitions of Hardware and Software n Analysis the complexity of MPEG-2 software n Determine the cut of the hardware and software n Software partition: l Operation movements are dispersed in different function. l Operation amount is small n Hardware partition: l Operation movements are suitable for accelerating regularly with the hardware. l Operation amount is great 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-5/115

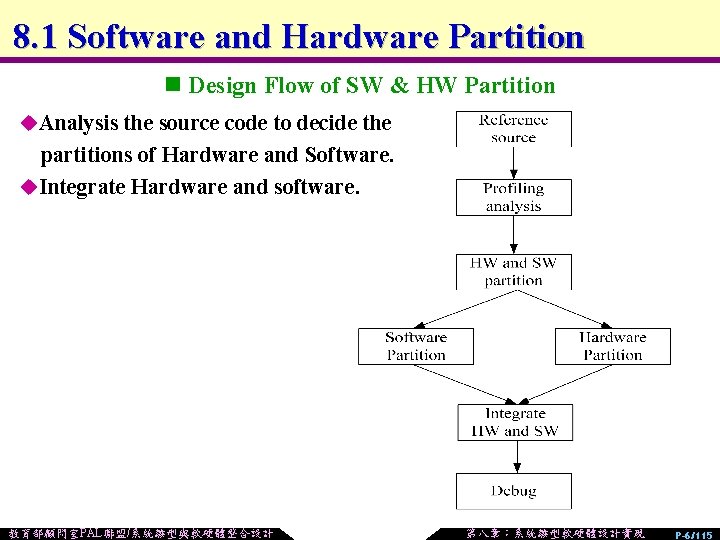

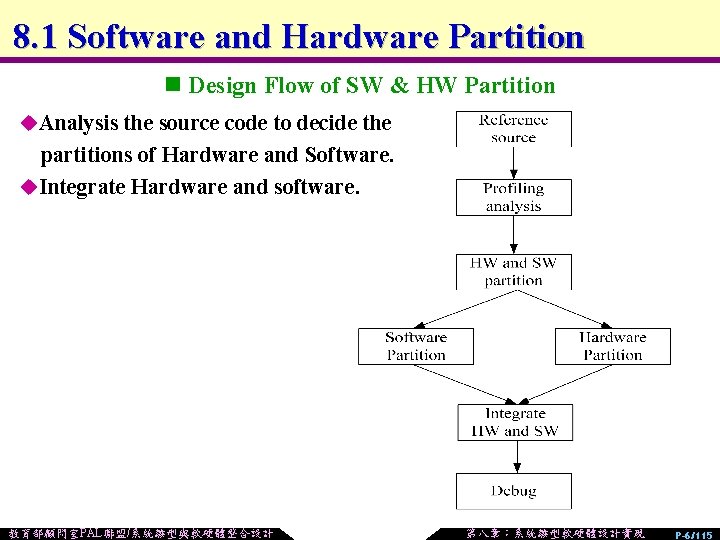

8. 1 Software and Hardware Partition n Design Flow of SW & HW Partition u. Analysis the source code to decide the partitions of Hardware and Software. u. Integrate Hardware and software. 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-6/115

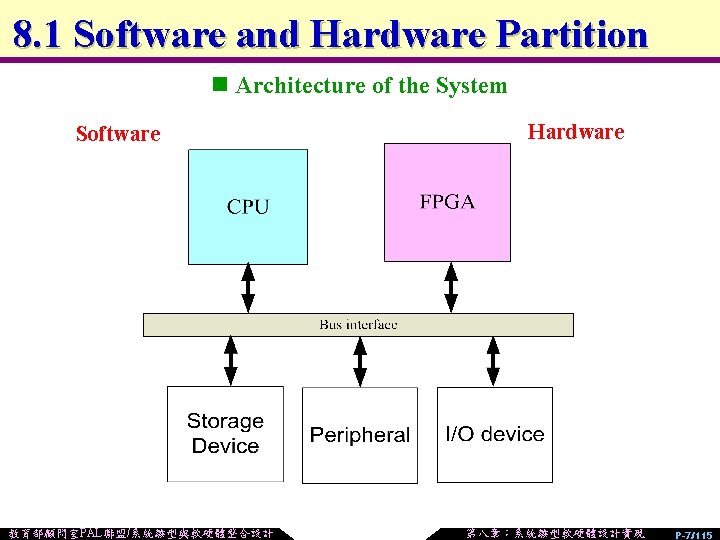

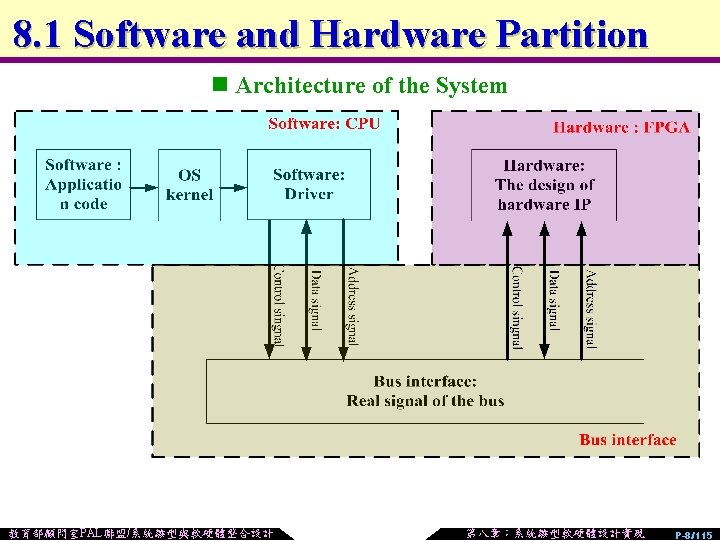

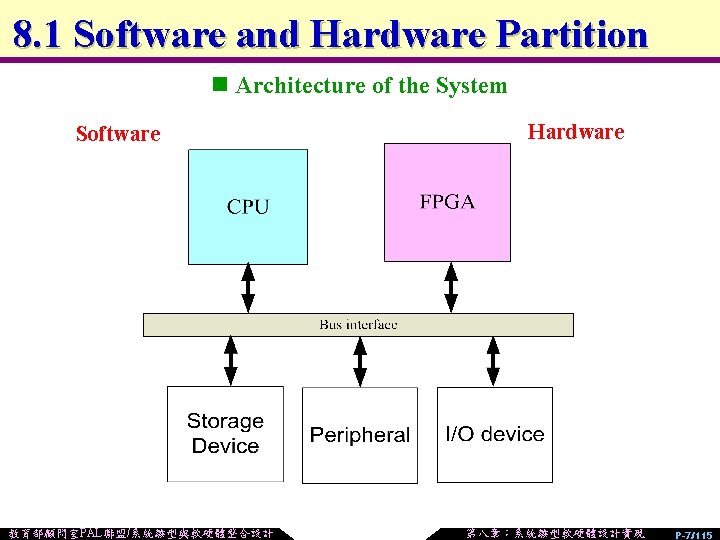

8. 1 Software and Hardware Partition n Architecture of the System Software 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 Hardware 第八章:系統雛型軟硬體設計實現 P-7/115

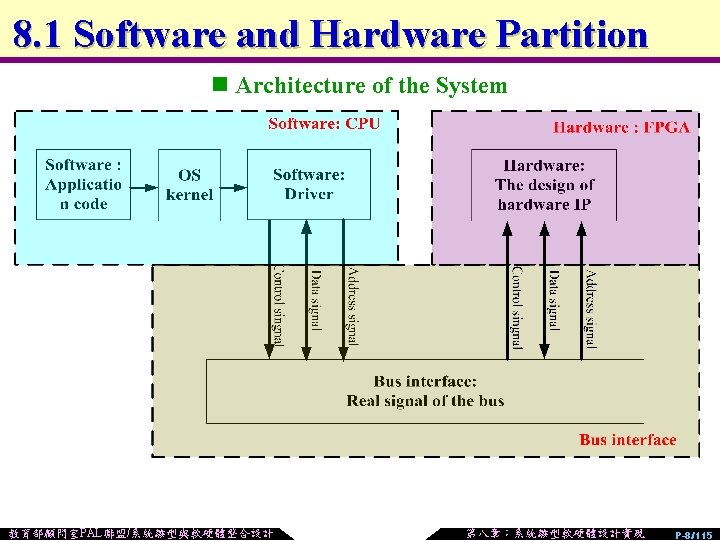

8. 1 Software and Hardware Partition n Architecture of the System 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-8/115

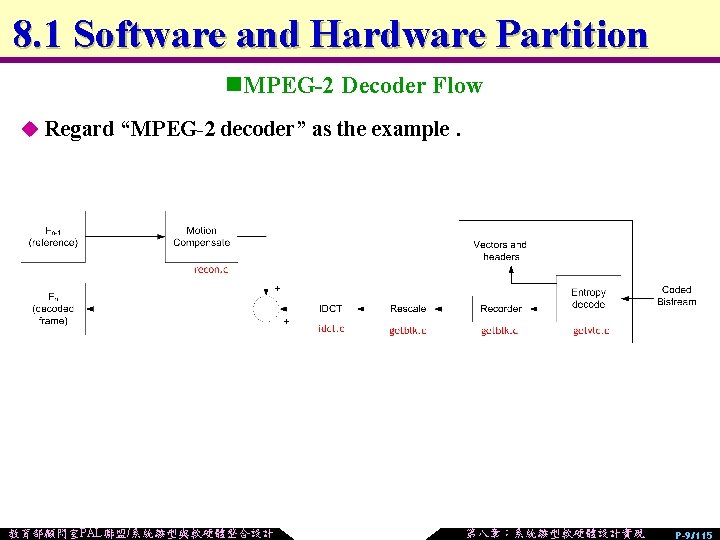

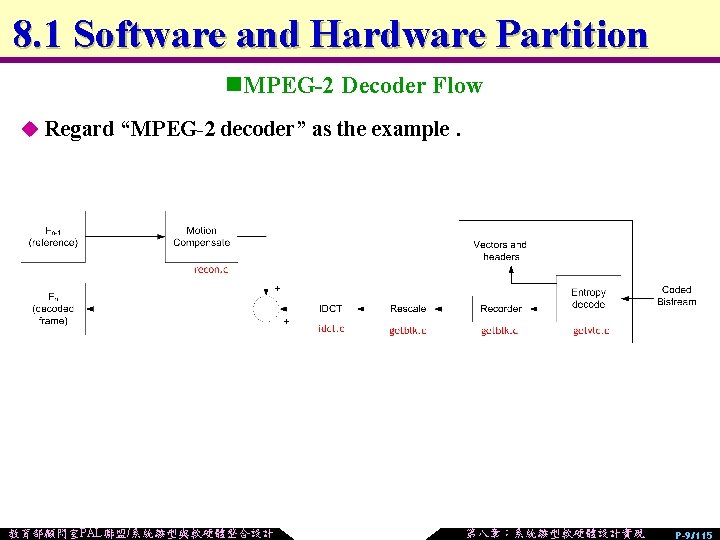

8. 1 Software and Hardware Partition n. MPEG-2 Decoder Flow u Regard “MPEG-2 decoder” as the example. 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-9/115

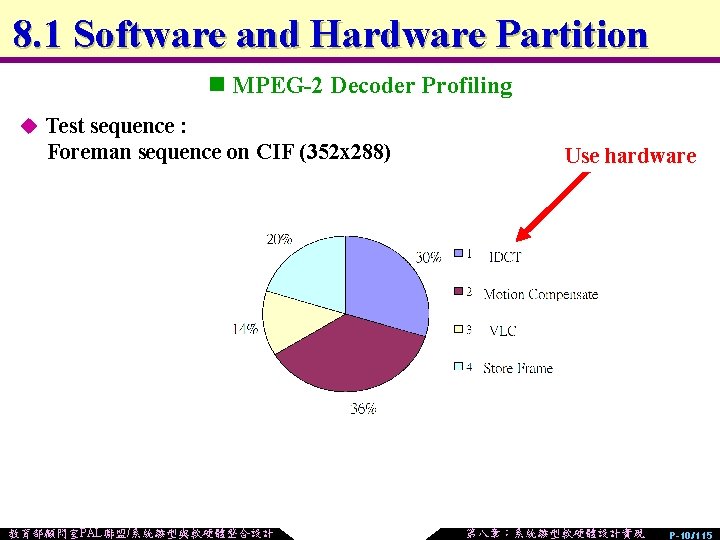

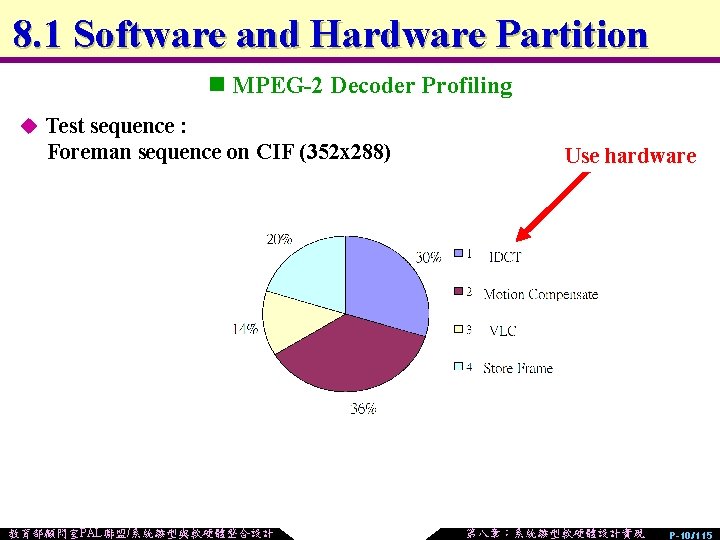

8. 1 Software and Hardware Partition n MPEG-2 Decoder Profiling u Test sequence : Foreman sequence on CIF (352 x 288) 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 Use hardware 第八章:系統雛型軟硬體設計實現 P-10/115

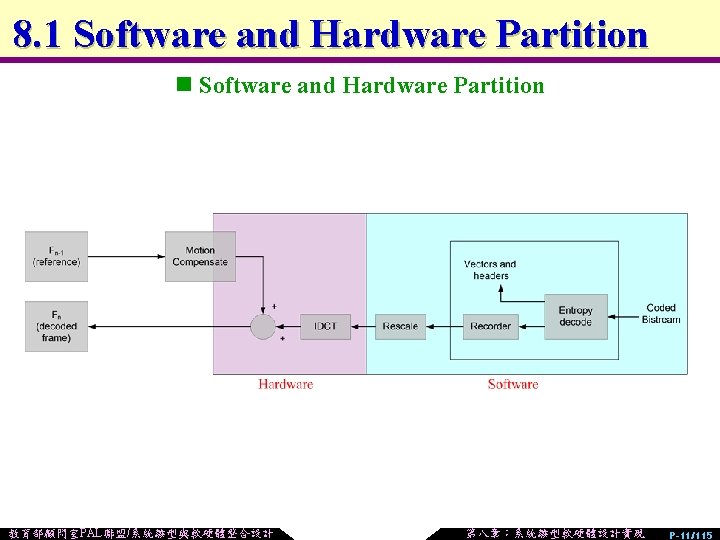

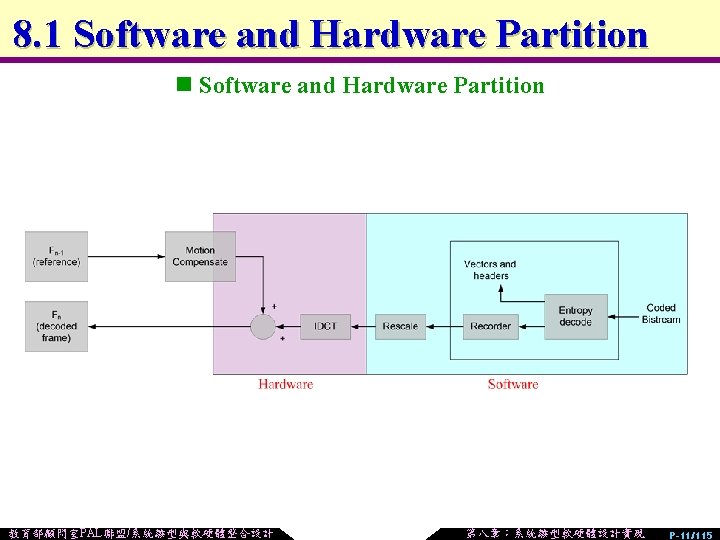

8. 1 Software and Hardware Partition n Software and Hardware Partition 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-11/115

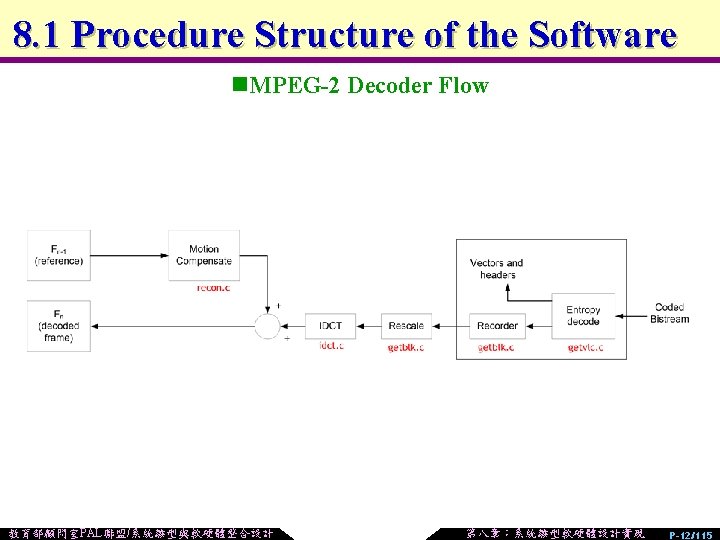

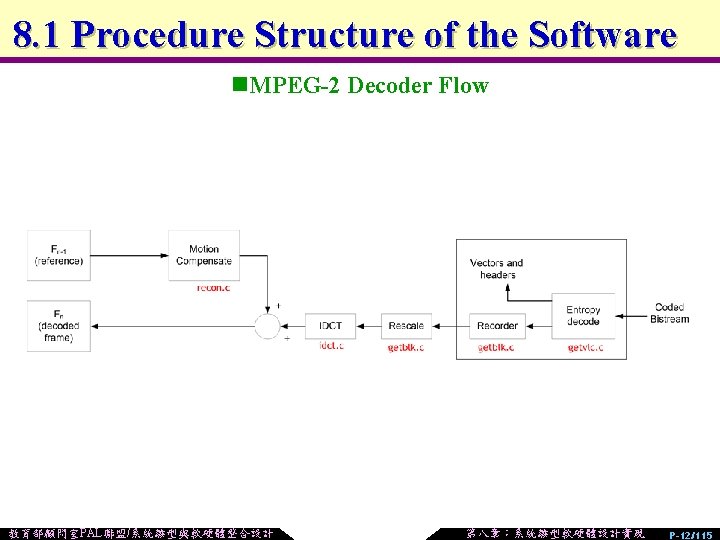

8. 1 Procedure Structure of the Software n. MPEG-2 Decoder Flow 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-12/115

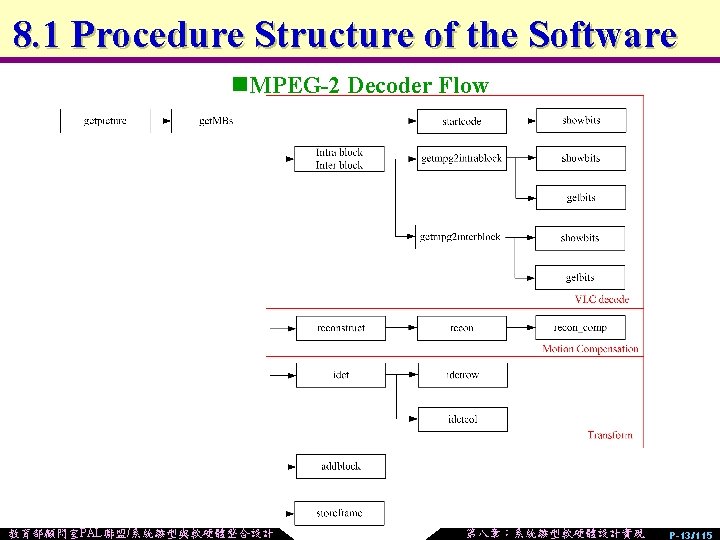

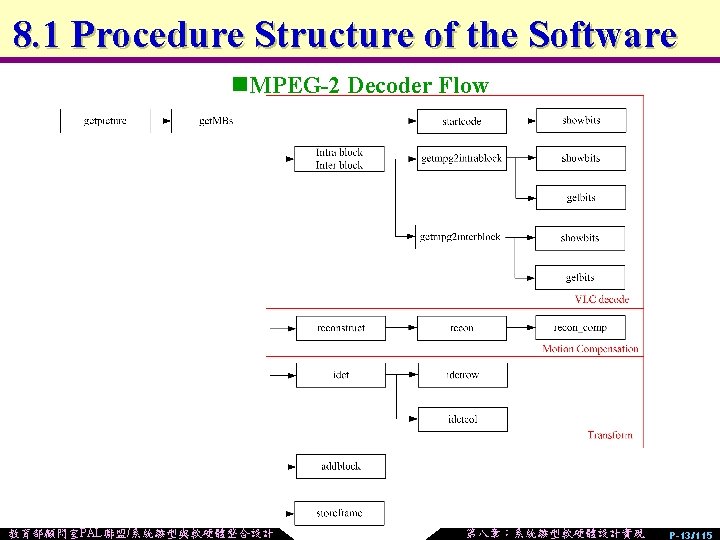

8. 1 Procedure Structure of the Software n. MPEG-2 Decoder Flow 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-13/115

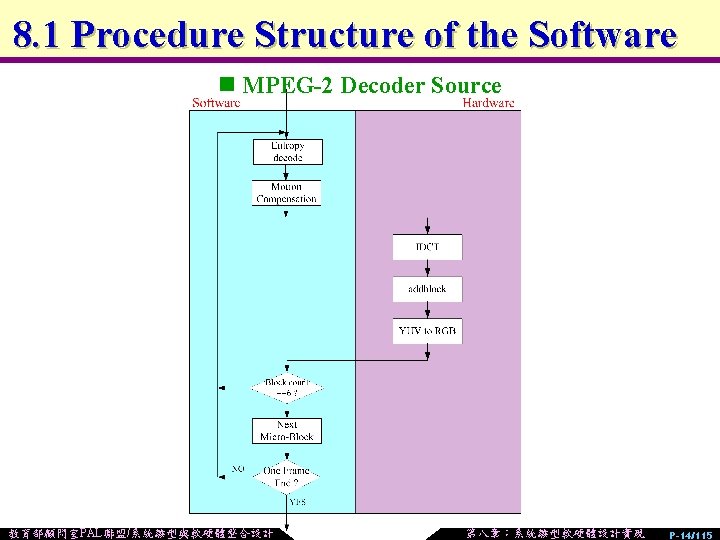

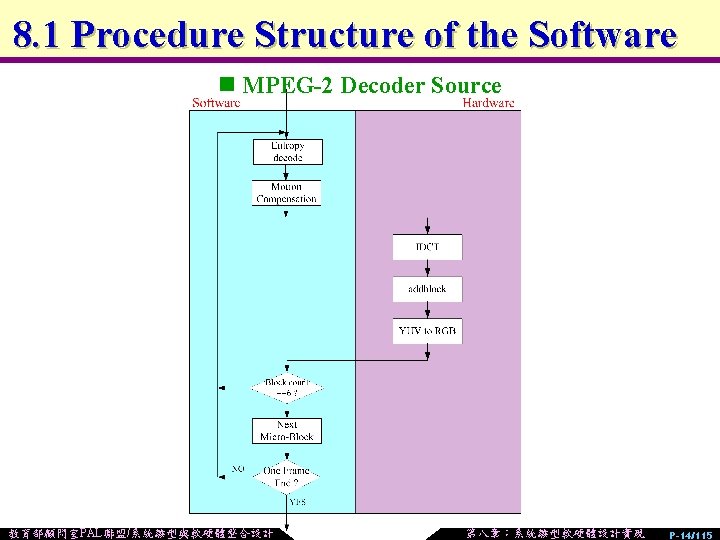

8. 1 Procedure Structure of the Software n MPEG-2 Decoder Source 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-14/115

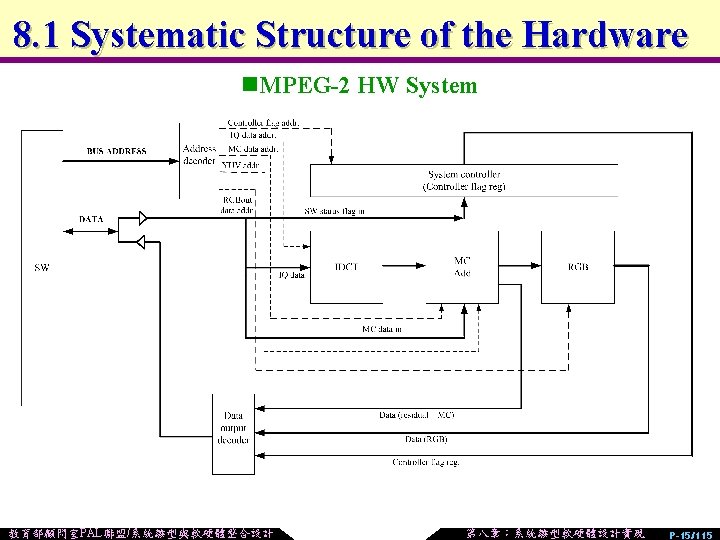

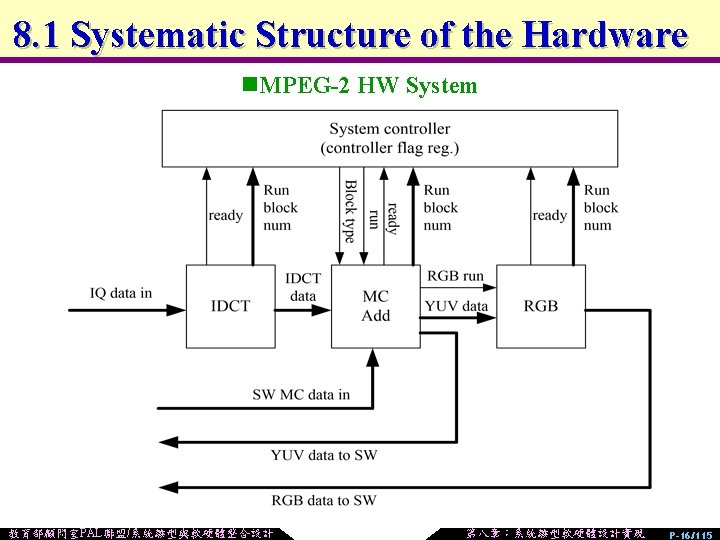

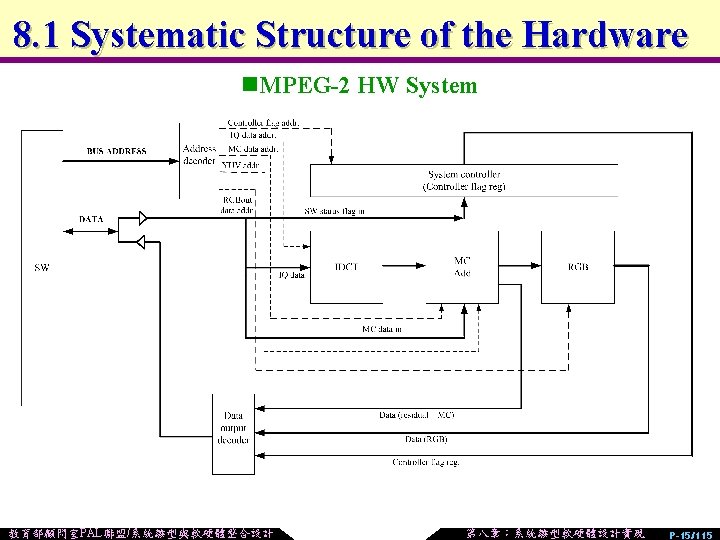

8. 1 Systematic Structure of the Hardware n. MPEG-2 HW System 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-15/115

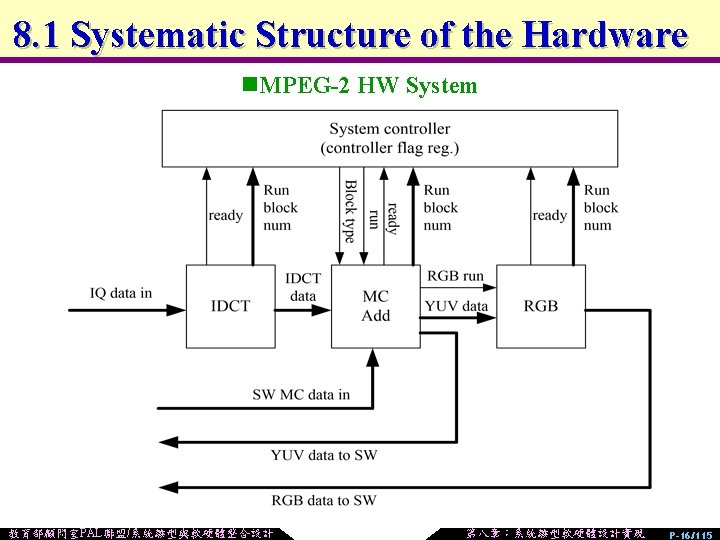

8. 1 Systematic Structure of the Hardware n. MPEG-2 HW System 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-16/115

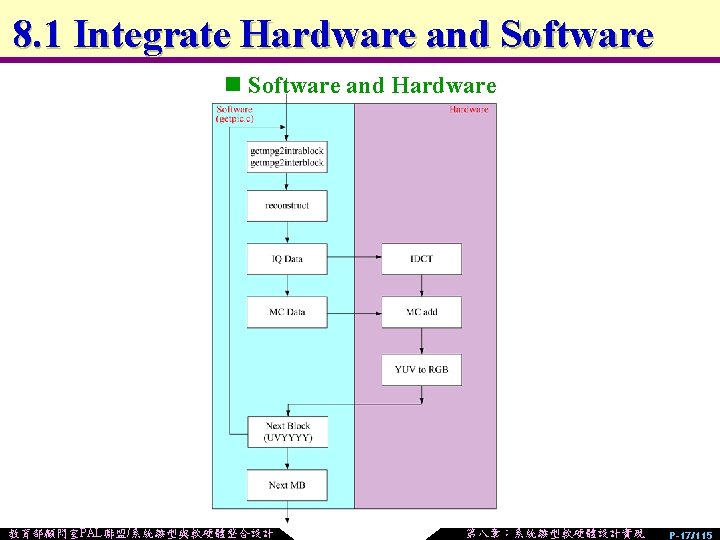

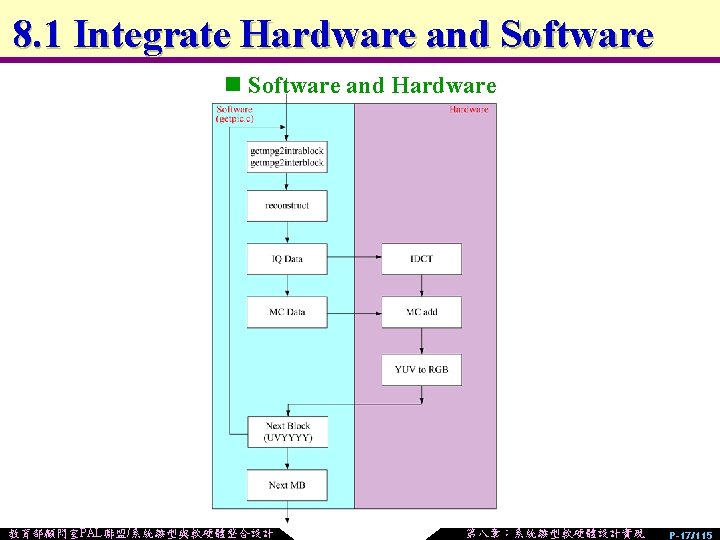

8. 1 Integrate Hardware and Software n Software and Hardware 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-17/115

8. 1 Integrate Hardware and Software n The Step of the Flow Step 1. Software procedure : n Get the type of the MB( Intra type or Inter type) n Get IQ data and MC data n Send IQ data and MC data into Hardware Step 2. n Check the HW Controller Flag Register (0 x 200) n Check whether the bit 11(S 2) is high or not n Judge the output (IDCT-Data) of IDCT-IP is ready or not. Step 3. n The output (IDCT-Data) of IDCT-IP is ready n Set the value into bit 12 and bit 13 of HW Controller Flag Register (0 x 200) n Bit 12:the step of the value to enable MC-IP work: 0 1 0 n Bit 13:set the type of the MB: 0 -intra type , 1 -inter type 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-18/115

8. 1 Integrate Hardware and Software n The Step of the Flow Step 4. n Check the HW Controller Flag Register (0 x 200) n Check whether the bit 10(S 1) is high or not n IF it is high, software read the YUV data from HW system Step 5. n When decode the MB, the order is U V Y Y n When decode Y block, check the bit 9(RGB-IP status) and bit 20(RGB block count) of the HW Controller Flag Register (0 x 200) n IF RGB-IP is ready, software read RGB data from Hardware Step 6. n Send RGB data to Frame Buffer n Display the picture 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-19/115

8. 2 Test and Debug on Prototype 8. 1 Hardware / Software Co-design on Prototype 8. 2 Test and Debug on Prototype 8. 3 Introduction to GDB Server 8. 4 Reference 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-20/115

8. 2 Test and Debug on Prototype u ARM Developer Suit u Quartus II u Logic Analyzer 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-21/115

8. 2 Test and Debug on Prototype u It is hard to debug on Embedded System, mainly divide three parts : n Software:ARM Developer Suit (ADS) l AXD Debugger n Hardware:Quartus II n Bus:Logic Analyzer 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-22/115

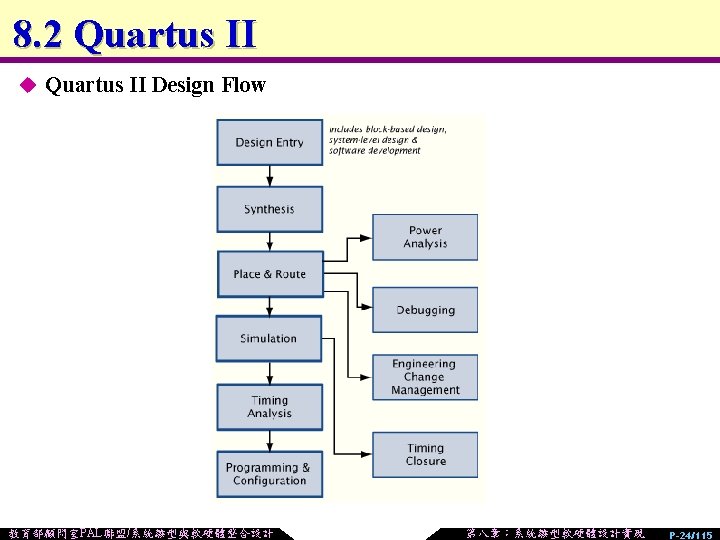

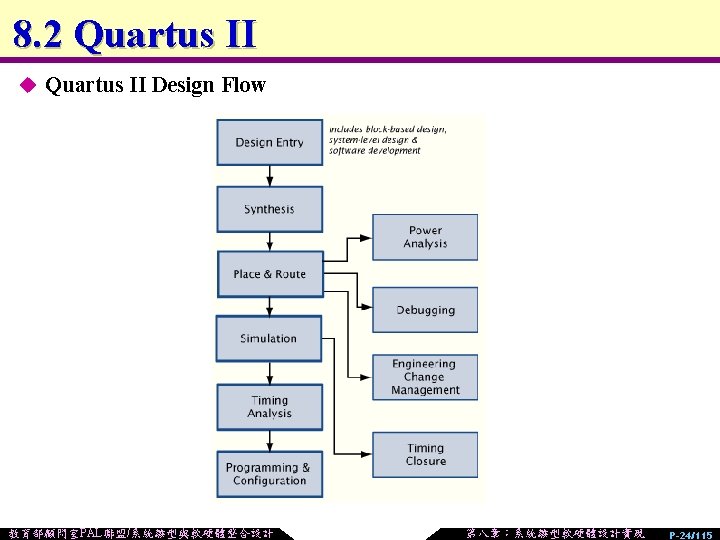

8. 2 Quartus II u The Quartus II development software provides a complete design environment for system-on-a-programmable-chip (SOPC) design. Regardless of whether you use a personal computer or a UNIX or Linux workstation, the Quartus II software ensures easy design entry, fast processing, and straightforward device programming. The following sections describe the general capabilities. n Quartus II Highlights n Design Capabilities n Native. Link Integration with other EDA Tools 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-23/115

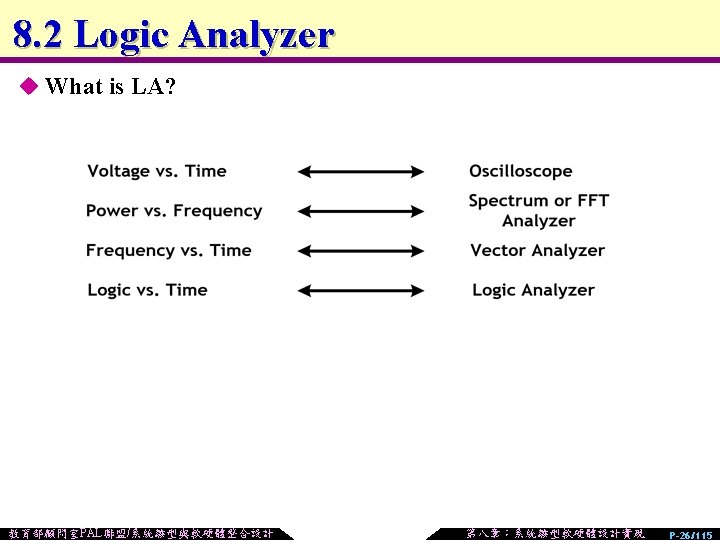

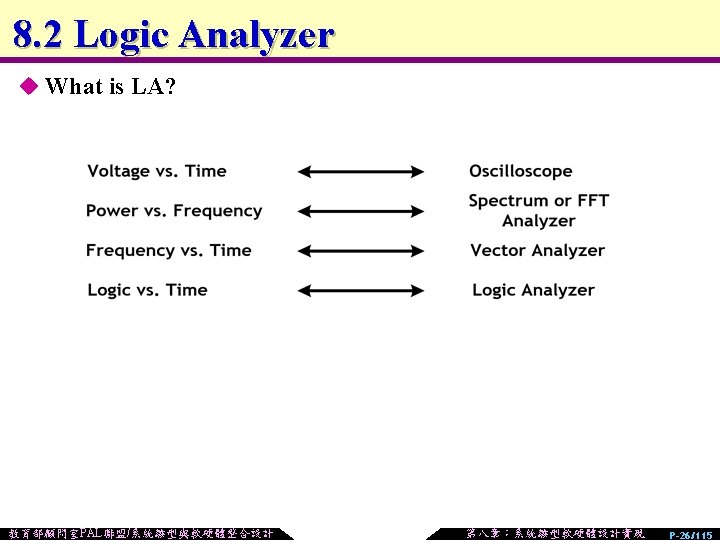

8. 2 Logic Analyzer u Basic Concept of Logic Analyzer n What is LA? n Why need LA? n Function of LA n Architecture of LA l Probe l Synchronous & Asynchronous l Trigger state machine l Acquisition memory 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-25/115

8. 2 Logic Analyzer u Why need LA? n LA can solve the following problem : l Chase the immediate data of microprocessor l Observe the multiple logic information at the same time l Acquisition the systematic trouble of intermission l Chase the reason of the system crash l Development of Embedded System 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-27/115

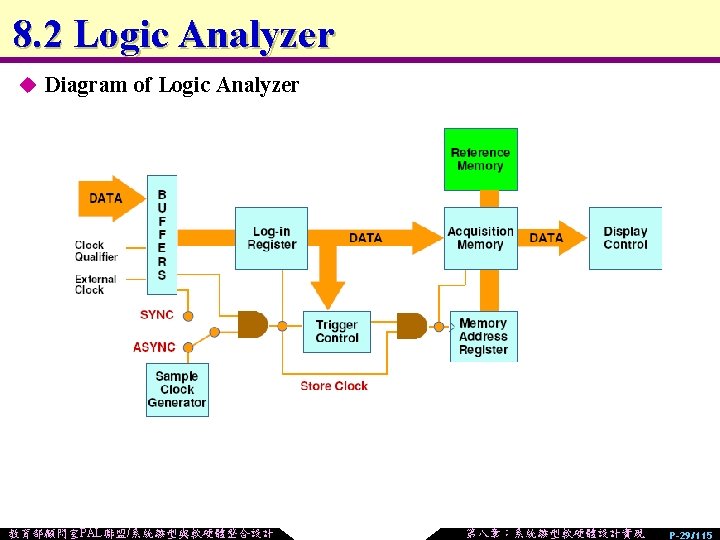

8. 2 Logic Analyzer u Function of LA n Retrieve (Asynchronous and Synchronous) n Store n Trigger and Qualification n Display (State and Waveform) 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-28/115

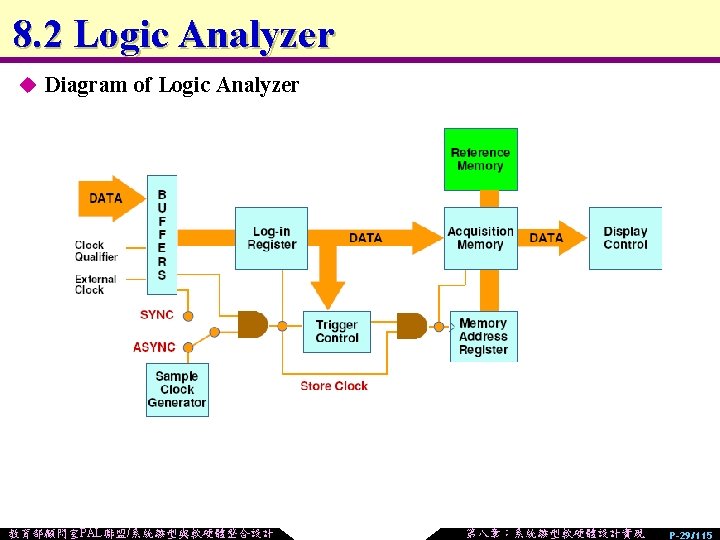

8. 2 Logic Analyzer u Architecture of LA n Probe n Asynchronous and Synchronous n Trigger State Machine n Acquisition Memory 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-30/115

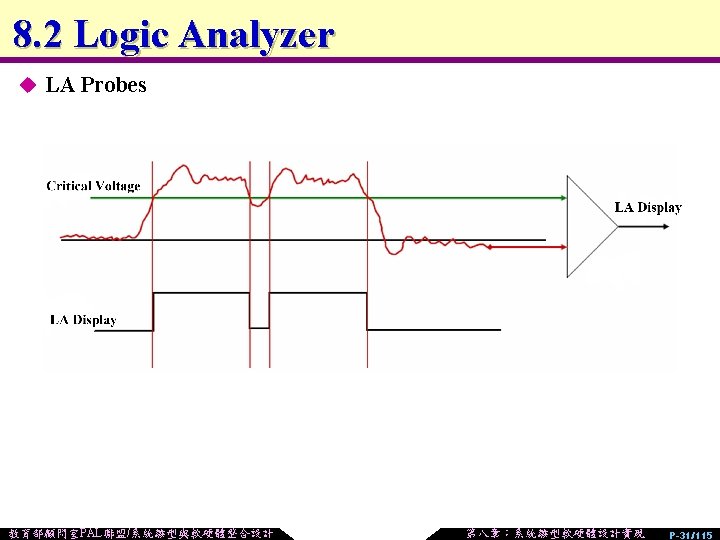

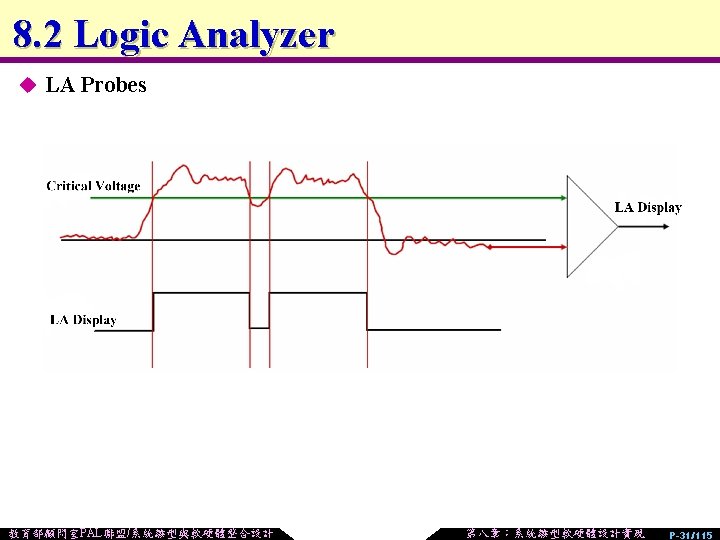

8. 2 Logic Analyzer u Characteristic of Digital Probe n Multi-channel n Limited Dynamic Range n Probe with Critical Point l Fix Value (TTL/CMOS Logic) l Variable Value (+/- 5 ~ 10 V) n Probe can change or reduce bandwidth 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-32/115

8. 2 Logic Analyzer u Architecture of LA n Probe n Asynchronous and Synchronous n Trigger State Machine n Acquisition Memory 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-33/115

8. 2 Logic Analyzer u Asynchronous Timing n Produce Sample Pulse from Logic Analyzer n The sooner the better u Synchronous State n Produce Sample Pulse from System n Logic Analyzer : it is enough for the acceptable external pulse 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-34/115

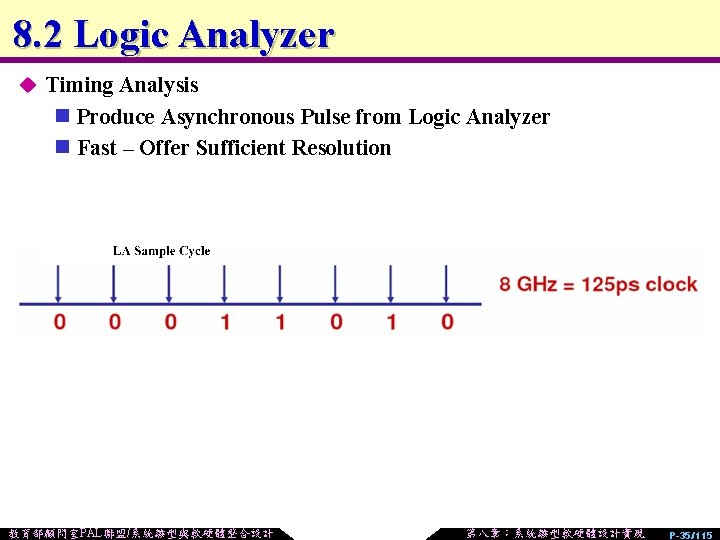

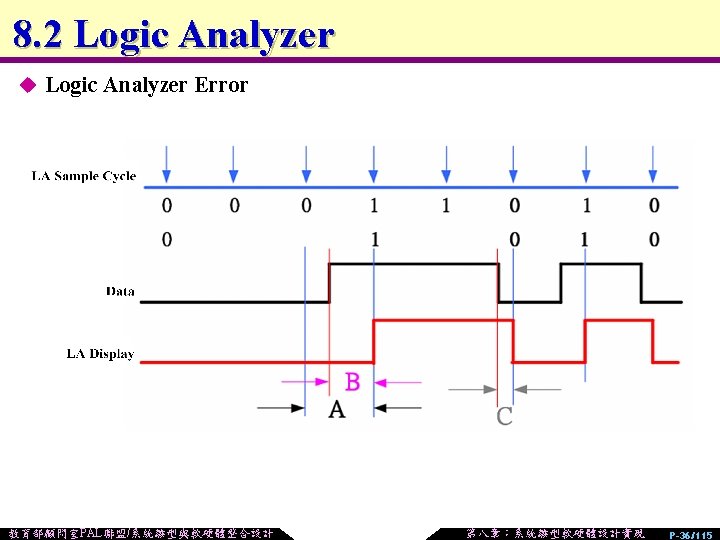

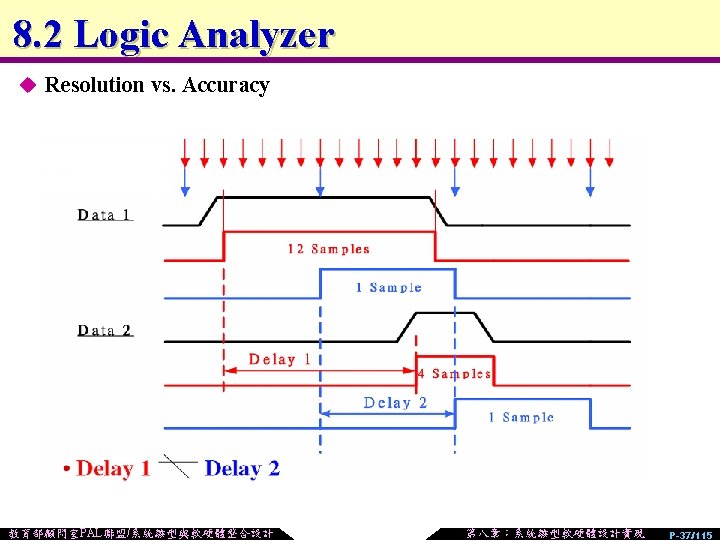

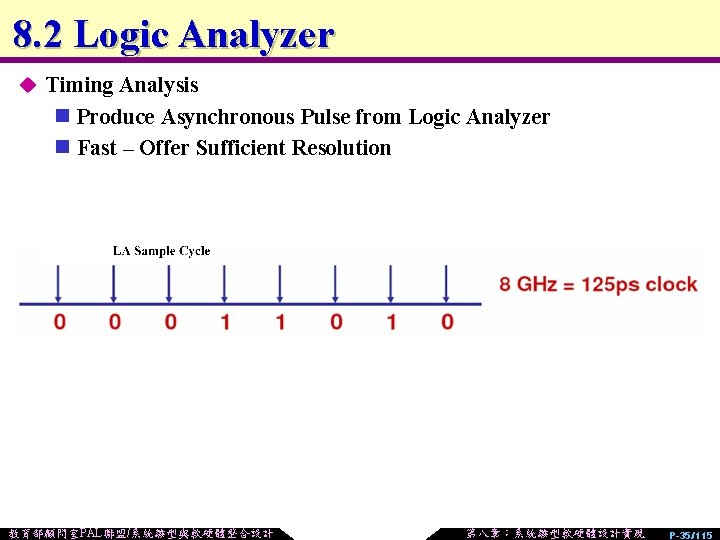

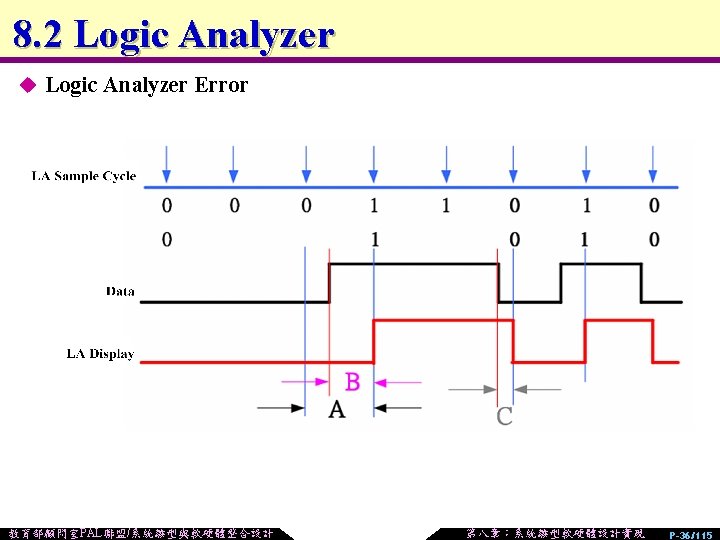

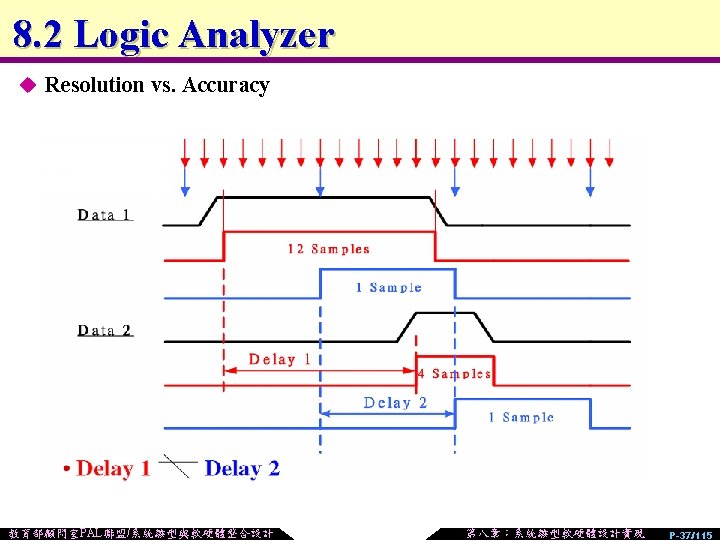

8. 2 Logic Analyzer u Timing Analysis n Produce Asynchronous Pulse from Logic Analyzer n Fast – Offer Sufficient Resolution 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-35/115

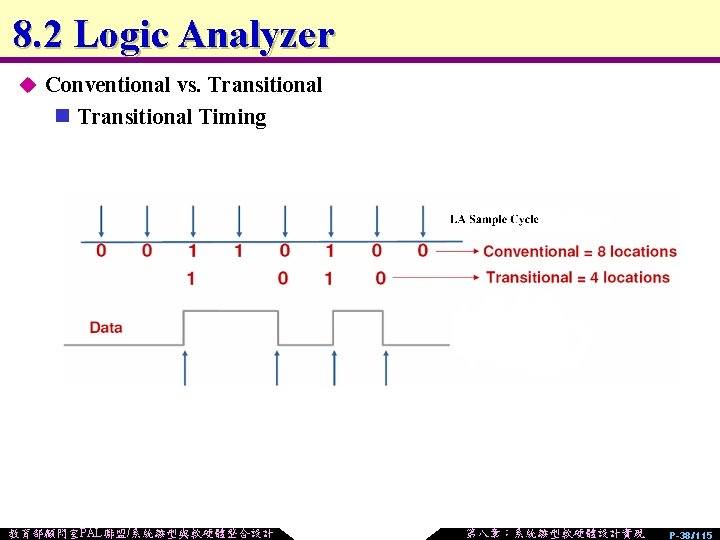

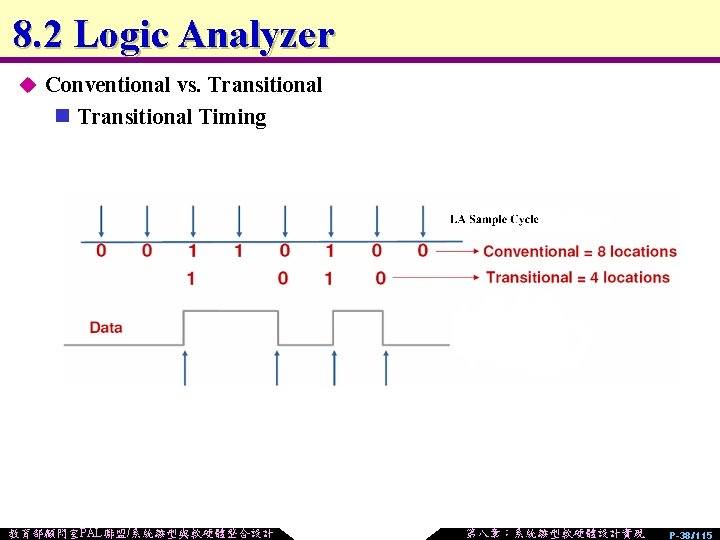

8. 2 Logic Analyzer u Conventional vs. Transitional n Transitional Timing 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-38/115

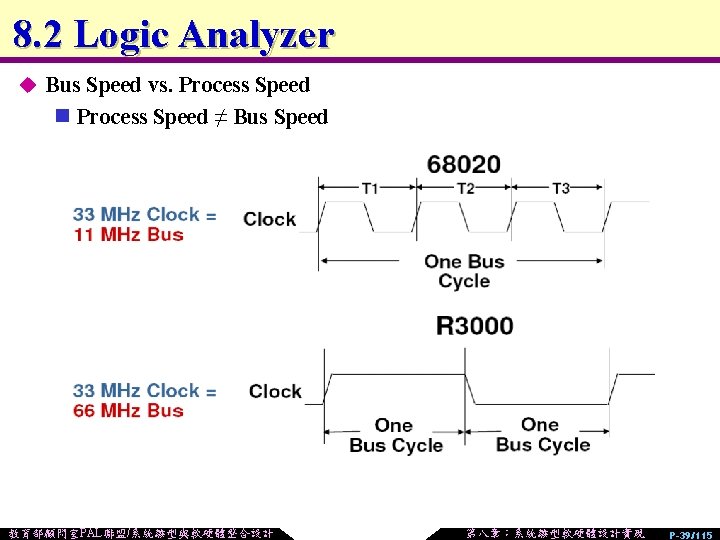

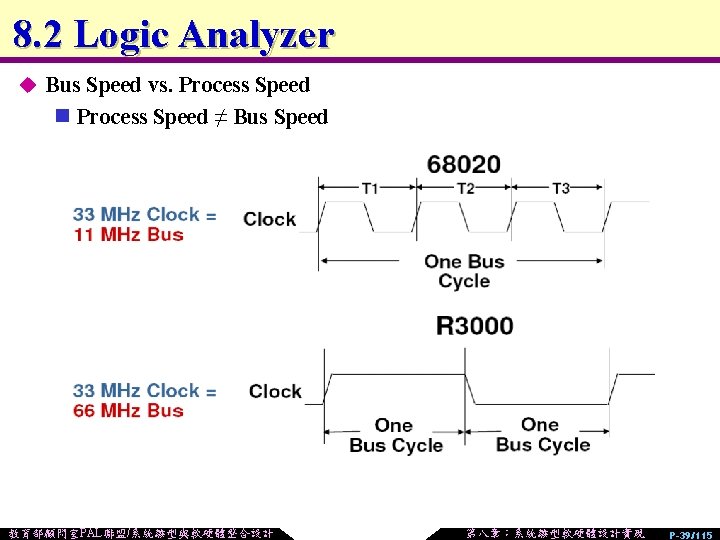

8. 2 Logic Analyzer u Bus Speed vs. Process Speed n Process Speed ≠ Bus Speed 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-39/115

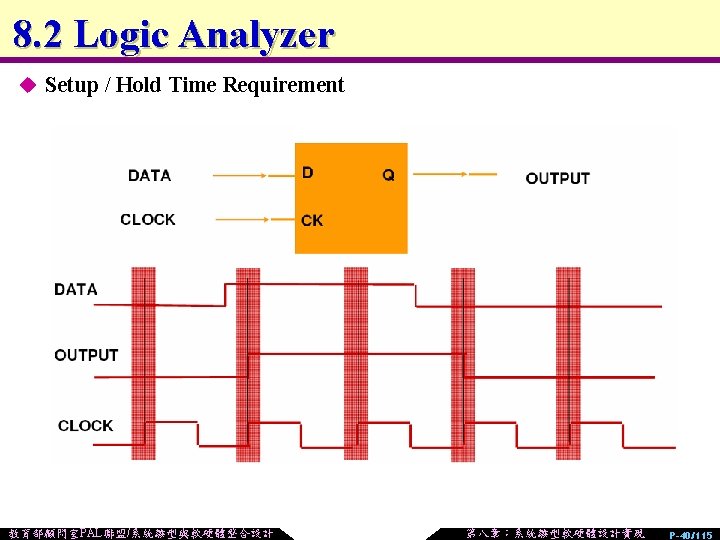

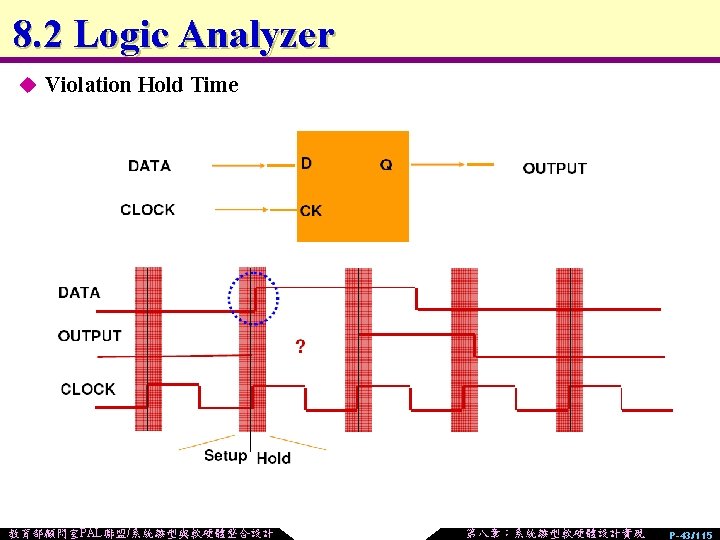

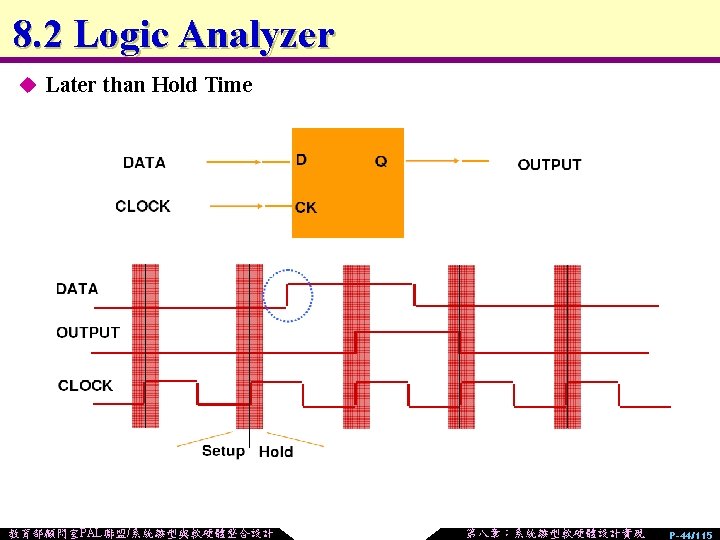

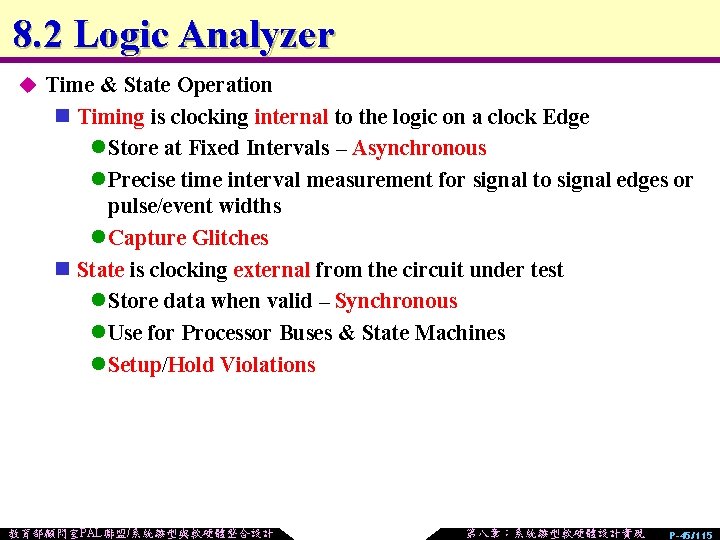

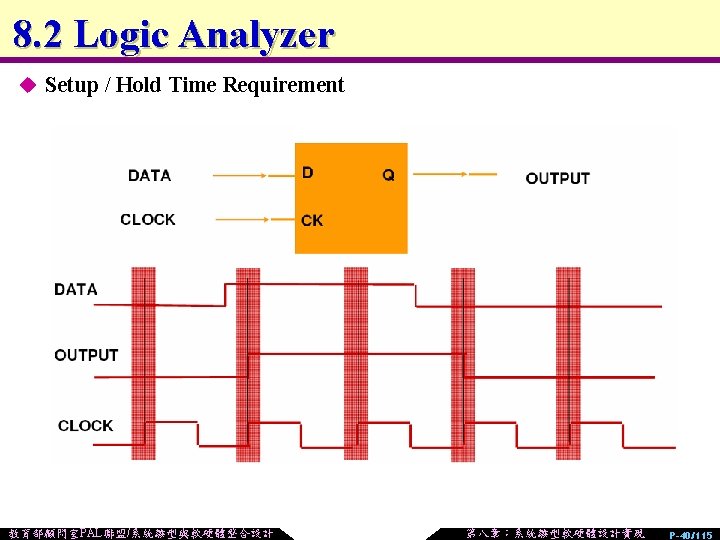

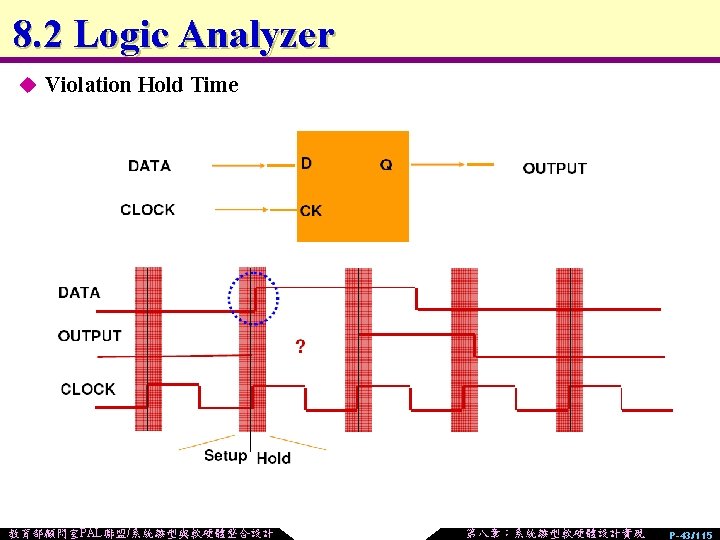

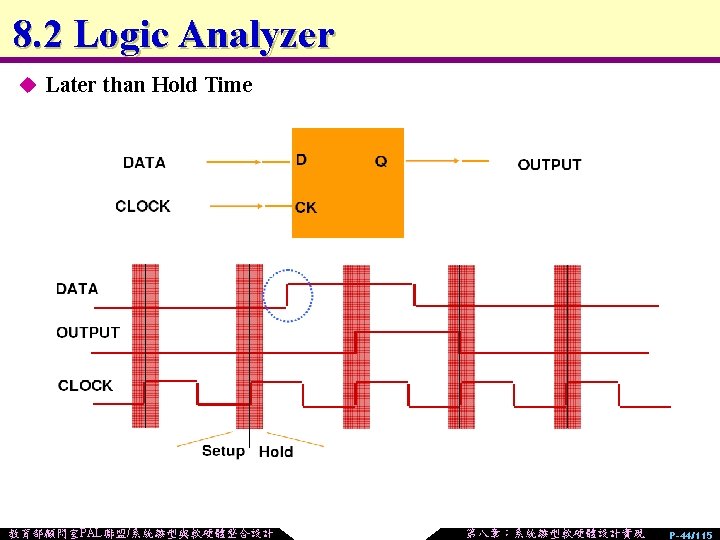

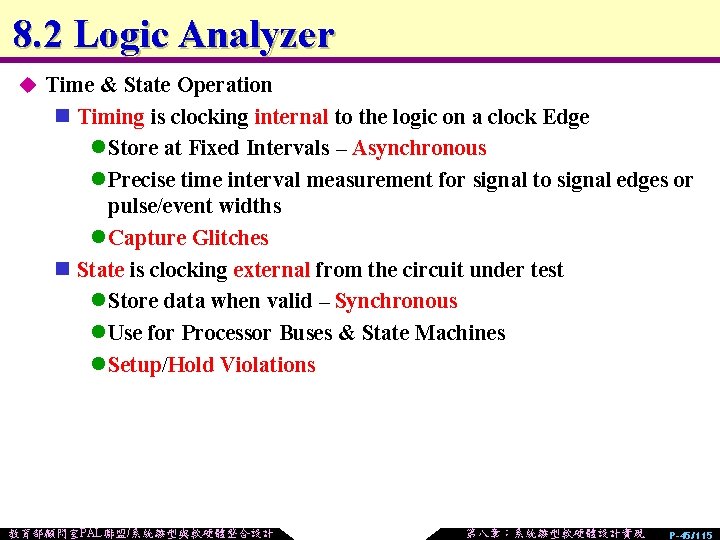

8. 2 Logic Analyzer u Time & State Operation n Timing is clocking internal to the logic on a clock Edge l Store at Fixed Intervals – Asynchronous l Precise time interval measurement for signal to signal edges or pulse/event widths l Capture Glitches n State is clocking external from the circuit under test l Store data when valid – Synchronous l Use for Processor Buses & State Machines l Setup/Hold Violations 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-45/115

8. 2 Logic Analyzer u Architecture of LA n Probe n Asynchronous and Synchronous n Trigger State Machine n Acquisition Memory 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-46/115

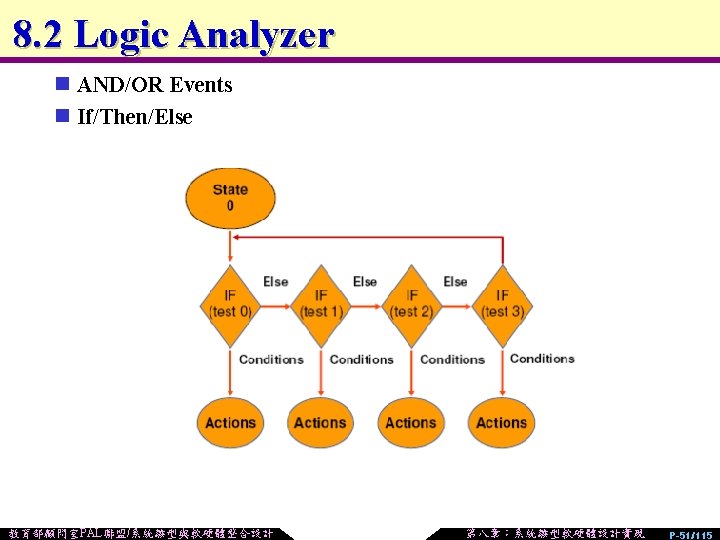

8. 2 Logic Analyzer u Triggering Source n Events l Timer/Counters n States/Levels l Search Events n Actions 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-47/115

8. 2 Logic Analyzer u Triggering Resources n Events l Word Recognition l Sequence Recognition l External Event l Range Recognition l Counter l Timer 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-48/115

8. 2 Logic Analyzer n Actions l Stop/Start Storage l External Pulse l Pause Data Storage l Trigger l Go State X l Control Timer l Control Counter 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-49/115

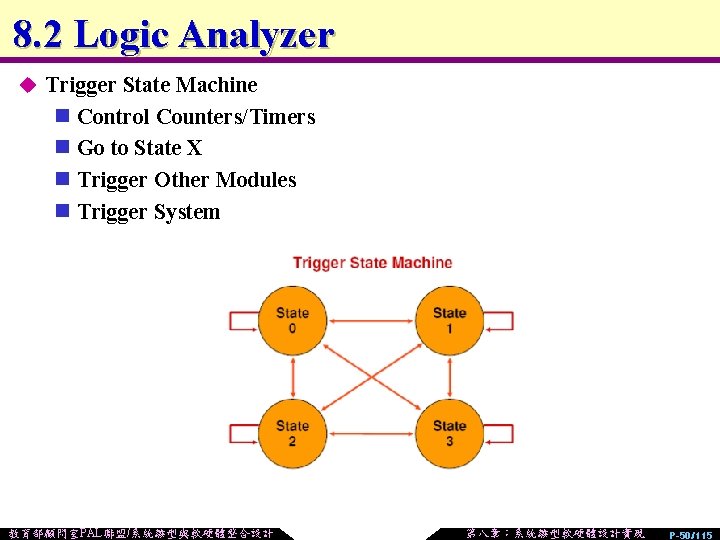

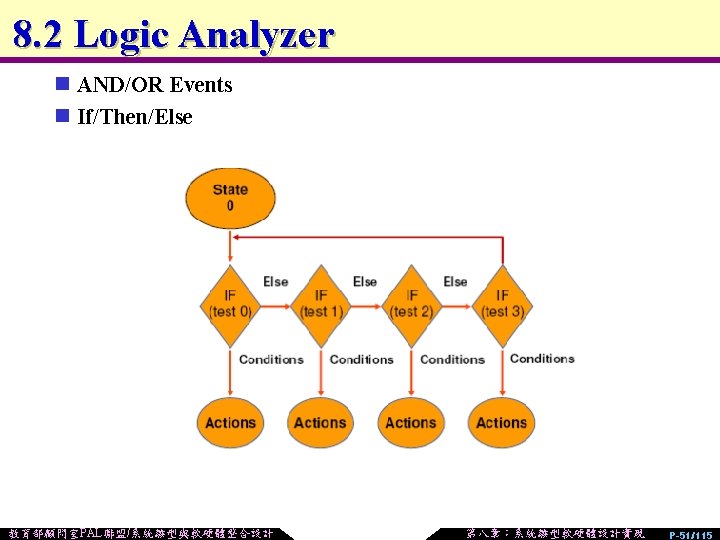

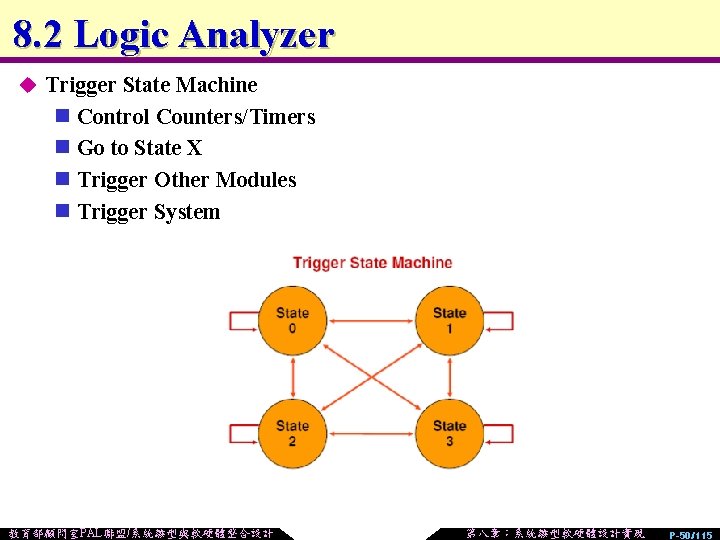

8. 2 Logic Analyzer u Trigger State Machine n Control Counters/Timers n Go to State X n Trigger Other Modules n Trigger System 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-50/115

8. 2 Logic Analyzer u Architecture of LA n Probe n Asynchronous and Synchronous n Trigger State Machine n Acquisition Memory 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-52/115

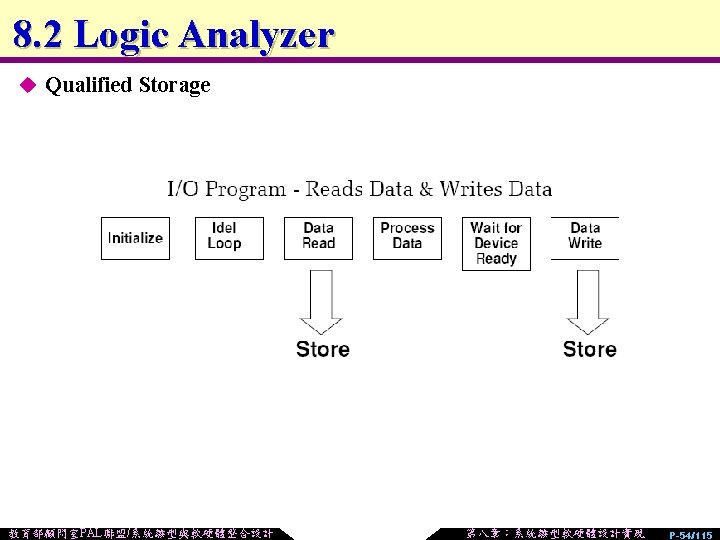

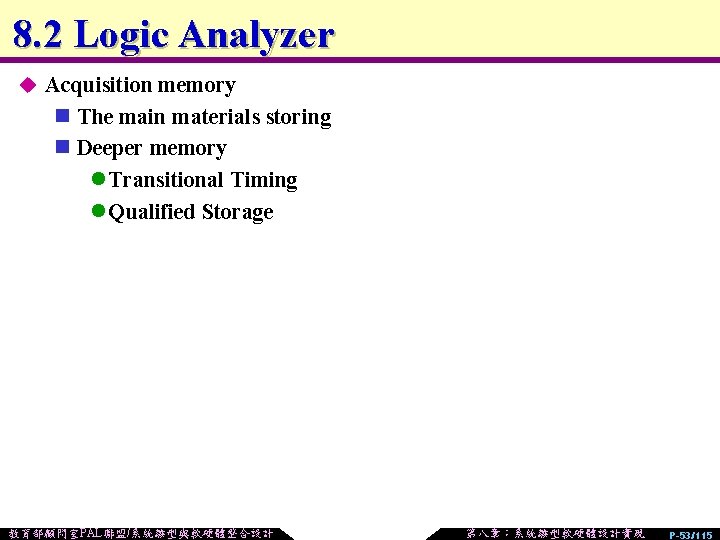

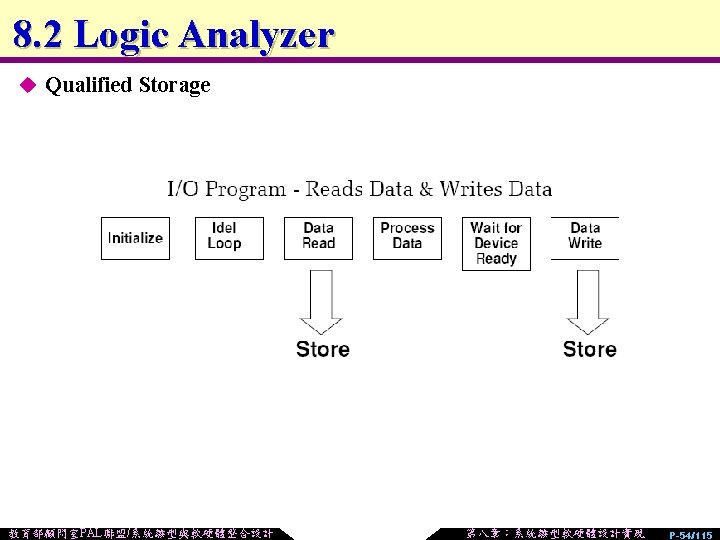

8. 2 Logic Analyzer u Acquisition memory n The main materials storing n Deeper memory l Transitional Timing l Qualified Storage 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-53/115

8. 3 Introduction to GDB Server 9. 1 Hardware / Software Co-design on Prototype 9. 2 Test and Debug on Prototype 9. 3 Introduction to GDB Server 9. 4 Reference 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-55/115

8. 3 Introduction to GDB Server u GDB Commands u How to install GDB u Compiling for Debugging 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-56/115

8. 3 Introduction to GDB Server u The purpose of a debugger such as GDB is to allow you to see what is going on "inside" another program while it executes or what another program was doing at the moment it crashed. u GDB can do these main kinds of things to help you catch bugs in the act: n Start your program, specifying anything that might affect its behavior. n Make your program stop on specified conditions. n Examine what has happened, when your program has stopped. 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-57/115

8. 3 Introduction to GDB Server u You can use GDB to debug programs written in C or C++, Modula-2 and Chill is partial. u Debugging Pascal programs which use sets, file variables, or nested functions does not currently work. GDB does not support entering expressions, printing values, or similar features using Pascal syntax. u GDB can be used to debug programs written in Fortran, although it does not yet support entering expressions, printing values, or similar features using Fortran syntax. 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-58/115

8. 3 GDB Commands u A GDB command is a single line of input. There is no limit on how long it can be. It starts with a command name, which is followed by arguments whose meaning depends on the command name. u GDB command names may always be truncated if that abbreviation is unambiguous. Other possible command abbreviations are listed in the documentation for individual commands. u You can always ask GDB itself for information on its commands, using the command help. 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-59/115

8. 3 GDB Commands u In addition to help, you can use the GDB commands info and show to inquire about the state of your program, or the state of GDB itself. n info l This command (abbreviated i) is for describing the state of your program. n show l In contrast to info, show is for describing the state of GDB itself. 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-60/115

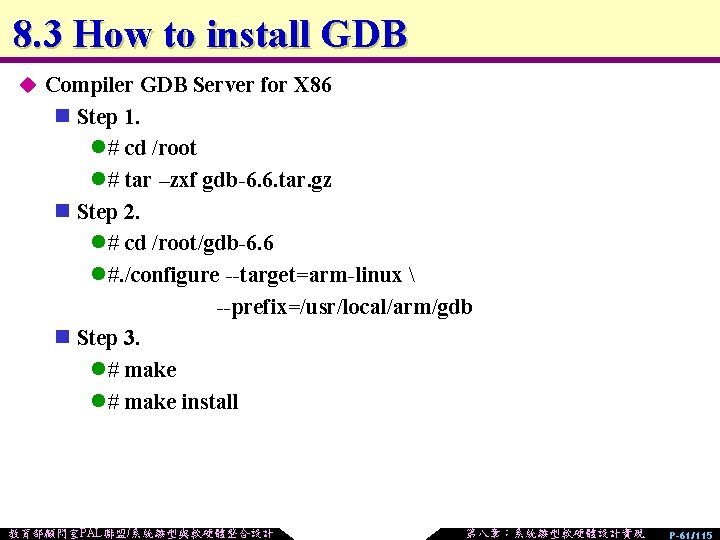

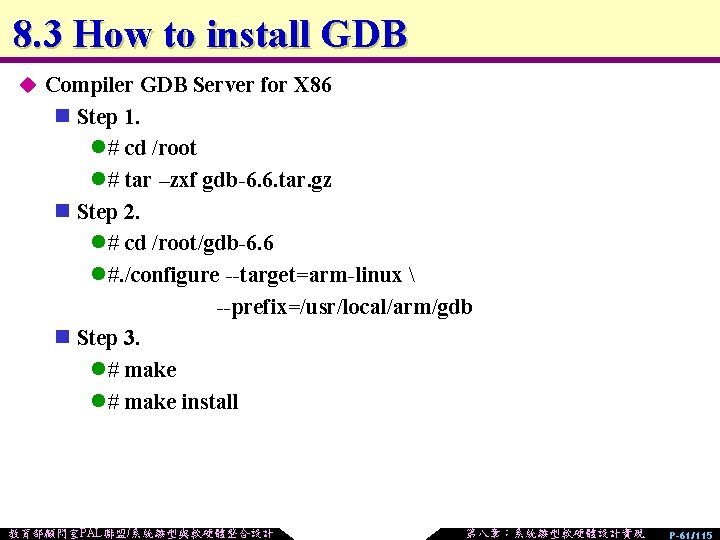

8. 3 How to install GDB u Compiler GDB Server for X 86 n Step 1. l # cd /root l # tar –zxf gdb-6. 6. tar. gz n Step 2. l # cd /root/gdb-6. 6 l #. /configure --target=arm-linux --prefix=/usr/local/arm/gdb n Step 3. l # make install 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-61/115

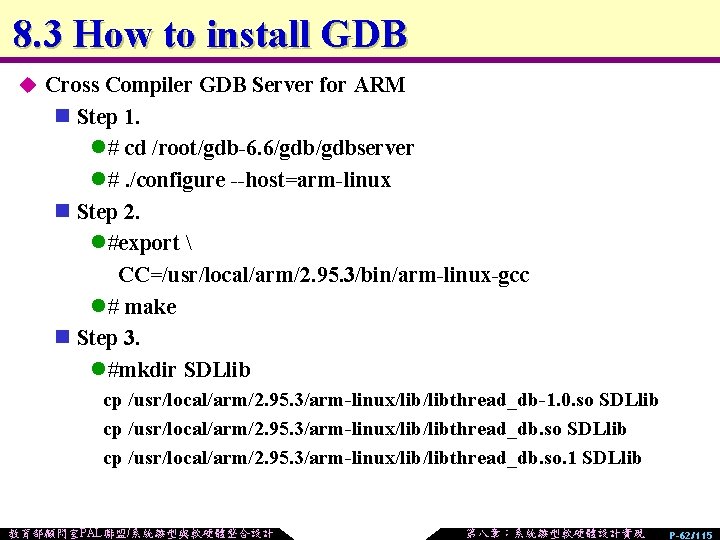

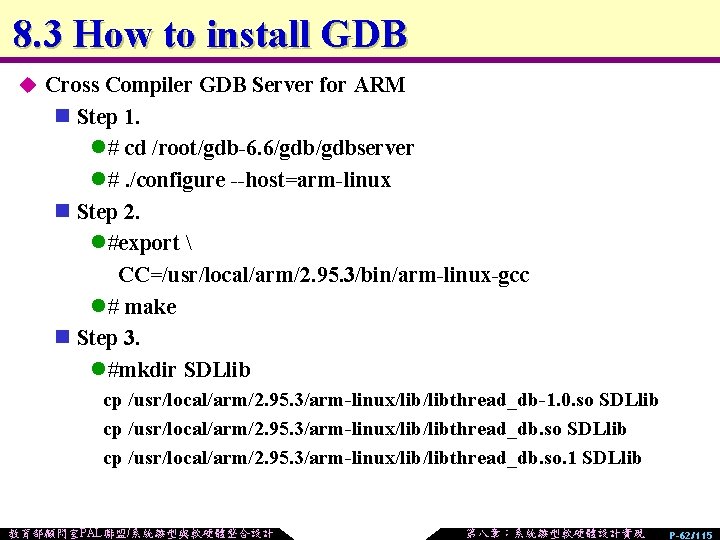

8. 3 How to install GDB u Cross Compiler GDB Server for ARM n Step 1. l # cd /root/gdb-6. 6/gdbserver l #. /configure --host=arm-linux n Step 2. l #export CC=/usr/local/arm/2. 95. 3/bin/arm-linux-gcc l # make n Step 3. l #mkdir SDLlib cp /usr/local/arm/2. 95. 3/arm-linux/libthread_db-1. 0. so SDLlib cp /usr/local/arm/2. 95. 3/arm-linux/lib/libthread_db. so. 1 SDLlib 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-62/115

8. 3 Compiling for Debugging u When you run a program under GDB, you must first generate debugging information when you compile it. u You may start GDB with its arguments, if any, in an environment of your choice. u If you are doing native debugging, you may redirect your program's input and output, debug an already running process, or kill a child process. 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-63/115

8. 3 Compiling for Debugging u In order to debug a program effectively, you need to generate debugging information when you compile it. u This debugging information is stored in the object file; it describes the data type of each variable or function and the correspondence between source line numbers and addresses in the executable code. u To request debugging information, specify the “-g” option when you run the compiler. 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-64/115

8. 3 Compiling for Debugging u The GNU C/C++ compiler, supports “-g” with or without “-O”, making it possible to debug optimized code. u Many compilers are unable to handle the “-g” and “-O” options together. Using those compilers, you cannot generate optimized executables containing debugging information. u When you debug a program compiled with “-g –O”, remember that the optimizer is rearranging your code. 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-65/115

8. 3 Compiling for Debugging u Older versions of the GNU C compiler permitted a variant option “- gg” for debugging information. GDB no longer supports this format; if your GNU C compiler has this option, do not use it. u GDB knows about preprocessor macros and can show you their expansion. u Most compilers do not include information about preprocessor macros in the debugging information if you specify the “-g” flag alone, because this information is rather large. 教育部顧問室PAL聯盟/系統雛型與軟硬體整合設計 第八章:系統雛型軟硬體設計實現 P-66/115