Hardware Software Codesign Organisatorisches Ziele Inhalte A Steininger

- Slides: 21

Hardware / Software Codesign Organisatorisches Ziele Inhalte A. Steininger TU Vienna

Trost & Rat Homepage: http: //ti. tuwien. ac. at/ecs/teaching/courses LVA Leiter: n n n Martin Delvai Andreas Steininger Peter Tummeltshammer email: hwsw@ecs. tuwien. ac. at Bitte LVA im TUWIS abonnieren 2 A. Steininger TU Vienna

Voraussetzungen Inhaltlich: gute Kenntnisse in VHDL günstig: HW-Modellierung Kenntnis des ASIC-Design Flow günstig: Di. De. VO & Di. De. LU Formal: VO, LU und Vorauss. formal unabhängig im Magister-Studienplan Techn. Informatik 3 A. Steininger TU Vienna

Abwicklung VO 9 fixe Termine: n n n n n 4 Mo 28. 4. Mi 30. 4. Mo 5. 5. Mi 7. 5. Mo 14. 5. Mi 26. 5. Mi 28. 5. Mo 2. 6. Mi 4. 6. jeweils 10: 15 bis 12: 00 im Sem TI A. Steininger TU Vienna

Benotung Vorlesung: n n Teilnahme an der Diskussion Besprechung der Lösung aus der LU Laborübung: n n 5 praktisches Ergebnis Besprechung der Lösung aus der LU A. Steininger TU Vienna

Vorlesung Ziel: n n n theoretischer Hintergrund Ausbildung eines Problembewusstseins prinzipielles Verständnis Weg: n n n 6 Impulsvorträge / Gastvorträge Diskussionen in Kleingruppen Diskussionen im Plenum A. Steininger TU Vienna

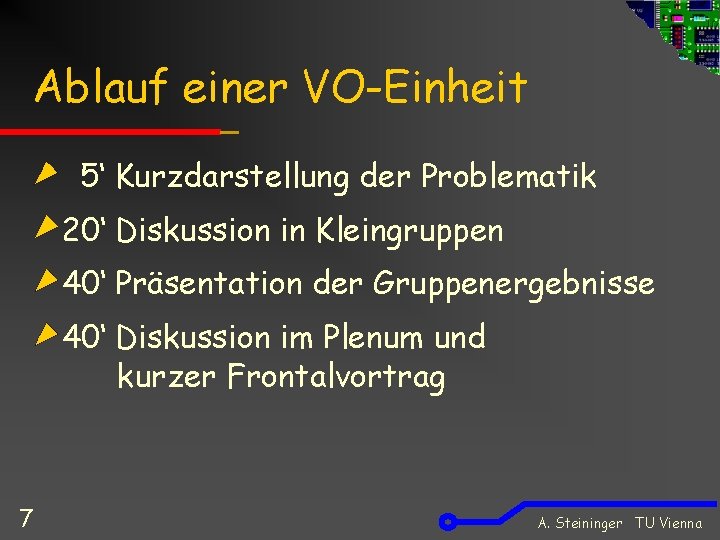

Ablauf einer VO-Einheit 5‘ Kurzdarstellung der Problematik 20‘ Diskussion in Kleingruppen 40‘ Präsentation der Gruppenergebnisse 40‘ Diskussion im Plenum und kurzer Frontalvortrag 7 A. Steininger TU Vienna

Vorstellungen zur LVA Was ist überhaupt HW/SW Codesign? Was lerne ich in dieser LVA? n Vorlesung n Laborübung Wofür brauche ich das Wissen später? 8 A A. Steininger TU Vienna

Was ist HW/SW Codesign? paralleler Entwurf HW/SW n n n schneller Bugs früher sichtbar höherer Abstraktionsgrad Partitionierung HW/SW n übergreifende Optimierung Integration v. Systemen aus/mittels HW/SW n n 9 systematische Schnittstellendefinition Komplexitätsbewältigung A. Steininger TU Vienna

Embedded Systems: Challenges „An exploding number of embedded reactive heterogeneous components in mass-market products“ „Massive seamless integration of heterogeneous components in a real-world environment“ „Building systems of guaranteed functionality and quality at an acceptable cost is a major technological and scientific challenge“ [Joseph Sifakis, Workshop on Strategies for Embedded Systems 2005] 10 A. Steininger TU Vienna

The Constraints Dependability n safety, security, availability [Joseph Sifakis, Workshop on Strategies for Embedded Systems 2005] Autonomy n no humans in the loop Low resource consumption n memory, power, energy Physical constraints n weight size, heat dissipation, … Market positioning n 11 optimal cost/quality, time to market A. Steininger TU Vienna

The System-Centric Approach Joint Design (HW, SW, Environment) to determine cost / quality tradeoffs Requires a combination of competencies in SW, automation, networks, electronics, man-machine interfaces => training, education [Joseph Sifakis, Workshop on Strategies for Embedded Systems 2005] 12 A. Steininger TU Vienna

The Current State no unified theory to predict the dynamic properties of a SW running on a given execution platform complex systems are built through a succession of incremental developments exploding validation costs 13 [Joseph Sifakis, Workshop on Strategies for Embedded Systems 2005] A. Steininger TU Vienna

Anwendungsbeispiele Consumer-Products unglaubliche Features kleiner Preis, kleine Größe, lange Akku-Lebensdauer Mobiltelefonie zusätzlich Mixed-Signal Design Automotive extreme Anforderungen bezügl. Sicherheit & Preis 14 A. Steininger TU Vienna

Die Herausforderungen Miniaturisierung n mixed signal, dynamische Rekonfiguration, Energiebudget n Rekonfiguration, power management, … Komplexität n Interfaces, formale Verifikation Produktivität / Time to market n Abstraktionsebenen, Automatisierung Fehlertoleranz 15 A. Steininger TU Vienna

Ziel der VO + LU Bewusst-Machen der Problematik Analysieren der Trade-offs Verständnis für den Optimierungsprozess, dessen Kriterien und Randbedingungen Vermitteln erster eigener Erfahrungen Non-Target: Kennenlernen bestehender Tools 17 A. Steininger TU Vienna

Termine Vorlesung 28. 4. 30. 4. 5. 5. 7. 5. 14. 5. 26. 5. 28. 5. 2. 6. 4. 6. 18 VB + allg. Einführung Kostenfaktoren & Constraints (WAS? ) Hardware vs. Software (WIE? ) Erklärung der Übungsaufgabe Gastvortrag DI. Scheurer Trends im Systemdesign Gastvortrag DI. Armengaud Gastvortrag Prof. Rupp Gastvortrag Dr. Knerr, Dr. Holzer A. Steininger TU Vienna

Gastvortrag Dipl. -Ing. Dieter Scheurer n n Managing Director Gleichmann Electronics Research Austria „Debugging mittels Semulator“ 14. Mai 2008, Seminarraum TI 19 A. Steininger TU Vienna

Gastvortrag Dipl. -Ing. Eric Armengaud n n Projektleiter Das Virtuelle Fahrzeug (Graz) „Detailed simulation on application level“ 28. Mai 2008, Seminarraum TI 20 A. Steininger TU Vienna

Gastvortrag Prof. Markus Rupp n n Institut für Nachrichtentechnik und HF-Technik Leiter des CD Labors „Design Methodology of Signal Processing Algorithms“ „The Chip Design Crisis“ 2. Juni 2008, Seminarraum TI 21 A. Steininger TU Vienna

Gastvortrag Dr. Knerr & Dr. Holzer n n Institut für Nachrichtentechnik und HF-Technik Dissertanten im CD Labor „Design Methodology of Signal Processing Algorithms“ Zusammenfassung der Dissertationen 4. Juni 2008, Seminarraum TI 22 A. Steininger TU Vienna