Chapter 5 Synchronous Sequential Logic Part 3 Originally

- Slides: 32

Chapter 5: Synchronous Sequential Logic – Part 3 Originally Wafa Alrajhi Imam Muhammad Bin Saud University

Outline q State reduction. q State assignment. q Design procedure Design with D FF. � Design with JK FF. � Design with T FF. � 2

State Reduction Ø This section discusses certain properties of sequential circuits that may be used to reduce the number of gates and flip-flops during the design Ø State reduction: The reduction of the number of flip-flops in a sequential circuit is referred to as the state-reduction problem Ø State-reduction algorithms are concerned with procedures for reducing the number of states in a state table, while keeping the external input-output requirements unchanged 3

State Reduction (Cont. ) Ø We explain with a sequential circuit whose state diagram is given in the next slide Ø Here, only input-output sequence is important, not the internal states Ø The states are denoted by letters 4

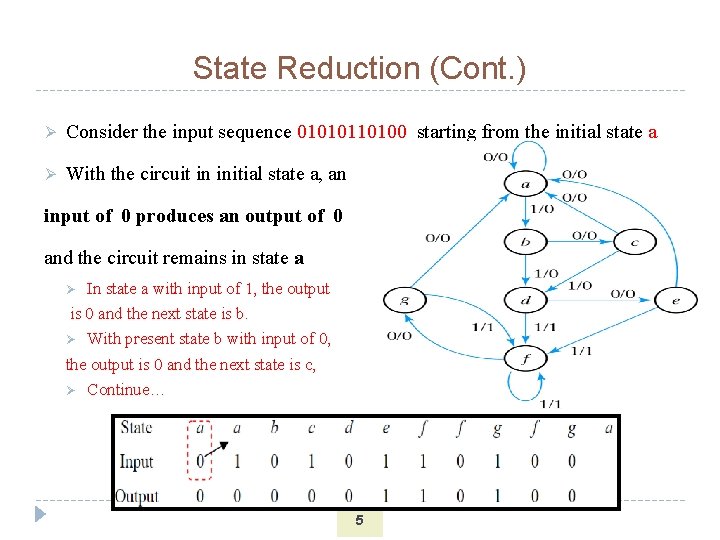

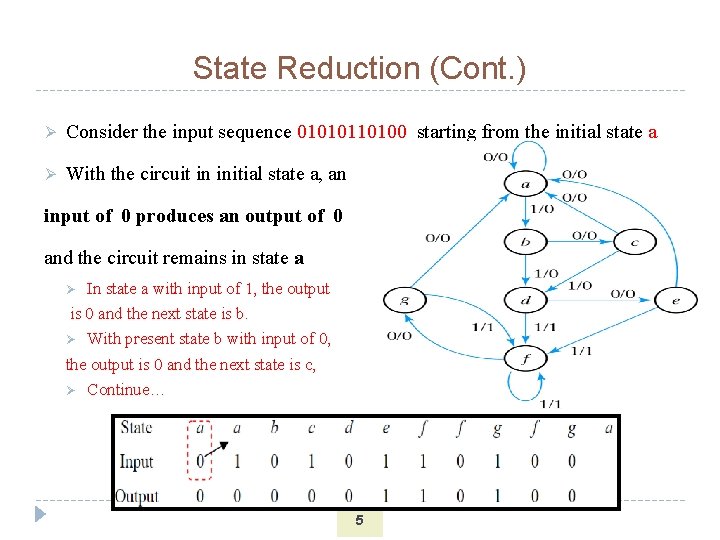

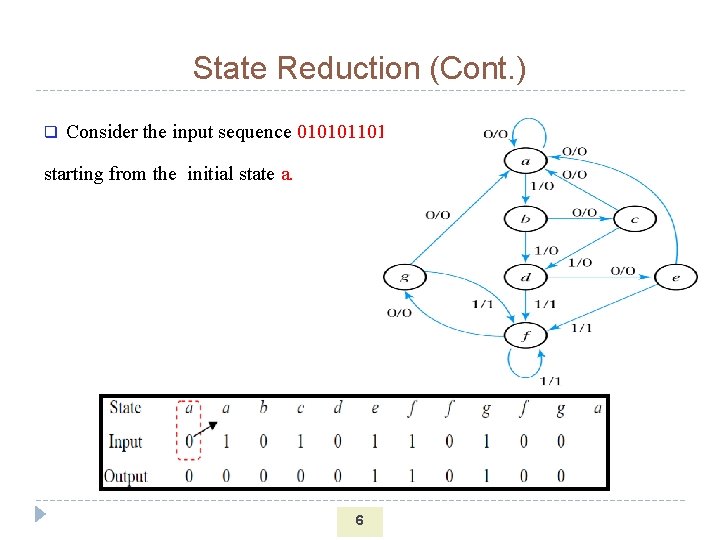

State Reduction (Cont. ) Ø Consider the input sequence 01010110100 starting from the initial state a Ø With the circuit in initial state a, an input of 0 produces an output of 0 and the circuit remains in state a In state a with input of 1, the output is 0 and the next state is b. Ø With present state b with input of 0, the output is 0 and the next state is c, Ø Continue… Ø 5

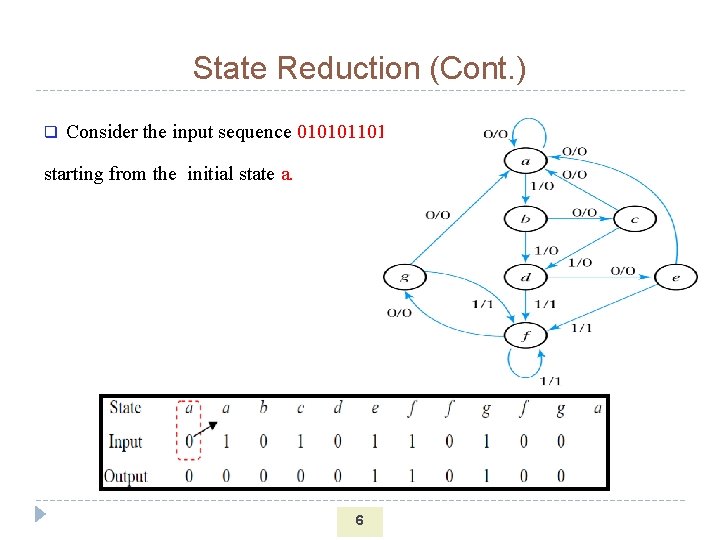

State Reduction (Cont. ) q Consider the input sequence 01010110100 starting from the initial state a. 6

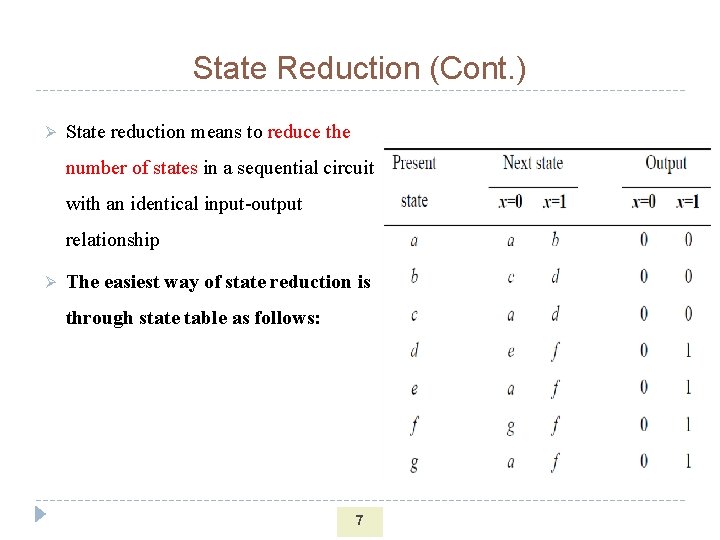

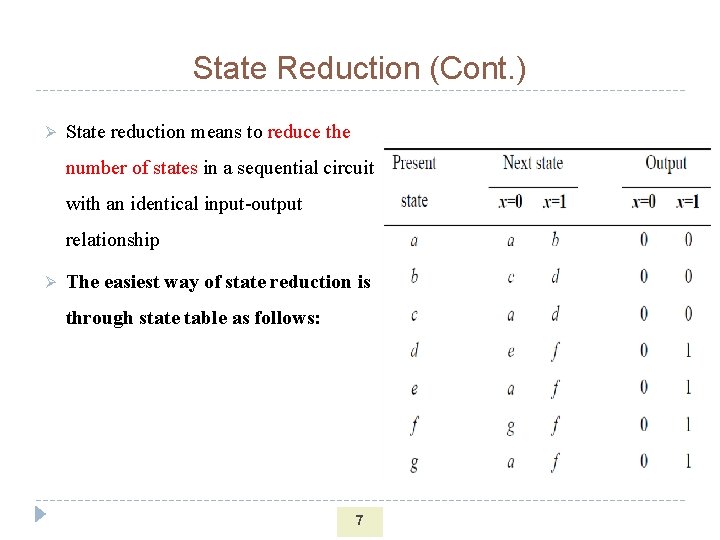

State Reduction (Cont. ) Ø State reduction means to reduce the number of states in a sequential circuit with an identical input-output relationship Ø The easiest way of state reduction is through state table as follows: 7

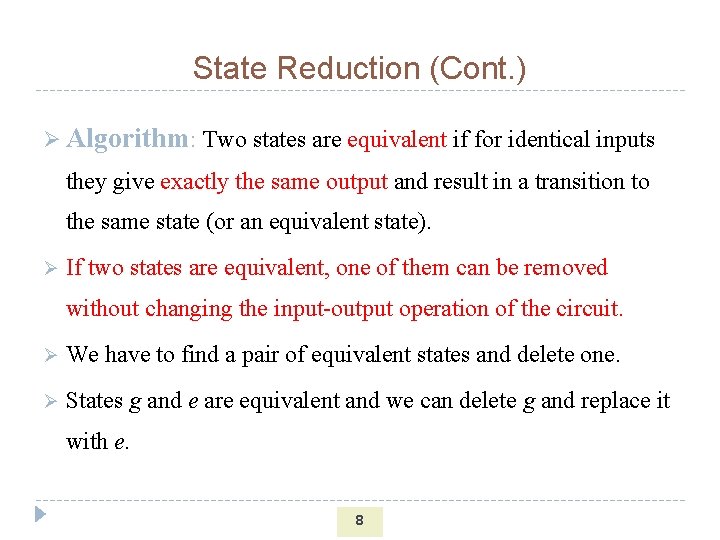

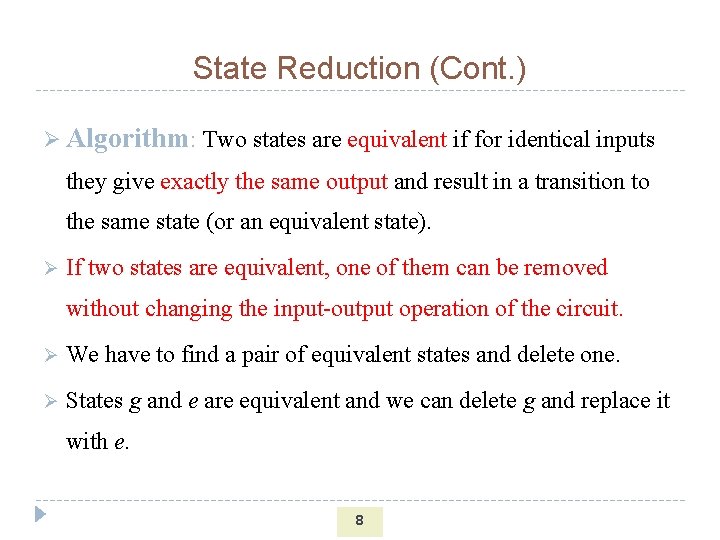

State Reduction (Cont. ) Ø Algorithm: Two states are equivalent if for identical inputs they give exactly the same output and result in a transition to the same state (or an equivalent state). Ø If two states are equivalent, one of them can be removed without changing the input-output operation of the circuit. Ø We have to find a pair of equivalent states and delete one. Ø States g and e are equivalent and we can delete g and replace it with e. 8

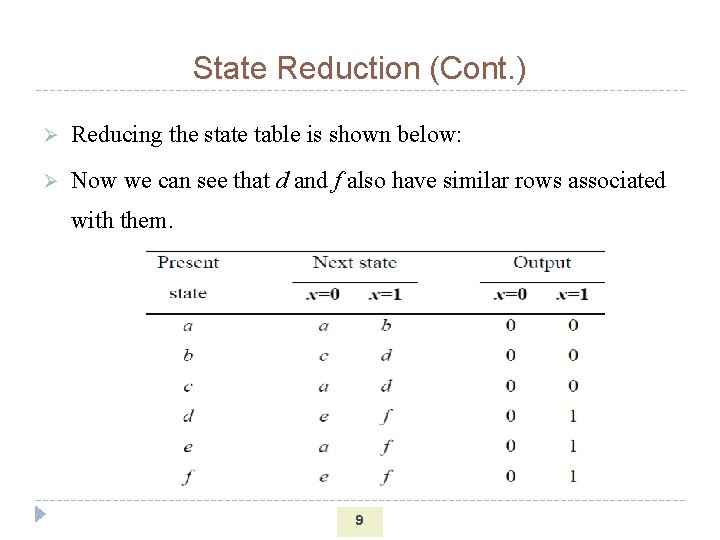

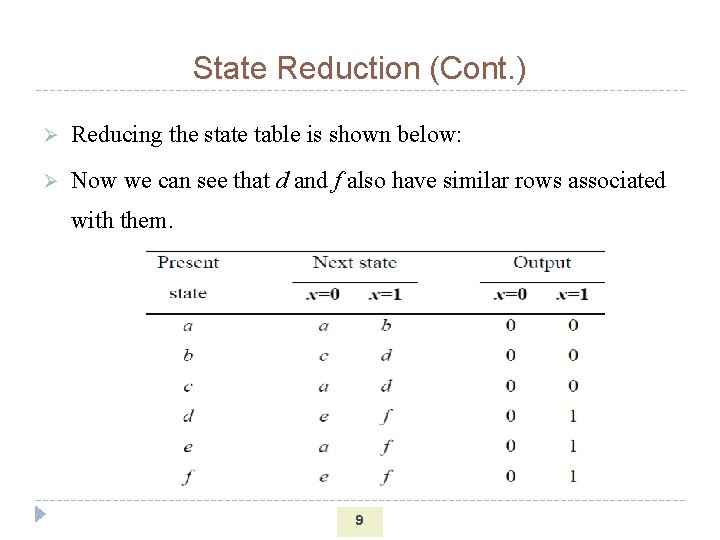

State Reduction (Cont. ) Ø Reducing the state table is shown below: Ø Now we can see that d and f also have similar rows associated with them. 9

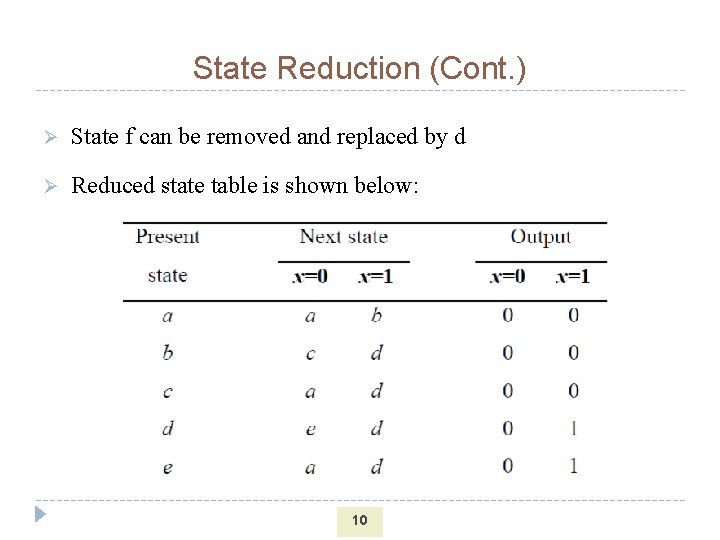

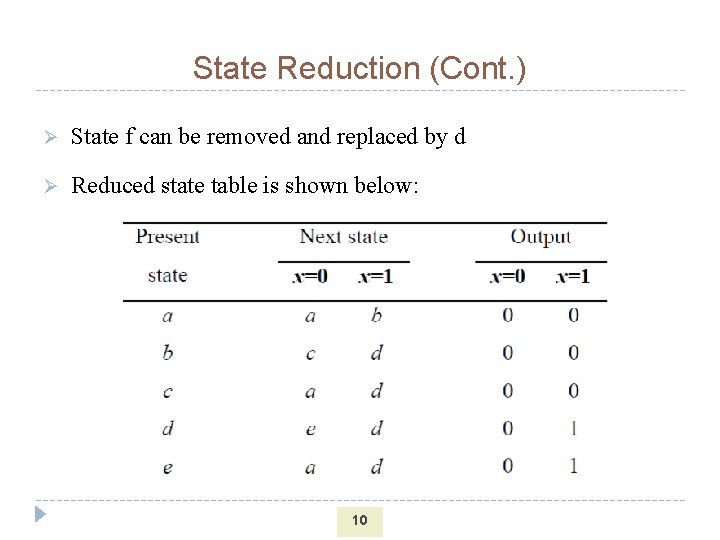

State Reduction (Cont. ) Ø State f can be removed and replaced by d Ø Reduced state table is shown below: 10

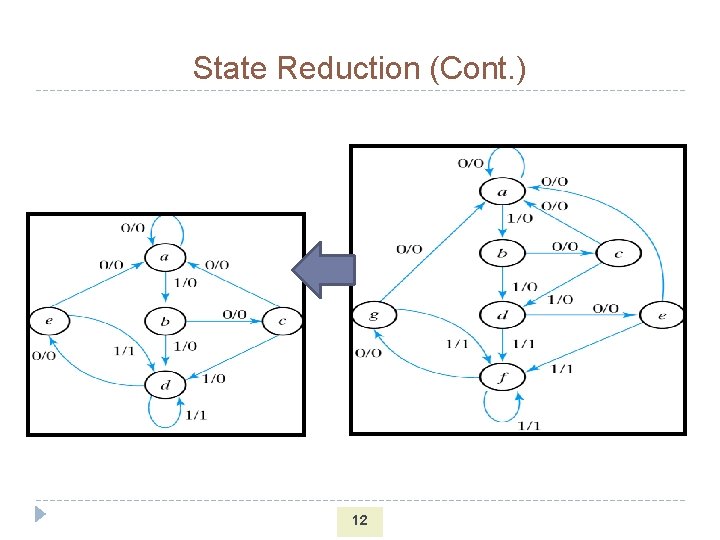

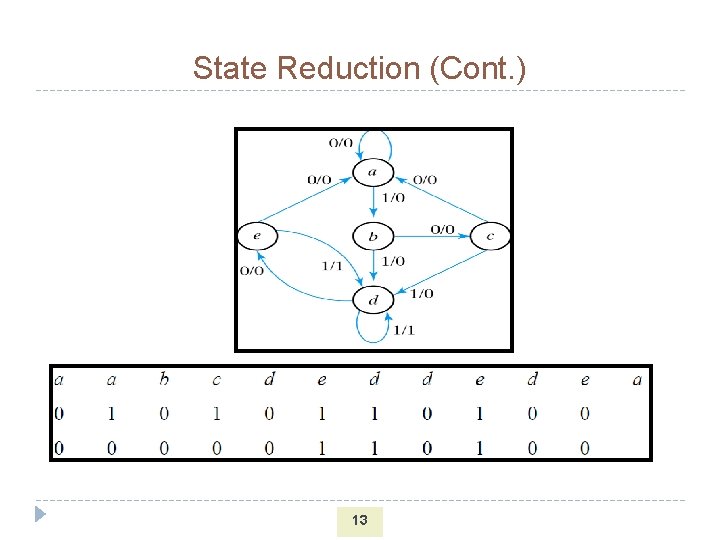

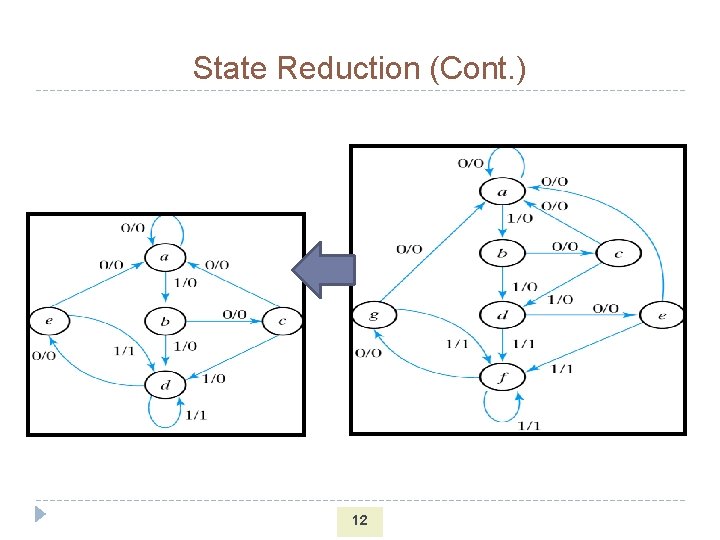

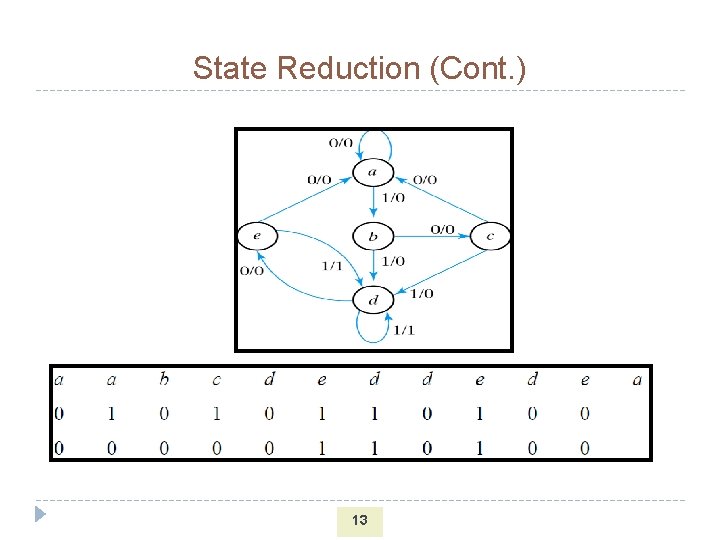

State Reduction (Cont. ) Ø Reducing the number of states does not necessarily mean a circuit with fewer gates and/or flip-flops. Ø Note that state reduction in general may lead to a circuit with more gates than the original system (for the combinational circuit which provides inputs to the flip-flops) Ø For the above reduced diagram and the input sequence that was given before, we have: 11

State Reduction (Cont. ) 12

State Reduction (Cont. ) 13

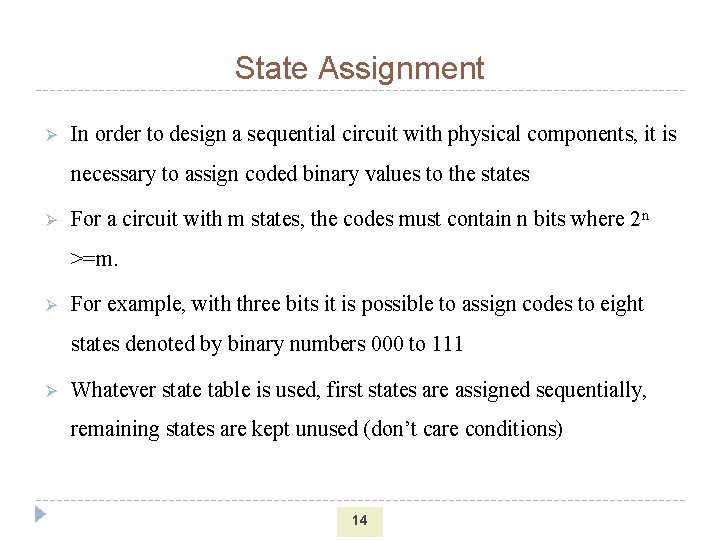

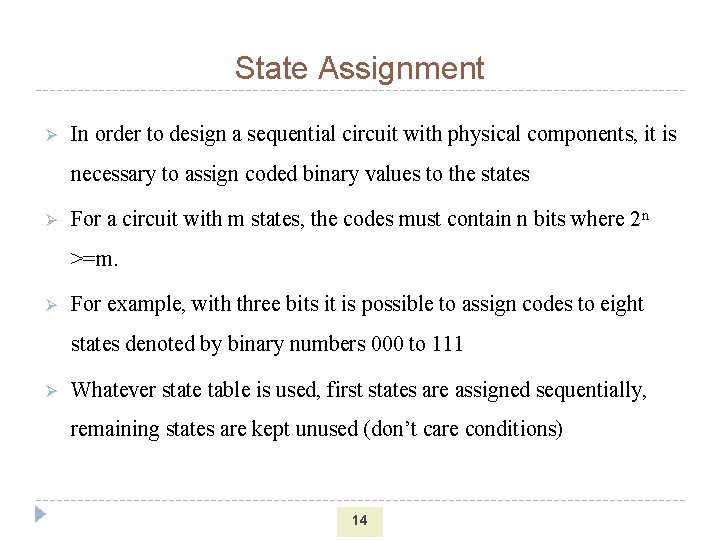

State Assignment Ø In order to design a sequential circuit with physical components, it is necessary to assign coded binary values to the states Ø For a circuit with m states, the codes must contain n bits where 2 n >=m. Ø For example, with three bits it is possible to assign codes to eight states denoted by binary numbers 000 to 111 Ø Whatever state table is used, first states are assigned sequentially, remaining states are kept unused (don’t care conditions) 14

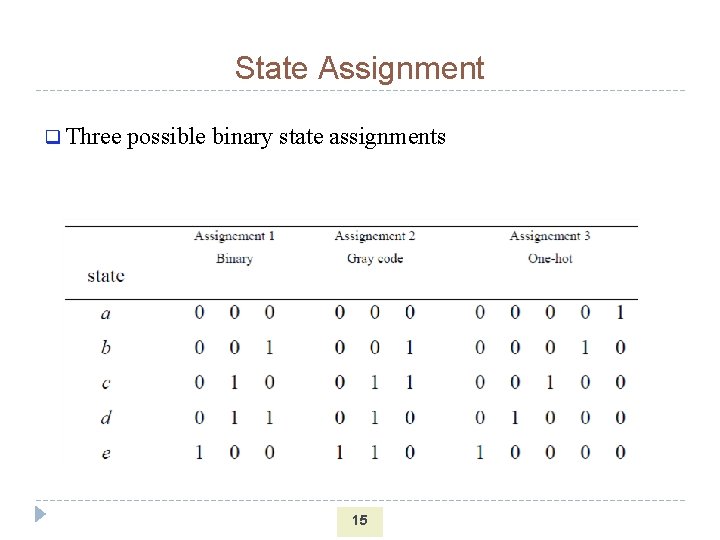

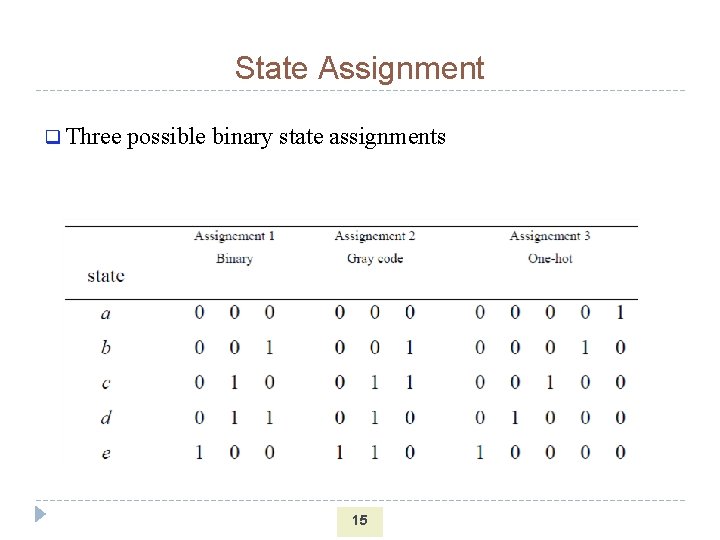

State Assignment q Three possible binary state assignments 15

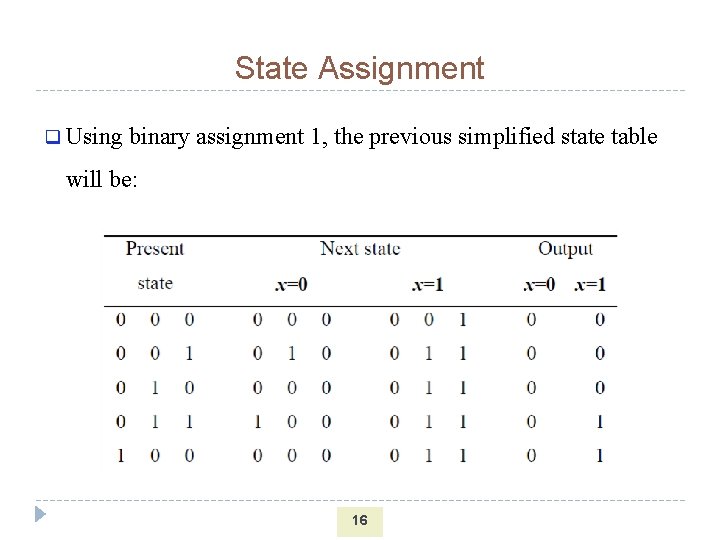

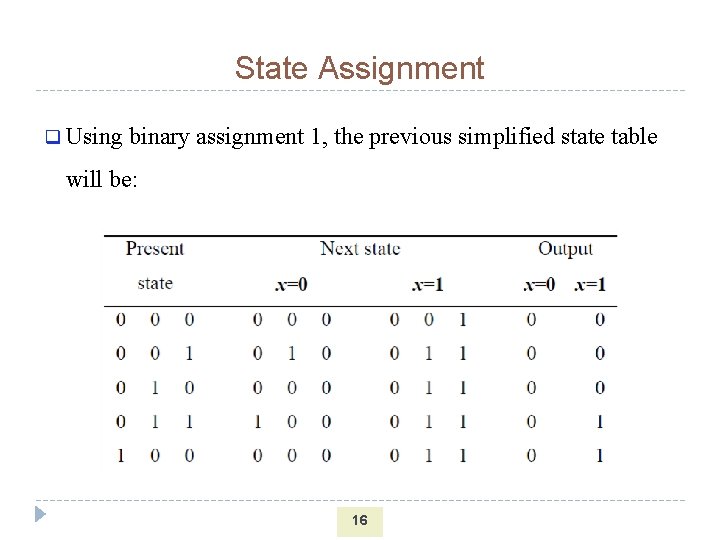

State Assignment q Using binary assignment 1, the previous simplified state table will be: 16

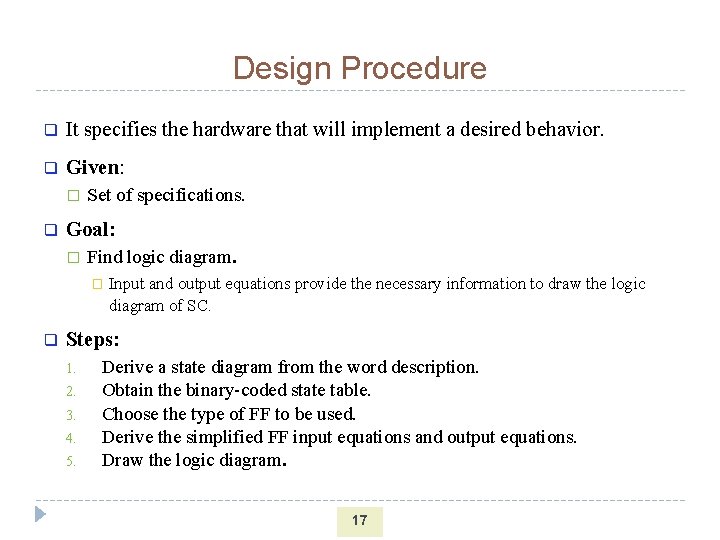

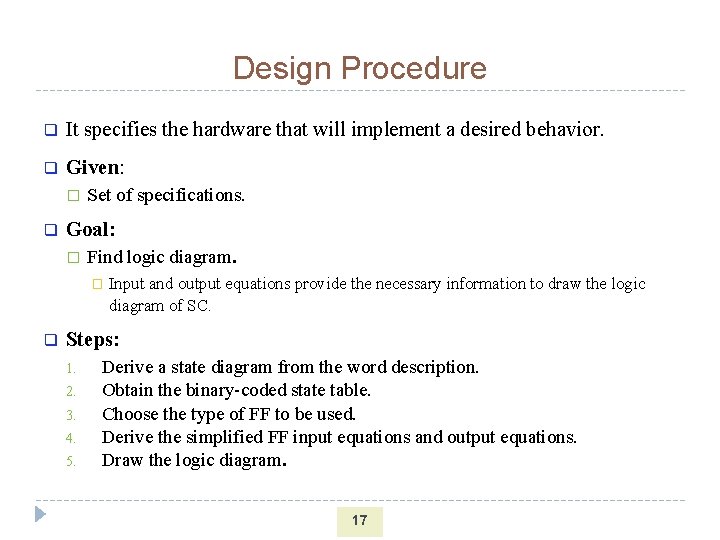

Design Procedure q It specifies the hardware that will implement a desired behavior. q Given: � q Set of specifications. Goal: � Find logic diagram. � q Input and output equations provide the necessary information to draw the logic diagram of SC. Steps: 1. 2. 3. 4. 5. Derive a state diagram from the word description. Obtain the binary-coded state table. Choose the type of FF to be used. Derive the simplified FF input equations and output equations. Draw the logic diagram. 17

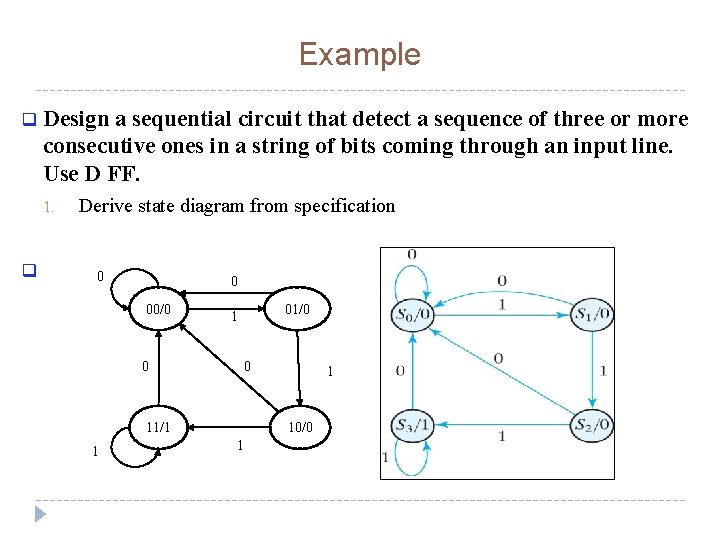

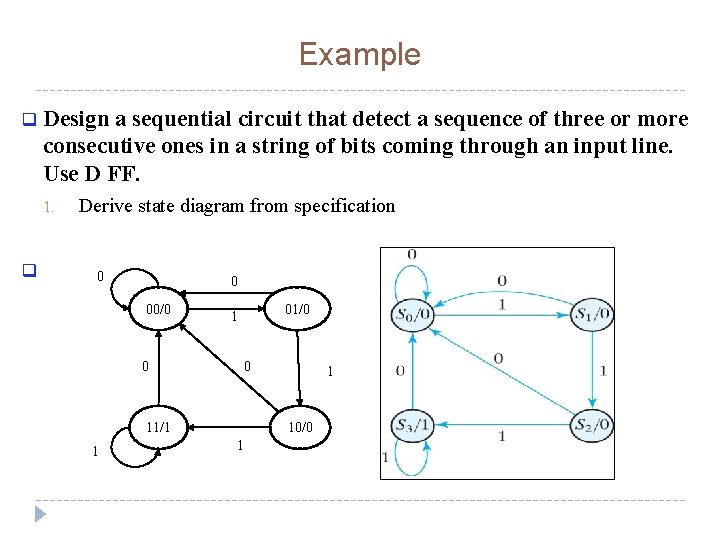

Example q Design a sequential circuit that detect a sequence of three or more consecutive ones in a string of bits coming through an input line. Use D FF. 1. q Derive state diagram from specification 0 0 00/0 0 0 11/1 1 01/0 1 1 10/0 1

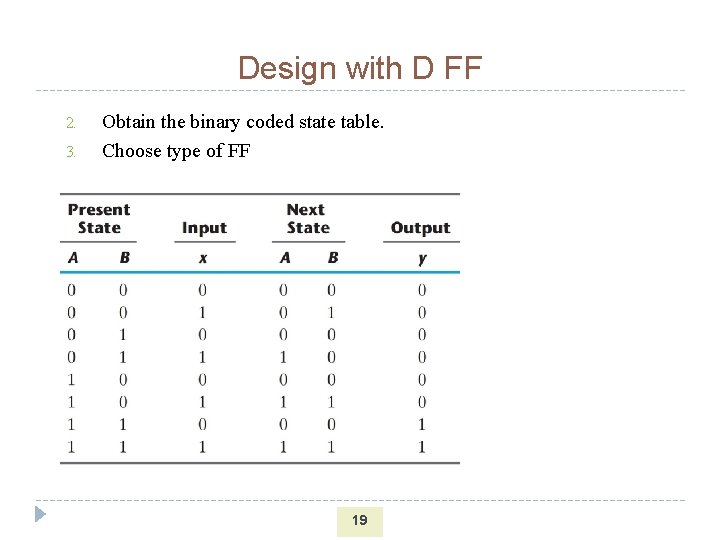

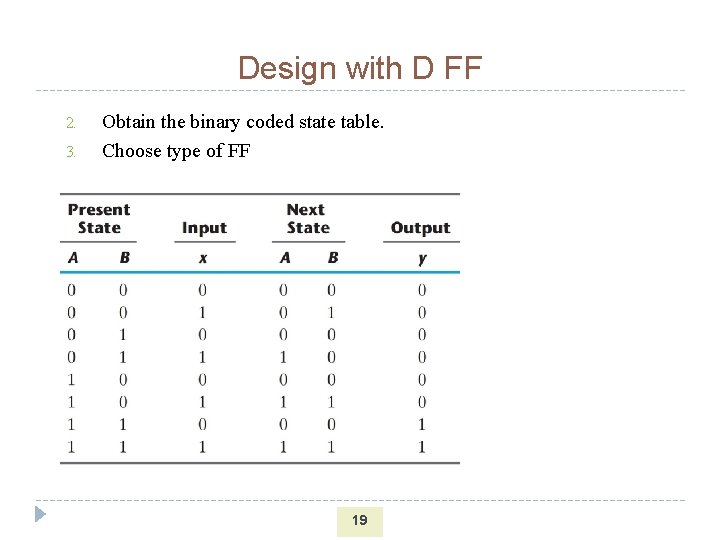

Design with D FF 2. 3. Obtain the binary coded state table. Choose type of FF 19

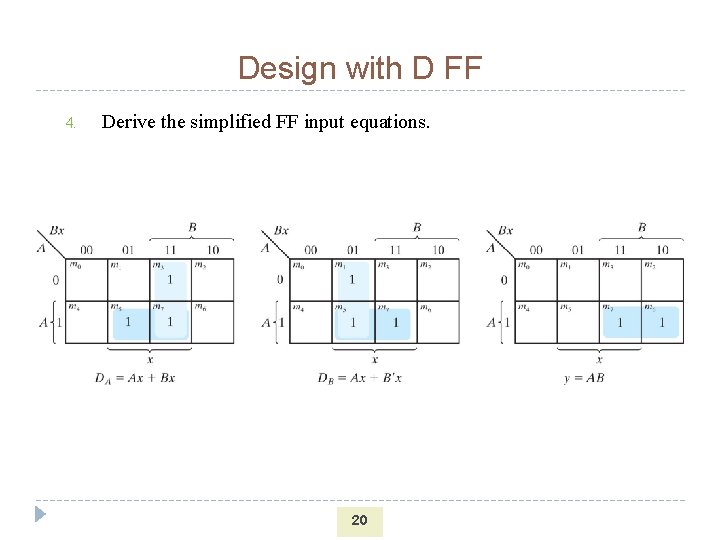

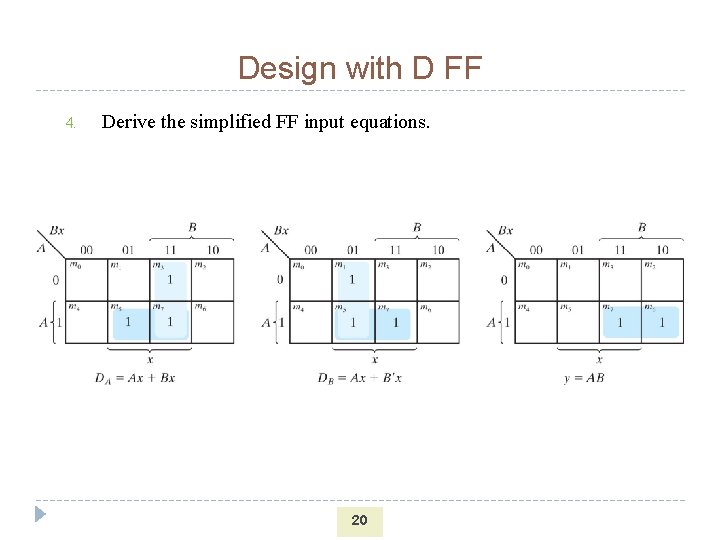

Design with D FF 4. Derive the simplified FF input equations. 20

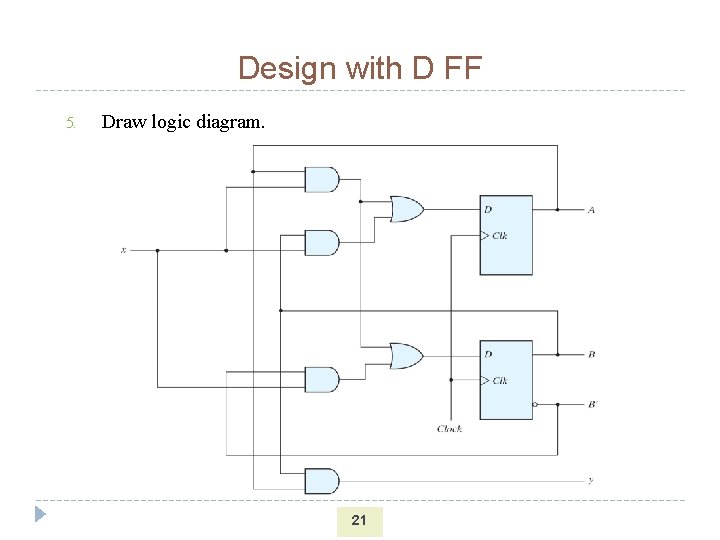

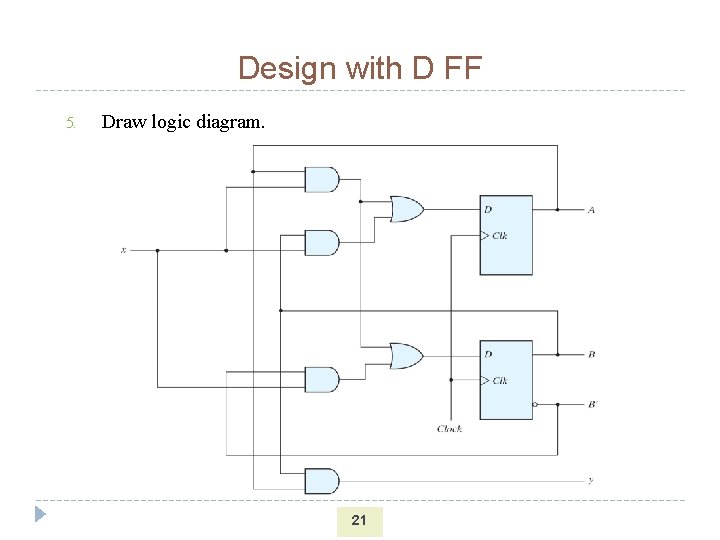

Design with D FF 5. Draw logic diagram. 21

Excitation Table Ø Design with other types of flip-flops is not straightforward as the next state cannot directly be related to the input equations Ø In such cases we should use excitation tables, which list the required input for a given change of state Ø Next slide shows excitation tables for JK & T Flip-Flops Ø The symbol X represents a don’t care condition 22

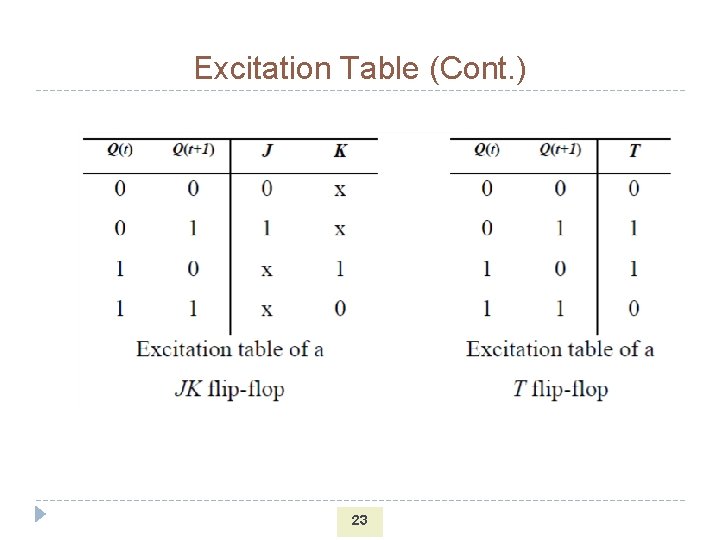

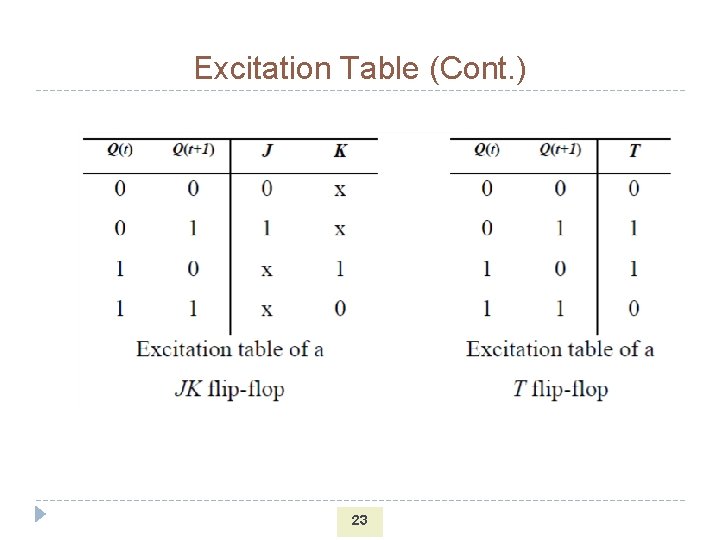

Excitation Table (Cont. ) 23

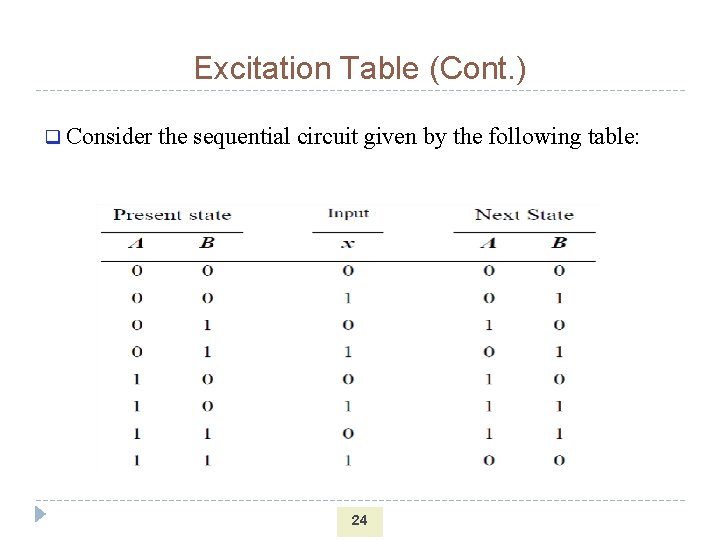

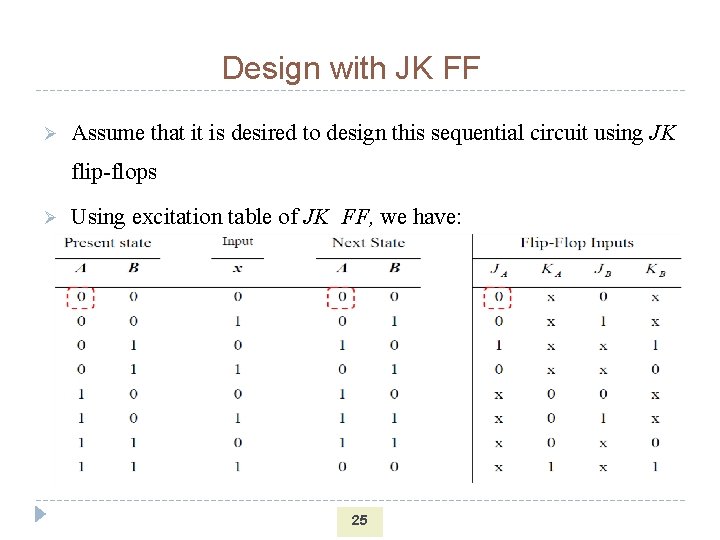

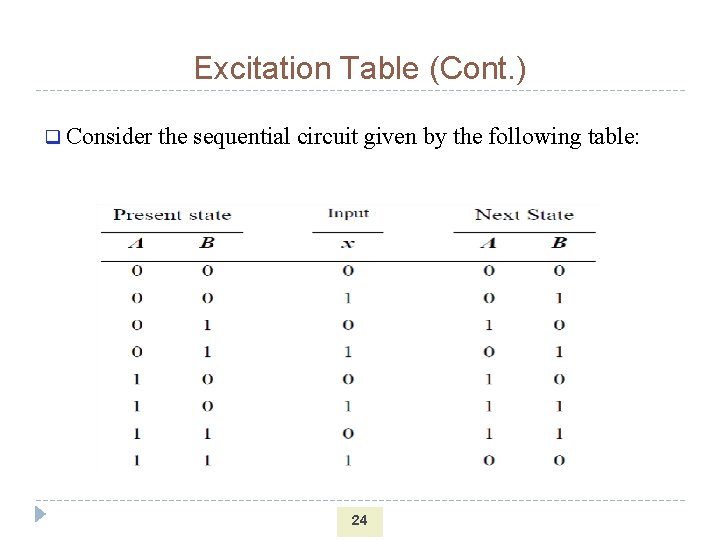

Excitation Table (Cont. ) q Consider the sequential circuit given by the following table: 24

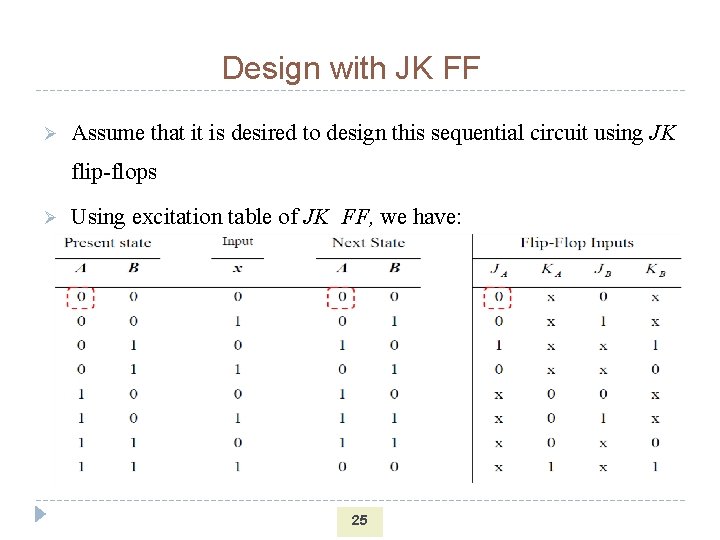

Design with JK FF Ø Assume that it is desired to design this sequential circuit using JK flip-flops Ø Using excitation table of JK FF, we have: 25

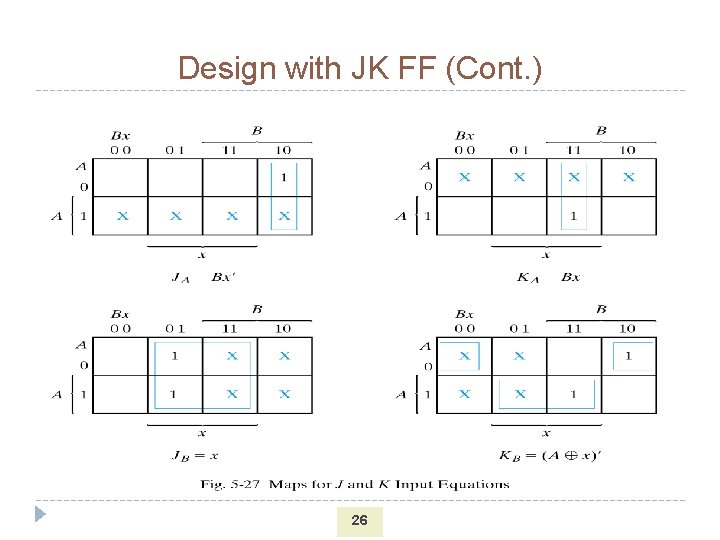

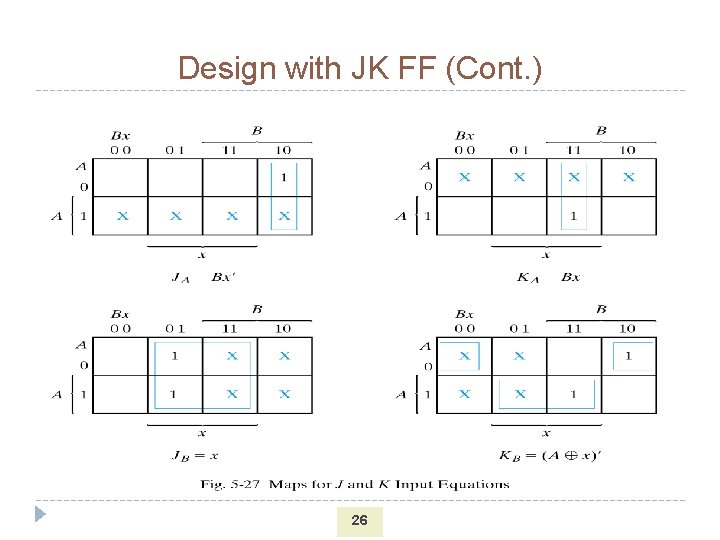

Design with JK FF (Cont. ) 26

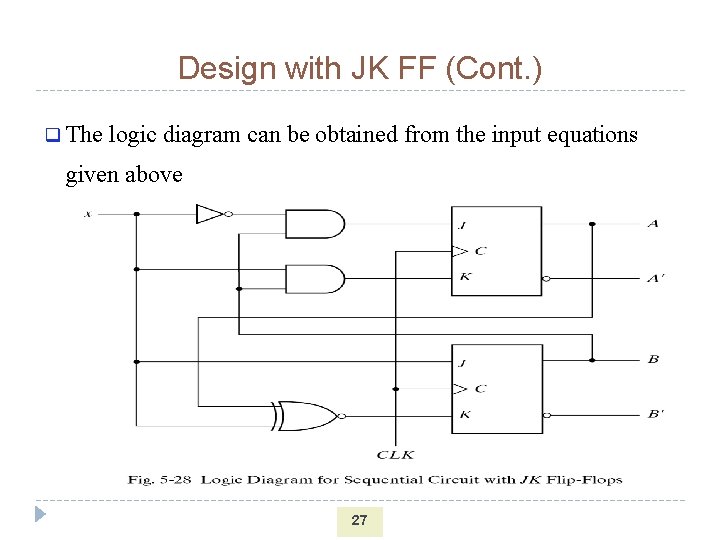

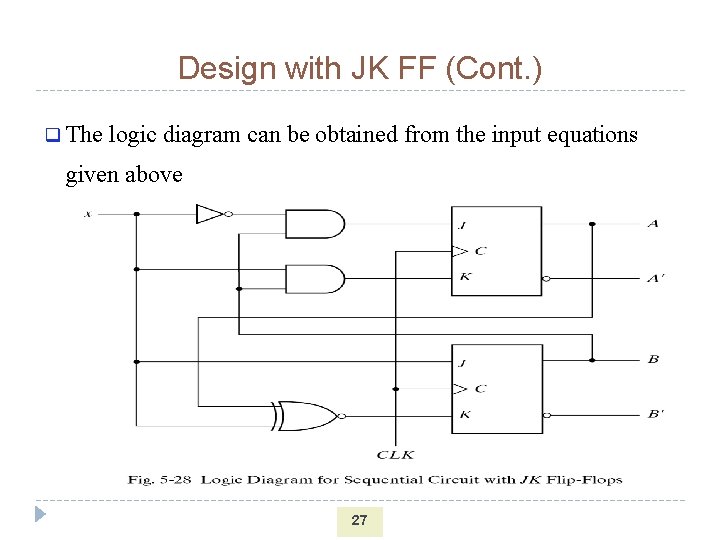

Design with JK FF (Cont. ) q The logic diagram can be obtained from the input equations given above 27

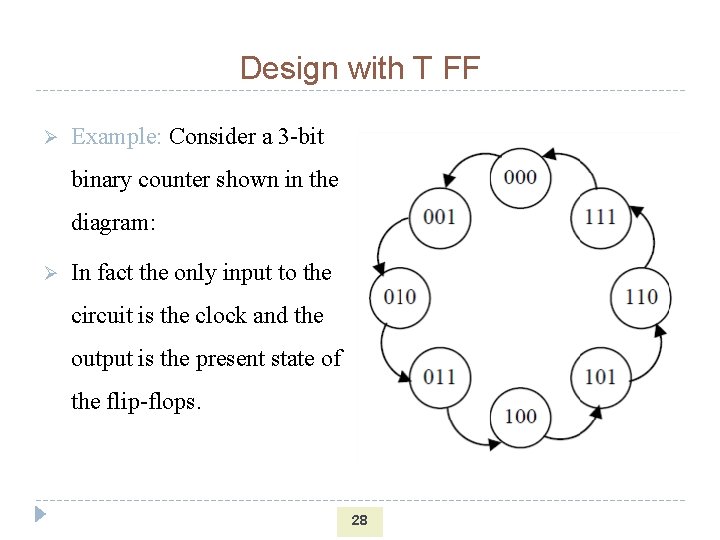

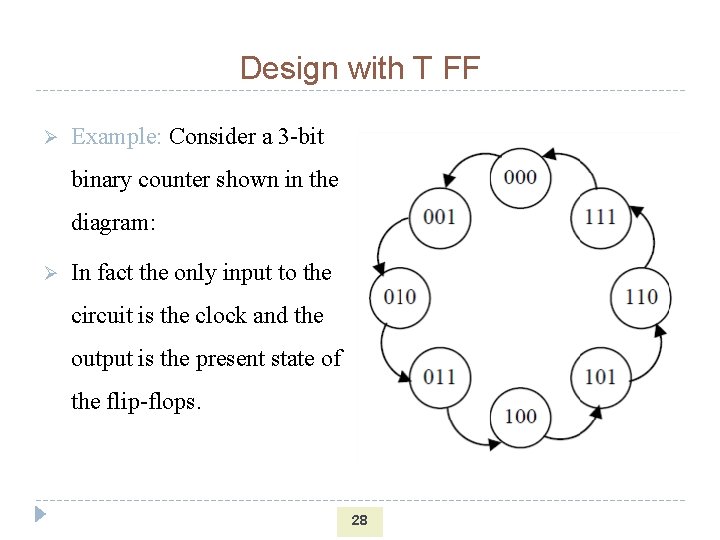

Design with T FF Ø Example: Consider a 3 -bit binary counter shown in the diagram: Ø In fact the only input to the circuit is the clock and the output is the present state of the flip-flops. 28

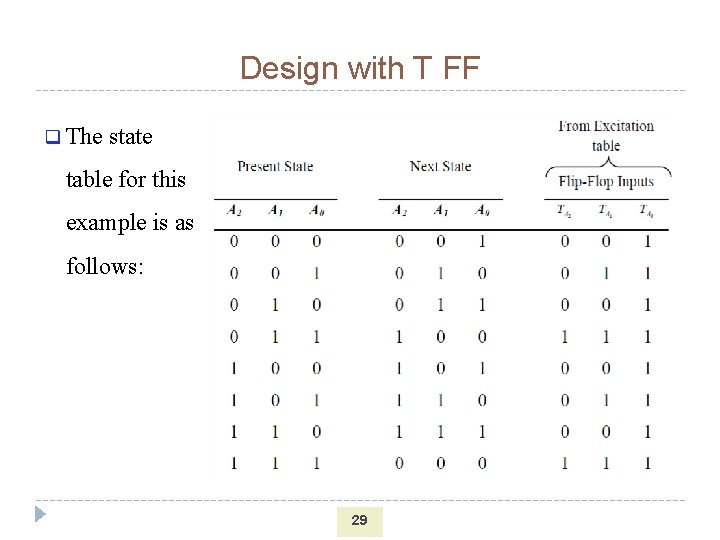

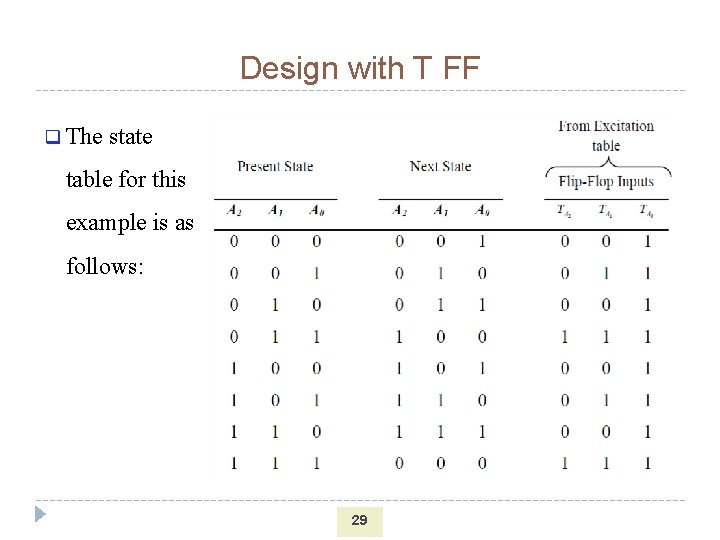

Design with T FF q The state table for this example is as follows: 29

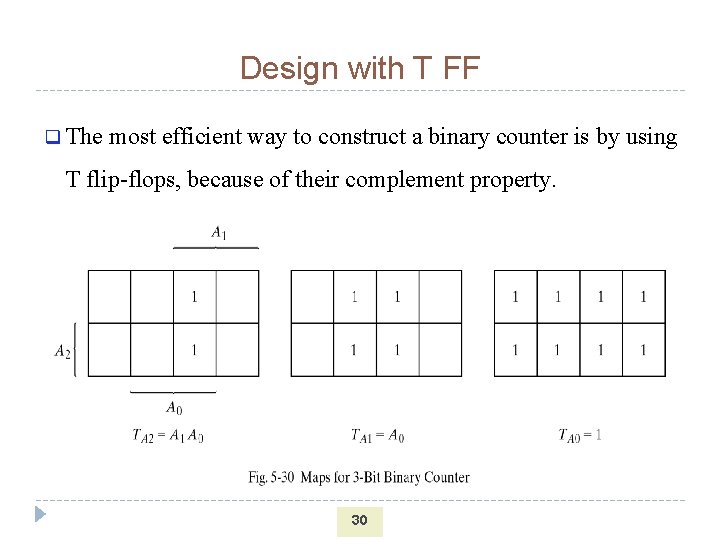

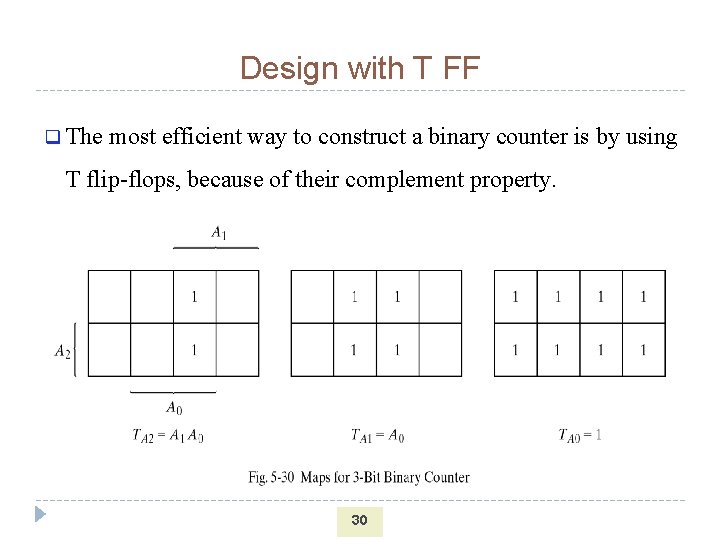

Design with T FF q The most efficient way to construct a binary counter is by using T flip-flops, because of their complement property. 30

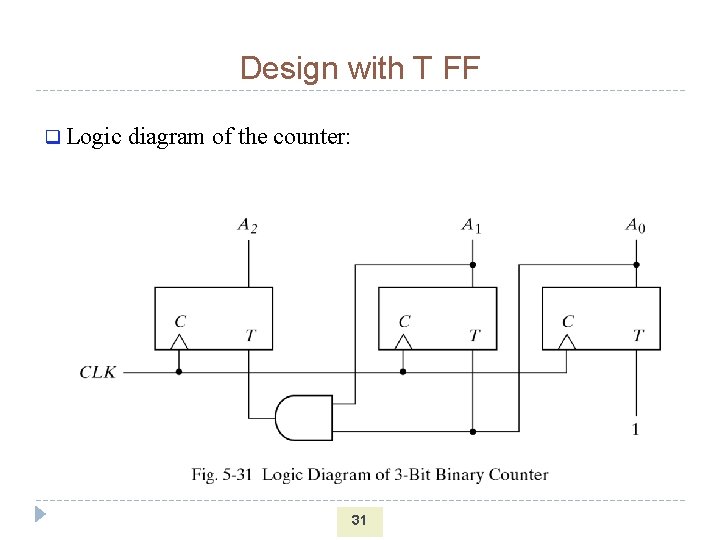

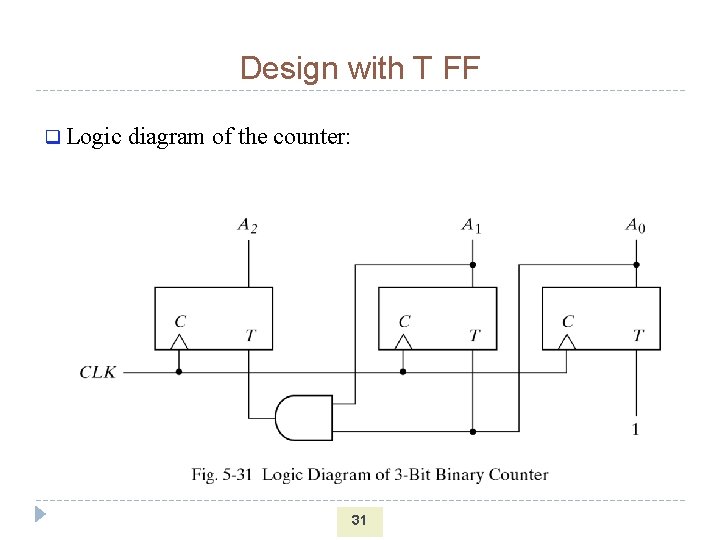

Design with T FF q Logic diagram of the counter: 31

Reading q 5. 1 q 5. 2 q 5. 3 q 5. 4 q 5. 5 q 5. 8 32