AIDEMC Low Emission Digital Circuit Design Department of

- Slides: 24

AID–EMC: Low Emission Digital Circuit Design Department of Electrical Engineering (ESAT) MICAS Update of the “Digital EMC project” March 1 st, 2006 Junfeng Zhou Wim Dehaene KULeuven ESAT-MICAS

Outline Department of Electrical Engineering (ESAT) 1. Test chip finished 2. 2. Theoretical analysis 3. 3. Chip Testing proposal MICAS

done Department of Electrical Engineering (ESAT) MICAS Layout transferred end of january, to be integrated in complete test chip. Taped out is/was when? One last change …

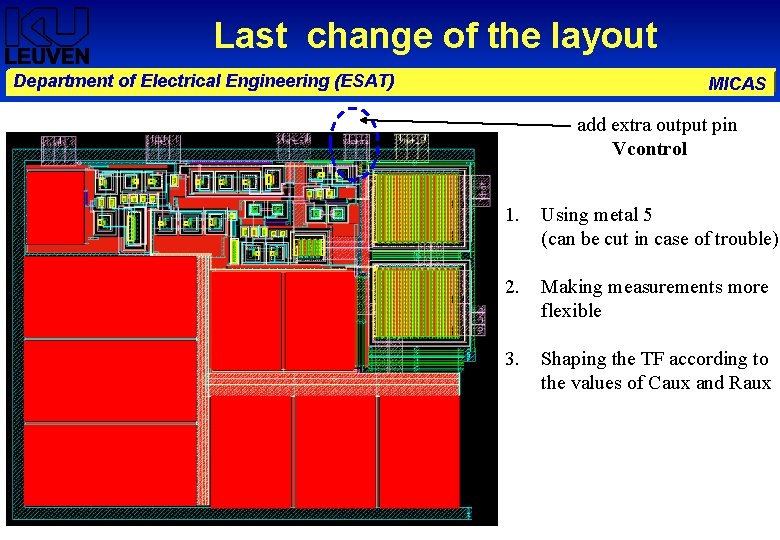

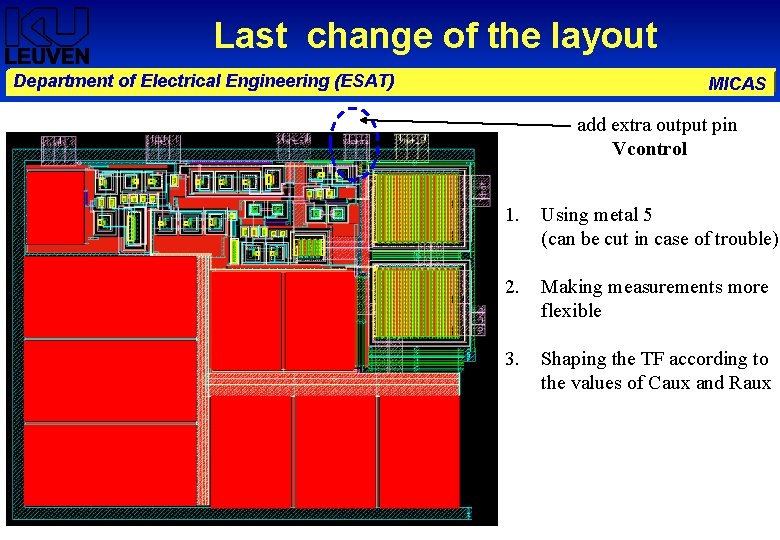

Last change of the layout Department of Electrical Engineering (ESAT) MICAS add extra output pin Vcontrol 1. Using metal 5 (can be cut in case of trouble) 2. Making measurements more flexible 3. Shaping the TF according to the values of Caux and Raux

Outline Department of Electrical Engineering (ESAT) 1. Test chip finished 2. 2. Theoretical analysis 3. 3. Chip Testing proposal MICAS

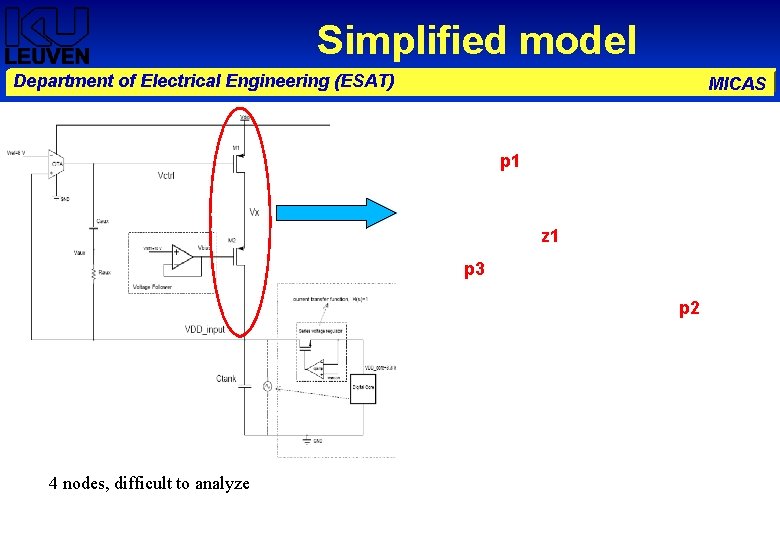

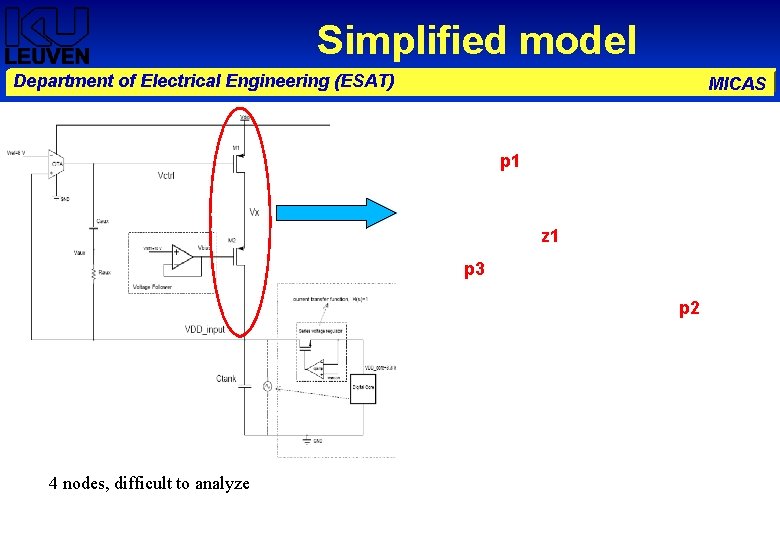

Simplified model Department of Electrical Engineering (ESAT) MICAS p 1 z 1 p 3 p 2 4 nodes, difficult to analyze

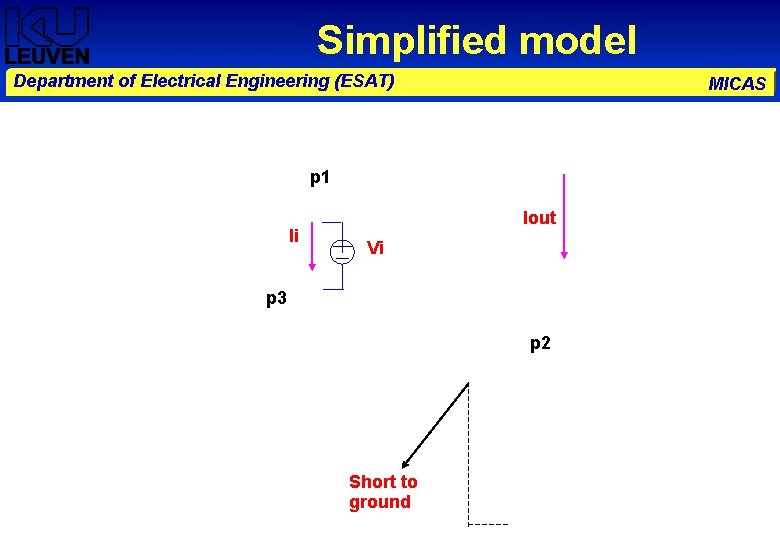

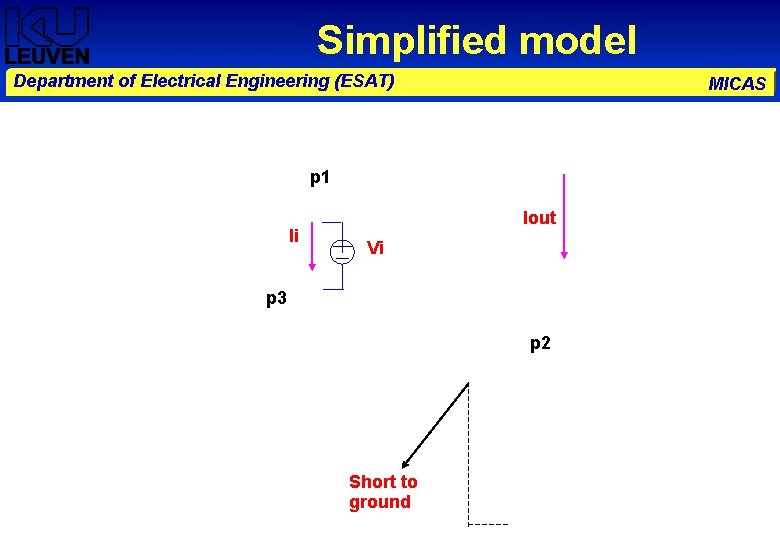

Simplified model Department of Electrical Engineering (ESAT) MICAS p 1 Ii Iout Vi p 3 p 2 Short to ground

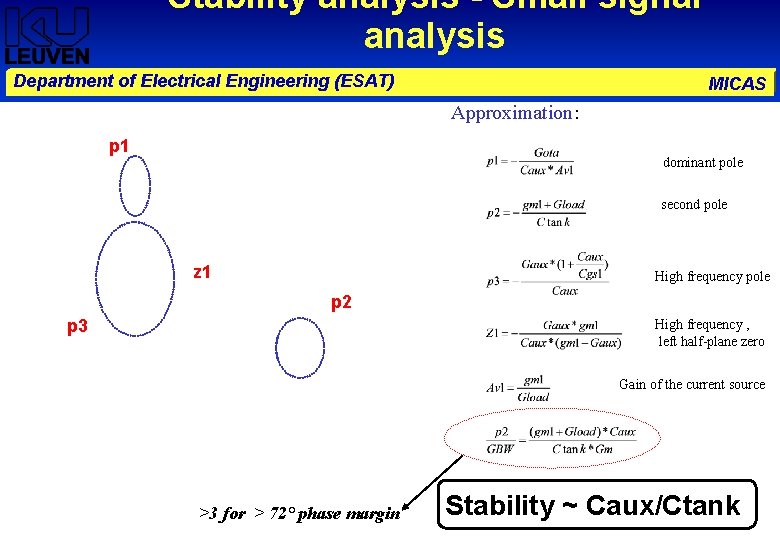

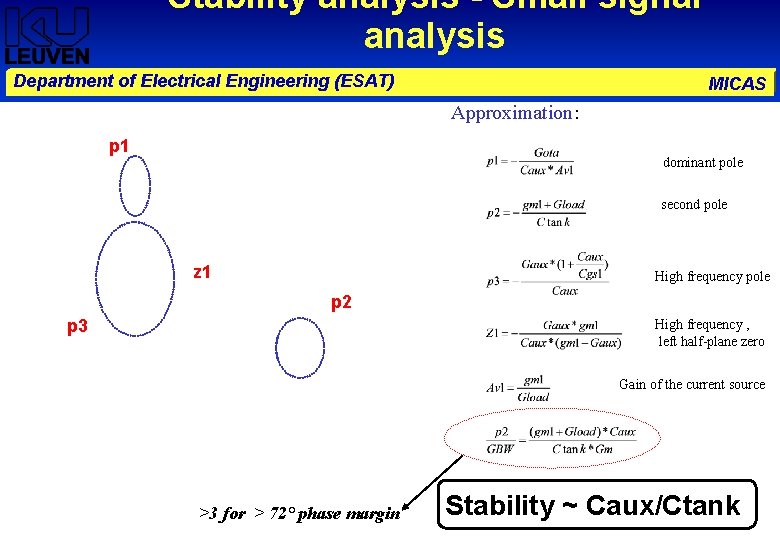

Stability analysis - Small signal analysis Department of Electrical Engineering (ESAT) MICAS Approximation: p 1 dominant pole second pole z 1 High frequency pole p 2 p 3 High frequency , left half-plane zero Gain of the current source >3 for > 72° phase margin Stability ~ Caux/Ctank

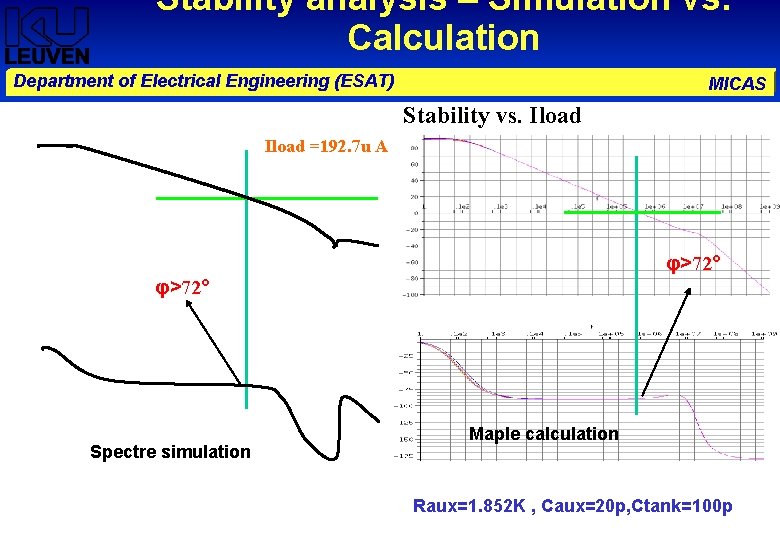

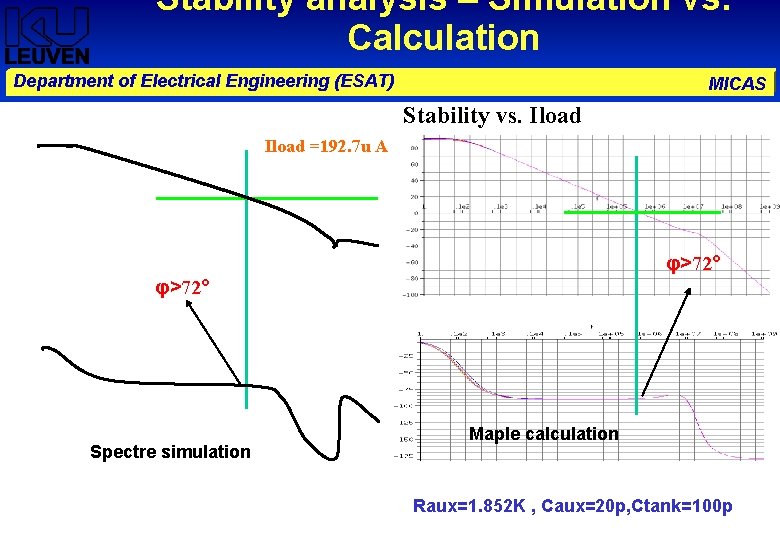

Stability analysis – Simulation vs. Calculation Department of Electrical Engineering (ESAT) MICAS Stability vs. Iload =192. 7 u A φ>72° Spectre simulation Maple calculation Raux=1. 852 K , Caux=20 p, Ctank=100 p

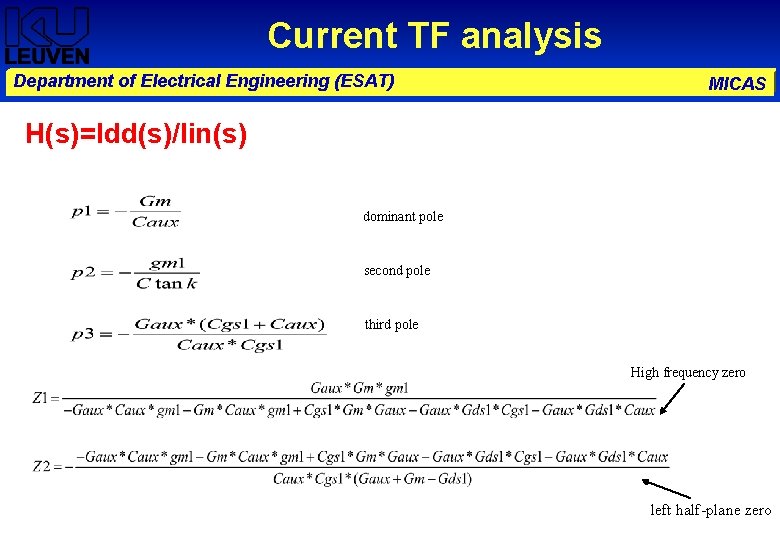

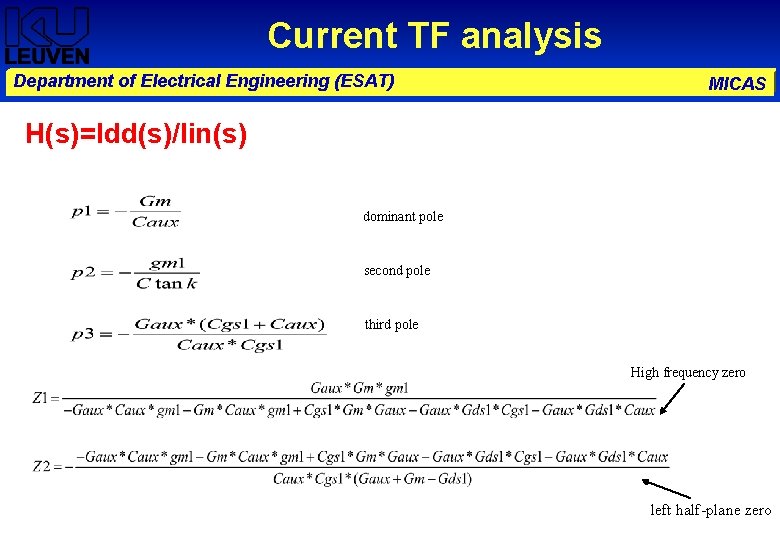

Current TF analysis Department of Electrical Engineering (ESAT) MICAS H(s)=Idd(s)/Iin(s) dominant pole second pole third pole High frequency zero left half-plane zero

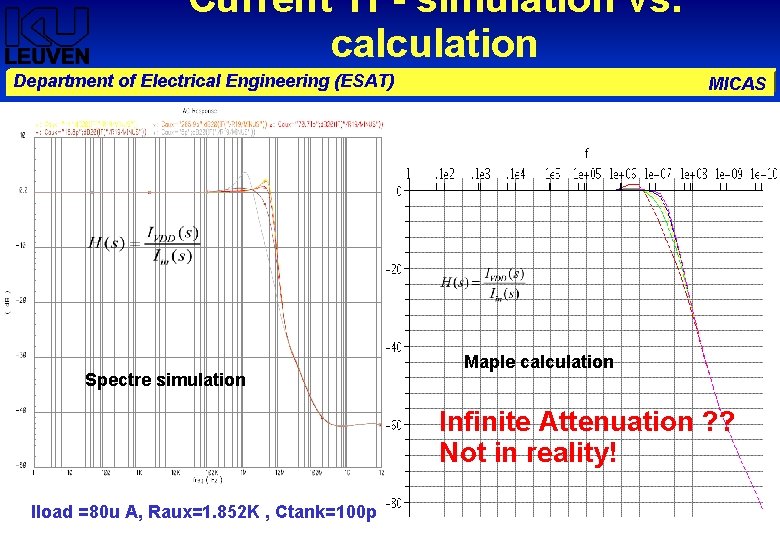

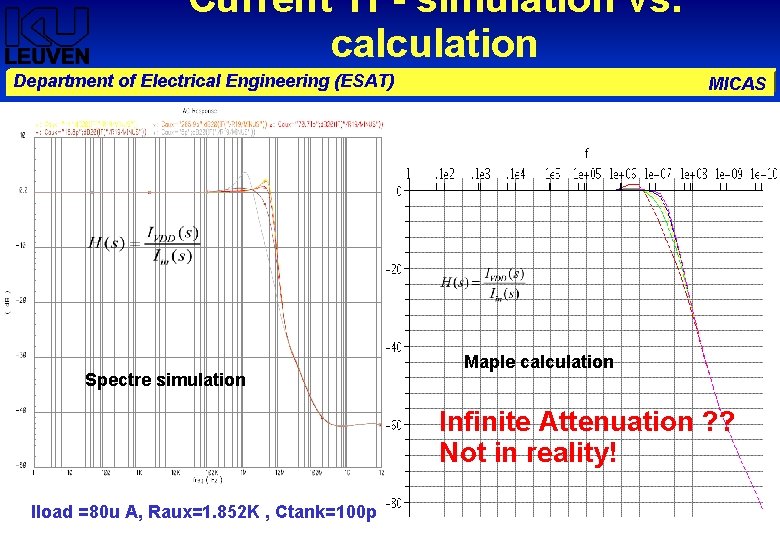

Current TF- simulation vs. calculation Department of Electrical Engineering (ESAT) Spectre simulation MICAS Maple calculation Infinite Attenuation ? ? Not in reality! Iload =80 u A, Raux=1. 852 K , Ctank=100 p

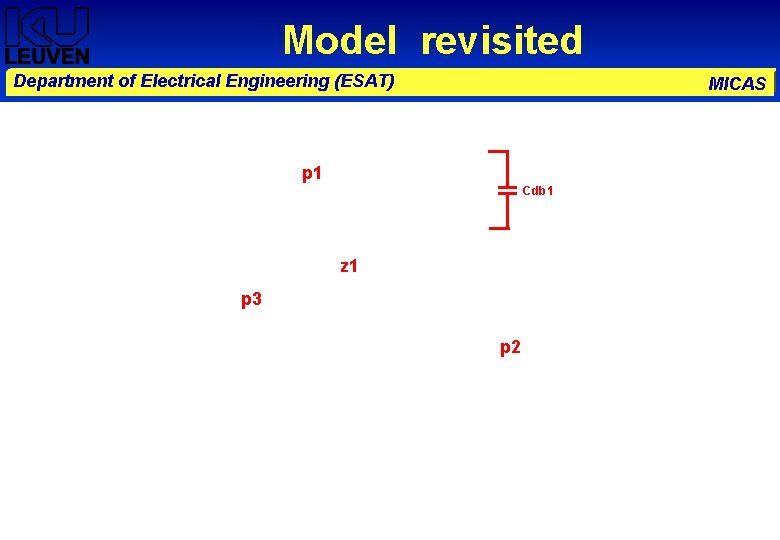

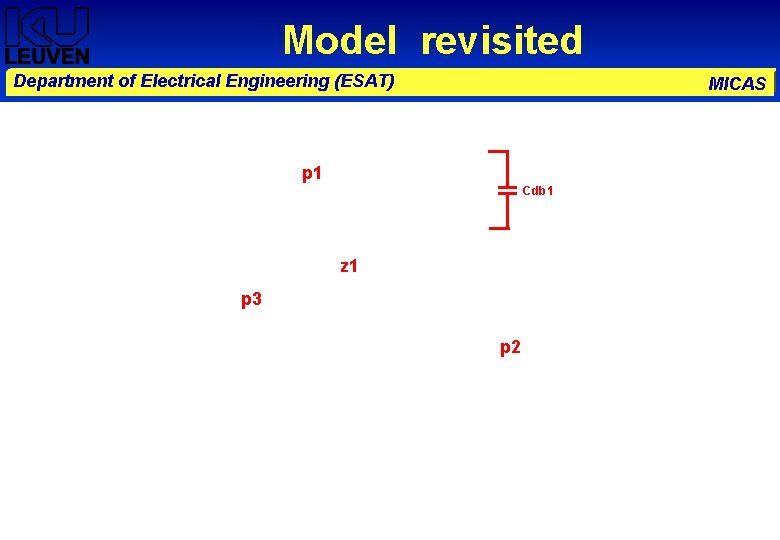

Model revisited Department of Electrical Engineering (ESAT) MICAS p 1 Cdb 1 z 1 p 3 p 2

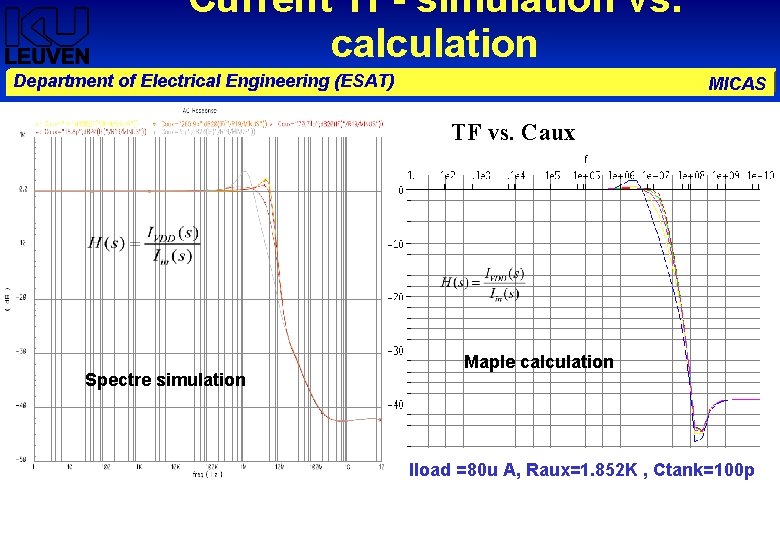

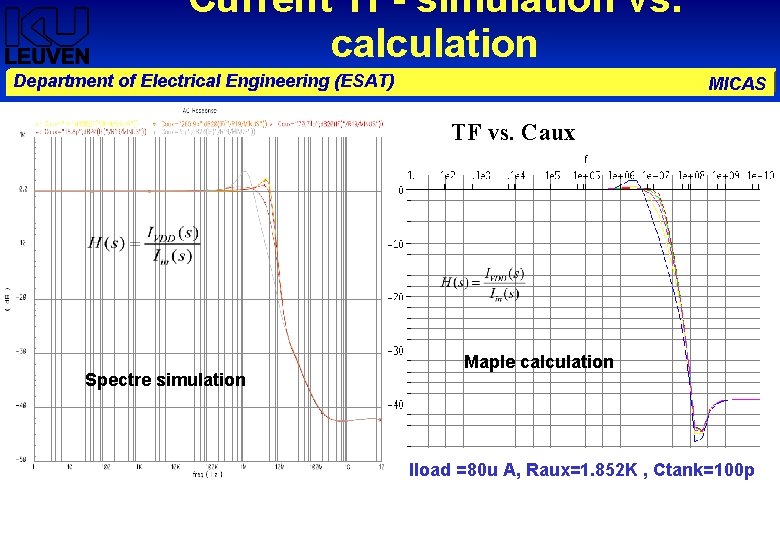

Current TF- simulation vs. calculation Department of Electrical Engineering (ESAT) MICAS TF vs. Caux Spectre simulation Maple calculation Iload =80 u A, Raux=1. 852 K , Ctank=100 p

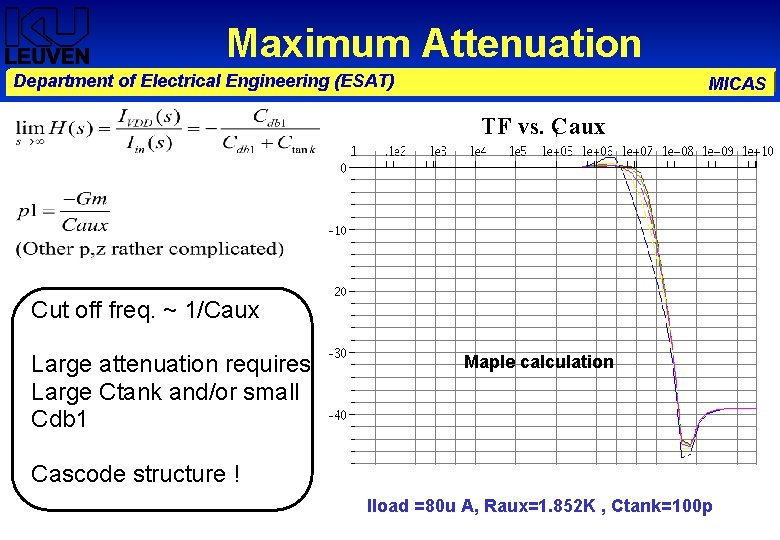

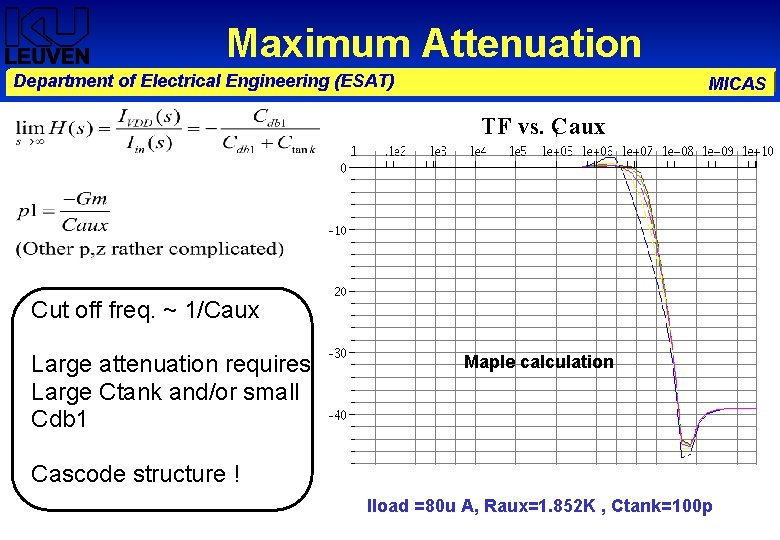

Maximum Attenuation Department of Electrical Engineering (ESAT) MICAS TF vs. Caux Cut off freq. ~ 1/Caux Large attenuation requires Large Ctank and/or small Cdb 1 Maple calculation Cascode structure ! Iload =80 u A, Raux=1. 852 K , Ctank=100 p

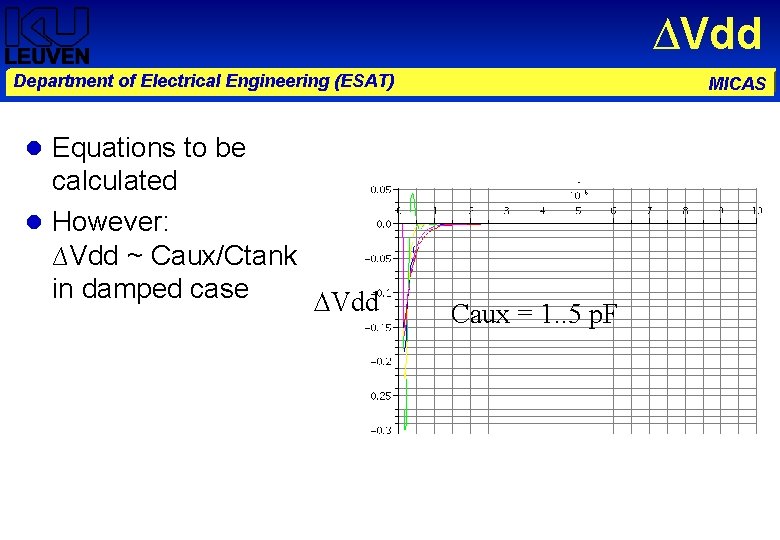

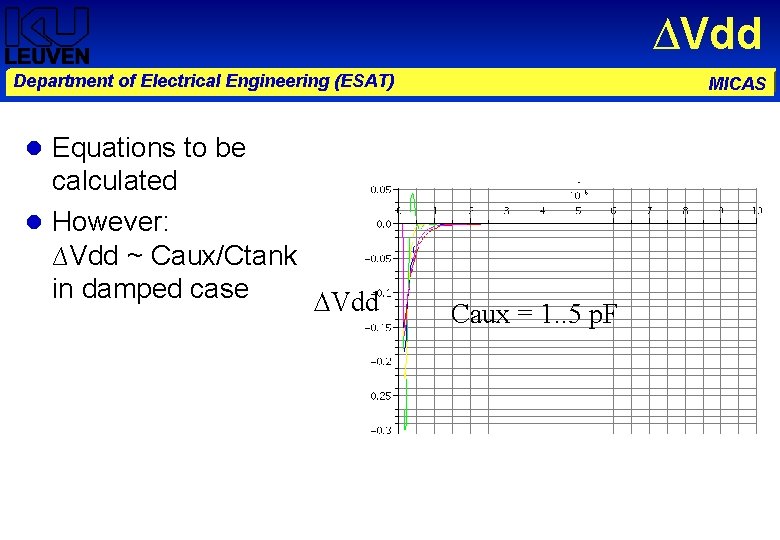

∆Vdd Department of Electrical Engineering (ESAT) MICAS Equations to be calculated However: ∆Vdd ~ Caux/Ctank in damped case ∆Vdd Caux = 1. . 5 p. F

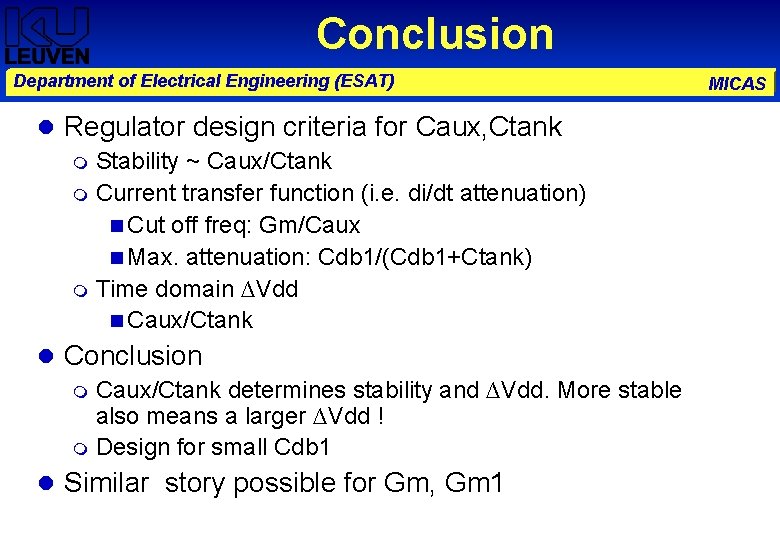

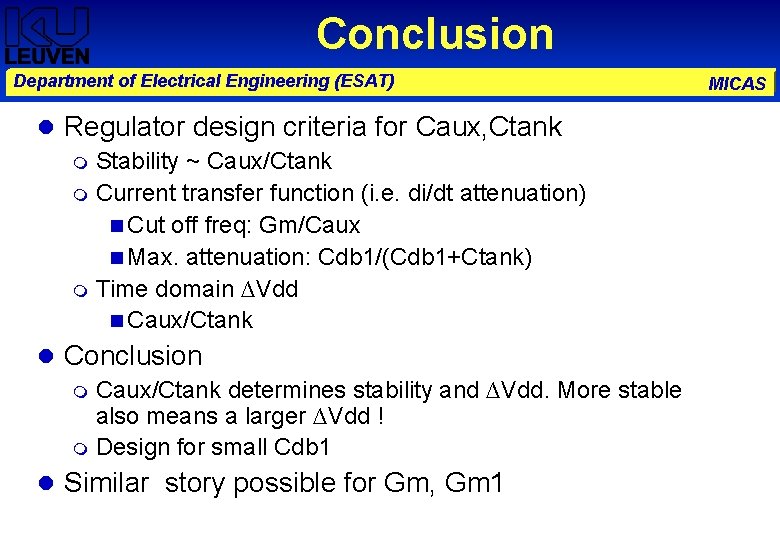

Conclusion Department of Electrical Engineering (ESAT) Regulator design criteria for Caux, Ctank Stability ~ Caux/Ctank Current transfer function (i. e. di/dt attenuation) Cut off freq: Gm/Caux Max. attenuation: Cdb 1/(Cdb 1+Ctank) Time domain ∆Vdd Caux/Ctank Conclusion Caux/Ctank determines stability and ∆Vdd. More stable also means a larger ∆Vdd ! Design for small Cdb 1 Similar story possible for Gm, Gm 1 MICAS

Chip Testing proposal Department of Electrical Engineering (ESAT) Test: 1. List of tests for di/dt 2. Test setup proposal 3. To be designed 4. => test board 5. 3. Will we also do the emission tests ? MICAS

List of tests for di/dt Department of Electrical Engineering (ESAT) MICAS For the special EMC regulator: 1. Current pulse measurement, 2. The current TF as a function of Ctank, Caux 3. Measurement of di/dt reduction vs. Ctank, Caux and decoupling cap, 4. Influence of different loads provided by AMIS -- D-FF or MS-FF -- number of gates -- distributed clocks over time ……

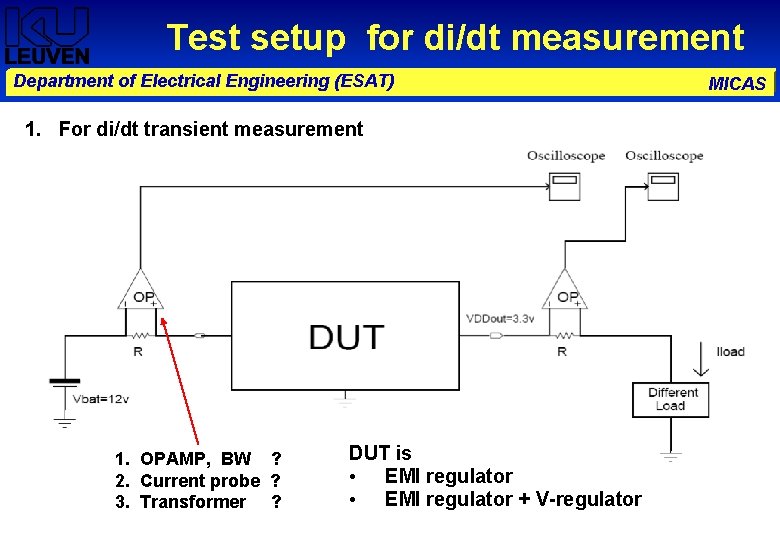

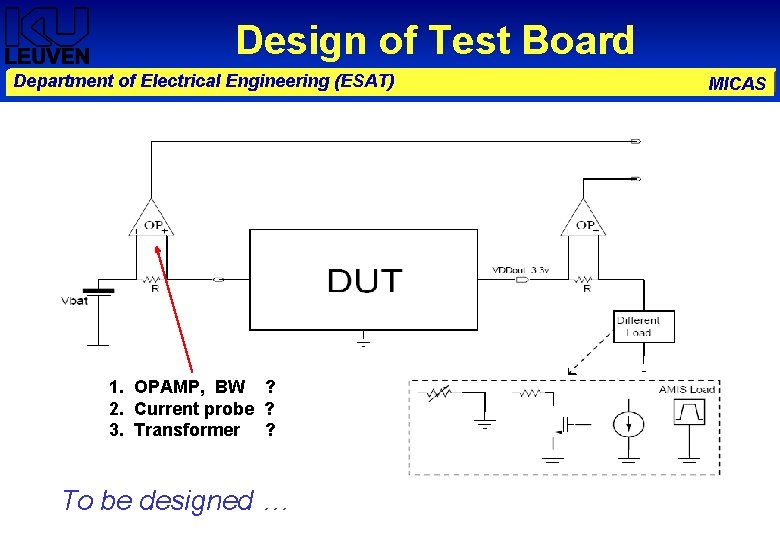

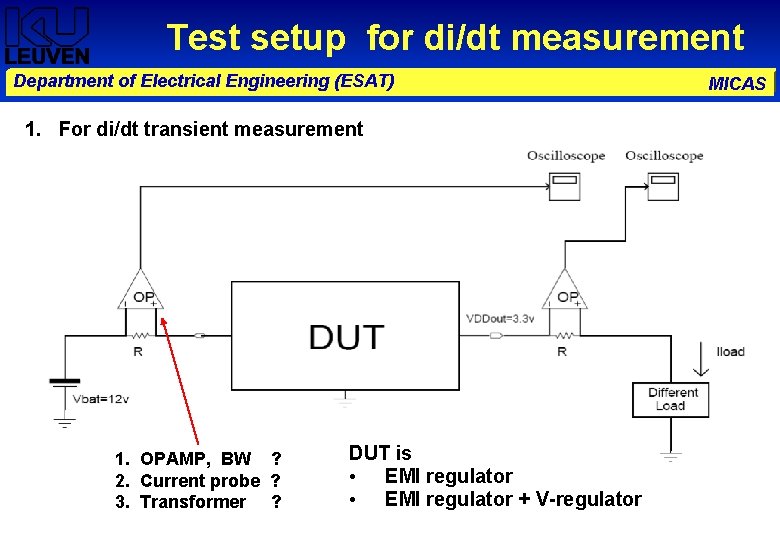

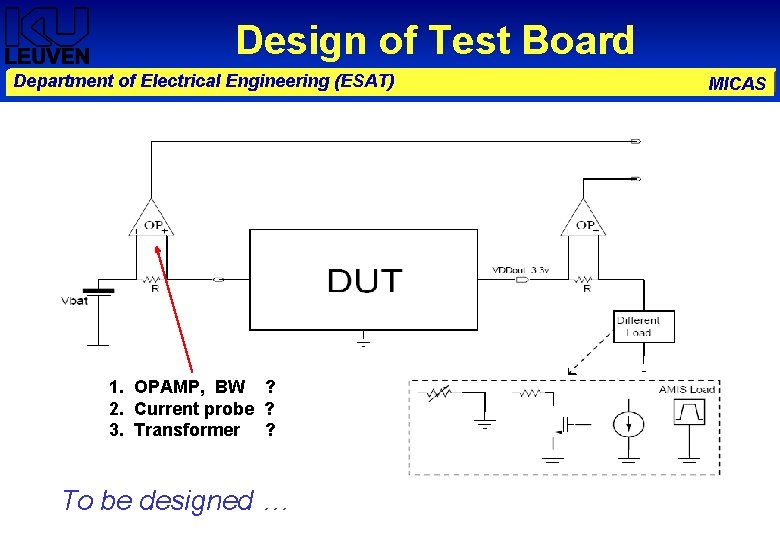

Test setup for di/dt measurement Department of Electrical Engineering (ESAT) 1. For di/dt transient measurement 1. OPAMP, BW ? 2. Current probe ? 3. Transformer ? DUT is • EMI regulator + V-regulator MICAS

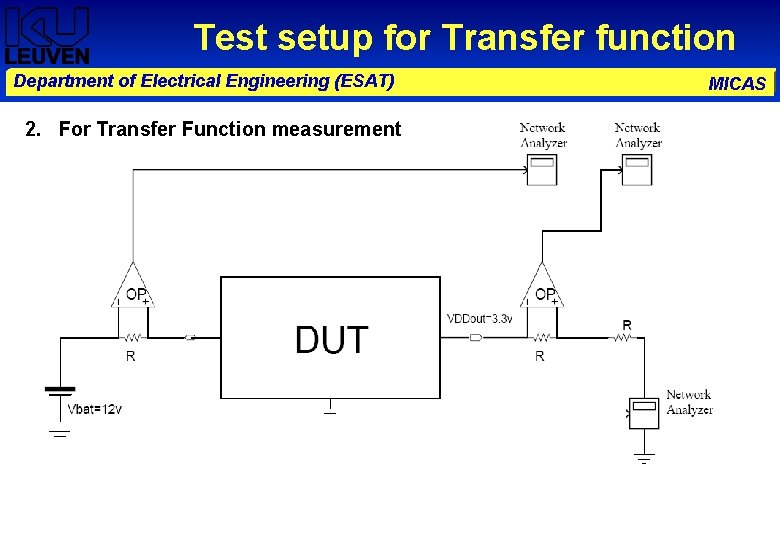

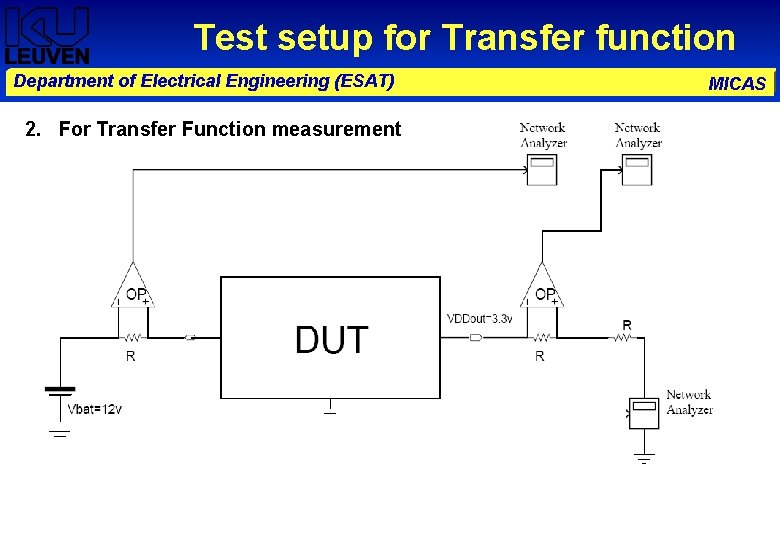

Test setup for Transfer function Department of Electrical Engineering (ESAT) 2. For Transfer Function measurement MICAS

Design of Test Board Department of Electrical Engineering (ESAT) 1. OPAMP, BW ? 2. Current probe ? 3. Transformer ? To be designed … MICAS

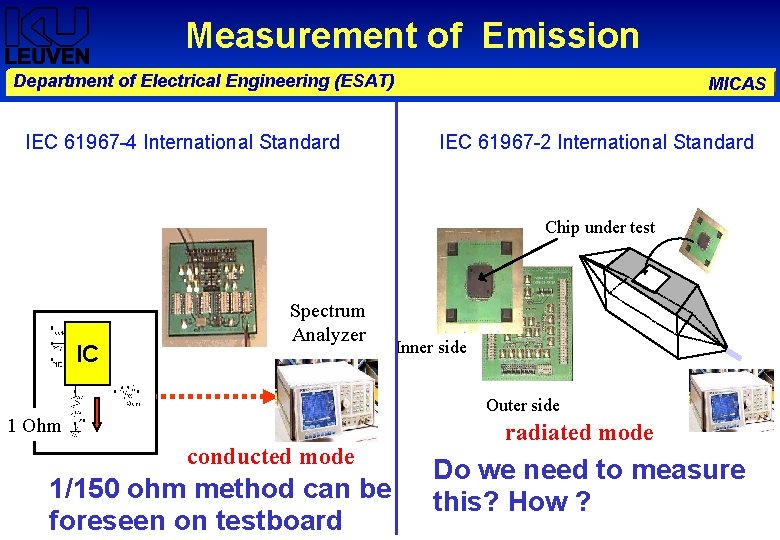

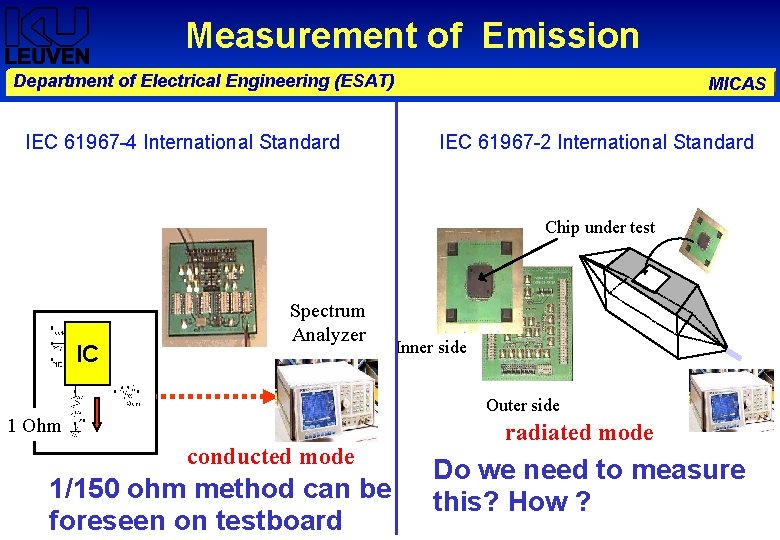

Measurement of Emission Department of Electrical Engineering (ESAT) IEC 61967 -4 International Standard MICAS IEC 61967 -2 International Standard Chip under test IC Spectrum Analyzer Inner side Outer side 1 Ohm conducted mode 1/150 ohm method can be foreseen on testboard radiated mode Do we need to measure this? How ?

Future work Department of Electrical Engineering (ESAT) 1. Test board ? , Chip measurement, Finish theoretical analysis, 2. Continue research on the Clock strategy: SSCG MICAS

Questions Department of Electrical Engineering (ESAT) Thank you for your attention MICAS