AIDEMC Low Emission Digital Circuit Design Department of

- Slides: 15

AID–EMC: Low Emission Digital Circuit Design Department of Electrical Engineering (ESAT) MICAS Update of the “Digital EMC project” May 9 th, 2006 Junfeng Zhou Wim Dehaene KULeuven ESAT-MICAS

Outline Department of Electrical Engineering (ESAT) 1. Theoretical analysis of the EMI regulator 2. Future work MICAS

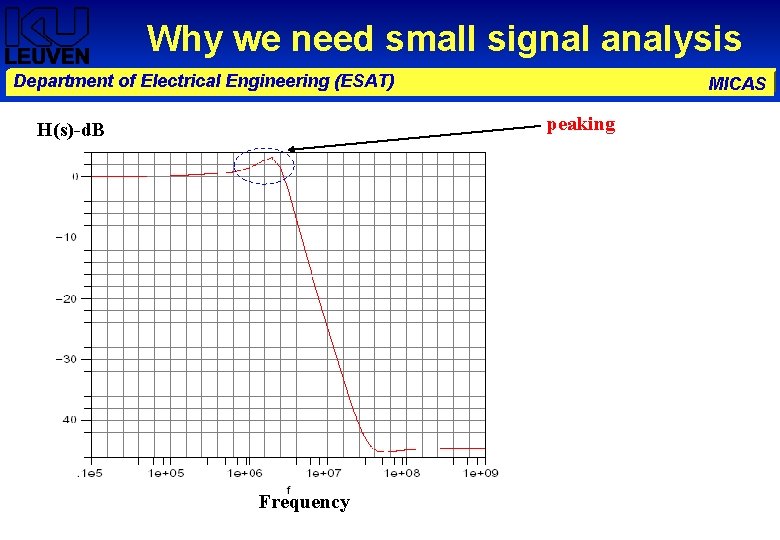

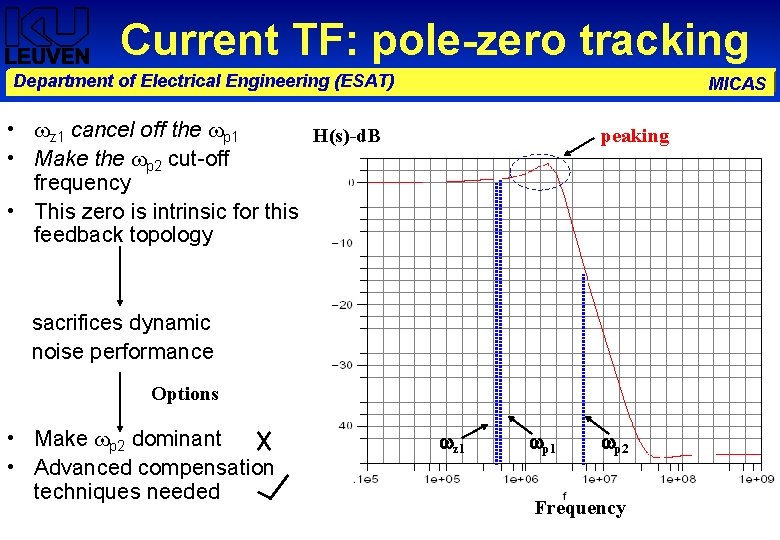

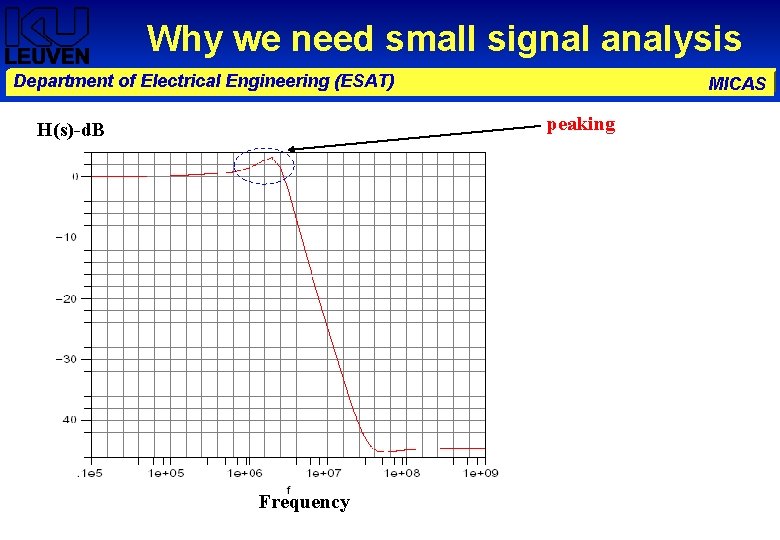

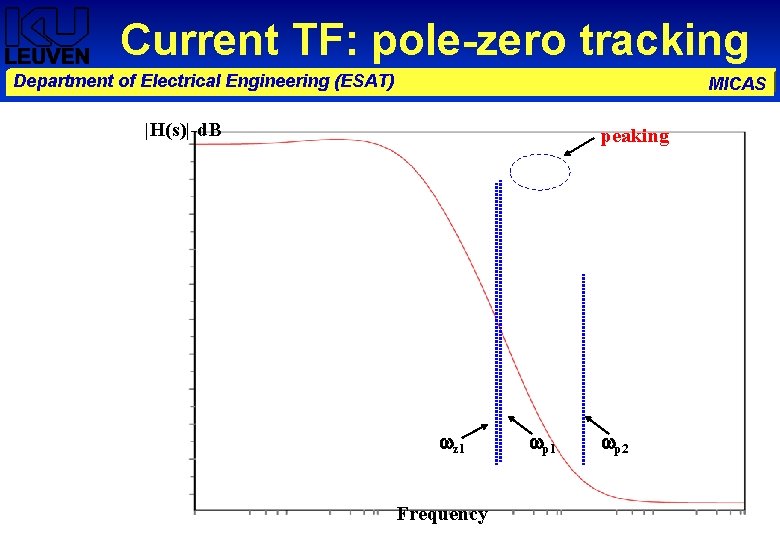

Why we need small signal analysis Department of Electrical Engineering (ESAT) MICAS peaking H(s)-d. B Frequency

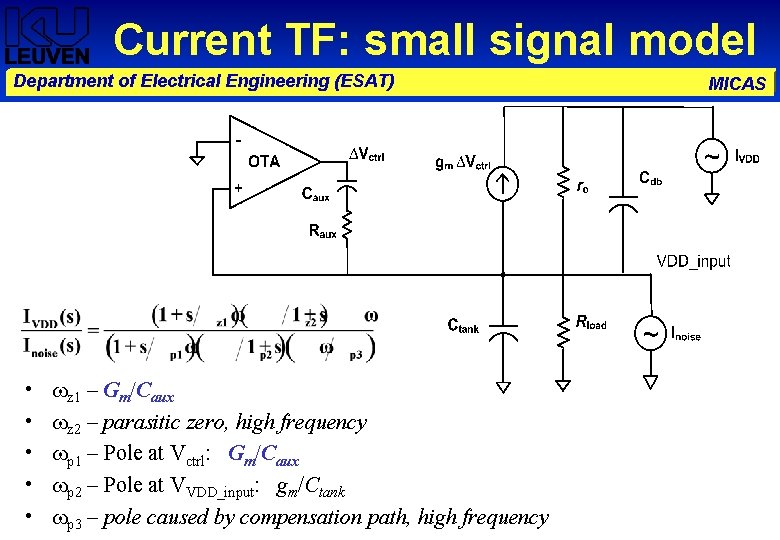

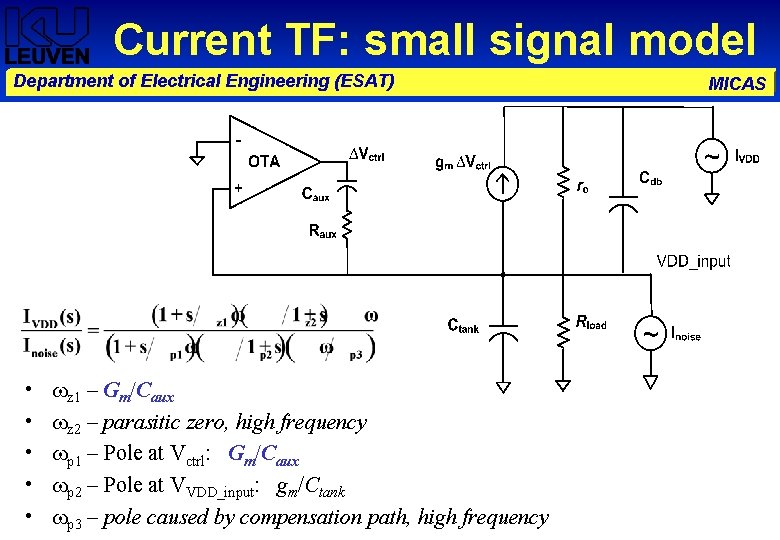

Current TF: small signal model Department of Electrical Engineering (ESAT) • • • z 1 – Gm/Caux z 2 – parasitic zero, high frequency p 1 – Pole at Vctrl: Gm/Caux p 2 – Pole at VVDD_input: gm/Ctank p 3 – pole caused by compensation path, high frequency MICAS

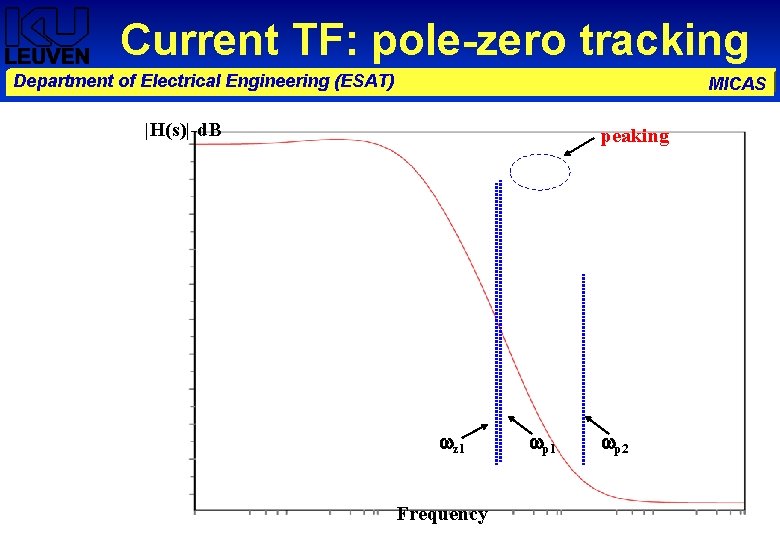

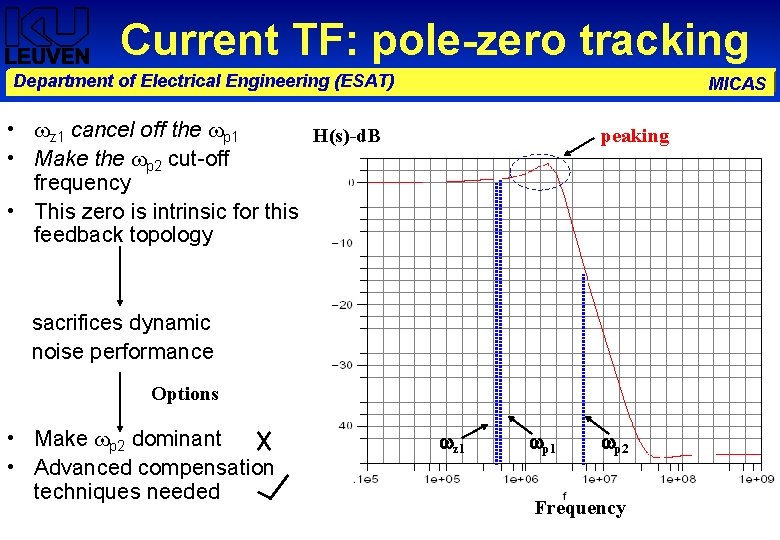

Current TF: pole-zero tracking Department of Electrical Engineering (ESAT) MICAS • z 1 cancel off the p 1 H(s)-d. B • Make the p 2 cut-off frequency • This zero is intrinsic for this feedback topology peaking sacrifices dynamic noise performance Options • Make p 2 dominant • Advanced compensation techniques needed z 1 p 2 Frequency

Current TF: pole-zero tracking Department of Electrical Engineering (ESAT) MICAS |H(s)|-d. B peaking z 1 Frequency p 1 p 2

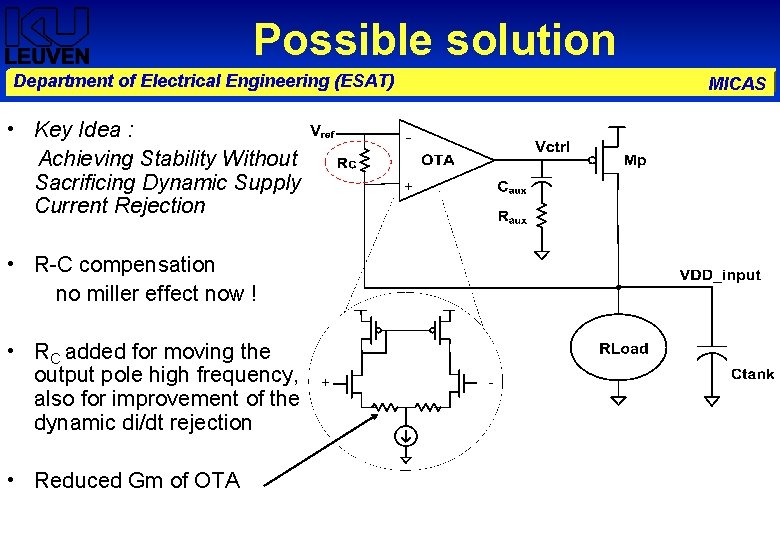

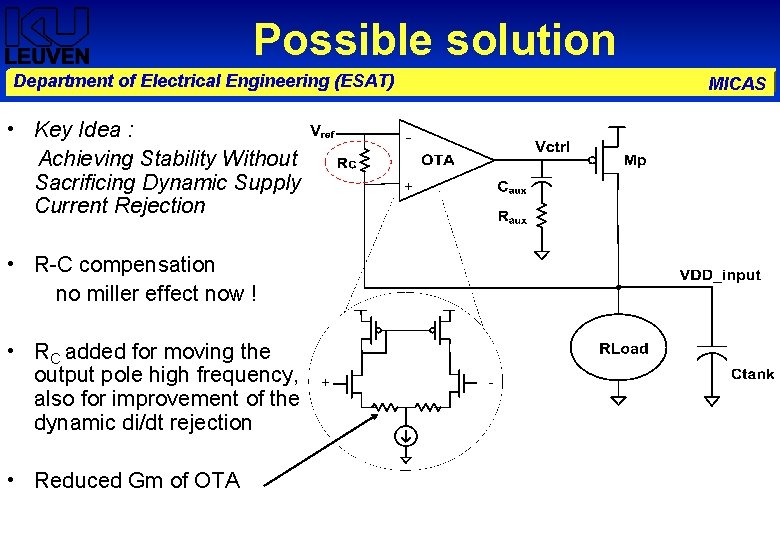

Possible solution Department of Electrical Engineering (ESAT) • Key Idea : Achieving Stability Without Sacrificing Dynamic Supply Current Rejection • R-C compensation no miller effect now ! • RC added for moving the output pole high frequency, also for improvement of the dynamic di/dt rejection • Reduced Gm of OTA MICAS

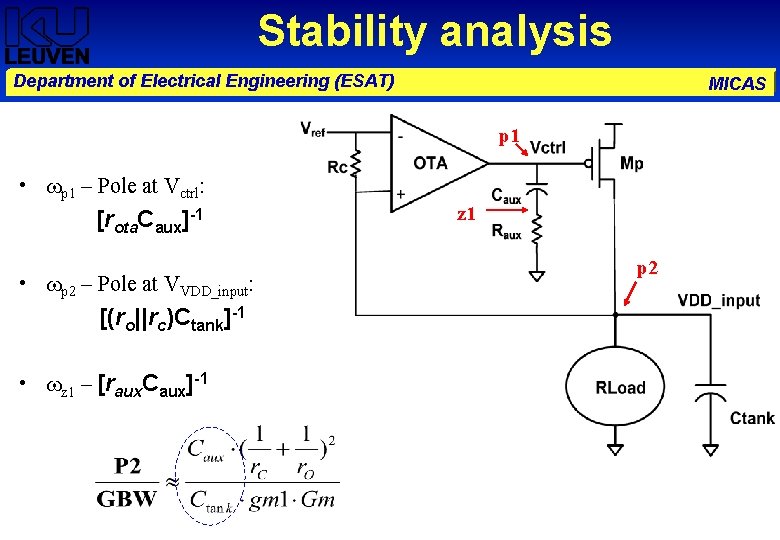

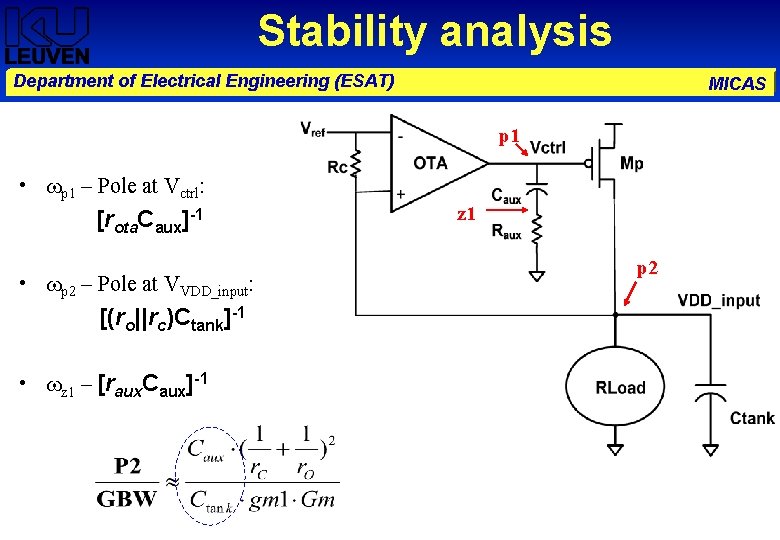

Stability analysis Department of Electrical Engineering (ESAT) MICAS p 1 • p 1 – Pole at Vctrl: [rota. Caux]-1 • p 2 – Pole at VVDD_input: [(ro||rc)Ctank]-1 • z 1 – [raux. Caux]-1 z 1 p 2

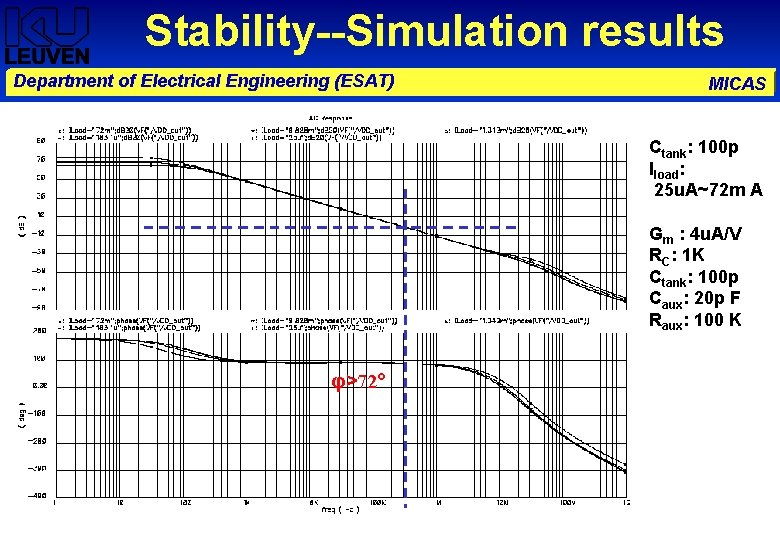

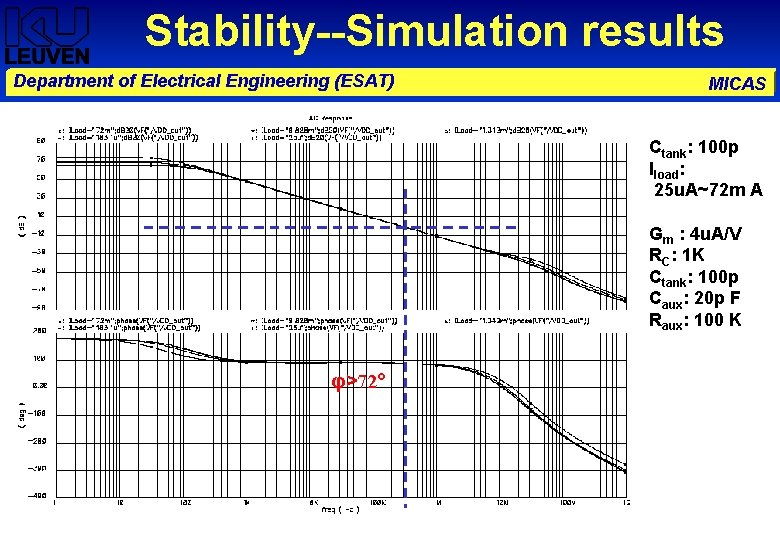

Stability--Simulation results Department of Electrical Engineering (ESAT) MICAS Ctank: 100 p Iload: 25 u. A~72 m A Gm : 4 u. A/V RC: 1 K Ctank: 100 p Caux: 20 p F Raux: 100 K φ>72°

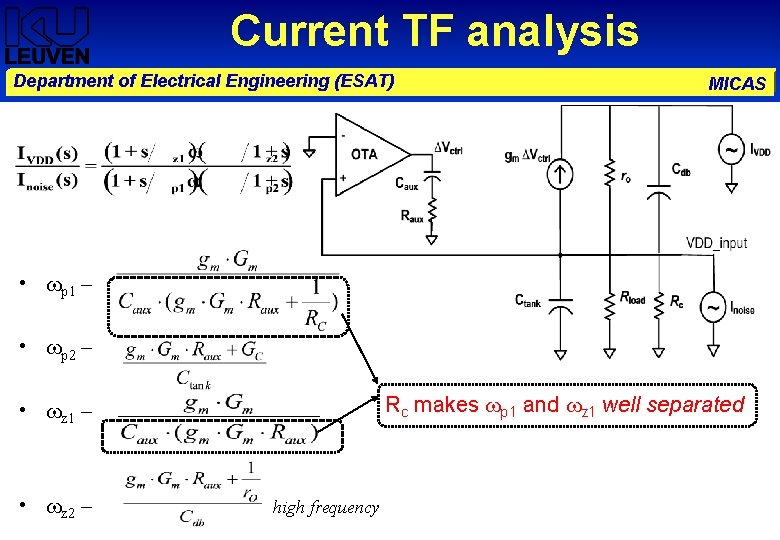

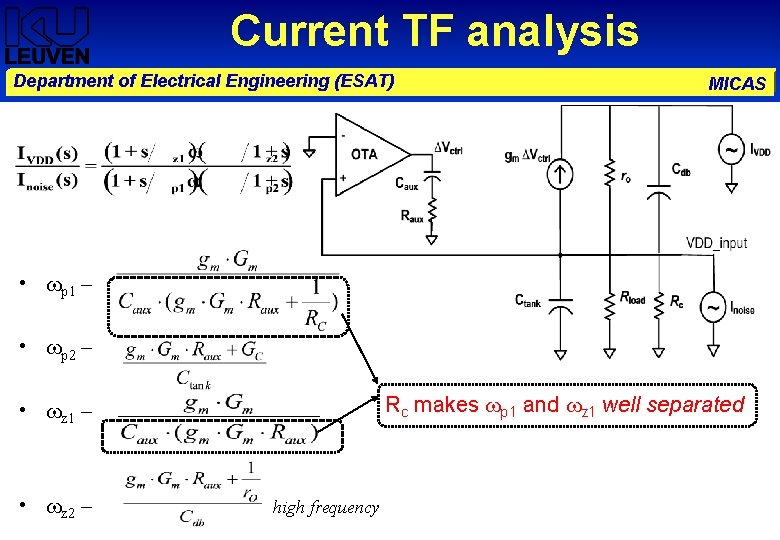

Current TF analysis Department of Electrical Engineering (ESAT) MICAS • p 1 – • p 2 – Rc makes p 1 and z 1 well separated • z 1 – • z 2 – high frequency

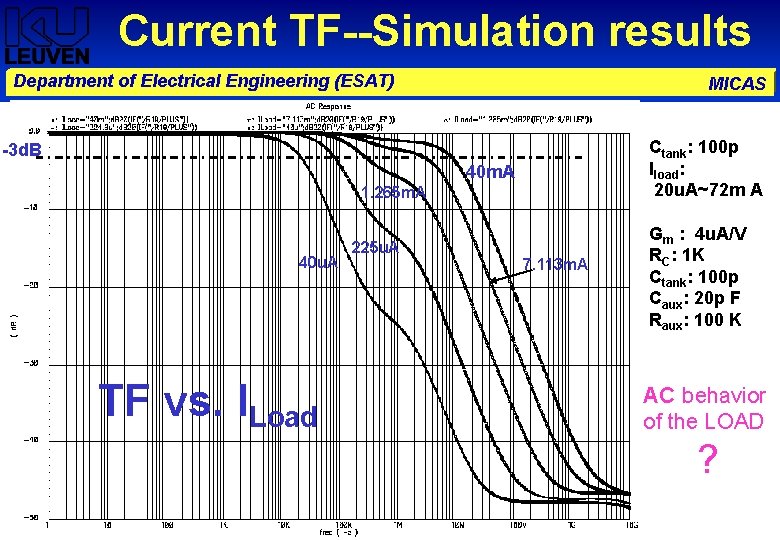

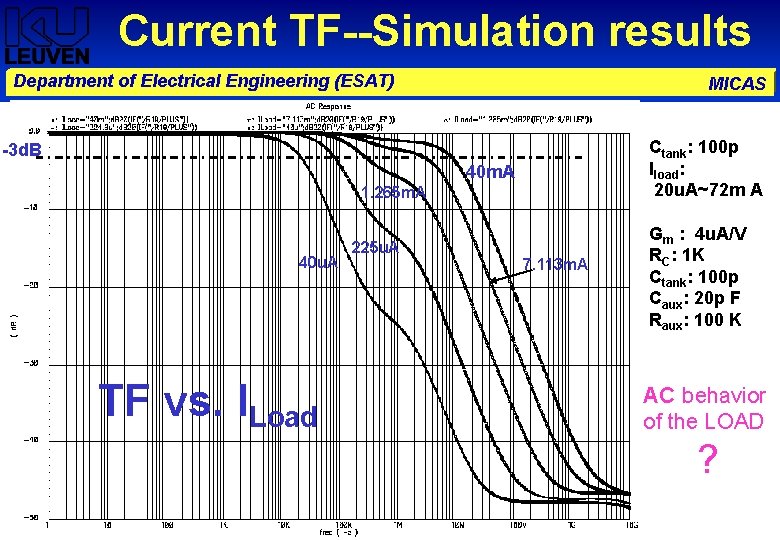

Current TF--Simulation results Department of Electrical Engineering (ESAT) MICAS Ctank: 100 p Iload: 20 u. A~72 m A -3 d. B 40 m. A 1. 265 m. A 40 u. A TF vs. ILoad 225 u. A 7. 113 m. A Gm : 4 u. A/V RC: 1 K Ctank: 100 p Caux: 20 p F Raux: 100 K AC behavior of the LOAD ?

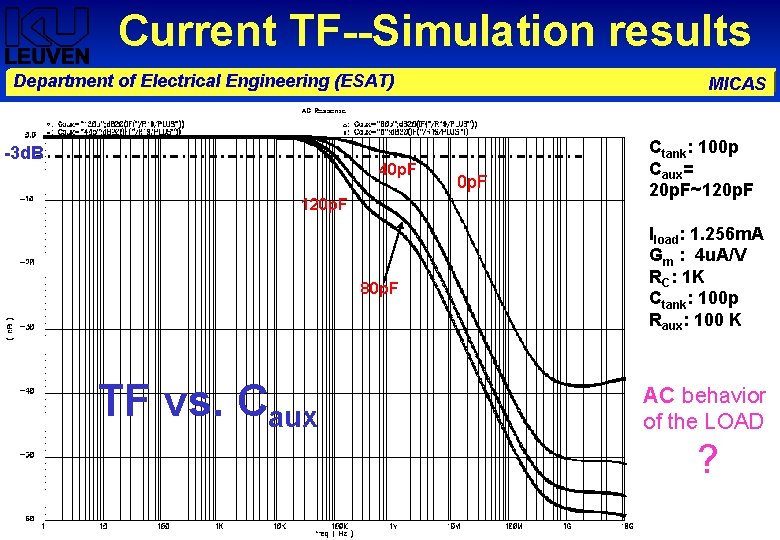

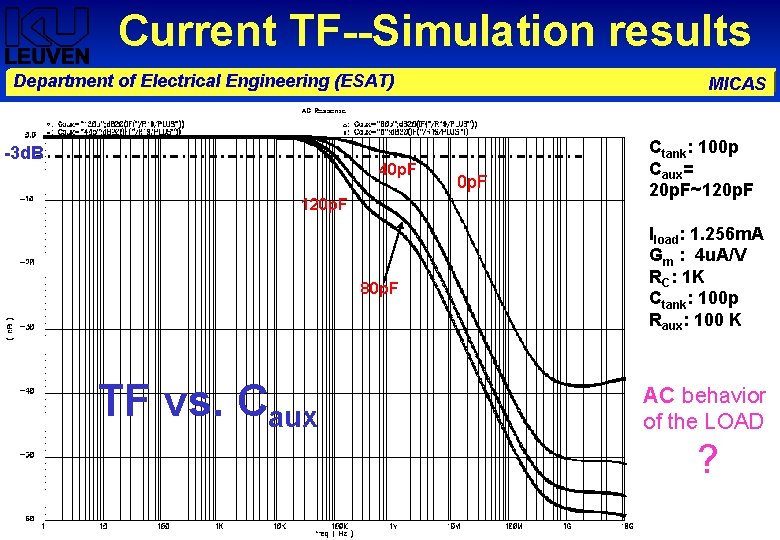

Current TF--Simulation results Department of Electrical Engineering (ESAT) -3 d. B 40 p. F 120 p. F 80 p. F TF vs. Caux MICAS 0 p. F Ctank: 100 p Caux= 20 p. F~120 p. F Iload: 1. 256 m. A Gm : 4 u. A/V RC: 1 K Ctank: 100 p Raux: 100 K AC behavior of the LOAD ?

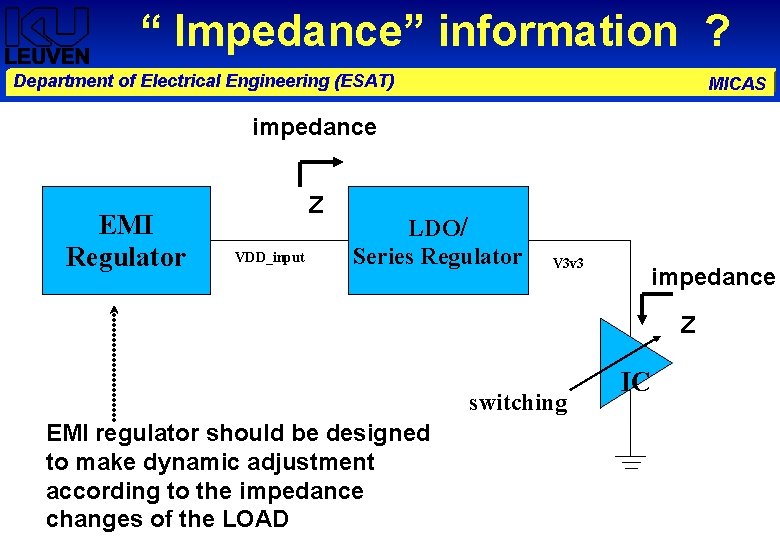

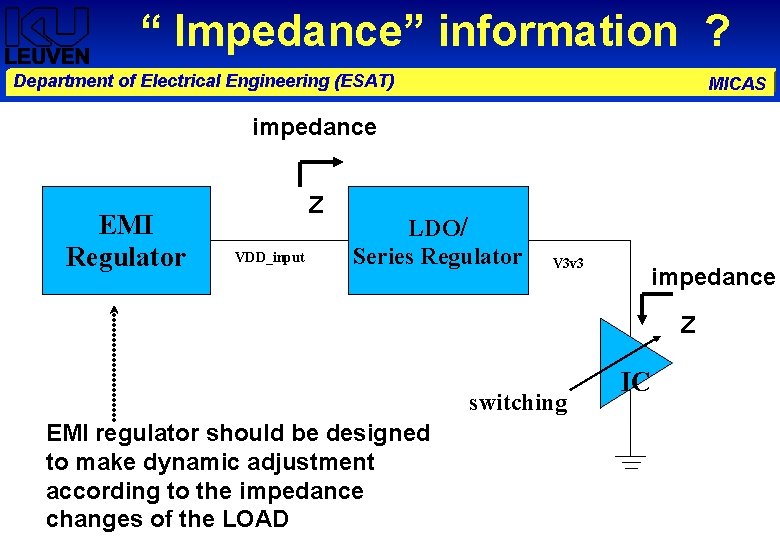

“ Impedance” information ? Department of Electrical Engineering (ESAT) MICAS impedance EMI Regulator Z VDD_input LDO/ Series Regulator V 3 v 3 impedance Z switching EMI regulator should be designed to make dynamic adjustment according to the impedance changes of the LOAD IC

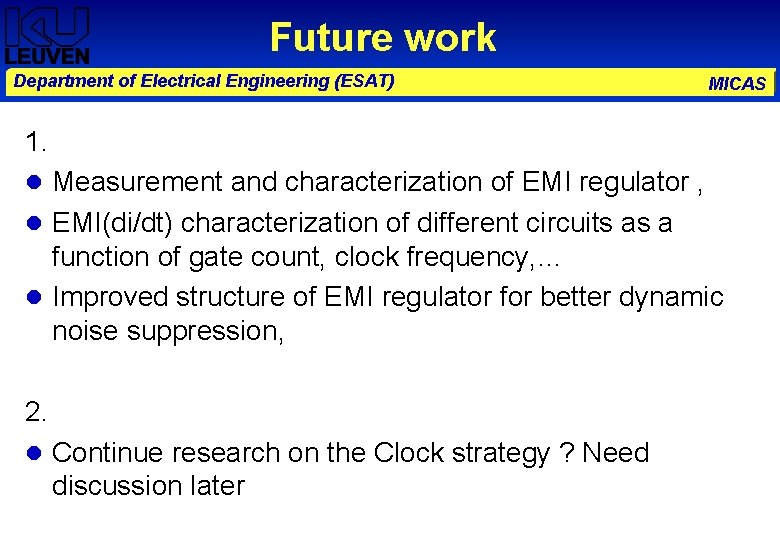

Future work Department of Electrical Engineering (ESAT) MICAS 1. Measurement and characterization of EMI regulator , EMI(di/dt) characterization of different circuits as a function of gate count, clock frequency, … Improved structure of EMI regulator for better dynamic noise suppression, 2. Continue research on the Clock strategy ? Need discussion later

Questions Department of Electrical Engineering (ESAT) Thank you for your attention MICAS