A Simple Microcontroller VHDL Tutorial R E Haskell

- Slides: 23

A Simple Microcontroller VHDL Tutorial R. E. Haskell and D. M. Hanna T 6: VHDL State Machines

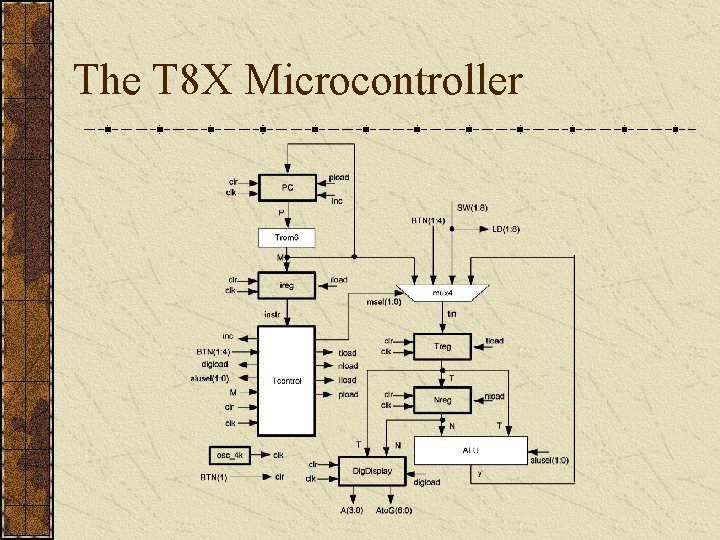

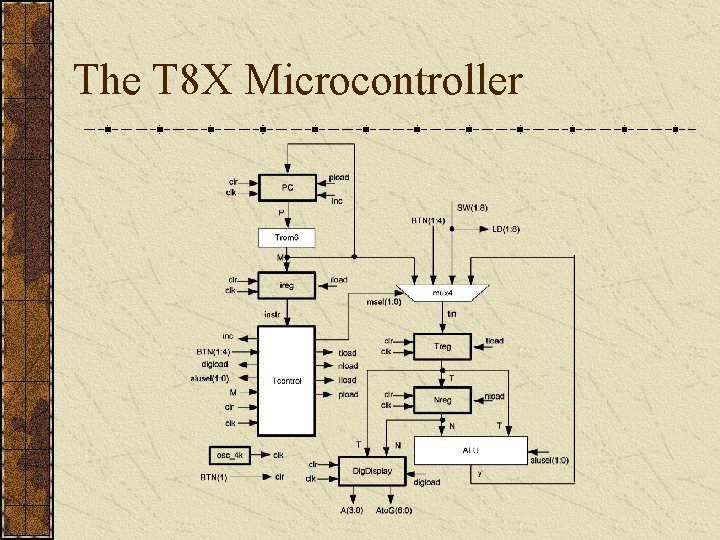

The T 8 X Microcontroller

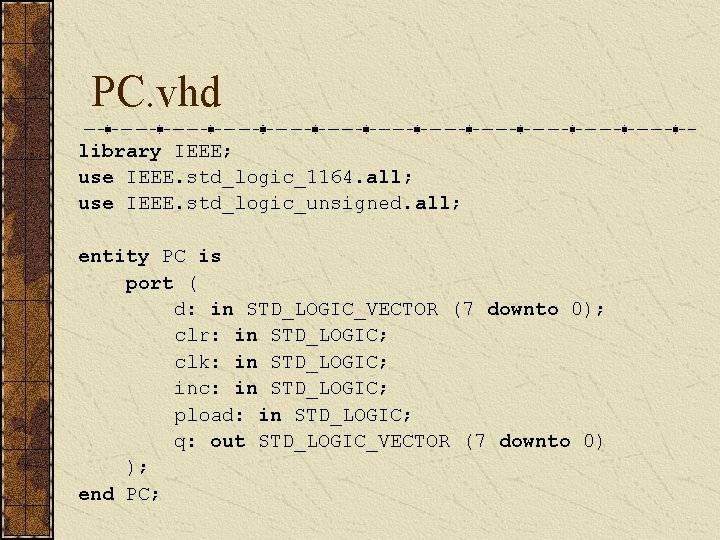

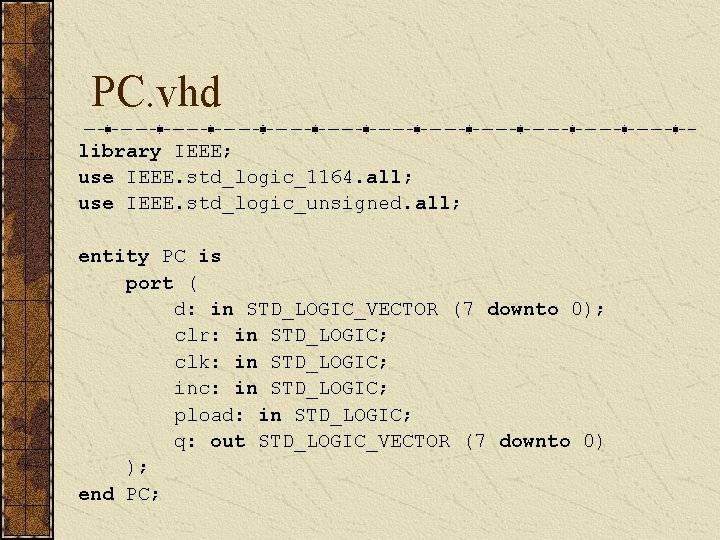

PC. vhd library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_unsigned. all; entity PC is port ( d: in STD_LOGIC_VECTOR (7 downto 0); clr: in STD_LOGIC; clk: in STD_LOGIC; inc: in STD_LOGIC; pload: in STD_LOGIC; q: out STD_LOGIC_VECTOR (7 downto 0) ); end PC;

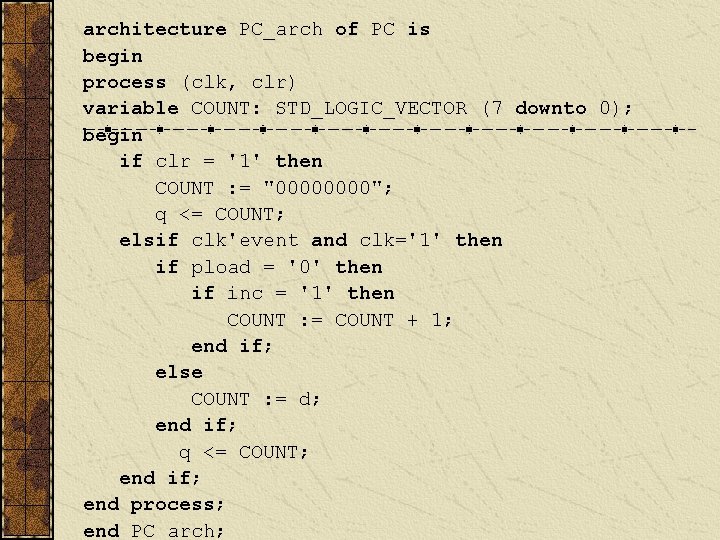

architecture PC_arch of PC is begin process (clk, clr) variable COUNT: STD_LOGIC_VECTOR (7 downto 0); begin if clr = '1' then COUNT : = "0000"; q <= COUNT; elsif clk'event and clk='1' then if pload = '0' then if inc = '1' then COUNT : = COUNT + 1; end if; else COUNT : = d; end if; q <= COUNT; end if; end process; end PC_arch;

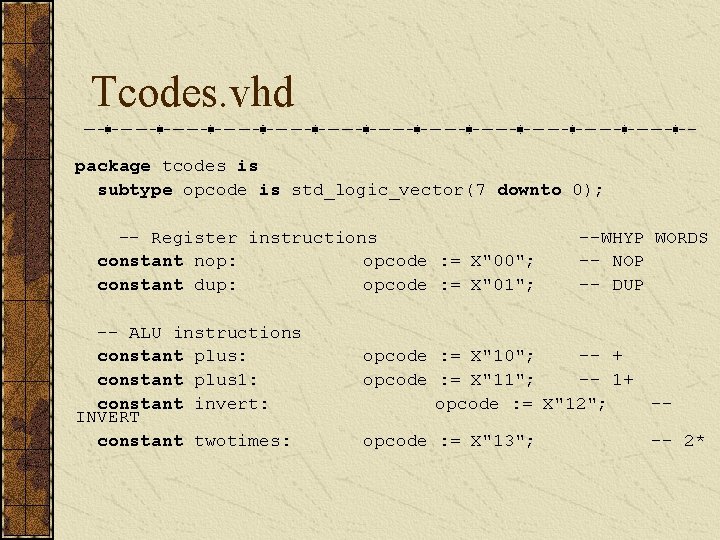

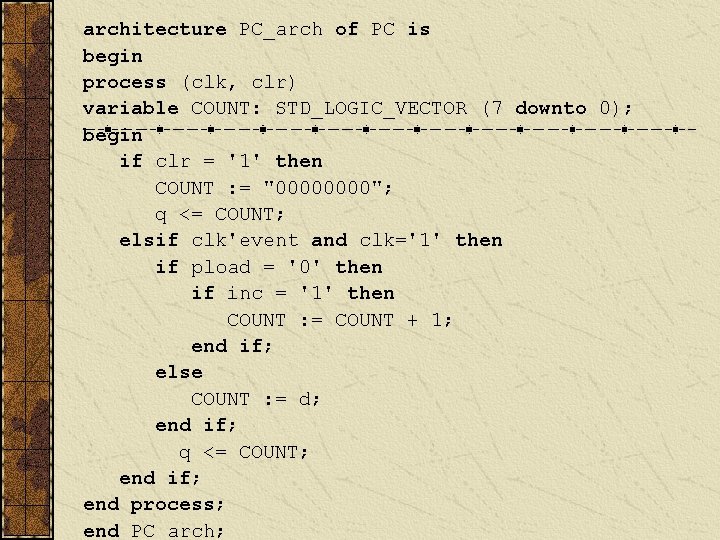

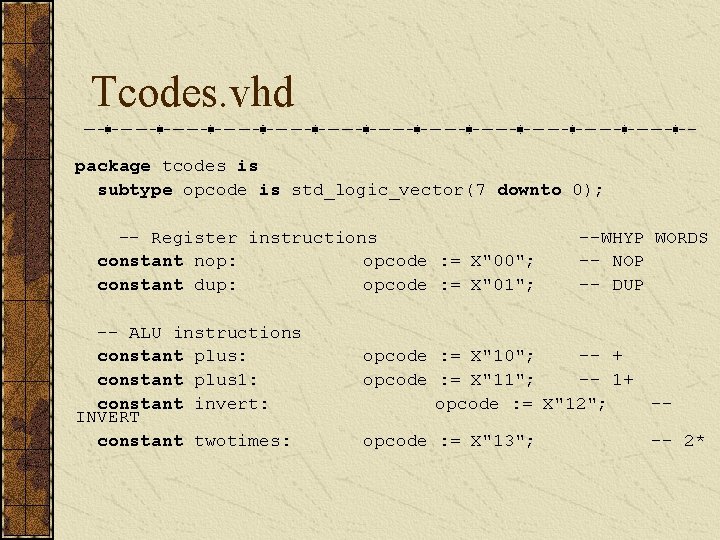

Tcodes. vhd package tcodes is subtype opcode is std_logic_vector(7 downto 0); -- Register instructions constant nop: opcode : = X"00"; constant dup: opcode : = X"01"; -- ALU instructions constant plus: constant plus 1: constant invert: INVERT constant twotimes: --WHYP WORDS -- NOP -- DUP opcode : = X"10"; -- + opcode : = X"11"; -- 1+ opcode : = X"12"; -- opcode : = X"13"; -- 2*

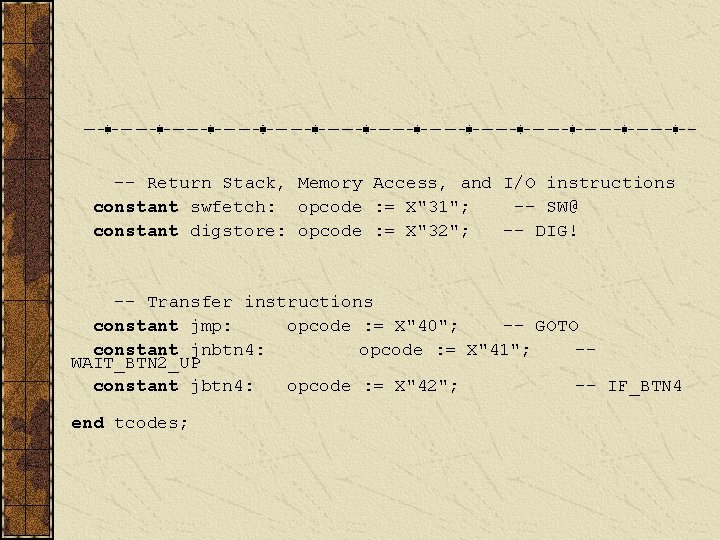

-- Return Stack, Memory Access, and I/O instructions constant swfetch: opcode : = X"31"; -- SW@ constant digstore: opcode : = X"32"; -- DIG! -- Transfer instructions constant jmp: opcode : = X"40"; -- GOTO constant jnbtn 4: opcode : = X"41"; -WAIT_BTN 2_UP constant jbtn 4: opcode : = X"42"; -- IF_BTN 4 end tcodes;

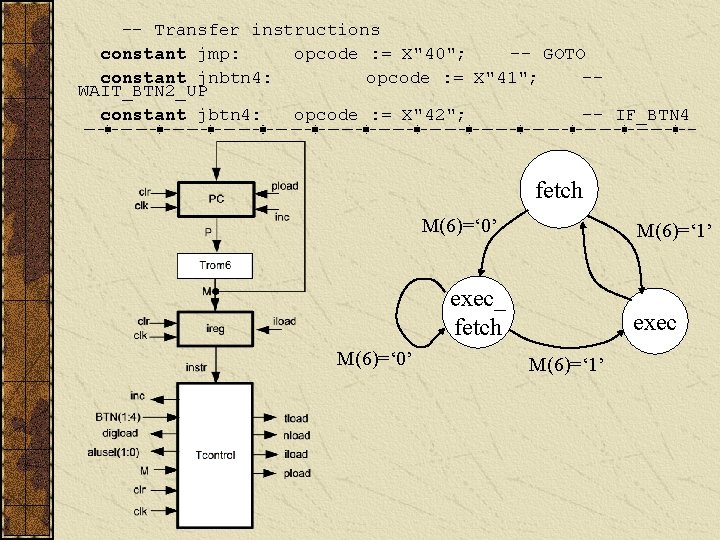

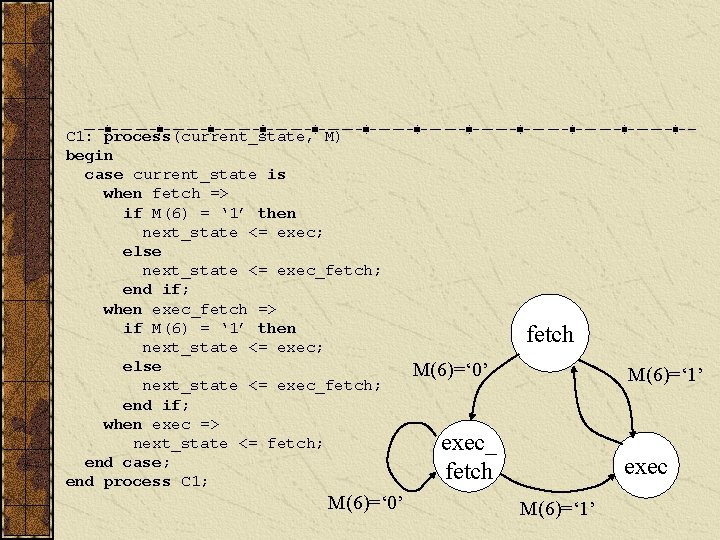

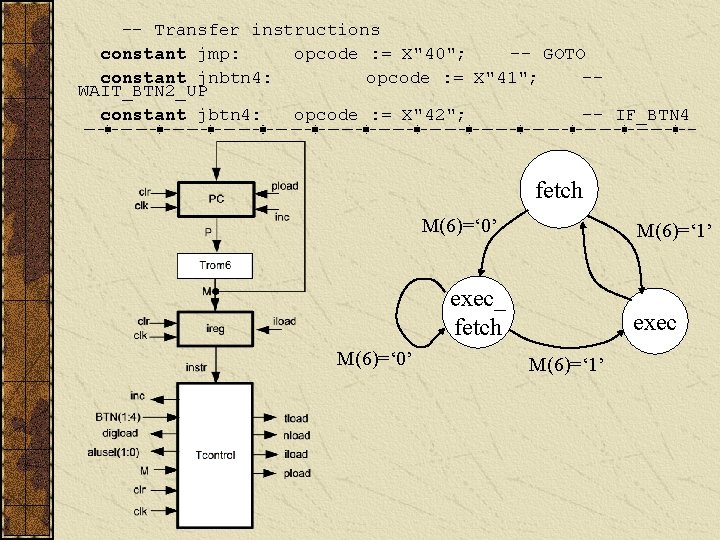

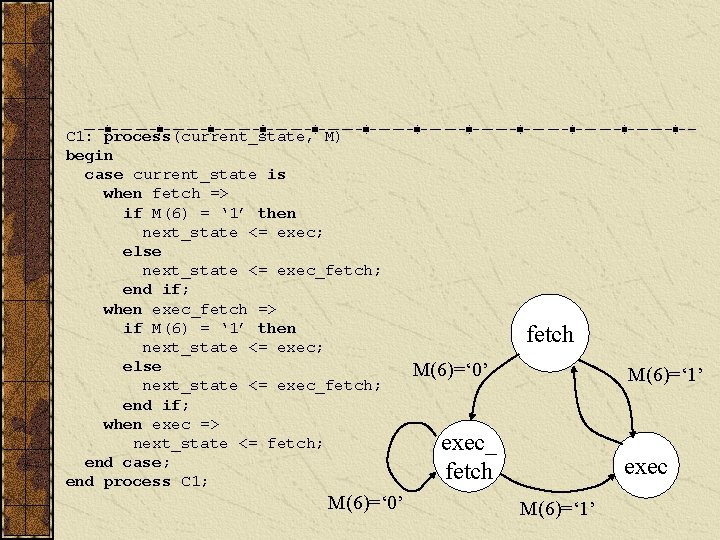

-- Transfer instructions constant jmp: opcode : = X"40"; -- GOTO constant jnbtn 4: opcode : = X"41"; -WAIT_BTN 2_UP constant jbtn 4: opcode : = X"42"; -- IF_BTN 4 fetch M(6)=‘ 0’ M(6)=‘ 1’ exec_ fetch M(6)=‘ 0’ exec M(6)=‘ 1’

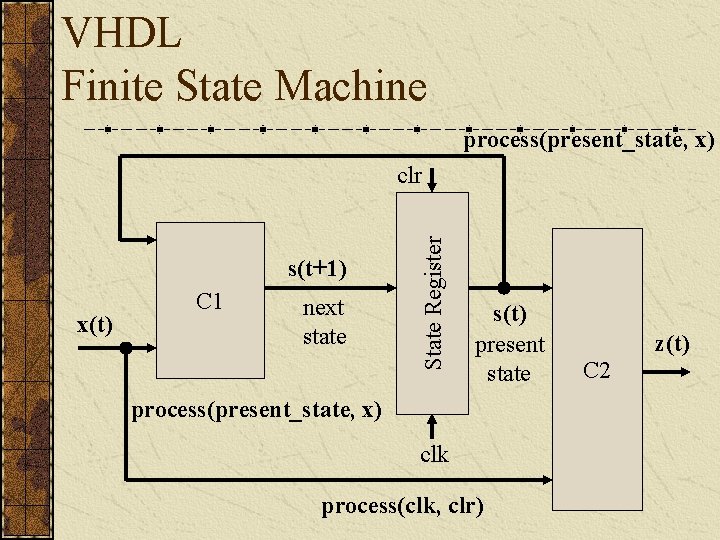

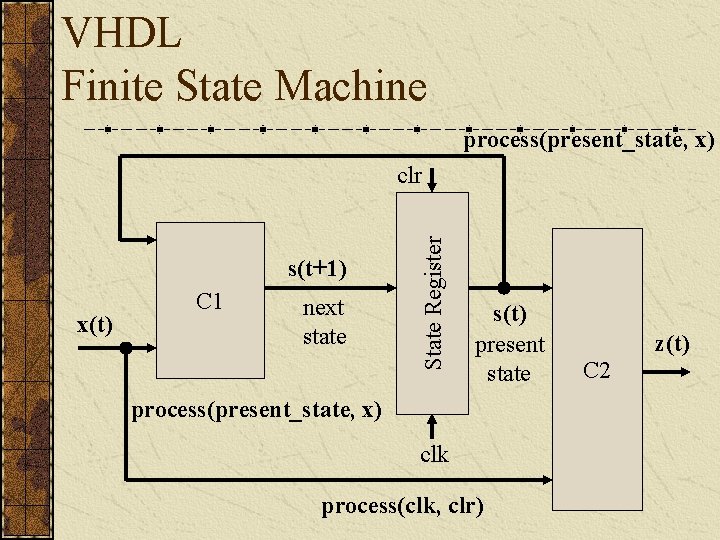

VHDL Finite State Machine process(present_state, x) s(t+1) x(t) C 1 next state State Register clr s(t) present state process(present_state, x) clk process(clk, clr) z(t) C 2

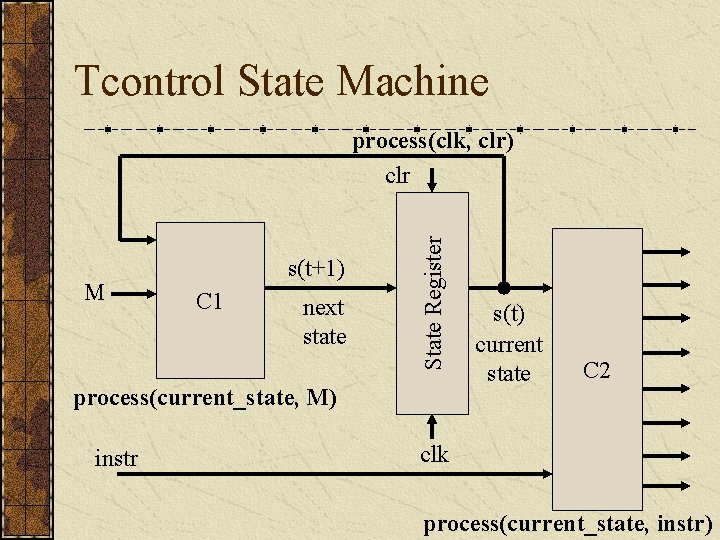

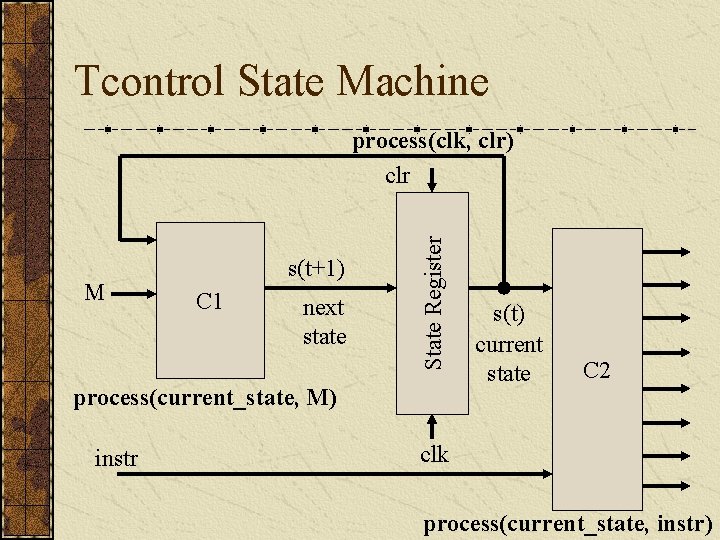

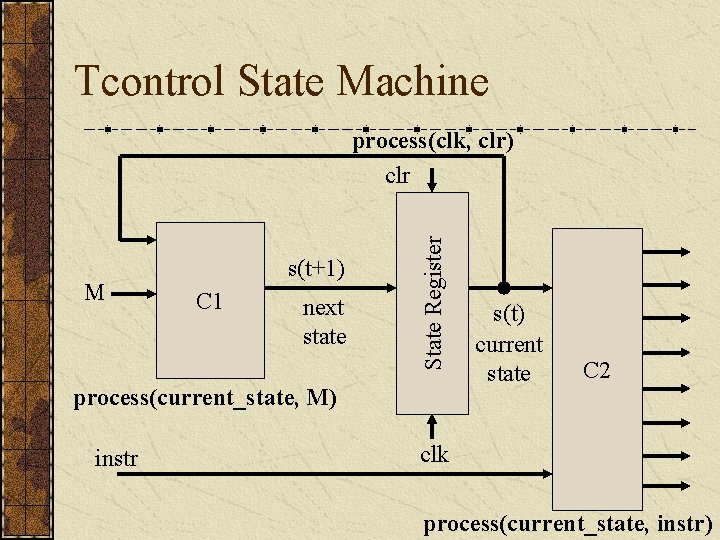

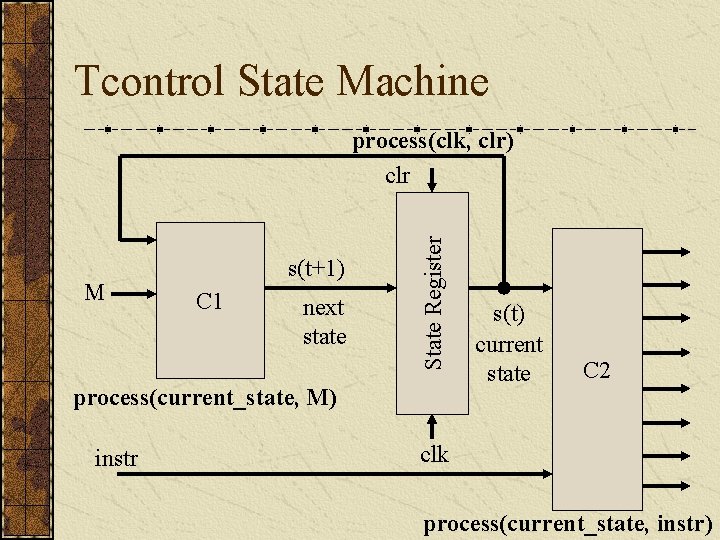

Tcontrol State Machine M s(t+1) C 1 next state State Register process(clk, clr) clr process(current_state, M) instr s(t) current state C 2 clk process(current_state, instr)

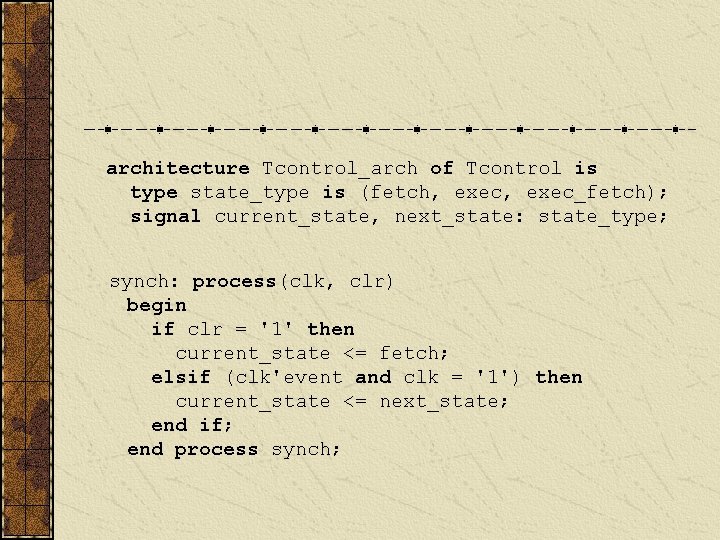

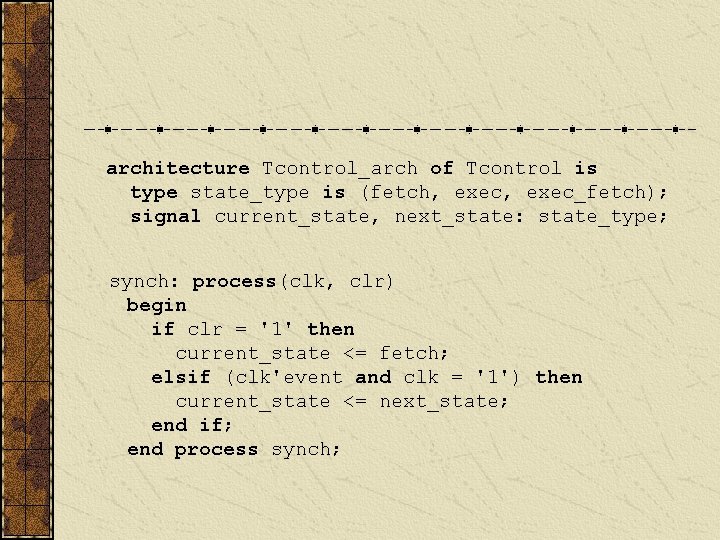

architecture Tcontrol_arch of Tcontrol is type state_type is (fetch, exec_fetch); signal current_state, next_state: state_type; synch: process(clk, clr) begin if clr = '1' then current_state <= fetch; elsif (clk'event and clk = '1') then current_state <= next_state; end if; end process synch;

C 1: process(current_state, M) begin case current_state is when fetch => if M(6) = ‘ 1’ then next_state <= exec; else next_state <= exec_fetch; end if; when exec_fetch => if M(6) = ‘ 1’ then next_state <= exec; else next_state <= exec_fetch; end if; when exec => next_state <= fetch; end case; end process C 1; M(6)=‘ 0’ fetch M(6)=‘ 0’ M(6)=‘ 1’ exec_ fetch exec M(6)=‘ 1’

Tcontrol State Machine M s(t+1) C 1 next state State Register process(clk, clr) clr process(current_state, M) instr s(t) current state C 2 clk process(current_state, instr)

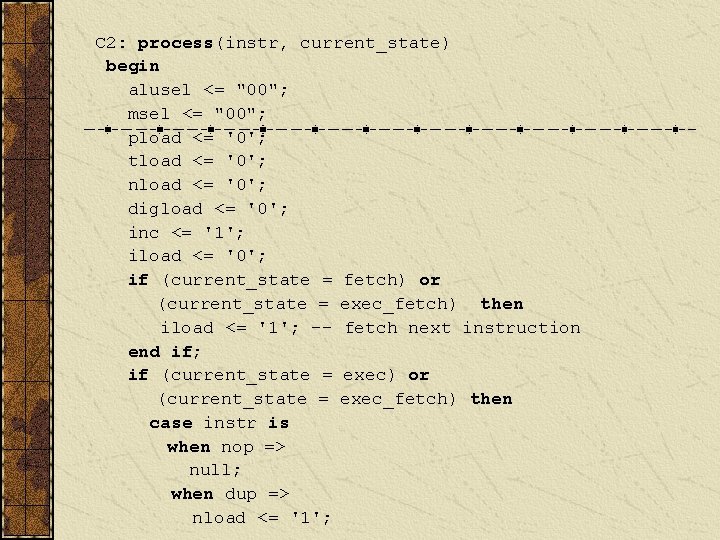

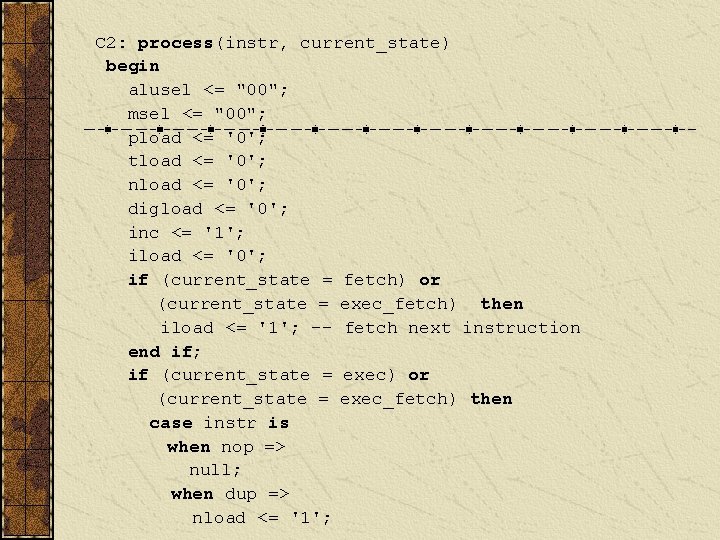

C 2: process(instr, current_state) begin alusel <= "00"; msel <= "00"; pload <= '0'; tload <= '0'; nload <= '0'; digload <= '0'; inc <= '1'; iload <= '0'; if (current_state = fetch) or (current_state = exec_fetch) then iload <= '1'; -- fetch next instruction end if; if (current_state = exec) or (current_state = exec_fetch) then case instr is when nop => null; when dup => nload <= '1';

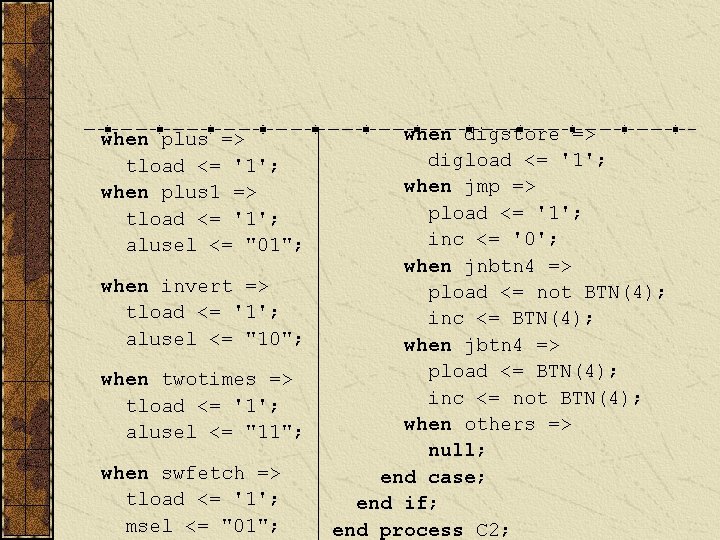

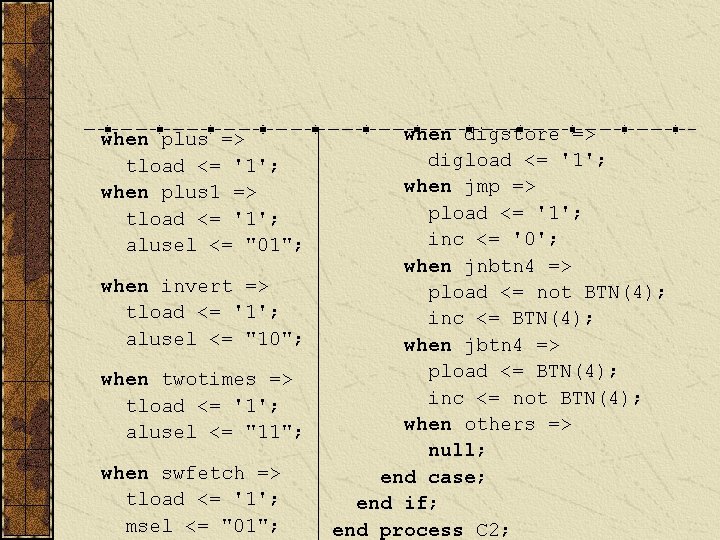

when plus => tload <= '1'; when plus 1 => tload <= '1'; alusel <= "01"; when invert => tload <= '1'; alusel <= "10"; when twotimes => tload <= '1'; alusel <= "11"; when swfetch => tload <= '1'; msel <= "01"; when digstore => digload <= '1'; when jmp => pload <= '1'; inc <= '0'; when jnbtn 4 => pload <= not BTN(4); inc <= BTN(4); when jbtn 4 => pload <= BTN(4); inc <= not BTN(4); when others => null; end case; end if; end process C 2;

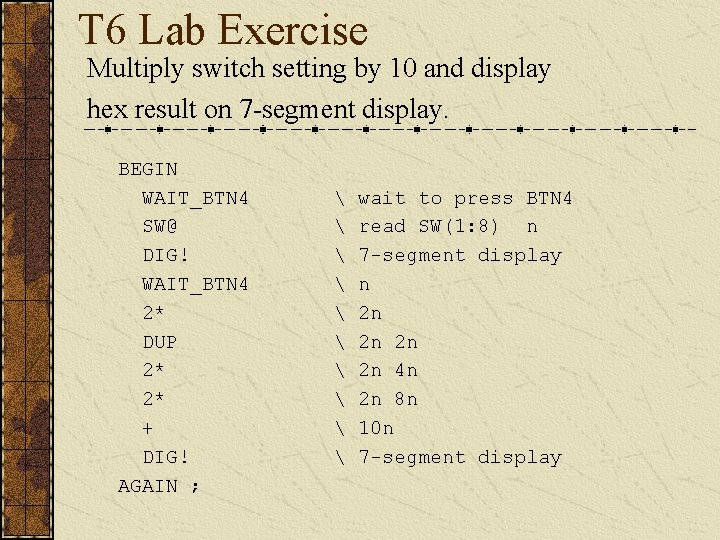

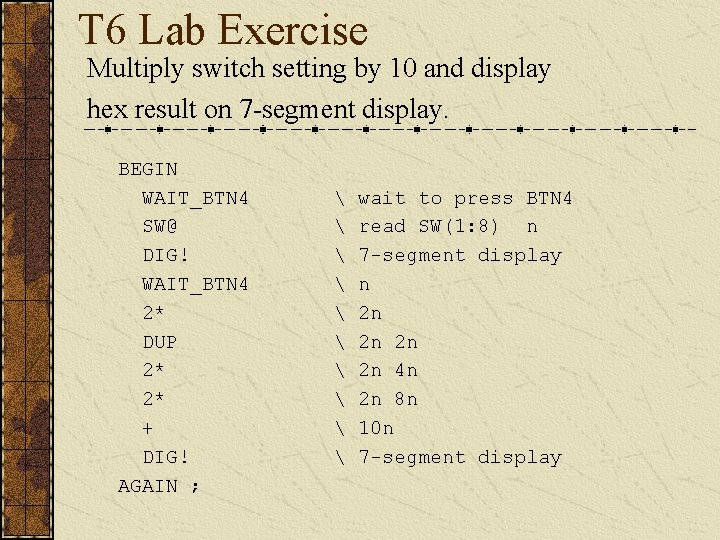

T 6 Lab Exercise Multiply switch setting by 10 and display hex result on 7 -segment display. BEGIN WAIT_BTN 4 SW@ DIG! WAIT_BTN 4 2* DUP 2* 2* + DIG! AGAIN ; wait to press BTN 4 read SW(1: 8) n 7 -segment display n 2 n 2 n 4 n 2 n 8 n 10 n 7 -segment display

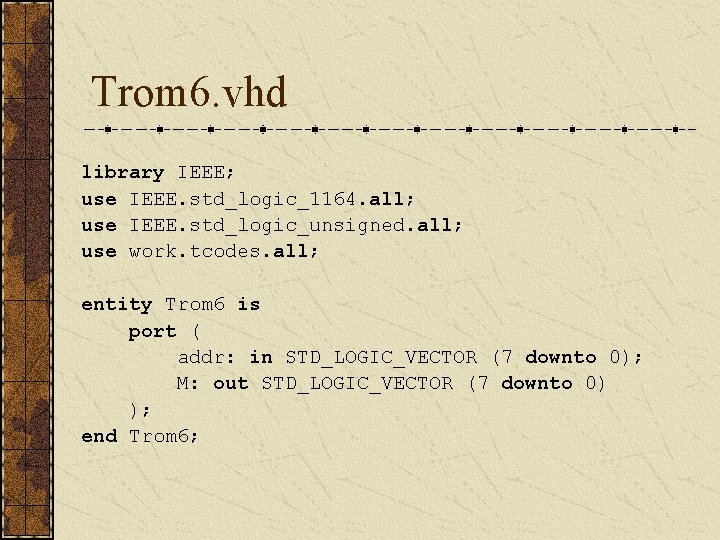

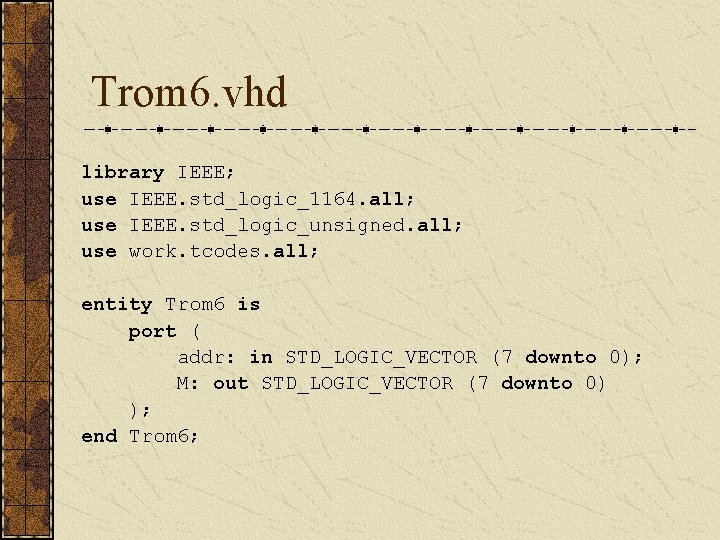

Trom 6. vhd library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_unsigned. all; use work. tcodes. all; entity Trom 6 is port ( addr: in STD_LOGIC_VECTOR (7 downto 0); M: out STD_LOGIC_VECTOR (7 downto 0) ); end Trom 6;

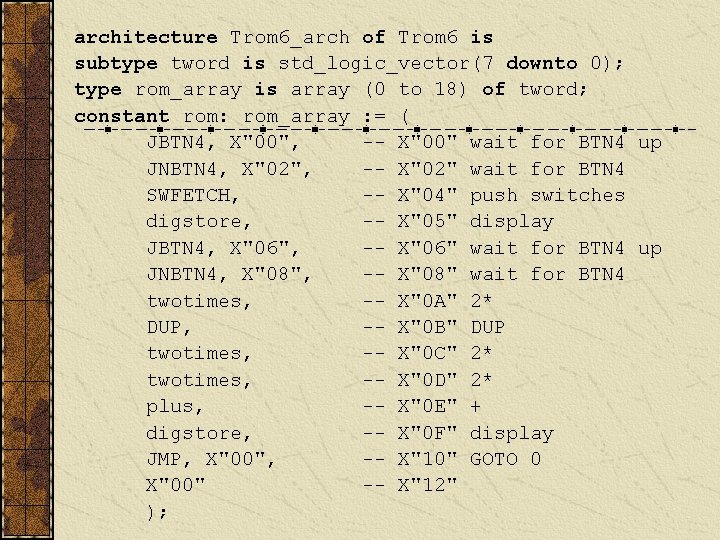

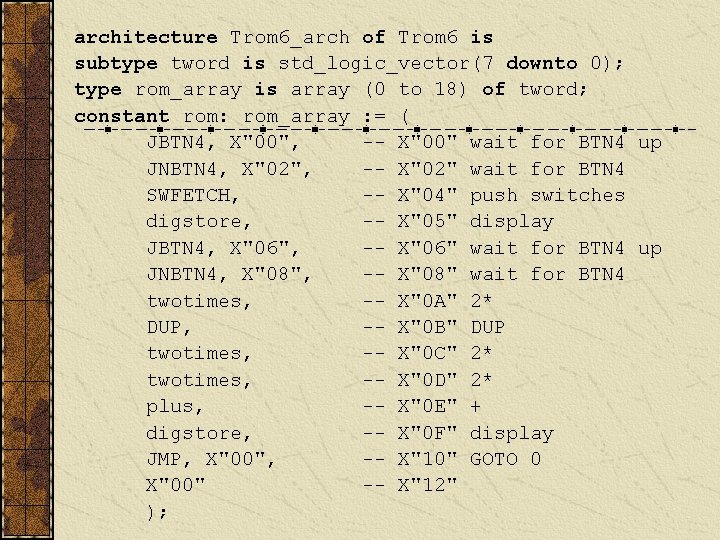

architecture Trom 6_arch of Trom 6 is subtype tword is std_logic_vector(7 downto 0); type rom_array is array (0 to 18) of tword; constant rom: rom_array : = ( JBTN 4, X"00", -- X"00" wait for BTN 4 up JNBTN 4, X"02", -- X"02" wait for BTN 4 SWFETCH, -- X"04" push switches digstore, -- X"05" display JBTN 4, X"06", -- X"06" wait for BTN 4 up JNBTN 4, X"08", -- X"08" wait for BTN 4 twotimes, -- X"0 A" 2* DUP, -- X"0 B" DUP twotimes, -- X"0 C" 2* twotimes, -- X"0 D" 2* plus, -- X"0 E" + digstore, -- X"0 F" display JMP, X"00", -- X"10" GOTO 0 X"00" -- X"12" );

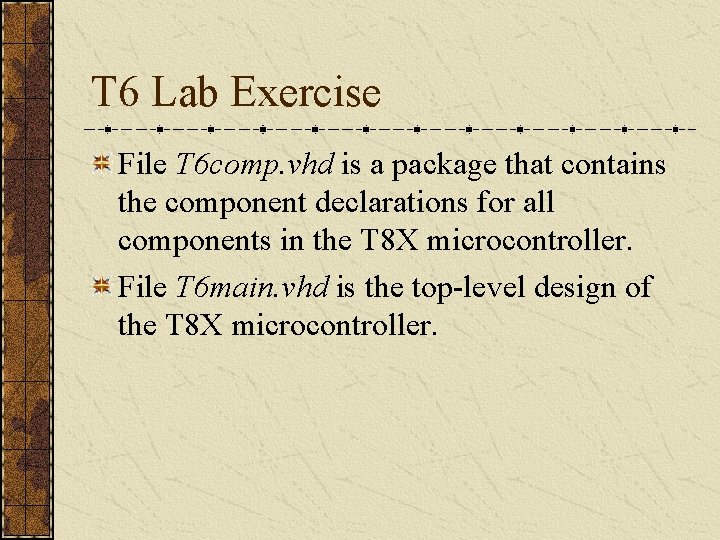

T 6 Lab Exercise File T 6 comp. vhd is a package that contains the component declarations for all components in the T 8 X microcontroller. File T 6 main. vhd is the top-level design of the T 8 X microcontroller.

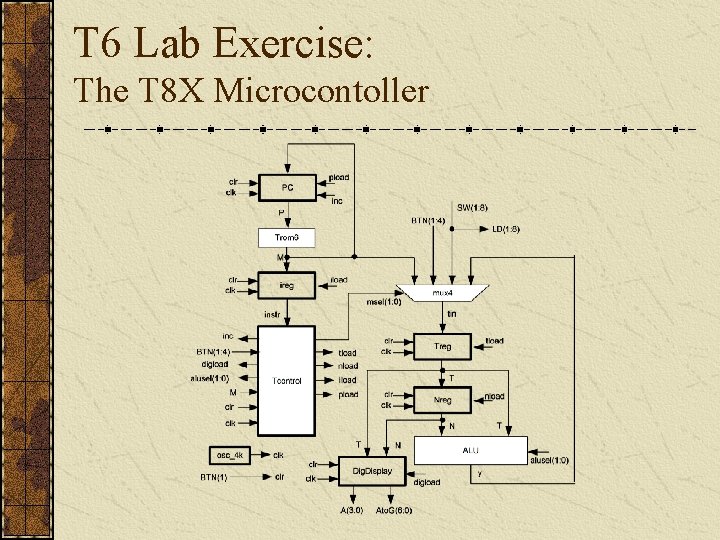

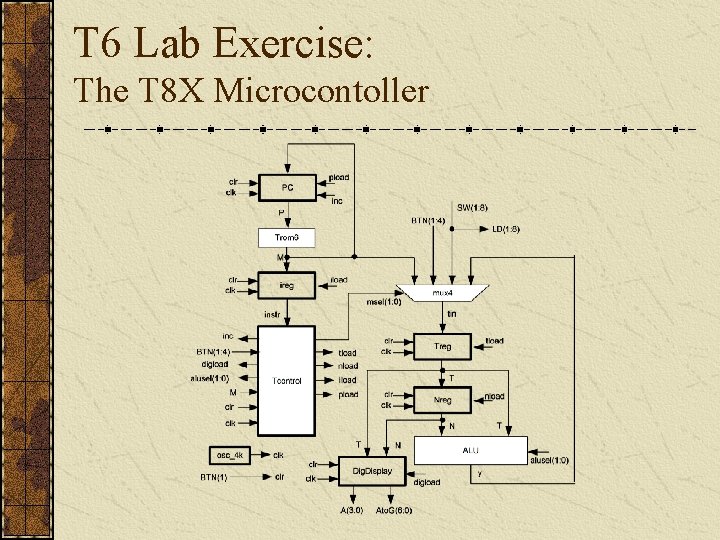

T 6 Lab Exercise: The T 8 X Microcontoller

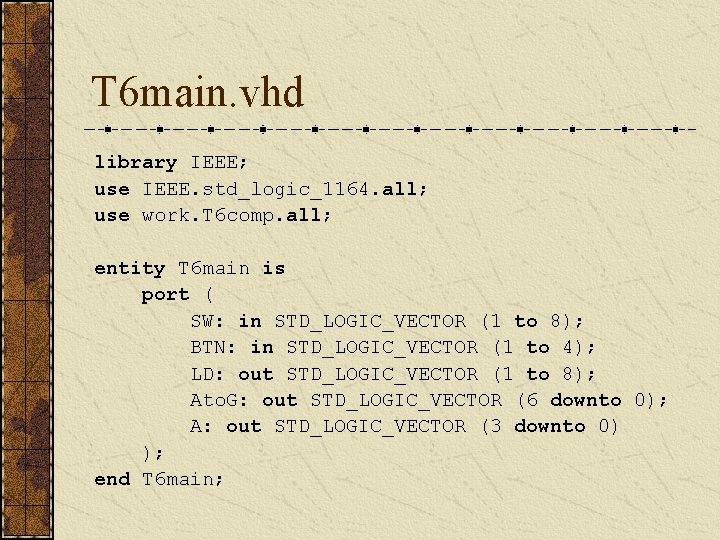

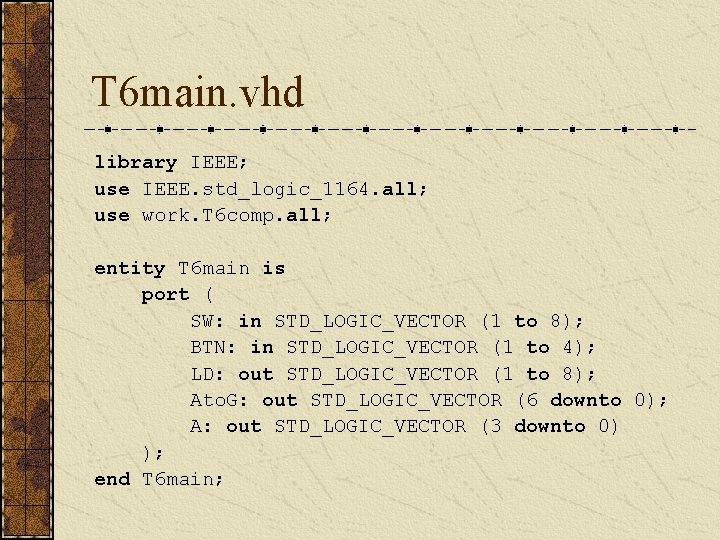

T 6 main. vhd library IEEE; use IEEE. std_logic_1164. all; use work. T 6 comp. all; entity T 6 main is port ( SW: in STD_LOGIC_VECTOR (1 to 8); BTN: in STD_LOGIC_VECTOR (1 to 4); LD: out STD_LOGIC_VECTOR (1 to 8); Ato. G: out STD_LOGIC_VECTOR (6 downto 0); A: out STD_LOGIC_VECTOR (3 downto 0) ); end T 6 main;

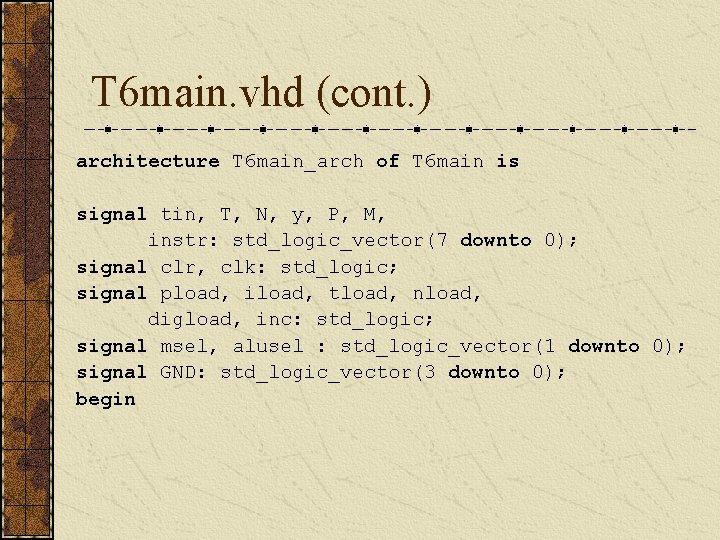

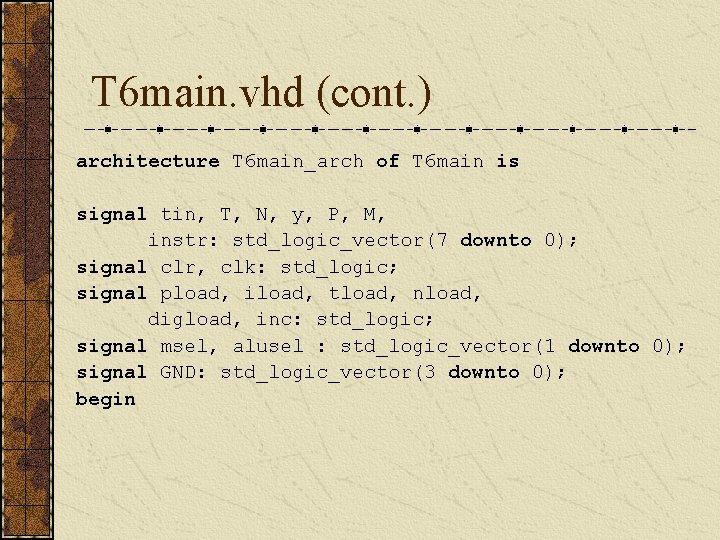

T 6 main. vhd (cont. ) architecture T 6 main_arch of T 6 main is signal tin, T, N, y, P, M, instr: std_logic_vector(7 downto 0); signal clr, clk: std_logic; signal pload, iload, tload, nload, digload, inc: std_logic; signal msel, alusel : std_logic_vector(1 downto 0); signal GND: std_logic_vector(3 downto 0); begin

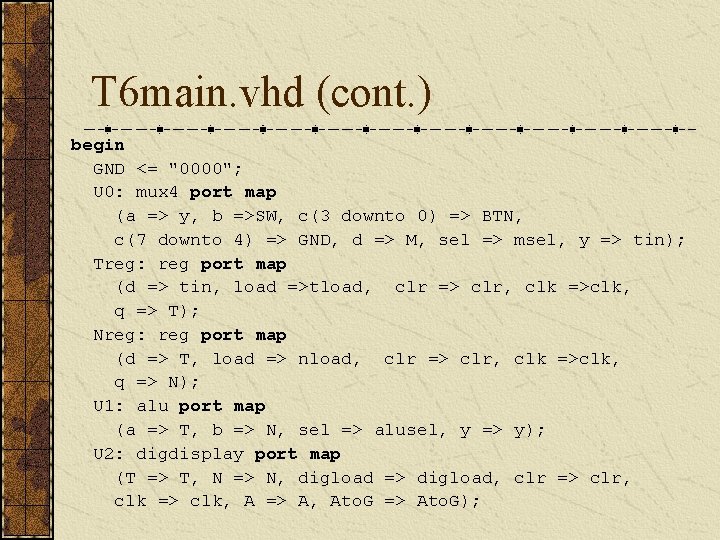

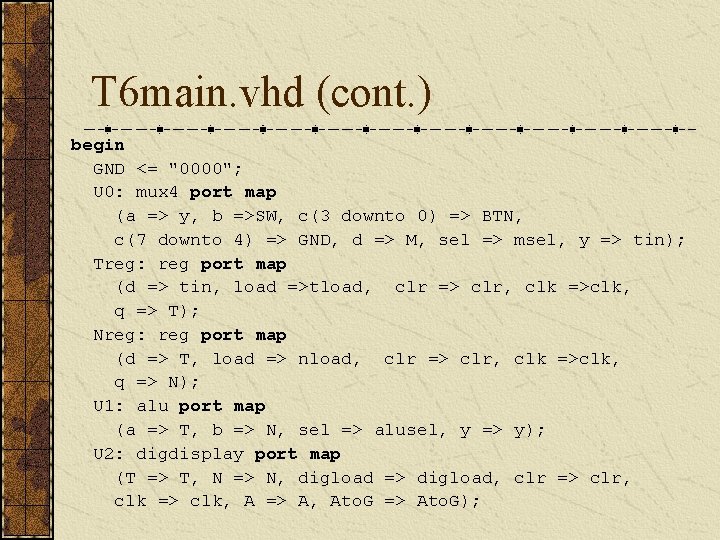

T 6 main. vhd (cont. ) begin GND <= "0000"; U 0: mux 4 port map (a => y, b =>SW, c(3 downto 0) => BTN, c(7 downto 4) => GND, d => M, sel => msel, y => tin); Treg: reg port map (d => tin, load =>tload, clr => clr, clk =>clk, q => T); Nreg: reg port map (d => T, load => nload, clr => clr, clk =>clk, q => N); U 1: alu port map (a => T, b => N, sel => alusel, y => y); U 2: digdisplay port map (T => T, N => N, digload => digload, clr => clr, clk => clk, A => A, Ato. G => Ato. G);

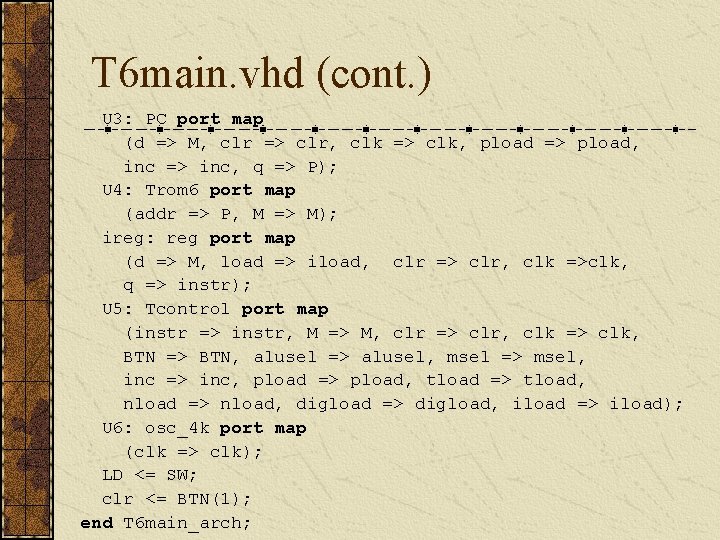

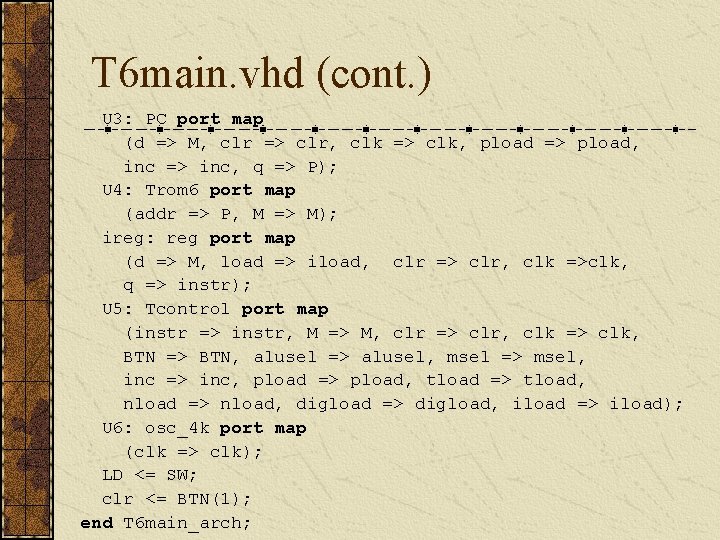

T 6 main. vhd (cont. ) U 3: PC port map (d => M, clr => clr, clk => clk, pload => pload, inc => inc, q => P); U 4: Trom 6 port map (addr => P, M => M); ireg: reg port map (d => M, load => iload, clr => clr, clk =>clk, q => instr); U 5: Tcontrol port map (instr => instr, M => M, clr => clr, clk => clk, BTN => BTN, alusel => alusel, msel => msel, inc => inc, pload => pload, tload => tload, nload => nload, digload => digload, iload => iload); U 6: osc_4 k port map (clk => clk); LD <= SW; clr <= BTN(1); end T 6 main_arch;