Structural VHDL Tutorial R E Haskell and D

- Slides: 14

Structural VHDL Tutorial R. E. Haskell and D. M. Hanna T 3: ALU Design

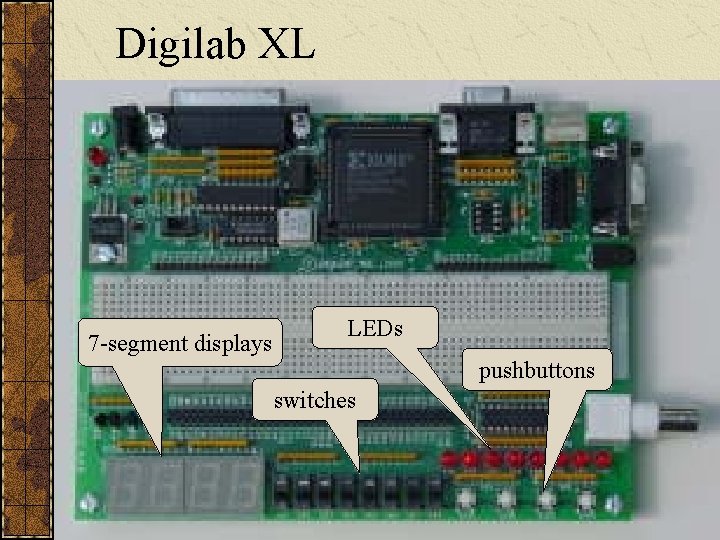

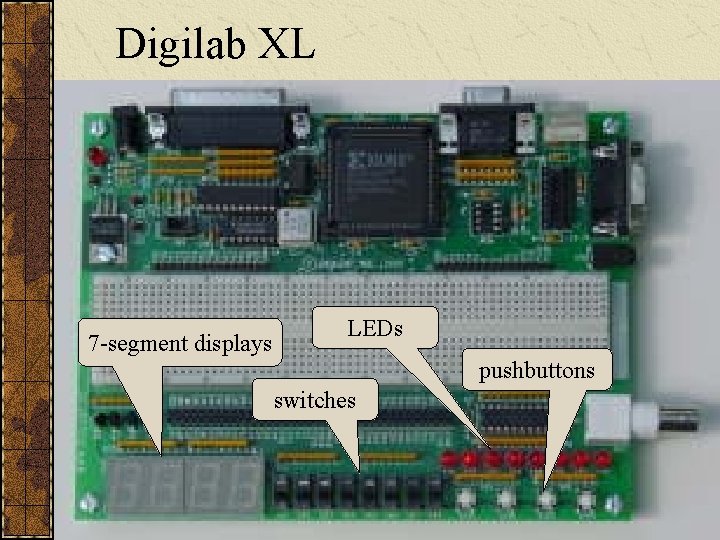

Digilab XL 7 -segment displays LEDs pushbuttons switches

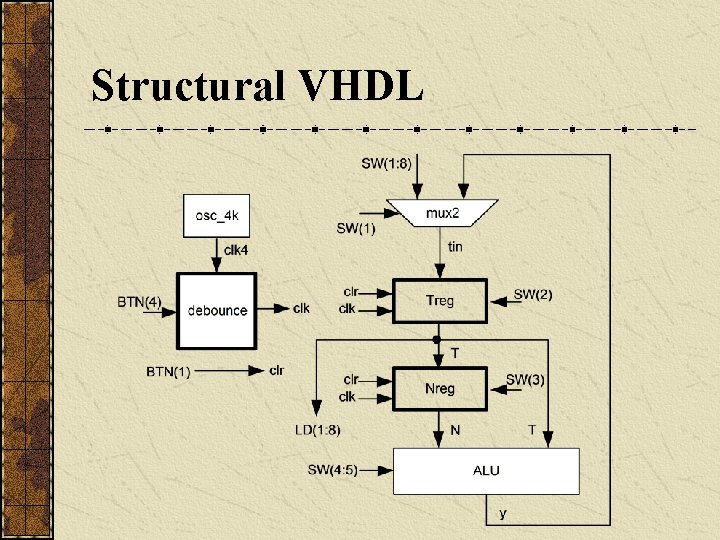

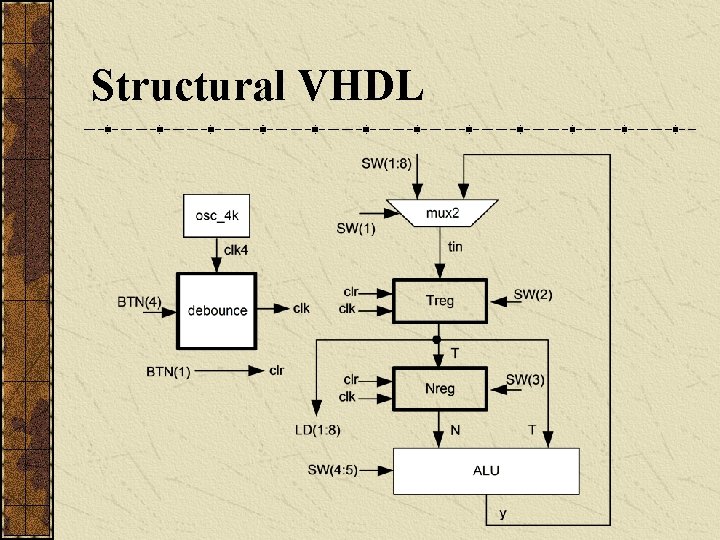

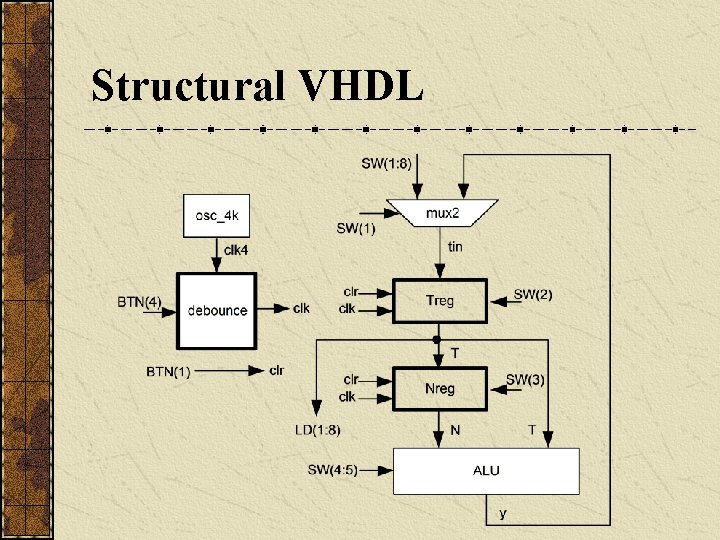

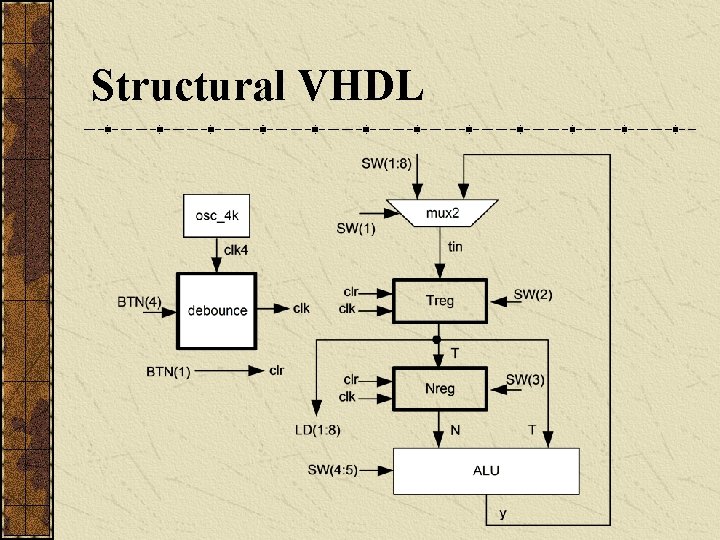

Structural VHDL

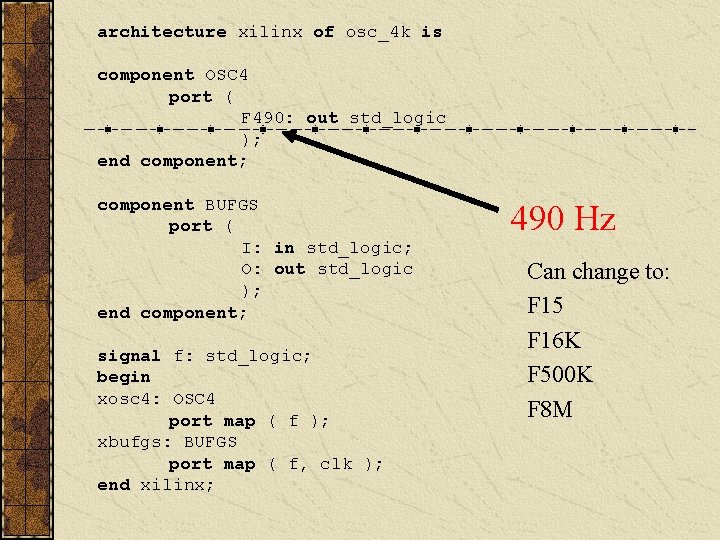

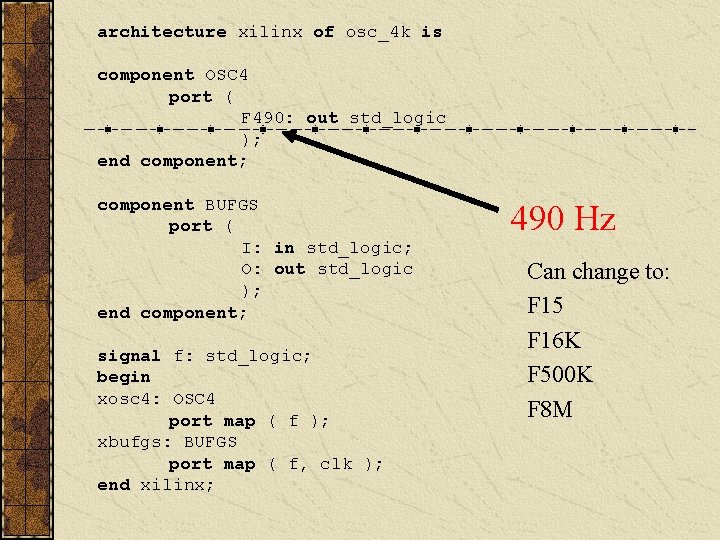

Clock Module: osc_4 k library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_arith. all; entity osc_4 k is port ( clk: out std_logic ); end osc_4 k;

architecture xilinx of osc_4 k is component OSC 4 port ( F 490: out std_logic ); end component; component BUFGS port ( I: in std_logic; O: out std_logic ); end component; signal f: std_logic; begin xosc 4: OSC 4 port map ( f ); xbufgs: BUFGS port map ( f, clk ); end xilinx; 490 Hz Can change to: F 15 F 16 K F 500 K F 8 M

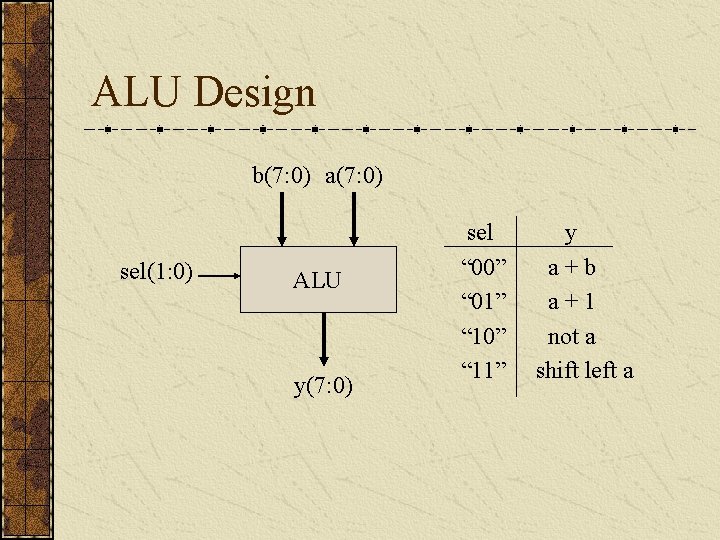

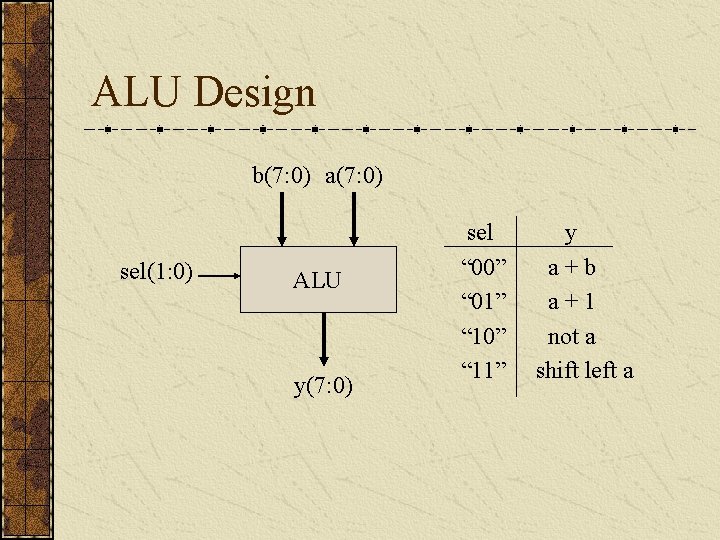

ALU Design b(7: 0) a(7: 0) sel(1: 0) ALU y(7: 0) sel “ 00” “ 01” “ 10” “ 11” y a+b a+1 not a shift left a

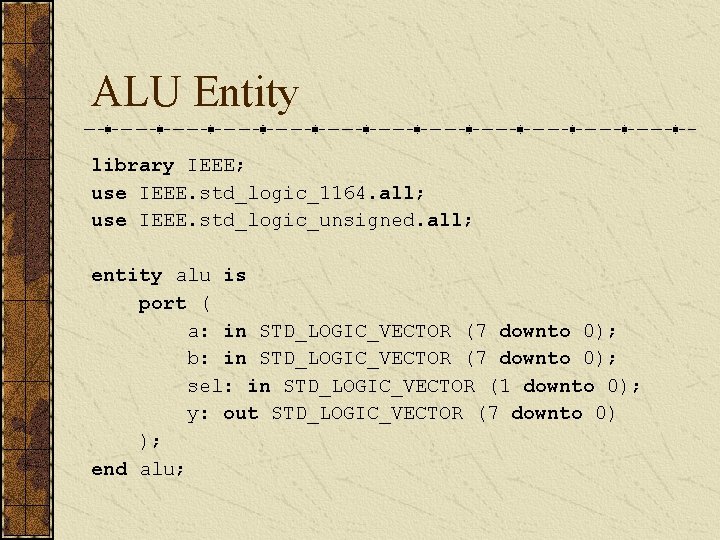

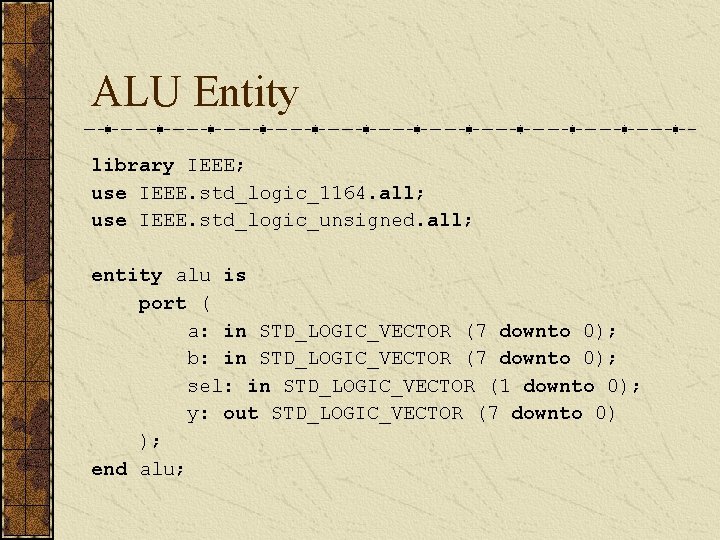

ALU Entity library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_unsigned. all; entity alu is port ( a: in STD_LOGIC_VECTOR (7 downto 0); b: in STD_LOGIC_VECTOR (7 downto 0); sel: in STD_LOGIC_VECTOR (1 downto 0); y: out STD_LOGIC_VECTOR (7 downto 0) ); end alu;

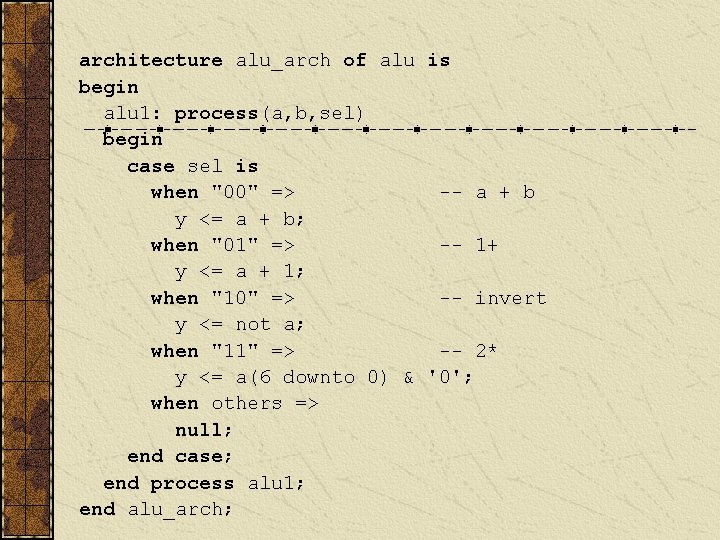

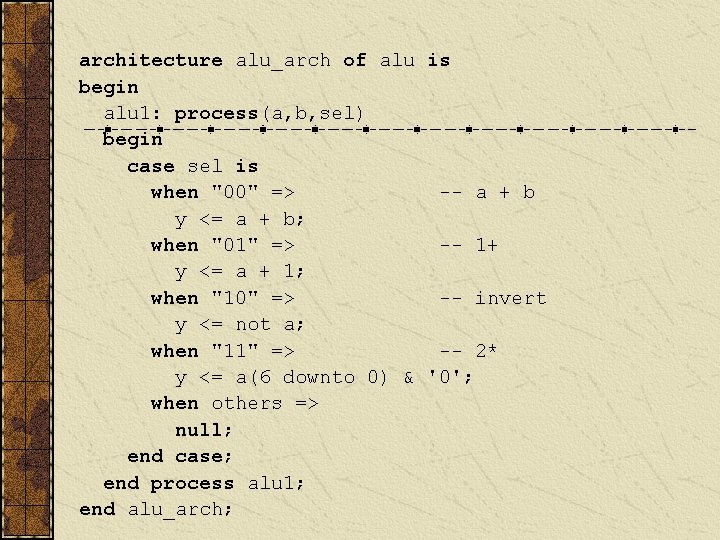

architecture alu_arch of alu is begin alu 1: process(a, b, sel) begin case sel is when "00" => -- a + b y <= a + b; when "01" => -- 1+ y <= a + 1; when "10" => -- invert y <= not a; when "11" => -- 2* y <= a(6 downto 0) & '0'; when others => null; end case; end process alu 1; end alu_arch;

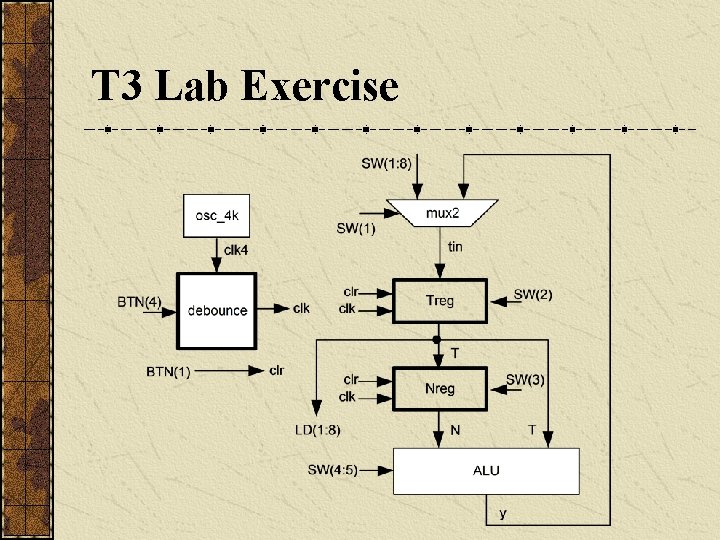

Structural VHDL

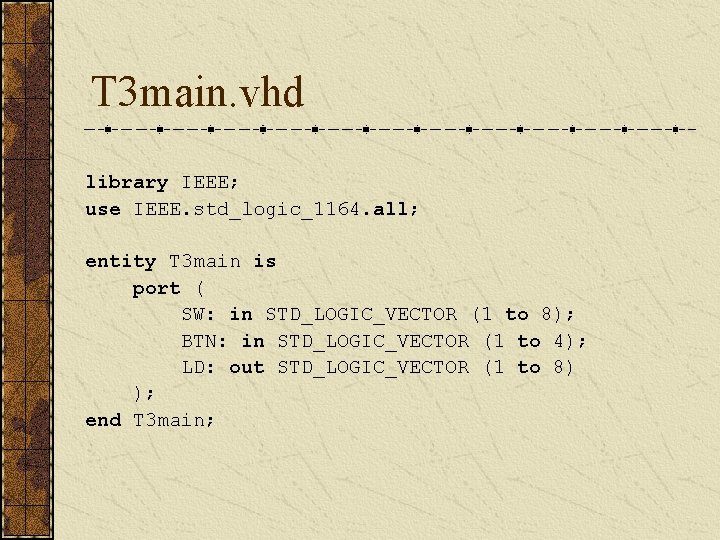

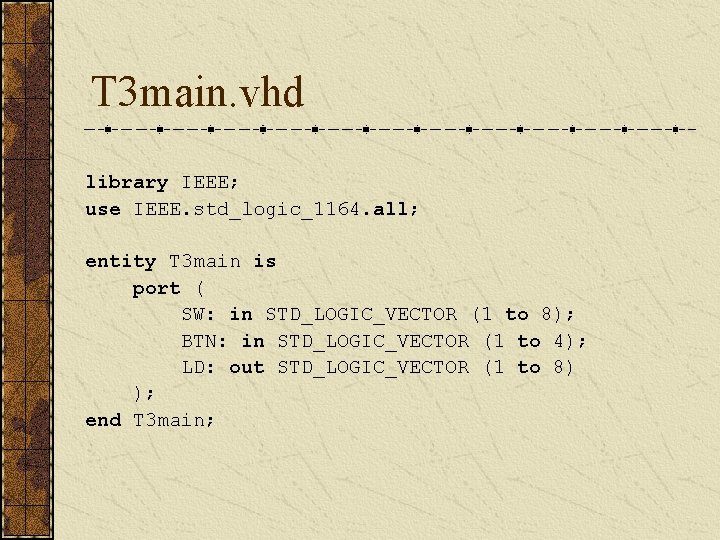

T 3 main. vhd library IEEE; use IEEE. std_logic_1164. all; entity T 3 main is port ( SW: in STD_LOGIC_VECTOR (1 to 8); BTN: in STD_LOGIC_VECTOR (1 to 4); LD: out STD_LOGIC_VECTOR (1 to 8) ); end T 3 main;

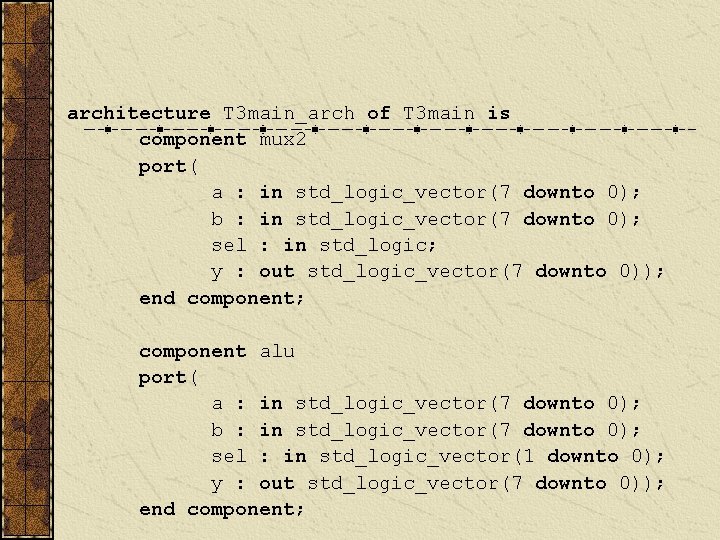

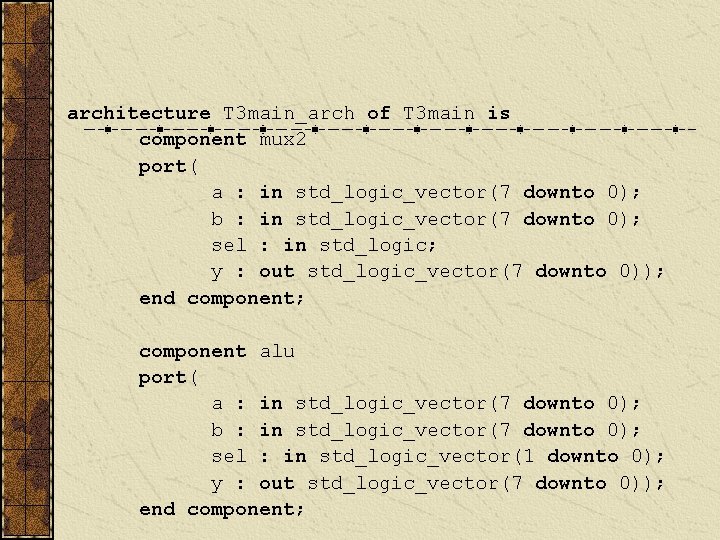

architecture T 3 main_arch of T 3 main is component mux 2 port( a : in std_logic_vector(7 downto 0); b : in std_logic_vector(7 downto 0); sel : in std_logic; y : out std_logic_vector(7 downto 0)); end component; component alu port( a : in std_logic_vector(7 downto 0); b : in std_logic_vector(7 downto 0); sel : in std_logic_vector(1 downto 0); y : out std_logic_vector(7 downto 0)); end component;

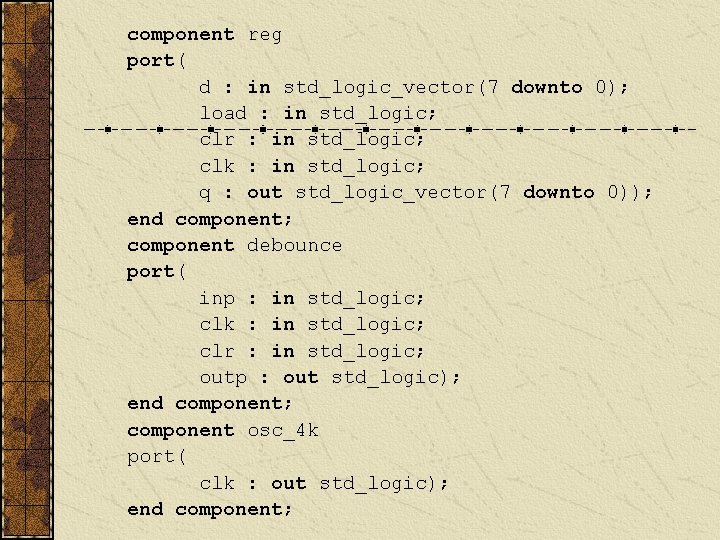

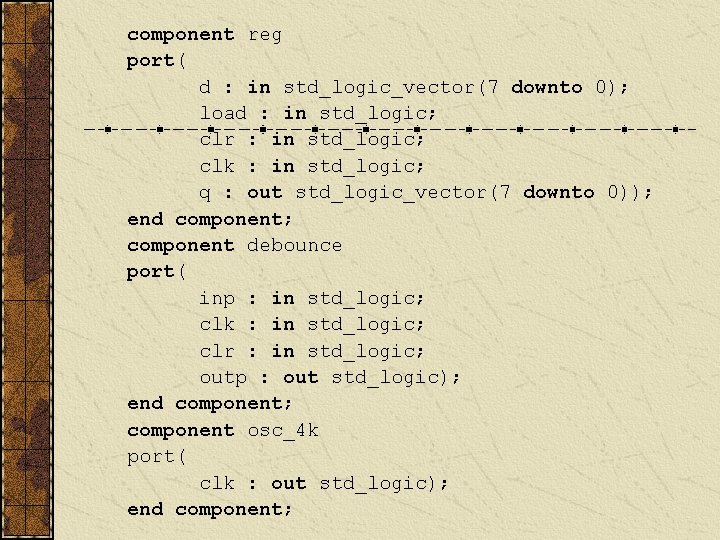

component reg port( d : in std_logic_vector(7 downto 0); load : in std_logic; clr : in std_logic; clk : in std_logic; q : out std_logic_vector(7 downto 0)); end component; component debounce port( inp : in std_logic; clk : in std_logic; clr : in std_logic; outp : out std_logic); end component; component osc_4 k port( clk : out std_logic); end component;

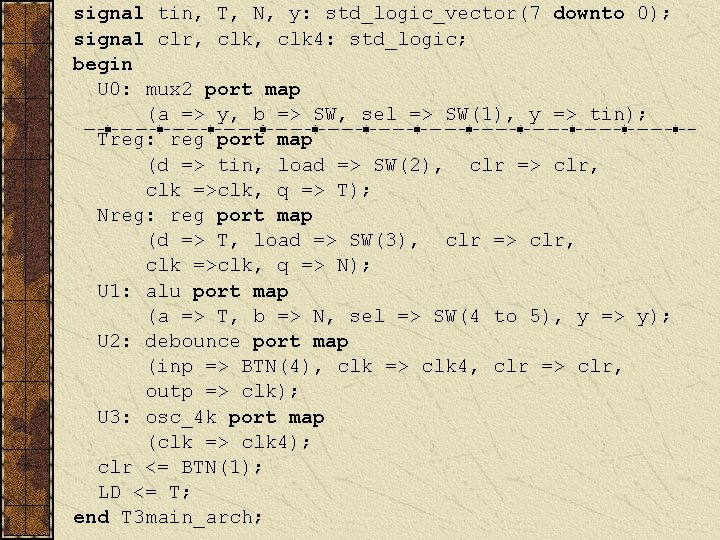

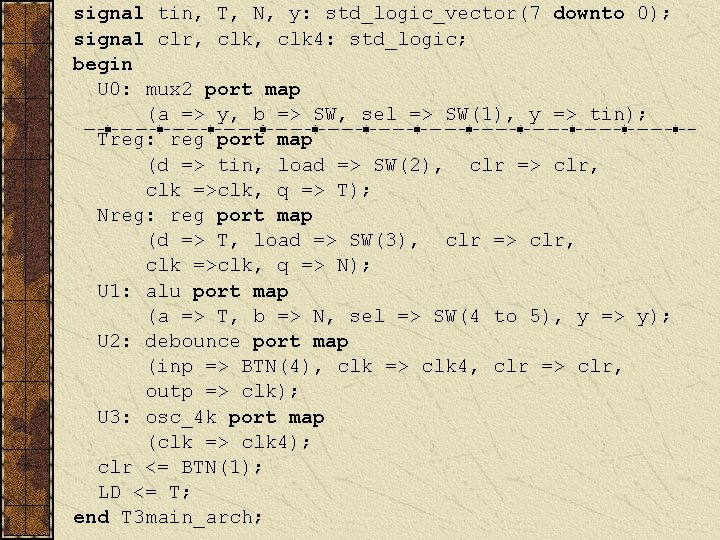

signal tin, T, N, y: std_logic_vector(7 downto 0); signal clr, clk 4: std_logic; begin U 0: mux 2 port map (a => y, b => SW, sel => SW(1), y => tin); Treg: reg port map (d => tin, load => SW(2), clr => clr, clk =>clk, q => T); Nreg: reg port map (d => T, load => SW(3), clr => clr, clk =>clk, q => N); U 1: alu port map (a => T, b => N, sel => SW(4 to 5), y => y); U 2: debounce port map (inp => BTN(4), clk => clk 4, clr => clr, outp => clk); U 3: osc_4 k port map (clk => clk 4); clr <= BTN(1); LD <= T; end T 3 main_arch;

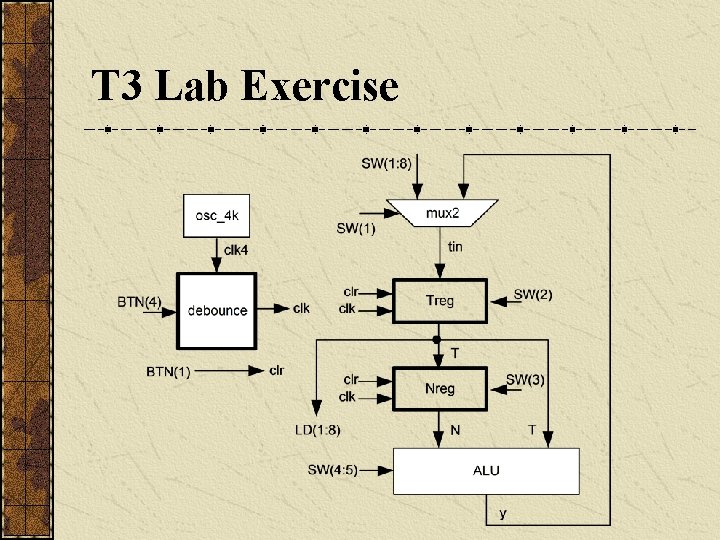

T 3 Lab Exercise